Изобретение относится к импульсной технике и может быть использовано для селекции импульсных сигналов по амплитуде, величина которой находится в заданных пределах.

Целью изобретения является повышение точности набора импульсов в канал за счет исключения ошибок, возникающих в момент прихода сигнала пе- реключения каналов.

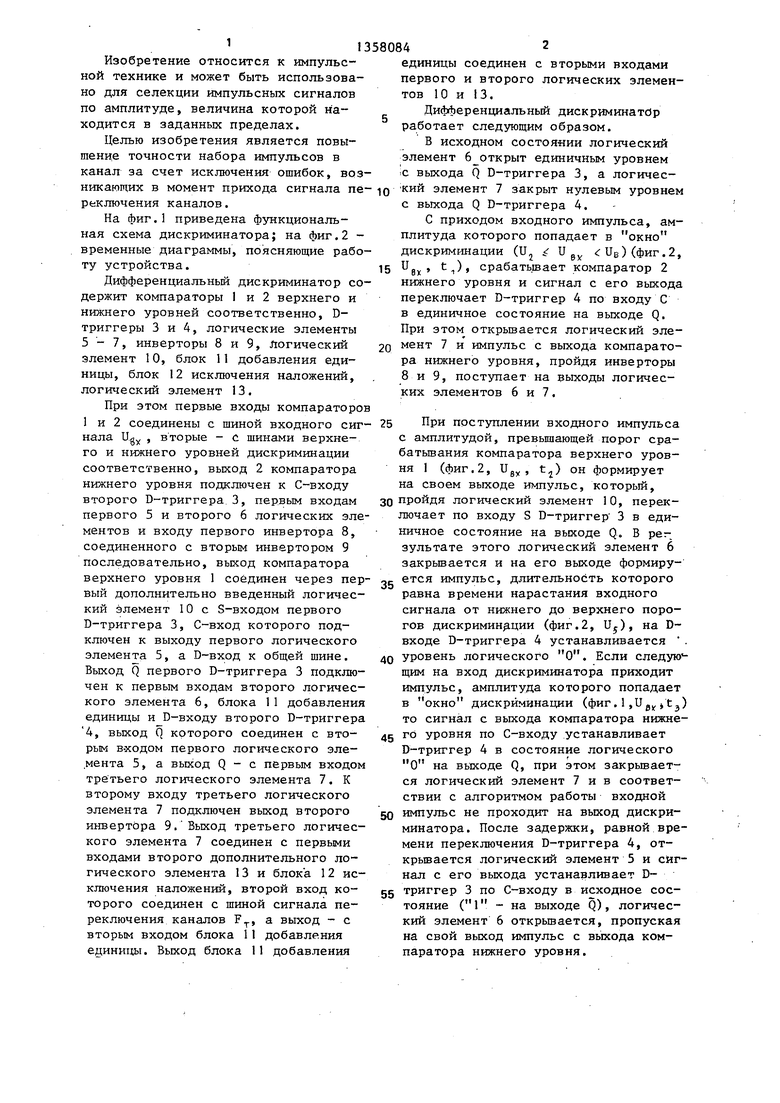

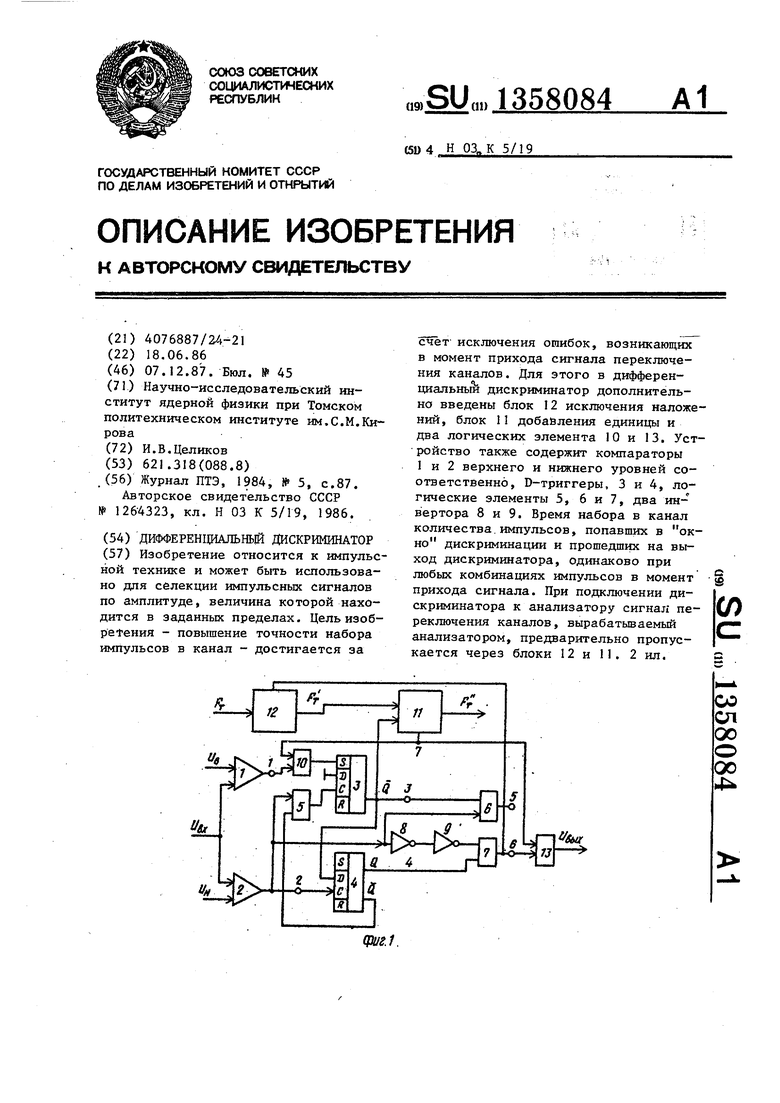

На фиг.1 приведена функциональная схема дискриминатора; на фиг,2 - временные диаграммы, поясняющие работу устройства.

Дифференциальньй дискриминатор содержит компараторы 1 и 2 верхнего и нижнего уровней соответственно, D- триггеры 3 и 4, логические элементы 5-7, инверторы 8 и 9, Логический элемент 10, блок 11 добавления единицы, блок 12 исключения наложений, логический элемент 13.

При этом первые входы компараторов 1 и 2 соединены с шиной входного сиг

нала и,

8х

вторые - с шинами верхнего и нижнего уровней дискриминации соответственно, выход 2 компаратора нижнего уровня подключен к С-входу второго D-триггера 3, первым входам первого 5 и второго 6 логических элементов и входу первого инвертора 8, соединенного с вторым инвертором 9 последовательно, выход компаратора верхнего уровня 1 соединен через первый дополнительно введенный логический элемент 10 с S-входом первого D-триггера 3, С-вход которого подключен к выходу первого логического элемента 5, а D-вход к общей шине. Выход Q первого D-триггера 3 подключен к первым входам второго логического элемента 6, блока 11 добавления единицы и D-входу второго D-триггера 4, выход Q которого соединен с вторым в-ходом первого логического эле- ,мента 5, а выход Q - с первым входом тре тьего логического элемента 7. К второму входу третьего логического элемента 7 подключен выход второго инвертора 9. Выход третьего логического элемента 7 соединен с первыми входами второго дополнительного логического элемента 13 и блока 12 исключения наложений, второй вход которого соединен с шиной сигнала переключения каналов F, а выход - с вторым входом блока 11 добавления единиць. Выход блока 11 добавления

единицы соединен с вторьми входами первого и второго логических элементов 10 и 13.

Дифференциальный дискриминатор работает следующим образом.

В исходном состоянии логический элемент 6 открыт единичным уровнем -с выхода Q D-триггера 3, а логичес- кий элемент 7 закрыт нулевым уровнем с выхода Q D-триггера 4.

С приходом входного импульса, амплитуда которого попадает в окно

дискриминации (U i U ие)(фиг.2.

и

Ug , t), срабатьюает компаратор 2 нижнего уровня и сигнал с его выхода переключает D-триггер 4 по входу С в единичное состояние на выходе Q. При этом открьюается логический элемент 7 и импульс с выхода компаратора нижнего уровня, пройдя инверторы 8 и 9, поступает на выходы логических элементов 6 и 7.

35

25 При поступлении входного импульса с амплитудой, превышающей порог сра- батьшания компаратора верхнего уровня 1 (фиг.2, Ug, tj) он формирует на своем выходе импульс, который, 30 пройдя логический элемент 10, переключает по входу S D-триггер 3 в единичное состояние на выходе Q. В рег- зультате этого логический элемент 6 закрывается и на его выходе формируется импульс, длительность которого равна времени нарастания входного сигнала от нижнего до верхнего порогов дискриминации (фиг.2, Uj), на D- входе D-триггера 4 устанавливается 40 уровень логического О. Если следую щим на вход дискриминатора приходит импульс, амплитуда которого попадает в окно дискриминации (фиг. 1 ,Ugi t то сигнал с выхода компаратора нижне 45 ° уровня по С-входу устанавливает D-триггер 4 в состояние логического О на выходе Q, при этом закрывается логический элемент 7 и в соответствии с алгоритмом работы входной so импульс не проходит на выход дискриминатора. После задержки, равной времени переключения D-триггера 4, открывается логический элемент 5 и сигнал с его выхода устанавливает D- триггер 3 по С-входу в исходное состояние (1 - на выходе Q), логический элемент 6 открьшается, пропуская на свой выход импульс с выхода компаратора нижнего уровня.

55

fO

31358084

Если на вход дискриминатора приходит подряд несколько импульсов с амплитудой, превьшающей верхний порог дискриминации (фиг.2,и,t),то В-триггер 3 по входам S и С переключается из нулевого состояния на выходе Q в единичное и обратно.

Таким образом, в результате работы устройства количество импульсов, прошедших на выход логического элемента 7, равно количеству входных импульсов, попавших в окно дискриминации .

Разделение импульсов по каналам осуществляется сигналом переключения каналов F (фиг.2,Р). Если в момент прихода сигнала F на вход блока 12 исключения наложений на вьпсоде логического элемента 7 присутствует выходной импульс (фиг.2, F,t), то прохождение сигнала F. блокируется. По срезу выходного импульса логического элемента 7 происходит разблокировка и сигнал F проходит на выход блока 12 исключения наложений в виде сигнала F (фиг.2, F, t,). Сигнал поступает на первый вход блока 12 добавления единицы,, которьш при наличии на его втором входе единичного уровня с выхода Q D-триггера 4, формирует импульс по фронту или срезу

При подключении дискриминатора к анализатору сигнал переключения каналов, вырабатьюаемый анализатором, предварительно пропускается через блоки исключения наложений и добавления единицы.

Формула изобретения

20

сигнала Т (фиг.2, U,). СформированДифференциальный дискриминатор, содержащий компараторы верхнего и нижнего уровней дискриминации, первые входы которых соединены с шиной входного сигнала, вторые - с шинами 5 верхнего и нижнего уровней дискриминации соответственно, выход первого элемента соединен с С-входом первого D-триггера, выход Q которого подключен к второму входу второго логического элемента и D-входу второго D- триггера, выход компаратора нижнего уровня соединен с первыми входами первого и второго логических элементов, через два последовательно соединенных инвертора - с вторым входом третьего логического элемента и D- входом второго D-триггера, выходы Q и Q которого подключены к вторым входам первого и третьего логических элементов соответственно, о т л и - чаюш;ийся тем, что, с целью повьш1ения точности набора импульсов в канал, в него дополнительно введены блок исключения наложений, блок

30

ный импульс складьтается с содержимым предьщущего канала через логический, элемент 13 (фиг.2, Ug,t). Одно- 35 добавления единицы и два дополнитель- временно из i-ro канала вычитается ньк логических элемента, причем вы единица путем установления D-триггера 3 через логический элемент 10 по

S-ВХОДУ в нулевое состояние на выхоход компаратора верхнего уровня соединен с первым входом первого дополнительного логического элемента, вы- де Q (фиг.2, Uj, t, )..Благодаря это- 40 ход которого подключен к S-входу му первый импульс, пришедший в первого D-триггера, выход Q первого (1+1)-й канал, независимо от амплиту- D-триггера соединен с первым входом ды предьщущего импульса не процус- блока добавления единицы, к второму кается на выход логического элемента входу которого подключен выход бло- 7 (фиг.2, и J, t .j) . Сигнал F преоб- ка исключения наложений выход блока разуется блоком добавления единицы в добавления единицы соединен с вторы- соответствии с алгоритмом работы устройства в сигнал F. (фиг.2, F).

ми входами первого и второго дополнительных логических элементов, выход третьего логического элемента подключен к первым входам второго дополнительного логического элемента и блока исключения наложений, второй вход блока исключения наложения соединен с шиной сигнала переключения каналов.

Таким образом, за время набора в канал количество, импульсов, попавших в окно дискриминации и прошедших на выход дискриминатора, одинаково при любых комбинациях импульсов в момент прихода сигнала переключения каналов.

При подключении дискриминатора к анализатору сигнал переключения каналов, вырабатьюаемый анализатором, предварительно пропускается через блоки исключения наложений и добавления единицы.

Формула изобретения

fO

20

Дифференциальный дискриминатор, содержащий компараторы верхнего и нижнего уровней дискриминации, первые входы которых соединены с шиной входного сигнала, вторые - с шинами 5 верхнего и нижнего уровней дискриминации соответственно, выход первого элемента соединен с С-входом первого D-триггера, выход Q которого подключен к второму входу второго логического элемента и D-входу второго D- триггера, выход компаратора нижнего уровня соединен с первыми входами первого и второго логических элементов, через два последовательно соединенных инвертора - с вторым входом третьего логического элемента и D- входом второго D-триггера, выходы Q и Q которого подключены к вторым входам первого и третьего логических элементов соответственно, о т л и - чаюш;ийся тем, что, с целью повьш1ения точности набора импульсов в канал, в него дополнительно введены блок исключения наложений, блок

30

35 добавления единицы и два дополнитель ньк логических элемента, причем вы

ход компаратора верхнего уровня соединен с первым входом первого дополнительного логического элемента, вы- 40 ход которого подключен к S-входу первого D-триггера, выход Q первого D-триггера соединен с первым входом блока добавления единицы, к второму входу которого подключен выход бло- ка исключения наложений выход блока добавления единицы соединен с вторы-

50

ми входами первого и второго дополнительных логических элементов, выход третьего логического элемента подключен к первым входам второго дополнительного логического элемента и блока исключения наложений, второй вход блока исключения наложения соединен с шиной сигнала переключения каналов.

i,

фиг. I

| название | год | авторы | номер документа |

|---|---|---|---|

| Дифференциальный дискриминатор | 1985 |

|

SU1264323A1 |

| УСТРОЙСТВО СЕЛЕКЦИИ ВЫБРОСОВ СЛУЧАЙНЫХ ПРОЦЕССОВ | 2005 |

|

RU2300803C1 |

| Амплитудный дифференциальный дискриминатор | 1980 |

|

SU900254A1 |

| Устройство для измерения временных параметров радиоимпульсов | 1977 |

|

SU687415A1 |

| Устройство для оценки напряженного состояния массива горных пород | 1989 |

|

SU1645512A1 |

| Устройство для передачи информации с вращающегося объекта | 1986 |

|

SU1334173A1 |

| ЦИФРОВАЯ ОБРАБОТКА ИМПУЛЬСОВ В СХЕМАХ СЧЕТА МУЛЬТИСПЕКТРАЛЬНЫХ ФОТОНОВ | 2008 |

|

RU2472179C2 |

| ЦЕЗИЕВЫЙ СТАНДАРТ ЧАСТОТЫ | 1994 |

|

RU2076411C1 |

| Устройство для регулирования реактивной мощности | 1987 |

|

SU1471247A1 |

| Устройство для цифрового анализа формы однократных электрических сигналов | 1982 |

|

SU1049832A1 |

Изобретение относится к импульсной технике и может быть использовано для селекции импульсных сигналов по амплитуде, величина которой находится в заданных пределах. Цель изобретения - повышение точности набора импульсов в каиал - достигается за счет исключения ошибок, возникающих в момент прихода сигнала переключения каналов. Для этого в дифференциальный дискриминатор дополнительно введены блок 12 исключения наложений, блок 11 добавления единицы и два логических элемента 10 и 13. Устройство также содержит компараторы 1 и 2 верхнего и нижнего уровней соответственно, D-триггеры, 3 и 4, логические элементы 5, 6 и 7, два ин-° вертора 8 и 9. Время набора в каиал количества, импульсов, попавших в окно дискриминации и прошедших на выход дискриминатора, одинаково при любых комбинациях импульсов в момент прихода сигнала. При подключении дискриминатора к анализатору сигнал переключения каналов, вырабатываемый анализатором, предварительно пропускается через блоки 12 и 11. 2 ил. сл со ел 00 о 00

| Журнал ПТЭ, 1984, 5, с.87 | |||

| Ударно-вращательная врубовая машина | 1922 |

|

SU126A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-12-07—Публикация

1986-06-18—Подача