Изобретение относится к импульсной Технике и быть использовано для амплитудной селекции импульсов.

Известны амплитудные дифференциальные дискриминаторы, содержащие кo шapaтopы вер. него и нижнего уровней г вспомогательный триггер, инвертор и выходной каскащ на схеме ИЛИ-НЕ 1.

Однако эти устройства обладают тем недостатком, что выходной сигнал по длительности равен той части входного исследуемого сигнала, которая превышает уровень дискриминации компаратора нижнего уровня, В результате при малых длительностях входного сигнала происходит потеря информации в линии, соединяющей выход дискриминатора с регистрирующим устройством.

Наиболее близким по технической сущности к предлагаемому является 1мгшитудный дифференциальный дискрилетнатор, содержащий компаратор нижнего и верхнего уровней, основной D-триггер, установочный вход которого подключен к выходу компаратора верхнего уровня и дополнительный D-триггер, входом синхронизации подключенный к выходу компаратора нижнего уровня.

Существенной особенностью известного устройства является то, что для его работы необходимо срабатывание основного триггера по переднему фронту , а дополнительного - по спаду импульса с выхода компаратора нижнего уровня.

Определенное состояние основного триггера в момент прихода спада импульса с компаратора нижнего уровня определяет попал ли исследуемый сигнал в окно дискриминатора. Работоспособность известного устройства сохраняется только при условии установления определенного состояния основного триггера до прихода спада импульса с выхода компаратора нижнего уровня 2.

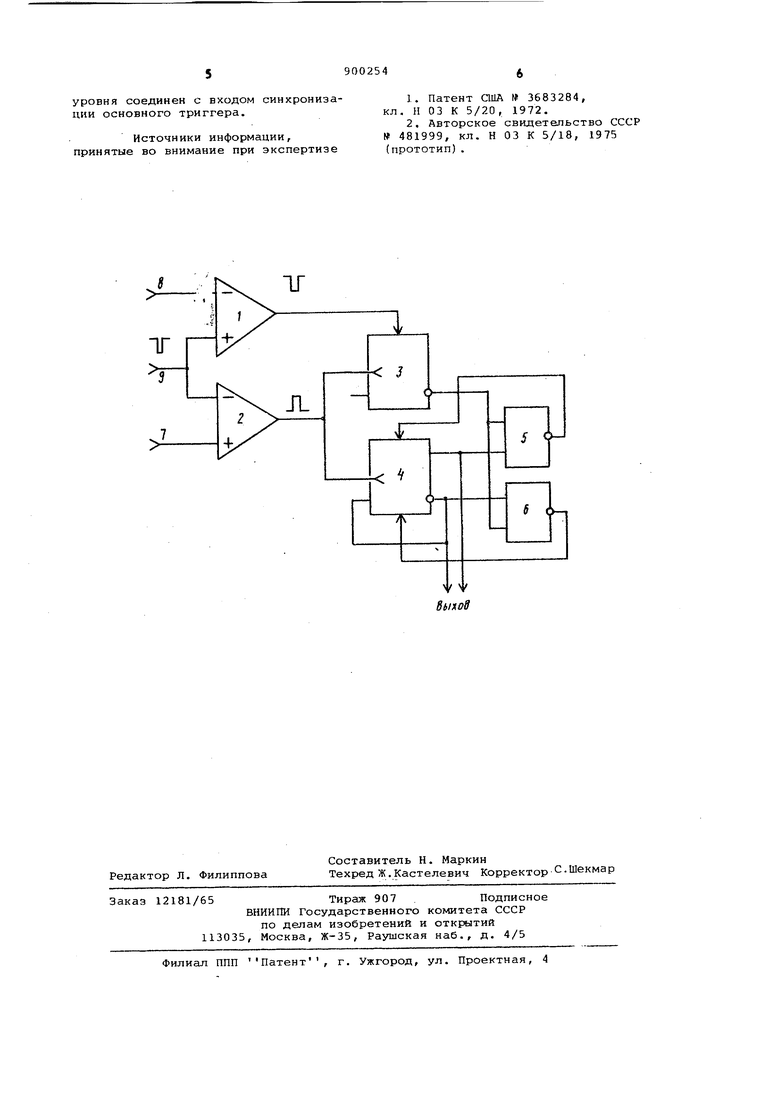

Однако из-за задержки сигнала на инверторе и вспомогательном триггере, это условие не выполняется при исследовании сигналов малой длительности, что приводит к ошибкам при дискриминации и снижает быстродействие известного устройства. Кроме этого, быстродействие известного устройства ограничивается собственным мертвым, обусловленным включением элемента задержки для форг ирования выходного сигнала по длительности. Цель изобретения - повьаиение быст родействия и расп1ирение функциональных возможностей. Для достижения поставленной цели в амплитудный дифференциальный дискриминатор, содержащий компараторы нижнего и верхнего уровней,- основной D-триггер, установочный вход которого подключен к выходу компаратора верхнего уровня, и дополнительНый D-триггер, входом синхронизации подключенный к выходу компаратора нижнего уровня, введены два элемента , первые входы которых подклю чены ic выходу основного триггера, а второй вход первого элемента И-НЕ соединен с неинвертирующим выходом дополнительного триггера, установочный вход установки в т которого псдключен к -выходу первого элемента И-НЕ, а установочный вход установки в - к выходу второго элемента И-НЕ, вторым входом соединенного с неинвертирующим выходом и Д-входом дополнительно1О триггера, причем выход компаратора нижнего уровня соединен с входом синхронизации основного триггера. На чертеже представлена блок-схем амплитудного дифференциального дискриминатора. Устройство содержит компг1раторы верхнего 1 и, нижнего 2 уровней, выходами подключенные к входам основного 3 и дополнительного 4 D-тригге ров, при этом выход основного триггера 3 подключен к первым входам элементов И-НЕ 5 и б. Шины , сигналов 7--9 подклю чены соответственно к источнику ниж него и верхнего уровня и источнику входного сигнала. Амплитудный дифференциальный дис криминатор работает следующим образом. Если амплитуда исследуемого импульса превышает напряжение только нижнего уровня дискриминации, то по положительному перепаду сигнала с выхода компаратора нижнего уровня 2 на выходе основного триггера 3 и, соответственно, на первых входах элементов 5 и 6 установится уровень логического О . Если же амплитуда исследуемого импульса превышает также напряжение верхнего уровня дискриминации, то сигнал с выхода компаратора верхнеГО)уровня 1 установит на выходе осHOj Horo триггера 3 .и, следовательно, на первых входах элементов 5 и уровень логической . . При уровне логического первых входах элементов 5 и 6 на их выходах и, следовательно, на устано вочных входах дополнительного триггера 4 устанавливается уровень логи ческой и каждый положительный перепад с выхода компаратора нижнего уровня 2 приводит к изменению состояния дополнительного триггера 4 на противоположное. При наличии уровня на первых входах элементов 5 и б, на их выходах, и, следовательно, на установочных входах дополнительного триггера 4 устанавливаются соответствующие логические уровни, подтверждающие состояние дополнительного триггера 4, в котором он был до этого.В результате дополнительный триггер 4 не изменяет своего состояния независимо от величины сигнала на его входе синхронизации. Таким образом, при поступлении каждого следующего исследуемого импульса, амплитуда которого превышает напряжение нижнего уровня дискриминации, по положительному перепаду сигнала с выхода компаратора нижнего уровня 2 изменяется состояние дополнительного триггера 4 только в том случае, если предьщущий исследуe «JIй импульс попал в окно дискриминатора, т.е. на выходе триггера 4 происходит деление частоты входного сигнала непосредственнов процессе амплитудной селекции. Поскольку для работы устройства не требуется установление определенного состояния на выходе основного триггера 3 за время действия исследуемого импульса, амплитудный диф/ференциальный дискриминатор характеризуется повышенным быстродействием и осуществляет деление частоты следования входных сигналов, удовлетворяющих условию амплитудного отбора, непосредственно в процессе амплитудной селекции. Формула изобретения Амплитудный дифференциальный дискриминатор, содержащий компараторы нижнего и верхнего уровней, основной D-триггер, установочный вход которого подключен к выходу компаратора верхнего уровня, и дополнительный D-триггер, входом синхронизации подключенный к выходу компаратора нижнего уровня, отличающийс я тем, что, с целью повышения быстродействия и расширения функциональных возможностей, в него введены два элемента И-НЕ, первые входы которых подключены к выходу основного триггера, а второй вход первого элемента И-НЕ соединен с неинвертирующим выходом дополнительного тригге-/ ра, установочный вход установки в 1 которого подключен; к выходу первого.элемента И-НЕ,а установочный вход установки в - к выходу второго элемента И-НЕ, вторым входом соединенного с инвертирующим выходом и Д-входом дополнительного триггера, причем выход компаратора нижнего

уровня соединен с входом синхронизации основного триггера.

Источники информации, принятые во внимание при экспертизе

1.Патент QUA № 3683284, кл. Н 03 К 5/20, 1972,

2.Авторское свидетельство СССР № 481999, кл. Н 03 К 5/18, 1975

(прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Амплитудно-фазовый дискриминатор | 1978 |

|

SU752216A1 |

| Дифференциальный дискриминатор | 1985 |

|

SU1264323A1 |

| ДИСКРИМИНАТОР ИМПУЛЬСОВ | 1992 |

|

RU2026604C1 |

| Амплитудный дифференциальный дискриминатор | 1978 |

|

SU765780A1 |

| Устройство для измерения временных параметров радиоимпульсов | 1977 |

|

SU687415A1 |

| Частотный дискриминатор | 1983 |

|

SU1124423A1 |

| Дифференциальный дискриминатор | 1986 |

|

SU1358084A1 |

| СПОСОБ РЕГИСТРАЦИИ СЛАБЫХ СВЕТОВЫХ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2001 |

|

RU2190196C1 |

| СПЕКТРОМЕТРИЧЕСКИЙ СПОСОБ ИЗМЕРЕНИЯ ЯДЕРНЫХ ИЗЛУЧЕНИЙ И РЕАЛИЗУЮЩАЯ ЕГО СПЕКТРОМЕТРИЧЕСКАЯ СИСТЕМА | 2002 |

|

RU2269798C2 |

| Устройство для определения динамических характеристик материалов | 1982 |

|

SU1021953A1 |

Авторы

Даты

1982-01-23—Публикация

1980-05-29—Подача