00

vj

СП

эо

11370758

Изобретение относится к импульсной технике и может быть использовано при построении аналого-цифровых преобразователей ,

Целью изобретения является уменьшение времени восстановления компаратора тока после перегрузки за счет обеспечения возможности быстрого

дифференциального усилителя 12, при этом управляющие входы ключей подсоединены непосредственно к входной шине 3 стробирования,

Устройство работает следующим образом.

Когда на входной шине 3 стробирования устройства присутствует высо

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1979 |

|

SU822295A1 |

| ПИКОВЫЙ ДЕТЕКТОР | 2009 |

|

RU2409818C1 |

| Устройство для выделения модуля | 1981 |

|

SU1019460A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU780048A1 |

| Генератор импульсов | 1985 |

|

SU1378019A1 |

| Устройство для управления преобразователем переменного напряжения в постоянное | 1991 |

|

SU1793521A1 |

| Электрометрический преобразователь заряда | 1986 |

|

SU1448293A1 |

| Устройство выборки-хранения | 1990 |

|

SU1716571A1 |

| Аналоговое запоминающее устройство | 1983 |

|

SU1104587A1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

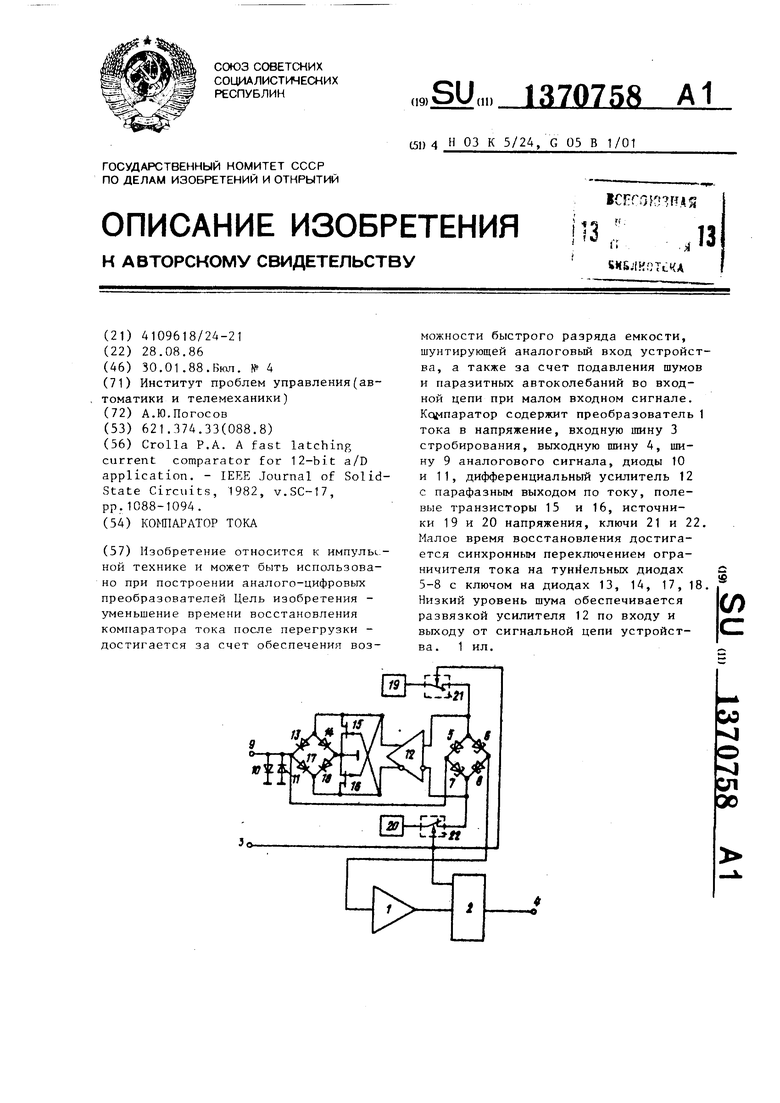

Изобретение относится к импулы..- ной технике и может быть использовано при построении аналого-цифровых преобразователей Цель изобретения - уменьшение времени восстановления компаратора тока после перегрузки - достигается за счет обеспечения возможности быстрого разряда емкости, шунтирующей аналоговый вход устройства, а также за счет подавления шумов и паразитных автоколебаний во входной цепи при малом входном сигнале. KqfinapaTop содержит преобразователь 1 тока в напряжение, входную шину 3 стробирования, выходную шину 4, шину 9 аналогового сигнала, диоды 10 и 11, дифференциальный усилитель 12 с парафазным выходом по току, полевые транзисторы 15 и 16, источники 1 9 и 20 напряжения, ключи 21 и 22. Малое время восстановления достигается синхронным переключением ограничителя тока на туннельных диодах 5-8 с ключом на диодах 13, 14, 17, 18. Низкий уровень шума обеспечивается развязкой усилителя 12 по входу и выходу от сигнальной цепи устройства. 1 ил. $ (Л

разряда емкости, шунтирующей аналого-Ю кий логический уровень, то источни- вый вход устройства, одновременно ки 19 и 20 напряжений отключены клю- с отключением тока от входа преобразователя тока в напряжение во время перегрузки, а также возможности почами 21 и 22 (нормально замкнутыми) от туннельных диодов 5-8, а информация с выхода преобразователя 1 тока

давления шумов и паразитных автоколе-15 в напряжение передается через триг

баний во входной цепи при малом входном сигнале.

На чертеже представлена структурная схема компаратора тока.

Компаратор тока содержит преобразователь 1 тока в напряжение, выход которого подключен к информационному входу триггера 2, соединенного входом синхронизацией и выходом соот- ветственно к входной шине 3 стробирования и выходной шине 4, четыре туннельных диода 5-8, соединенных между собой по мостовой схеме, один вывод первой диагонали мостовой схемы подключен к входу преобразоват -.я 1 тока в напряжение, второй вывод - с шиной 9 аналогового сигнала, подсодиненной через встречно-параллельно включенные первый и второй диоды 10 и 11 к ббщей шине, а выводы второй диагонали подключены к входам дифференциального усилителя 12 с па- рафазным выходом по току, прямой выход которого подключен к анодам третьего и четвертого диодов 13 и 14 стоку первого 15 и затвору второго 16 полевых транзисторов,инвернсный выход - к катодам пятого и шестого диодов 17 и 18, стоку второго 16 и затвору первого 15 полевых транзисторов, причем катод третьего и анод пятого диодов 13 и 17, катод первого 5 и анод третьего 7 туннельных диодов подключены к шине 9 аналогового сигнала, при этом катод четвертого 14 и анод шестого 18 диодов подключены к истокам обоих полевых транзисторов 15 и 16 и общей шине, в первый и второй источники 19 и 20 напряжения подсоединены соответственно через первый и второй ключи 21 и 22 к неинвертирующему и инвертирующему входам

кий логический уровень, то источни- ки 19 и 20 напряжений отключены клю-

чами 21 и 22 (нормально замкнутыми) от туннельных диодов 5-8, а информация с выхода преобразователя 1 тока

0

5

0

5

0

0

5

гер 2 на выходную шину устройства 4 и устройство работает в асинхронном режиме.

Если напряжение на входной шине 1 аналогового сигнала невелико, то рабочие точки туннельных диодов 5-8 находятся на первых восходящих ветвях из вольтамперных характеристик (ВАХ), дифференциальное сопротивление туннельных диодов невелико, весь ток с входной шины 1 аналогового сигнала поступает на вход преобразователя 1 тока в напряжение. В силу близости параметров туннельных дио- дов 5-8 мост сбалансирован, и дифференциальное напряжение между входами дифференциального усилителя 12 близко к нулю.При этом близки к нулю и выходные токи дифференциального усилителя 12. Полевые транзисторы 15 и 16 открыты и замыкают выходы усилителя 12 на общую шину устройства, предотвращая проникновение шумов и пульсаций из выходной цепи усилителя 12 во входную цепь устройства через емкости запертых диодов

13 и 17.

I

По мере увеличения напряжения на входной шине 9 аналогового сигнала рабочие точки туннельных диодов 5 и 8 (или 6 и 7 в зависимости от полярности входного сигнала) переходят, в область падающего участка ВАХ и далее скачком - в область впадины ВАХ. При этом входной ток преобразователя 1 тока в напряжение резко уменьшится (до значения тока впадины ВАХ туннельного диода) и перегрузка преобразователя 1 тока в напряжение предотвращается. Одновременно за счет скачкообразной разбалансиров- ки моста между входами усилителя 12 появляется сигнал перегрузки, причем более положительный потенциал сигнала перегрузки прикладыпается к неинвертирующему входу усилителя 12 не зависимо от знака напряжения на вход ной шине 9 аналогового сигнала.

Входные токи усилителя 12 отпирают диоды 13, 14, 17, 18, причем запирающиеся транзисторы 15 и 16 ускоряют этот процесс. Мост диодов 13, 14, 17, 18 быстро разряжает выходную емкость источника сигнала, подключенного к входной шине 9 аналогового сигнала, обеспечивая устройству малое время восстановления.

Когда в процессе восстановления после перегрузки напряжение на входной шине 9 аналогового сигнала падает примерно до удвоенного напряжения пика ВАХ туннельного диода, рабочие точки туннельных диодов 5 и 8 (или 6 и 7) переходят в область первой восходящей ветви ВАХ, мост туннельных диодов 5-8 подключает вход преобразователя 1 к входной шине 9 аналогового сигнала и одновременно балансируется. При этом исчезает входное напряжение усилителя 12, падают его выходные токи и начиают запираться диоды 13, 14, 17, 18. Процесс запирания ускоряется открывающимися транзисторами 15 и 16, что способствует уменьшению заряда переключения и предотвращает автоколебательные процессы. Окончательное восстановление устройства происходит по мере экспоненциального разряда входной емкости через входное сопротивление преобразователя 1 и диф-, ференциальное сопротивление моста туннельных диодов 5-8.

При поступлении сигнала низкого логического уровня на входную шину 3 стробирования устройства ключи 21 и 22 замыкаются, а напряжения от источников 19 и 20 запирают мост туннельных диодов 5-8, переводя рабочие точки всех четырех туннельных диодов 5-8 в область впадины ВАХ. При этом входной ток преобразователя 1 почти прекращается, а триггер 2 фиксирует входной сигнал преобразователя 1 в предыдущий момент времени. Одновременно открываются диоды 13,14,17,18. При значительных перегрузках устройства в действие вступают дополнительные ограничительные диоды 10 и 1 1 .

Таким образом, в предлагаемом компараторе тока малое время восста0

5

0

5

0

5

0

5

0

5

новления достигается синхронным переключением ограничителя тока на туннельных диодах 5-8 с коротящим ключом на диодах 13, 14, 17, 18, причем низкий уровень шума при малом напряжении на входной шине 9 аналогового сигнала обусловлен развязкой усилителя 12 по входу и выходу от сигнальной цепи устройства.

Формула изобретения

Компаратор тока, содержаш 1Й триггер, первый и второй диоды, включенные встречно-параллельно между шиной аналогового сигнала и общей шиной устройства,преобразователь тока в напряжение, выход которого соединен с информационным входом триггера, вход синхронизации и выход которого подключены соответственно к входной шине стробирования и выходной шине устройства, отличающий- с я тем, что, с целью уменьшения времени восстановления устройства после перегрузки, в него введены соединенные по мостовым схемам четыре тyf нeльныx диода, четыре диода, первый полевой транзистор с каналом п- типа, второй полевой транзистор с каналом р-типа, два ключа, два источника напряжения, дифференциальный усилитель с парафазным выходом по току, неинвертирующий вход которого подключен к анодам первого и второго туннельных диодов, инвертирующий вход - к катодам третьего и четвертого туннельных диодов, прямой выход - к анодам третьего и четвертого диодов, стоку первого и затвору второго полевых транзисторов, инверсный выход - к катодам пятого и шестого диодов, стоку второго и затвору первого полевых транзисторов, причем катод третьего и анод пятого диодов, катод первого и анод третьего туннельных диодов подключены к шине аналогового сигнала, катод второго и анод четвертого туннельных диодов соединены с входом преобразователя тока в напряжение, катод четвертого и анод шестого диодов подключены к истокам обоих полевых транзисторов и общей шине устройства, а первый и второй источники напряжения подсоединены соответственно через первый и второй ключи к неинвертирующим и инвертирующим вхо513707586

дам дифференциального усилителя, при- динены к входной шине строби чем управляющие входы ключей подсое- рования.

| Crolla Р.А | |||

| Способ гальванического снятия позолоты с серебряных изделий без заметного изменения их формы | 1923 |

|

SU12A1 |

| - IEEE Journal of Solid- State Circuits, 1982, v., pp.1088-1094. | |||

Авторы

Даты

1988-01-30—Публикация

1986-08-28—Подача