i

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПРОВЕРКИ ЭЛЕКТРОННОГО КОММУТАТОРА СИСТЕМЫ ЗАЖИГАНИЯ ДВИГАТЕЛЯ ВНУТРЕННЕГО СГОРАНИЯ | 1996 |

|

RU2105896C1 |

| Устройство для измерения температуры | 1987 |

|

SU1425472A1 |

| Переключатель | 1982 |

|

SU1081792A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ | 1996 |

|

RU2110144C1 |

| Электронный музыкальный звонок | 1988 |

|

SU1748176A1 |

| Электронное музыкальное устройство | 1988 |

|

SU1793459A1 |

| Генератор импульсов с изменяющейся частотой | 1987 |

|

SU1503060A1 |

| Тиристорная система зажигания | 1989 |

|

SU1710816A1 |

| Устройство для подавления дребезга контактов @ выключателей | 1988 |

|

SU1621155A1 |

| Устройство для генерации импульсов с постоянной и переменной скважностью | 1986 |

|

SU1348766A1 |

Изобретение может быть использовано для формирования сигналов управления при ограниченном числе информационных входов. Цель изобретения - расширение области применения и повышение достоверности функционирования устройства. Входное логическое устройство содержит инвертор 2, D-триггер 5, элемент ИЛИ-НЕ 9 и элементы II. Введение инверторов 10 и 12, RS-триггеров 13 и 14 и образование новых функциональных связей исключает необходимость в каких-либо дополнительных сигналах при подключении логического устройства к электронному устройству. Таким образом, обеспечивается уменьшение количества используемых выводов электронного устройства. 2 ил.

со

00

со ;

СХ) О5

Фиг.1

Изобретение относится к цифровым логическим устройствам и может использоваться для формирования сигналов управления при ограниченном числе информационных входов.

Целью изобретения является расширение области применения и повышение достоверности функционирования.

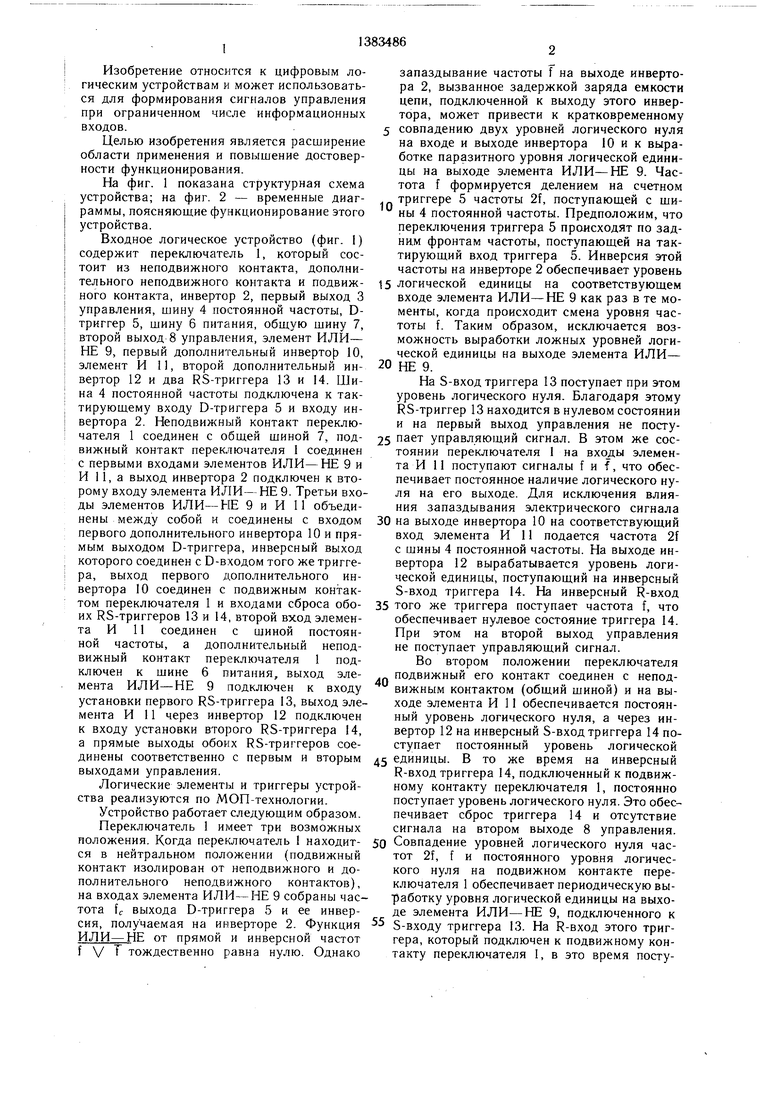

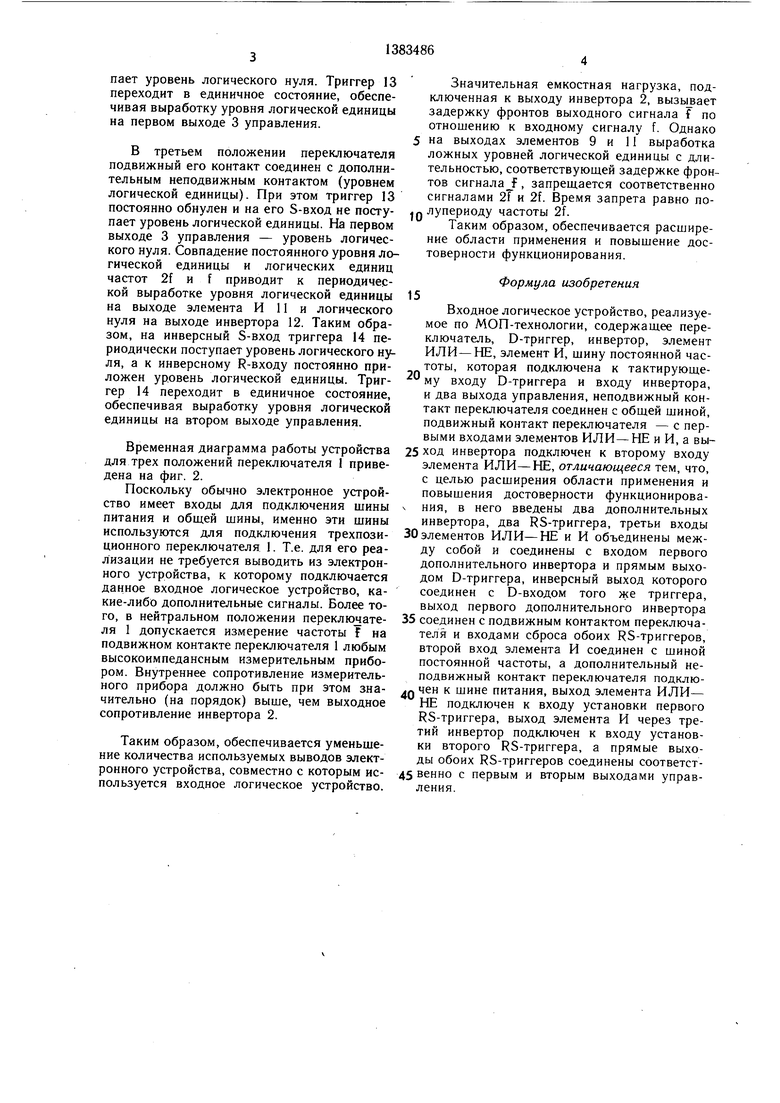

На фиг. 1 показана структурная схема устройства; на фиг. 2 - временные диаграммы, поясняюш,ие функционирование этого устройства.

Входное логическое устройство (фиг. 1) содержит переключатель 1, который состоит из неподвижного контакта, дополнительного неподвижного контакта и подвижного контакта, инвертор 2, первый выход 3 управления, шину 4 постоянной частоты, D- триггер 5, шину б питания, общую шину 7, второй выход 8 управления, элемент ИЛИ- НЕ 9, первый дополнительный инвертор 10, элемент И 11, второй дополнительный инвертор 12 и два RS-триггера 13 и 14. Шина 4 постоянной частоты подключена к так- тируюшему входу D-триггера 5 и входу инвертора 2. Неподвижный контакт переключателя 1 соединен с общей шиной 7, подвижный контакт переключателя 1 соединен с первыми входами элементов ИЛИ-НЕ 9 и И 11, а выход инвертора 2 подключен к второму входу элемента ИЛИ-НЕ 9. Третьи входы элементов ИЛИ-НЕ 9 и И 11 объединены между собой и соединены с входом первого дополнительного инвертора 10 и прямым выходом D-триггера, инверсный выход которого соединен с D-входом того же триггера, выход первого дополнительного инвертора 10 соединен с подвижным контактом переключателя 1 и входами сброса обоих RS-триггеров 13 и 14, второй вход элемента И 11 соединен с шиной постоянной частоты, а дополнительный неподвижный контакт переключателя 1 подключен к шине 6 питания, выход элемента ИЛИ-НЕ 9 подключен к входу установки первого RS-триггера 13, выход элемента И 11 через инвертор 12 подключен к входу установки второго RS-триггера 14, а прямые выходы обоих RS-триггеров соединены соответственно с первым и вторым выходами управления.

Логические элементы и триггеры устройства реализуются по МОП-технологии.

Устройство работает следующим образом.

Переключатель 1 имеет три возможных положения. Когда переютючатель 1 находится в нейтральном положении (подвижный контакт изолирован от неподвижного и дополнительного неподвижного контактов), на входах элемента ИЛИ-НЕ 9 собраны частота fc выхода D-триггера 5 и ее инверсия, получаемая на инверторе 2. Функция ИЛИ-НЕ от прямой и инверсной частот f V тождественно равна нулю. Однако

запаздывание частоты f на выходе инвертора 2, вызванное задержкой заряда емкости цепи, подключенной к выходу этого инвертора, может привести к кратковременному 5 совпадению двух уровней логического нуля на входе и выходе инвертора 10 и к выработке паразитного уровня логической единицы на выходе элемента ИЛИ-НЕ 9. Частота f формируется делением на счетном триггере 5 частоты 2f, поступающей с ши- ны 4 постоянной частоты. Предположим, что переключения триггера 5 происходят по задним фронтам частоты, поступающей на тактирующий вход триггера 5. Инверсия этой частоты на инверторе 2 обеспечивает уровень

5 логической единицы на соответствующем входе элемента ИЛИ-НЕ 9 как раз в те моменты, когда происходит смена уровня частоты f. Таким образом, исключается возможность выработки ложных уровней логической единицы на выходе элемента ИЛИ-

0 НЕ 9.

На S-вход триггера 13 поступает при этом уровень логического нуля. Благодаря этому RS-триггер 13 находится в нулевом состоянии и на первый выход управления не посту5 пает управляющий сигнал. В этом же состоянии переключателя 1 на входы элемента И II поступают сигналы f и f, что обеспечивает постоянное наличие логического нуля на его выходе. Для исключения влияния запаздывания электрического сигнала

0 на выходе инвертора 10 на соответствующий вход элемента И 11 подается частота 2f с щины 4 постоянной частоты. На выходе инвертора 12 вырабатывается уровень логической единицы, поступающий на инверсный S-вход триггера 14. На инверсный R-вход

5 того же триггера поступает частота f, что обеспечивает нулевое состояние триггера 14. При этом на второй выход управления не поступает управляющий сигнал.

Во втором положении переключателя подвижный его контакт соединен с неподвижным контактом (общий шиной) и на выходе элемента И 11 обеспечивается постоянный уровень логического нуля, а через инвертор 12 на инверсный S-вход триггера 14 поступает постоянный уровень логической

5 единицы. В то же время на инверсный R-вход триггера 14, подключенный к подвижному контакту переключателя 1, постоянно поступает уровень логического нуля. Это обеспечивает сброс триггера 14 и отсутствие сигнала на втором выходе 8 управления.

0 Совпадение уровней логического нуля частот 2f, f и постоянного уровня логического нуля на подвижном контакте переключателя 1 обеспечивает периодическую выработку уровня логической единицы на выходе элемента ИЛИ-НЕ 9, подключенного к

5 S-входу триггера 13. На R-вход этого триггера, который подключен к подвижному контакту переключателя I, в это время посту0

пает уровень логического нуля. Триггер 13 переходит в единичное состояние, обеспечивая выработку уровня логической единицы на первом выходе 3 управления.

В третьем положении переключателя подвижный его контакт соединен с дополнительным неподвижным контактом (уровнем логической единицы). При этом триггер 13 постоянно обнулен и на его S-вход не поступает уровень логической единицы. На первом выходе 3 управления - уровень логического нуля. Совпадение постоянного уровня логической единицы и логических единиц частот 2f и f приводит к периодической выработке уровня логической единицы на выходе элемента И 11 и логического нуля на выходе инвертора 12. Таким образом, на инверсный S-вход триггера 14 периодически поступает уровень логического нуля, а к инверсному R-входу постоянно приложен уровень логической единицы. Триггер 14 переходит в единичное состояние, обеспечивая выработку уровня логической единицы на втором выходе управления.

Временная диаграмма работы устройства для трех положений переключателя 1 приведена на фиг. 2.

Поскольку обычно электронное устройство имеет входы для подключения шины питания и общей шины, именно эти шины используются для подключения трехпози- ционного переключателя 1. Т.е. для его реализации не требуется выводить из электронного устройства, к которому подключается данное входное логическое устройство, какие-либо дополнительные сигналы. Более того, в нейтральном положении переключателя 1 допускается измерение частоты f на подвижном контакте переключателя 1 любым высокоимпедансным измерительным прибором. Внутреннее сопротивление измерительного прибора должно быть при этом значительно (на порядок) выше, чем выходное сопротивление инвертора 2.

Таким образом, обеспечивается уменьшение количества используемых выводов электронного устройства, совместно с которым используется входное логическое устройство.

Значительная емкостная нагрузка, подключенная к выходу инвертора 2, вызьшает задержку фронтов выходного сигнала f по отношению к входному сигналу f. Однако 5 на выходах элементов 9 и 11 выработка ложных уровней логической единицы с длительностью, соответствующей задержке фронтов сигнала,, запрещается соответственно сигналами 2f и 2f. Время запрета равно по- .длупериоду частоты 2f.

Таким образом, обеспечивается расширение области применения и повышение достоверности функционирования.

15

Формула изобретения

Входное логическое устройство, реализуемое по МОП-технологии, содержащее переключатель, D-триггер, инвертор, элемент ИЛИ-НЕ, элемент И, шину постоянной час- тоты, которая подключена к тактирующе му входу D-триггера и входу инвертора, и два выхода управления, неподвижный контакт переключателя соединен с общей шиной, подвижный контакт переключателя - с первыми входами элементов ИЛИ-НЕ и И, а вы25 ход инвертора подключен к второму входу элемента ИЛИ-НЕ, отличающееся тем, что, с целью расширения области применения и повышения достоверности функционировач ния, в него введены два дополнительных инвертора, два RS-триггера, третьи входы

30 элементов ИЛИ-НЕ и И объединены между собой и соединены с входом первого дополнительного инвертора и прямым выходом D-триггера, инверсный выход которого соединен с D-входом того же триггера, выход первого дополнительного инвертора

35 соединен с подвижным контактом переключателя и входами сброса обоих RS-триггероБ, второй вход элемента И соединен с шиной постоянной частоты, а дополнительный неподвижный контакт переключателя подклю л чен к шине питания, выход элемента ИЛИ- НЕ подключен к входу установки первого RS-триггера, выход элемента И через третий инвертор подключен к входу установки второго RS-триггера, а прямые выходы обоих RS-триггеров соединены соответст45 венно с первым и вторым выходами управления.

Переключатель 1 Переключатель Переключатель 1 д среднем положении 9 оерхнем полосе- 6 нижнем положении

Фиг. 2

| Патент США № 4030284, 1977 | |||

| Входное логическое устройство | 1984 |

|

SU1262723A1 |

Авторы

Даты

1988-03-23—Публикация

1986-07-28—Подача