сл

СП

о со

О Од

31503

рости изменения частоты формируемой импульсной последовательности, которая достигается введением задатчи- ка 13 скорости изменения частоты, который устанавливает на выходах блока 1 генераторов и задатчиков 1 1 и 12 максимальную и минимальную частоты. Частоты через переключатель А задают начальные значения суммирующего

интегратора 5. Граница изменения частотного диапазона определяется блоком 8 сравнения. Задатчик 14 режима работы через блок 9 управления устанавливает режим работы генератора. Генератор содержит также переключатели 2, 3, вычитающий интегратор 6, блок 7 сравнения, выходную ишну 10. 1 з.п. ф-лы, 3 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения отклонения сопротивления от заданного значения | 1986 |

|

SU1536322A1 |

| Устройство для управления фотоколориметрическим газоанализатором | 1982 |

|

SU1092468A1 |

| СПОСОБ ФОРМИРОВАНИЯ СИГНАЛОВ ТРЕВОЖНОГО ИЗВЕЩЕНИЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ (ВАРИАНТЫ) | 2007 |

|

RU2379759C2 |

| Измеритель скорости распространения ультразвуковых колебаний в материалах | 1985 |

|

SU1298643A1 |

| Устройство для регулирования температуры | 1983 |

|

SU1151932A1 |

| Цифровой измеритель температуры | 1985 |

|

SU1303849A1 |

| Интегрирующий аналого-цифровой преобразователь | 1989 |

|

SU1633493A1 |

| Устройство для пуска синхронной @ -фазной машины | 1990 |

|

SU1823119A1 |

| Устройство для регистрации информации | 1982 |

|

SU1167635A1 |

| Устройство для контроля влажности и зольности сыпучих материалов | 1983 |

|

SU1088475A1 |

Изобретение может быть использовано в цифровых имитаторах сигналов частотных датчиков, в качестве генератора частотной развертки панорамных анализаторов. Цель изобретения - расширение функциональных возможностей за счет задания диапазона и скорости изменения частоты формируемой импульсной последовательности, которая достигается введением задатчика 13 скорости изменения частоты, который устанавливает на выходах блока 1 генераторов и задатчиков 11,12 максимальную и минимальную частоты. Частоты через переключатель 4 задают начальные значения суммирующего интегратора 5. Граница изменения частотного диапазона определяется блоком 8 сравнения. Задатчик 14 режима работы через блок 9 управления устанавливает режим работы генератора. Генератор содержит также переключатели 2,3, вычитающий интегратор 6, блок 7 сравнения, выходную шину 10. 1 з.п. ф-лы. 3 ил.

Изобретение относится к импульсной технике и может быть использовано в цифровых имитаторах сигналов частотных датчиков в качестве генератора частотной развертки панорамных анализаторов спектра для проверки статистических и динамических свойств цифровых умножителей и сигнализато- ров частоты.

Целью изобретения является расширение функциональных возможностей за счет задания диапазона и скорости изменения частоты формируемой импульсной последовательности.

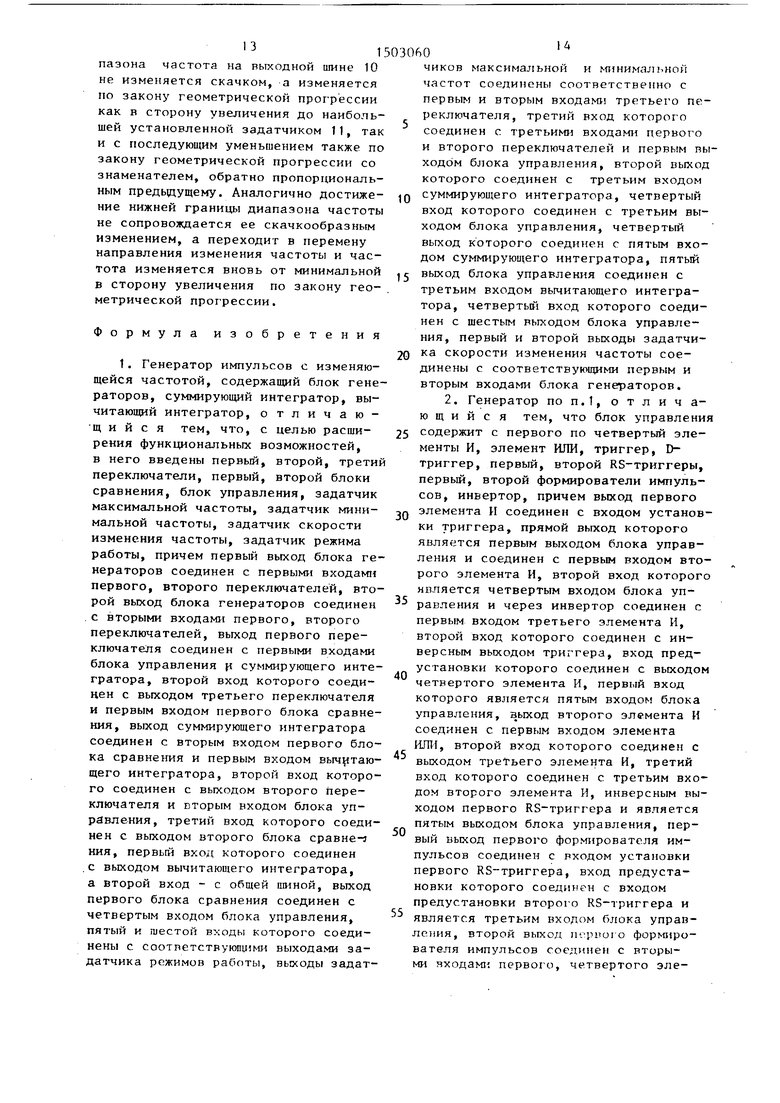

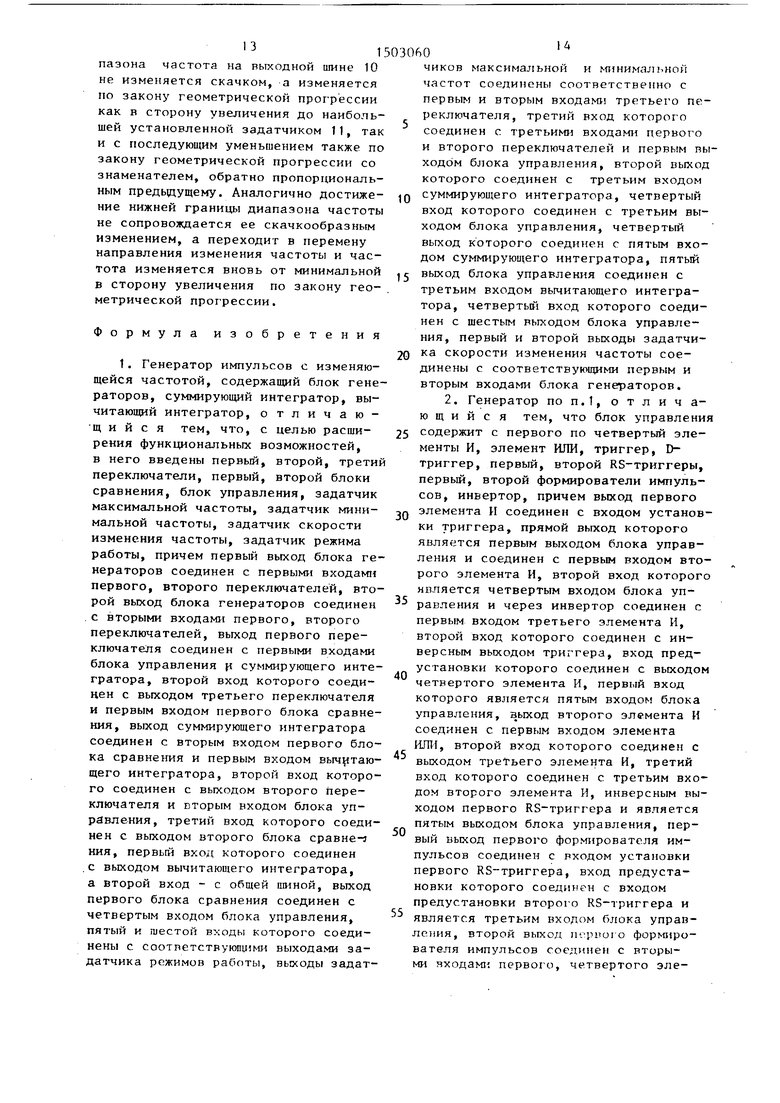

На фиг.1 представлена функциональная схема генератора импульсов с изменяющейся частотой на фиг.2 - временные диаграммы пояснякмцие его работу; на фиг.З - временные диаграммы выходной частоты для различных режимов работы.

Генератор содержит блок 1 генераторов, переключатели 2-4, суммирующий интегратор 5, вычитающий интегратор 6, блоки 7 и 8 сравнения, блок 9 управления, выходную шину 10, задат- чик 11 максимальной частоты, задатчик 12 минимальной частоты, задатчик 13 скорости изменения частоты, задатчик 14 режима работы.

Первый выход блока 1 генераторов соединен с первыми входами переключателей- 2 и 3. Второй выход блока 1 генераторов соединен с втopы и входами переключателей 2 и 3. Выход пере- ключателя 2 соединен с первыми входами блока 9 управления и суммирующего интегратора 5, второй вход которого соединен с выходом переключателя 4 и первым входом блока 8 сравнения. Выход суммирующего интегратора 5 соединен с вторым входом блока 8 сравнения и первым входом вычитающего интегратора 6,.второй вход которого соединен с выходом переключателя 3 и вторым входом блока 9 управления, третий вход которого соединен с выходом блока 7 сравнения, первый вход которого соединен с выходом вьтчитаю- щего интегратора 6, а второй вход - с общей шиной. Выход блока 8 сравнения соединен с четвертым входом блока 9 управления, пятый и шестой входы которого соединены с соответствующими выходами Задатчика 14 режима работы. Задатчики 11 и 12 максимальной и минимальной частот соединены соответственно с первым и вторым входами переключателя 4, третий вход которого соединен с третьими входами переключателей 2 и 3 и первым выходом блока 9 управления, второй выход которого соединен с третьим входом суммирующего интегратора 5, четвертый вход которого соединен с третьим выходом блока 9 управления, четвертый выход которого соединен с пятым входом суммирующего интегратора 5. Пятый выход блока 9 управления соединен с выходной шиной 10 и третьим входом вычитающего интегратора 6, четвертый вход которого соединен с шестым вькодом блока 9 управления. Первый и второй выходы задатчика 13 скоррсти изменени частоты соединены с соответствующими первым и вторым входами блока 1 генераторов .

Блок 1 генераторов содержит управляемые делители 15 и 16, источник 17 опорных сигналов. Первые входы управляемых делителей 15 и 16 являются соответственно первым и вторым входами, а их выходы - первым и вторым выходами блока 1 генераторов. Выход источника 17 опорных сиг налов соединён с вторыми входами управляемых делителей 15 и 16.

Блок 9 управления содержит элементы И 18-21, элемент ИЛИ 22, триггер 23, D-триггер 24, RS-триггеры 25 и 26, формирователи 27 и 28 импульсов, инвертор 29.

Выход элемента И 18 соединен с входом установки триггера 23, прямой выход которого является первым выходом блока 9 управления и соединен с первым входом элемента И 21, второй вход которого является четвертым входом блока 9 управления и через инвертор 29 соединен с первым входом элемента И 20, второй вход которого соединен с инверсным выходом триггера 23, вход предустановки которого соединен с выходом элемента И 19, первый вход которого является пятым

входом блока 9 управления. Выход эле-20 УРовней на выходах задатчика 14, вы- мента И 21 соединен с первым входом ходных сигналов задатчика 13 и выходэлемента ИЛИ 22, второй вход которого соединен с выходом элемента И 20, третий вход которого соединен с

30

35

40

третьим входом элемента И 21, инверс-25 о суммирующего интегратора 5 ра- ным выходом RS-триггера 26 и является пятым вь1ходом блока 9 управления. Первый выход формирователя 28 импульсов соединен с входом установки RS- триггера 26, вход предустановки которого соединен с входом предустановки RS-триггера 25 и является третьим входом блока 9 управления. Второй выход формирователя 28 импульсов соединен с вторыми входами элементов И 18 и 19, первым входом D-триггера 24 и является третьим выходом блока 9 управления. Первый вход формирователя 28 импульсов является вторым входом блока 9. управления, шестой выход которого является третьим выходом формирователя 28 импульсов, второй вход которого соединен с прямым выходом RS-триггера 26, Первый вход формирователя 27 импульсов является первым входом блока 9 управл - ния, а его второй вход соединен с прямым выходом RS-триггера 25, вход установки которого соединен с выходом формирователя 27 импульсов. Инверсный выход RS-триггера 25 является вторым выходом блока 9 управления. В. Выход элемента ИЛИ 22 соединен с вторым входом D-триггера 24.

Формирователи 27 и 28 импульсов имеют одинаковую функциональную схему и содержат счетчик 30 (31), дешифратор 32 (33) . Выходы счетчика 30 соединены с соответствующиыи входами ле45

вен Nj(t) (фиг.2а), а код вычитающего интегратора 6 равен N,(t)(фиг.2б).

Iо .

Если принять, что на первом выходе блока 9 управления, а следовательно, и на третьих входах переключателей 2-4 присутствует уровень логической 1, то на первый счетный вход сум- мируюя(его интегратора 5 поступает частота f, с первого выхода блока 1 генераторов через переключатель 2, а на второй счетный вход вычитающего интегратора 6 - пастота f с второго выхода блока 1 генераторов. При этом в последующие моменты времени код суммирующего интегратора 5 увеличивается с каждым икэтульсом входной частоты f, а код вычитающего интегратора 6 с каждым импульсом частоты f,. уменьшается на единицу и при достижении в нем нулевого значения кода, блок 7 сравнения (фиг.2а) формирует уровень логической 1 в момент времени tj. В этот момент код суммирующего интегратора 5 становится равным

50

N(t;) N(t,) + (t- to) f 1 (О.

55

Логическая 1 с выхода блока 7 сравнения, поступая на третий вход блока 9 управления, г апускает его. В ответ на этот и myльc блок 9 управления формирует на своем пятом выходе (фиг.2е) импульс, длительность q-,- которого обрагно пропорциональна частоте, поступавшей на второй

5

шифратора 32, выход которого является выходом формирователя 27 импульсов. Счетный вход счетчика 30 является первым входом формирователя 27 импульсов, второй вход которого является входом сброса счетчика 30.

Генератор работает следующим образом.

Первый вход D-триггера 24 является потенциальным входом предустановки, второй вход является тактовым входом этого триггера с переключением по фронту импульса. Информационный вход D-триггера 24 соединен с источником логической 1.

Работа устройства и характер изменения частоты на его выходной шине 10 определяются состояниями логических

ных сигналов эадатчиков П и 12 максимальной и минимальной частот.

Пусть в некоторый момент времени

0

5

0

5 о суммирующего интегратора 5 ра-

5

вен Nj(t) (фиг.2а), а код вычитающего интегратора 6 равен N,(t)(фиг.2б).

Iо .

Если принять, что на первом выходе блока 9 управления, а следовательно, и на третьих входах переключателей 2-4 присутствует уровень логической 1, то на первый счетный вход сум- мируюя(его интегратора 5 поступает частота f, с первого выхода блока 1 генераторов через переключатель 2, а на второй счетный вход вычитающего интегратора 6 - пастота f с второго выхода блока 1 генераторов. При этом в последующие моменты времени код суммирующего интегратора 5 увеличивается с каждым икэтульсом входной частоты f, а код вычитающего интегратора 6 с каждым импульсом частоты f,. уменьшается на единицу и при достижении в нем нулевого значения кода, блок 7 сравнения (фиг.2а) формирует уровень логической 1 в момент времени tj. В этот момент код суммирующего интегратора 5 становится равным

25 о суммирующего интегратора 5 ра-

50

N(t;) N(t,) + (t- to) f 1 (О.

25 о суммирующего интегратора 5 ра

55

Логическая 1 с выхода блока 7 сравнения, поступая на третий вход блока 9 управления, г апускает его. В ответ на этот и myльc блок 9 управления формирует на своем пятом выходе (фиг.2е) импульс, длительность q-,- которого обрагно пропорциональна частоте, поступавшей на второй

вход вьгчитаюп1его интегратора 6 (в данном случае f

2)

К

9-S

(2)

где К - постоянная величина.

Кроме того, в течение времени действия этого импульса блок 9 управления вырабатывает последовательно во времени импульсы на своих шестом и третьем выходах Ua.g и Uq., (фиг.2,г,д). Импульс с шестого выхода блока 9 управления производит запись содержимого суммирующего интегратора 5 в вычитающий интегратор 6 (t;) Ng(t;). Во время действия импульса с пятого выхода блока 9 управления на третьем входе вычитающего интегратора 6 блокируется про10

15

Таким образом, с момента времени t; + )-5 содержимое вычитающего интегратора 6 уменьшается под действием счетных импульсов, поступающих на его второй вход, до нуля к моменту времени

t,4, t + Ng(t;)/f., t; + + ,.5 N,(ti)/f,,,(4)

a код суммирующего интегратора 5 увеличивается с момента времени t, t; + и в момент времени t;, становится равным

Ny(t,4, ) (t;. - t,). f, - (t;,, - t; -C,.)-f, (5)

В результате состояние схемы возвращается к тому, какое она имела в момент времени t, с той лишь разницей, что содержимое суммирующего инхождение импульсов на его втором вхо- 20 тегратора 5 изменяется на новое значение. Аналогично для последующего цикла, заканчивакицегося в момент времени , можно записать

де. С появлением импульса на выходе блока 7 сравнения дополнительно на втором выходе блока 9 управления вы- рабатьгеается импульс, длительность с которого обратно пропорциональ- 25 на частоте, поступающей на второй вход суммирующего интегратора 5 (фиг.2ж), т.е. f,.

и-г

,t,)/f (6)

и

Ny(tuz t

1«-г

( i-l

Так как импульсы на выходной шине 10 устройства появляются в моменты времени t; , t;, , t ; ..., то от- нощение последующих интервалов времени между импульсами к предыдущим можно определить как

к

Ч-г

(3) 30

в течение всего времени действия этого импульса, поступающего на третий вход суммирующего интегратора 5, блокируется счетный вход последнего. Импульс с третьего выхода блока 9 управления поступает на четвертый вход (сброса) суммирующего интегратора 5 и переводит его в нулевое состояние.

выражая t, через t согласно (4),

„ (t i±i-J ± N5iti.i/b.r ti 3±i-jLl ll/fi. г,.5 - N,(t;)/fi

Из выражеугнй (2) и (3) получаем

f. .- И-г f- - .-s

q

,5 (4s - N,(ti)/f2-ff -Vz |fi l

V5 N,(t;y7f il

Ч

Таким образом, с момента времени t; + )-5 содержимое вычитающего интегратора 6 уменьшается под действием счетных импульсов, поступающих на его второй вход, до нуля к моменту времени

t,4, t + Ng(t;)/f., t; + + ,.5 N,(ti)/f,,,(4)

a код суммирующего интегратора 5 увеличивается с момента времени t, t; + и в момент времени t;, становится равным

Ny(t,4, ) (t;. - t,). f, - (t;,, - t; -C,.)-f, (5)

В результате состояние схемы вози-г

,t,)/f (6)

Ny(tuz t

1«-г

( i-l

Так как импульсы на выходной шине 10 устройства появляются в моменты времени t; , t;, , t ; ..., то от- нощение последующих интервалов времени между импульсами к предыдущим можно определить как

35

а - -J t,4, - t;

(8)

40

тогда, подставляя в выражение (8) значения моментов времени иэ (6) и (4) с учетом (1) и (5), имеем

имеем

Отскэда следует, что

Таким образом, интервалы времени между выходными импульсами генератора, а следовательно, и их частота изменяются по закону геометрической прогрессии со знаменателем, равным отношению частот на выходах блока 1 генераторов. Для смены направления изменения частоты на выходной шине 10 генератора достаточно изменить логический уровень сигнала управления на третьих входах переключателей 2 и 3. Требуемое значение скорости изменения выходной частоты задается с помощью задатчика 13, устанавливающего коэффициент деления управляемых делителей частоты 15 и 16 источника 17 опорных сигналов.

С помощью задатчиков 11 и 12 максимальной частоты устанавливают наибольшее и наименьшее значение частоты импульсов на выходной шине 10, при этом характер изменения частоты от максимальной к минимально и наоборот определяется комбинацией логических сигналов на выходах задатчика 14 режима.

Так, если на втором вькоде задатчика 14 режима установлен уровень логической 1, а на его первом выходе установлен уровень логического О, то частота на выходной шине 10 устройства изменяется от минимальной - ДО максимальной Рд,д,. после чего частота скачком изменяется до минимального значения F, установ- ,ленного задатчиком 12 минимальной- частоты, после этого выходная частот вновь плавно увеличивается по закону геометрической прогрессии до максимальной, установленной задатчиком 11 максимальной частоты, затем цикл изменения повторяется (фиг.36).

Если на втором выходе задатчика 1 режима установлен логический , а на его первом выходе - уровень лдги- ческой 1, то на выходной шине 10 генерируются импульсы, частота которых изменяется от наибольшей к наименьшей Fд,J по закону геометрической прогрессии, после чего частота скачком изменяется до максимальных значений F

Макс

затем цикл повторяется (фиг.За).

В том случае, когда на выходах задатчика 14 режима установлены нулевые уровни напряжений, выходная частота плавно изменяется по закону геометрической прогрессии как в сто

0

5

0

рону увеличения частоты, так и в сторону уменьшения частоты в Пределах заданных границ от ° мин установленных задатчиками 11 и 12 максимальной и минимальной частоты (фиг.Зв).

Рассмотрим работу устройства в первом режиме, когда на втором выходе задатчика 14 режима установлен уровень логической единицы, а на его первом выходе - уровень логического нуля. Этот режим обеспечивается при задании кода на первом выходе задатчика 13 меньше кода на его втором выходе, чем обеспечивается более высокая частота на втором выходе блока 1 генераторов по сравнению с частотой на его первом выходе, при этом на выходе задатчика 11 максимальной частоты устанавливают код периода этой максимальной частоты, а на выходе задатчика 12 минимальной частоты устанавливают код, соответствующий пе- 5 риоду заданной минимальной частоты, В этом режиме работа устройства ничем не отличается от рассмотренного выше до тех пор, пока код суммирующего счетчика 5 к концу очередного

0

5

0

5

0

5

интервала t не станет меньше кода, установленного на первом входе переключателя 4, при этом на первом выходе блока 9 управления присутствует уровень логической единицы и, следовательно, первый вход переключателя 4 скоммутирован с его выходом, а, следовательно, и с первым входом блока 8 сравнения, на второй вход которого Поступает, код суммирующего интегратора 5. Если после момента времени t этот код на втором входе блока 8 сравнения меньше, чем код на его первом входе, то на выход е блока 8 сравнения устанавливается код логической единицы (фиг.2к), который поступая на четвертый вход блока 9 управления открывает элемент И 21 для прохождения сигнала со второго выхода RS-триггера 26, который возникает в момент времени tj с приходом импульса блока 7 сравнения па третий вход блока 9 управления. С элемента И 21 сигнал через элемента ИЛИ 22, поступая на второй вход D- триггера 24, устанавливает на его выходе уровень логической единицы (фиг.2з), который своим фронтом, поступающим на второй (счетный) вход триггера 23, изменяет его состояние

так, что на его первом выходе устанавливается нулевой уровень (фиг,2и), а на его втором выходе - уровень логической 1. Таким образом, на первом выходе блока 9 управления появляется уровень логического О, который переводит переключатели 2-4 во второе состояние, когда их выходы ском- мутированы с вторыми входами. При этом на входе суммирующего интегратора 5 устанавливается код N минимальной частоты с выхода задатчика 12 минимальной частоты (фиг.2а). Так как на четвертом выходе блока 9 управления действует высокий уровень с выхода D-триггера 24, который, поступая на пятый вход (записи) суммирующего ин тегратора 5, записывает в него код минимальной частоты, импульс, появляющийся на шестом выходе блока 9 управления, поступая на четвертый вход вычитающего интегратора 6, производит запись в него кода минимальной частоты с выхода суммирукнцего ин- 25 12 минимальной частоты через пе- тегратора 5 (фиг.26). Очередной им- реключатель 4, на выходе блока 8

пульс, вьфабатываемый на втором выходе дешифратора 33, сбрасывает D-триггер 24 и через элемент И 18 устанавливает триггер 23 в исходное состояние, когда на его первом выходе установлен уровень логической 1. Кроме того, тот же импульс с второго выхода дешифратора 33, поступая через третий выход блока 9 управления на четвертый вход (сброса) суммирующего интегратора 5, устанавливает его в нулевое состояние. После того, как коды счетчиков 30 и 31 достигнут значения К соответствующего К импульсам, поступившим на их первые (счетные) входы через первый и второй входы блока 9 управления с выходов переключателей 2 и 3, на первых выходах дешифраторов 32 и 33 вырабатываются импульсы, устанавливающие RS-тригге- ры 25 и 26 в исходные состояния, после чего .код суммирующего интегратора 5 начинает изменяться от нулевого с каждым импульсом входной частоты, а код вычитающего интегратора 6 изменяется от максимального, соответствующего низшей частоте диапазона, с каждым импульсом последовательности, действующей на его втором входе. Далее работа устройства происходит в соответствии с ранее описанным.

Работа устройства на втором режиме, когда на втором выходе задатчика

5

0

14 режима установлен уровень логического нуля, а на его первом выходе - уровень логической единицы, аналогична рассмотренной. Отличие заключается в том, что в исходном состоянии на первом выходе блока 9 управления устанавливается уровень логического нуля, так как триггер 23 устанавливается в нулевое состояние уровнем логической единицы, поступающей с пятого входа блока 9 управления через элемент И 19 на третий вход (сброса) триггера 23 в момент формирования импульса на втором выходе де- щифратора 33. С завершением каждого цикла работы в момент времени t: коды суммирующего интегратора 5 уве личиваются от цикла к циклу (при этом выходная частота уменьшается) и при превышении кода суммирующего интегратора 5 кода минимальной час- тоты, поступающего на первый вход блока 8 сравнения с выхода задатчи

сравнения устанавливается уровень логического О, который, поступая через четвертый вход блока 9 ления после преобразования в

5

0

5

0

5

управ- логическую 1 инвертором 29, проходит через элемент И 20 в момент появле ния импульса на втором выходе RS- триггера 26, а следовательно, и через элемент ИЛИ 22 на второй вход D-триггера 24, взводя его, чем вызьгоается переключение триггера 23 в единичное состояние. При этом код минимальной частоты через суммирующий интегратор 5 переписьшается в вычитающий интегратор 6, что сопровождается скачкообразным увеличением частоты на выходной шине 10 устройства и последующим ее уменьшением по закону геометрической прогрессии.

Работа устройства в третьем режиме, который устанавливается при нулевых уровнях на выходах задатчика 14 режима аналогична рассмотренным с той лишь разницей, что формирование импульса на выходе D-триггера 24, приводящее, к изменению состояния триггера 23, не сопровождается его принудительной установкой под действием импульса с второго выхода дешифратора 33, так как элементы И 18 и 19 закрыты нулевыми уровнями, действующими на их первых входах. Это приводит к тому, что на границах диапазона частота на выходной шине 10 не изменяется скачком, а изменяется по закону геометрической прогрессии как в сторону увеличения до наибольшей установленной задатчиком 11, так и с последующим уменьшением также по закону геометрической прогрессии со знаменателем, обратно пропорциональным предьщущему. Аналогично достижение нижней границы диапазона частоты не сопровождается ее скачкообразным изменением, а переходит в перемену направления изменения частоты и частота изменяется вновь от минимальной в сторону увеличения по закону геометрической прогрессии.

Формула изобретения

.с вторыми входами первого, второго переключателей, выход первого переключателя соединен с первыми входами блока управления fi суммирующего интегратора, второй вход которого соединен с выходом третьего переключателя и первым входом первого блока сравнения, выход суммирующего интегратора соединен с вторым входом первого блока сравнения и первым входом вычртаю- щего интегратора, второй вход которого соединен с выходом второго Переключателя и вторым входом блока управления, третий вход которого соединен с выходом второго блока сравне-э ния, первый вход которого соединен

.с выходом вычитающего интегратора, а второй вход - с общей шиной, выход первого блока сравнения соединен с четвертым входом блока управления, пятый и шестой входы которого соединены с соотпетствуюпи)ми выходами за- датчика режимов работы, выходы задат

5

0

5

0

5

0

5

0

5

чиков максимальной и М1 нимялънои частот соединены соответственно с первым и вторым входами третьего переключателя, третий вход которого соединен с третьими входами первого и второго переключателей и первым пы- ходбм блока управления, второй выход которого соединен с третьим входом суммирующего интегратора, четвертый вход которого соединен с третьим выходом блока управления, четвертый выход которого соединен с пятым входом суммирующего интегратора, пятый выход блока управления соединен с третьим входом вычитающего интегратора, четвертый вход которого соединен с шестым выходом блока управления, первый и второй выходы задатчи- ка скорости изменения частоты соединены с соответствующими первым и вторым входами блока генераторов.

Н5

-1

i а

«.

и ft / 2

8t

Н

аК5|

п

жГЧт

п

t3

ff/

9

прямым выходом второго RS-триггера, вход установки которого соединен с выходом второго формирователя импульсов, инверсный выход второго RS-триггера является вторым выходом блока управления, выход элемента ИЛИ соединен с вторым входом D-триггера, первый вход первого элемента И является шестым входом блока управления, четвертый выход которого соединен с выходом D-триггера и тактовым входом триггера.

/,

1Z

Л

11

Xr

JL

IL

JL

гг

п п

п п п

фие.2

ffTiax

фие.З

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-08-23—Публикация

1987-04-22—Подача