00

00 со

01

.1

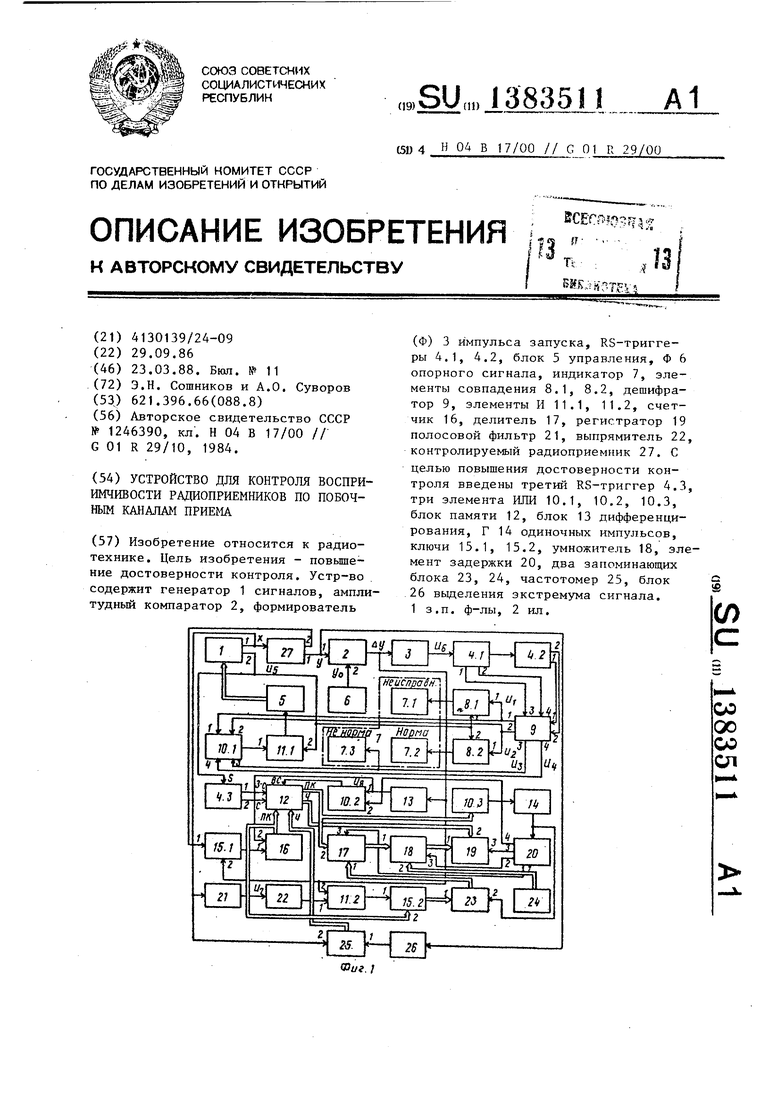

Изобретение относится к радиотехнике и может использоваться для автоматического измерения и контроля уровней восприимчивости радиоприем- Йиков по побочным каналам приема, а акже автоматического измерения и регистрации величины отклонения уровней восприимчивости радиоприемников йо побочным каналам приема от задан- Иой нормы и частот эт1;сх каналов, ; Цель изобретения- повышение досто ерности контроля. На фиг. 1 представлена структурная электрическая схема предлагаемог З стройства; на фиг. 2 - вариант выполнения блока памяти. I Устройство для контроля восприимчивости радиоприемников по побочным йаналам приема содержит генератор 1 (сигналов, амплитудный компаратор 2, (||ормирователь 3 импульса запуска, 1:ервый, второй и RS-триггеры .1, 4.2 и 4.3, блок 5 управления, формирователь 6 опорного сигнала, индикатор 7, состоящий из первого с|ветового табло 7.1 Неисправность, второго светового табло 7.2 Норма и третьего светового табло 7.3 Не норма, первый 8.1 и в торой 8.2 эле- М1енты совпадения, дешифратор 9, пер- в{.1й, второй и. третий элементы ИЛИ lb.1, 10.2 и 10.3, первый и второй элементы И 11.1 и 11.2, блок 12 памяти, блок 13 дифференцирования, гене- ратор 14 одиночных импульсов, первьш И| второй ключи 15.1 и 15.2, счетчик 16, делитель 17, умножитель 18, регистратор 19, элемент 20 задержки, по- лрсовой фильтр 21, вьшрямитель 22, П|ЕРВЫЙ и второй запоминающие блоки 2|3 и 24, частотомер 25, блок 26 вы- д|Еления экстремума сигнала, показан контролируемый радиоприемник 27.

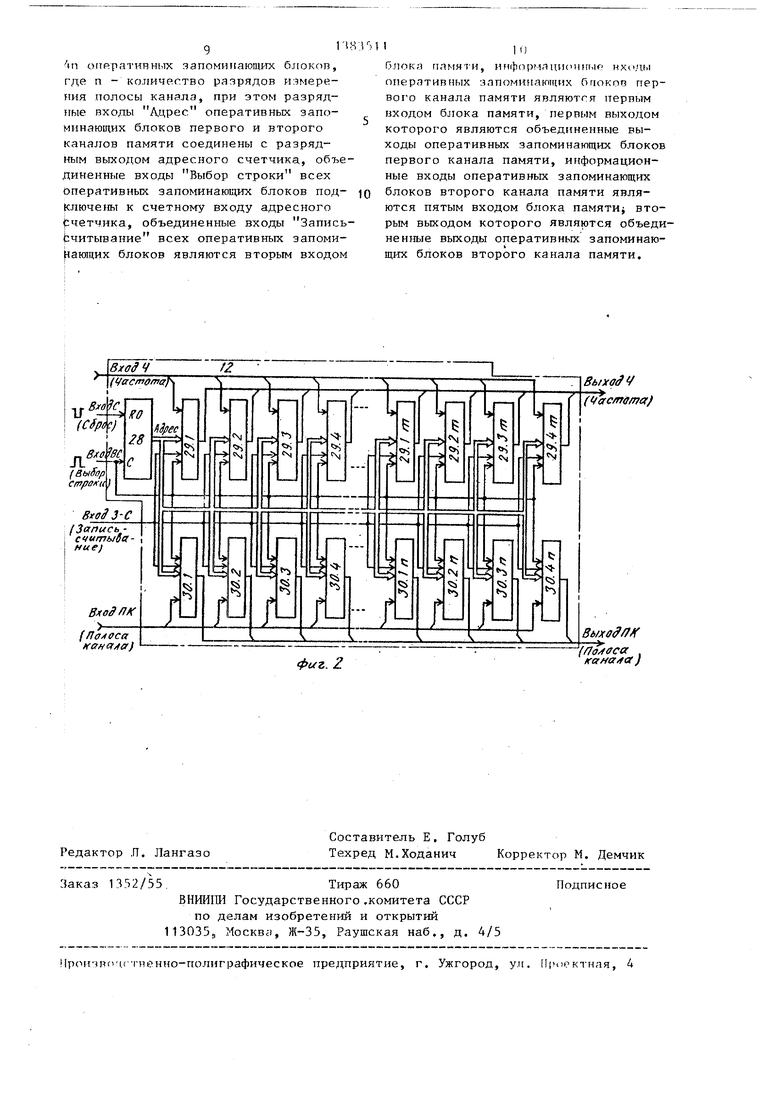

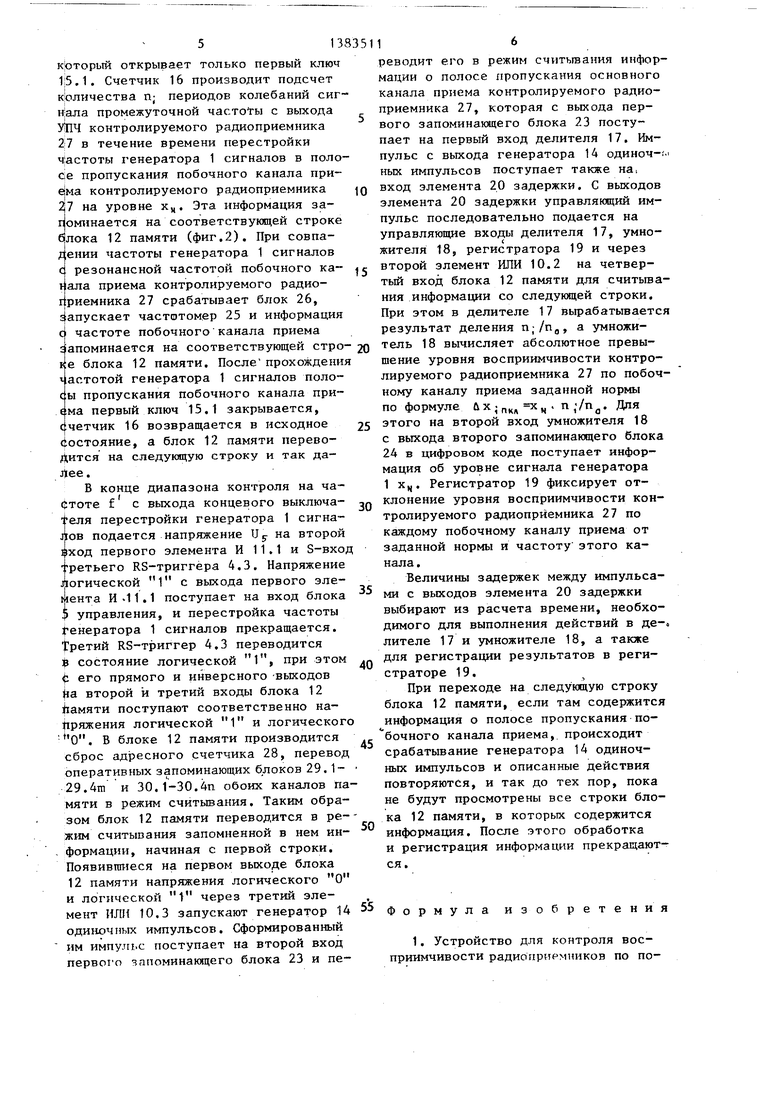

Блок 12 памяти содержит (фиг.2) адресный счетчик 28, 4т оперативных запоминающих блоков 29.1-29.4т, 4п оперативных запоминаюш,их блоков 30.1- 30.4п.

Устройство работает следующим образом.

В начальный момент времени третий RS-триггер 4.3 находится в исходном состоянии, на его прямом выходе вырабатывается напряжение логи чбского О, которое устанавливает блок 12 памяти в режим Запись (фиг.1).

с 5 0 5 0 5 0

5

0

5

11 2

Частоту f генератора 1 сигналов устанавливают на верхний предел диапазона контроля f . На вход контролируемого радиоприемника 27 подают сигнал уровня х, равный заданной норме х, который создает на выходе амплитудного детектора контролируем мого радиоприемника 27 сигнал у, сравниваемьй далее с уровнем опорного сигнала у, вьфабатываемым формирователем 6 опорного сигнала. Блок 5 управления осуществляет плавное изменение частоты генератора 1 сигналов в контролируемом диапазоне час- fft f - f .

В результате контроля установлено, что в случае неисправности ко«троли- руемого радиоприемника 27 на выходе амплитудного компаратора 2 разностный сигнал Д у у-Уо отрицательный () в контролируемом диапазоне частот f - f и формирователь 3 импульса запуска оказывается запертым. С его выхода на первьй RS-триггер 4.1 не поступит ни один импульс. Первый и второй RS-триггеры 4.1 и 4.2 находятся в исходном состоянии 1. При этом четыре выхода дешифратора 9 находятся в следующих состояниях: U,f О, U2 и 11 0. В конце диапазона контроля на частоте f с выхода концевого выключателя перестройки генератора 1 сигналов на вторые входы первого 8.1 и второго 8.2 элементов совпадения и первого элемента И 11.1 поступает напряжение U, срабатывает первый элемент 8.1 совпаде- ния,-включая индикатор 7, на первом световом табло 7.1 которого высвечивается сигнал Неисправность, второй и третий световые табло 7.2 и 7.3 не включаются. При этом на первом и втором входах первого элемента И 11.1 образуются напряжения логической 1, которые формируют на его выходе напряжение логической 1, и перестройка частоты генератора 1 сигналов сервоприводом блока 5 управления прекра- щается.

В случае удовлетворения восприимчивости побочных каналов приема установленной норме при совпадении частоты генератора 1 сих налов с частотой основного канала приема контролируемого радиоприемника 27 на выходе амплитудного компаратора 2 вырабатывается положительный сигнал ьу О, который, поступая на формирователь 3

импульса запуска, формирует один импульс остроконечной формы, переводя первый и второй RS-триггеры 4.1 и А.2 из состояния 1, 1 в состояни О, 1. При этом на выходах дешиф- ратора 9 и, V О, а . В конце диапазона контроля на частоте f с выхода кольцевого выключателя перестройки генератора 1 сигналов на вторые входы первого 8.1 и вто-. рого 8,2 элементов совпадения и первого элемента И 11.1 поступает напряжение Uy, второй элемент 8.2 совпадения срабатывает, включая индика тор 7, на втором световом табло 7.2 которого высвечивается сигнал Норма Первый и третий световые табло 7,1 и 7.3 не включаются, так как U, Uj О, Перестройка частоты генера- тора 1 сигналов сервоприводом блока 5 управления прекращается так же, как это было описано.

В случае неудовлетворения восприимчивости побочных каналов приема установленной норме на частоте основного канала приема контролируемого радиоприемника 27 и на частоте хотя бы одного побочного канала приема (или на частотах двух побочных ка- налов приема) уровень восприимчивости контролируемого радиоприемника 27, который не удовлетворяет установленной норме, на выходе амплитудного компаратора 2 дважды образуется сигнал , а на выходе формиро- вателя 3 импульса запуска вЫрабаты- ваются два импульса, переводящие первый и второй RS-триггеры 4.J и 4,2

II 4 II Illft

из исходного состояния 1, 1

состояние 1, О, в результате чего на выходах дешифратора 9 имеют место напряжения 11, 1 V О, а U,0, Напряжение U, поступает на индикатор 7, на третьем световом табло 7,3 которого высвечивается сигнал Не норма а перестройка частоты генератора 1 сигналов продолжается. При этом в случае совпадения частоты генератора 1 сигналов с нижней границей полосы пропускания основного канала приема контролируемого радиоприемника 27, на выходе полосового фильтра 21 вырабатьшается напряжение V-i, которое поступает через вы прямитель 22 на первый вход второго элемента И 11,2, на второй вход которого с выхода амплитудного компаратора 2 поступает напряжение лу. При

Q 0

5

0

0

5

этом на ныходе второго .элемента И 11.2 образуется напряжение логической 1, которое открЕлвает второй ключ 15.2. Напряжение &у с выхода амплитудного компаратора 2 открывает также первый ключ 15.1.

Счетчик 16 осуществляет подсчет количества п периодов колебаний сигнала промежуточной частоты с выхода промежуточной частоты (УПЧ) контролируемого радиоприемника 27 в течение времени перестройки частоты генератора 1 сигналов в полосе пропускания основного канала приема контролируемого радиоприемника 27 на уровне Хм. Эта информация с выхода счетчика 16 поступает на вход Полоса канала блока 12 памяти и через открытый второй ключ 15.2 на вход первого запоминающего блока 23. Счетчик 16 и первый запоминающий блок 23 при этом находятся в режиме записи информации. При совпадении частоты генератора 1 сигналов с резонансной частотой основного канала приема контролируемого радиоприемника 27 на выходе блока 26 вырабатьшается импульс, который запускает частотомер 25 для измерения частоты основного канала приема контролируемого радиоприемника 27. Эта информация с выхода частотомера 25 поступает на первый вход блока 12 памяти и запоминается в нем.

При совпадении частоты генератора 1 сигналов с верхней границей полосы пропускания основного канала приема контролируемого радиоприемника 27 на уровне x,j на выходе амплитудного компаратора 2 напряжение Лу становится равным логическому О, первьй и второй ключи 15.1 и 15.2 закрьгаают- ся, а задний фронт напряжения ду с выхода амплитудного компаратора 2 дифференцируется блоком 13, Импульс Ug с выхода блока 13 дифференцирования возвращает счетчик 16 в исходное состояние, а через второй элемент ИЛИ 10,2 переводит блок 12 памяти на следукяцую строку для регистрации информации о частоте и полосе пропускания следующего канала приема контролируемого радиоприемника 27.

При совпадении частоты генератора 1 сигналов с нижней границей полосы пропускания побочного канала приема контролируемого радиоприемника 27 на выходе амплитудного компарато{ а 2 также вырабатывается сигнал .

513

который открывает только первый ключ 1:5.1. Счетчик 16 производит подсчет количества п; периодов колебаний сиг iijana промежуточной частоты с выхода контролируемого радиоприемника 27 в течение времени перестройки ч;астоты генератора 1 сигналов в полосе пропускания побочного канала при- е|ма контролируемого радиоприемника 27 на уровне Хц. Эта информация запоминается на соответствующей строке блока 12 памяти (фиг.2). При совпа- р,ент1 частоты генератора 1 сигналов с резонансной частотой побочного ка- нала приема контролируемого радио- гриемника 27 срабатывает блок 26, Запускает частотомер 25 и информация с частоте побочного канала приема 21апоминается на соответствующей стро в:е блока 12 памяти. После прохождени частотой генератора 1 сигналов полосы пропускания побочного канала при- eiMa первый ключ 15.1 закрывается, счетчик 16 возвращается в исходное Достояние, а блок 12 памяти переводится на следующую строку и так да- Лее.

В конце диапазона контроля на ча- Стоте f с вькода концевого выключа- перестройки генератора 1 сигналов подается напряжение Ug на второй нход первого элемента И 11.1 и S-вхо ретьего RS-триггера 4.3. Напряжение логической 1 с выхода первого элемента И «11.1 поступает на вход блока 5 управления, и перестройка частоты Генератора 1 сигналов прекращается. 1ретий RS-триггер 4.3 переводится S состояние логической 1, при этом его прямого и инверсного выходов ifia второй и третий входы блока 12 Памяти поступают соответственно на- (1ряжения логической 1 и логическог . В блоке 12 памяти производится сброс адресного счетчика 28, перевод оперативных запоминающих блоков 29.1- 29.4т и 30. 1-30.4п. обоих каналов памяти в режим считьюания. Таким образом блок 12 памяти переводится в режим считывания запомненной в нем информации, начиная с первой строки. Появившиеся на первом выходе блока 12 памяти напряжения логического О и логической V через третий элемент ИЛИ 10.3 запускают генератор 14 ОДИ1ЮЧНЫХ импульсов. Сформированный им импульс поступает на второй вход первого запоминающего блока 23 и пе-

Q с 0 5

п Q 5

5

116

реводит его в режим считывания информации о полосе пропускания основного канала приема контролируемого радиоприемника 27, которая с выхода первого запоминакяцего блока 23 поступает на первый вход делителя 17. Импульс с выхода генератора 14 одиноч-;. ных импульсов поступает также на, вход элемента 20 задержки. С выходов элемента 20 задержки управляющий импульс последовательно подается на управляющие входы делителя 17, умножителя 18, регистратора 19 и через второй элемент ИЛИ 10.2 на четвертый вход блока 12 памяти для считьгаа- ния информации со следующей строки. При этом в делителе 17 вырабатывается результат деления п;/Па, а умножитель 18 вычисляет абсолютное превышение уровня восприимчивости контролируемого радиоприемника 27 по побочному каналу приема заданной нормы по формуле . п /Пд. Для этого на второй вход умножителя 18 с выхода второго запоминающего блока 24 в цифровом коде поступает информация об уровне сигнала генератора 1 х. Регистратор 19 фиксирует отклонение уровня восприимчивости контролируемого радиоприемника 27 по каждому побочному каналу приема от заданной нормы и частоту этого канала .

Величины задержек между импульсами с выходов элемента 20 задержки выбирают из расчета времени, необходимого для выполнения действий в де-« лителе 17 и умножителе 18, а также для регистрации результатов в регистраторе 19.

При переходе на следующую строку блока 12 памяти, если там содержится информация о полосе пропускания побочного канала приема, происходит срабатывание генератора 14 одиночных импульсов и описанные действия повторяются, и так до тех пор, пока не будут просмотрены все строки блока 12 памяти, в которых содержится информация. После этого обработка и регистрация информации прекращаются.

Формула изобретения

1. Устройство для контроля восприимчивости радиоПрирмииков по по113

бочным каналам приема, содержащее дешифратор, формирователь опорного сигнала, последовательно соединенные блок управления и генератор сигналов, информационный выход которого является входом контролируемого радиоприемника, первый элемент И, последовательно соединенные амплитудный компаратор, первый вход кото{)ого яв- ляется информационным выходом контролируемого радиоприемника, а второй вход соединен с выходом формирователя опорного сигнала, формирователь импульса запуска, первый RS-триггер и второй RS-триггер, первый и второй выходы которого соединены с первым и вторым входами дешифратора, третий и четвертый входы которого соединены с вторым и третьим выходами первого RS-триггера, индикатор, первый и второй элементы совпадения, первые входы которых соединены соответственно с первым и вторым выходами дешифратора, а выходы первого и второго элементов совпадения соединены соответственно с первым и вторым входами индикатора, третий вход которого соединен с третьим выходом дешифратора, вторые входы первого и второго элементов совпадения соединены с выходом концевого выключателя генератора сигналов, счетчик, делитель, регистратор, последовательно соединенные полосовой фильтр, вход которого соединен с информационным выходом генератора сигналов, выпрямитель и второй элемент И, второй вход которого соединен с выходом амплитудного компаратора, отличающееся тем, что, с целью повышения достоверности контроля, введены первый элемент ИЛИ, первый, второй, третий и четвертый входы и выход которого соединены соответственно с первым, вторым, третьим и четвертым выходами дешифратора и первым входом элемента И, второй вход и выход которого соединены соответственно с выходом концевого выключателя генератора сигналов и входом блока управ- ления, первый ключ, первый и второй входы и выход которого соединены соответственно с выходом промежуточной частоты контролируемого радиоприемника, с выходом амплитудного компара- тора и первым входом счетчика, блок памяти, последовательно соединенные блок выделения экстремума сигнала.

д 0 5 « Р 5

0

5

1 8

вход которого соединен с первым входом амплитудного компаратора, и частотомер, второй вход и выход которого соединены соответственно с информационным выходом генератора сигналов и первым входом блока памяти, третий RS-триггер, вход и первый и второй выходы которого соединены соответственно с выходом концевого выключателя генератора сигналов и вторым и третьим входами блока памяти, последовательно соединенные блок дифференцирования, вход которого соединен с выходом амплитудного компаратора, и второй элемент ИЛИ, выход которого подключен к четвертому вхо-- ду блока памяти, умножитель, последовательно соединенные третий элемент ИЛИ, вход которого соединен с первым выходом блока памяти, генератор одиночных импульсов и элемент задержки, первый, второй, третий и четвертый выходы которого соединены соответственно с первым входом делителя, с первым входом умножителя, с первым входом регистратора и вторым входом второго элемента ИЛИ, первый вход которого соединен с вторым входом счетчика, последовательно соединенные второй ключ, первый вход которого соединен с выходом второго элемента И, и первый запоминающий блок, второй вход и выход которого соединены соответственно с выходом генератора одиночных импульсов и вторым входом делителя, третий вход которого соединен с первым выходом блока памяти, второй выход которого под- клктаен к второму входу регистратора, третий вход которого соединен с выходом умножителя, второй вход которого соединен с выходом делителя, второй запоминающий блок, выход которого подключен к третьему входу умножителя, выход счетчика подключен It пятому входу блока памяти и второму входу второго ключа.

.1

2. Устройство по п. 1, отличающееся тем, что блок памяти содержит адресный счетчик, счетный вход и вход Сброс которого являются соответственно четвертым и третьим входами блока памяти, и два канала памяти, первый из которых содержит 4т оперативных запоминающих блоков,где m - количество разрядов измерения частоты, а второй содержит,

gП8

m огткратнвных запоминающих блоков, где п - количество разрядов измерения полосы канала, при этом разрядные входы Лцрес оперативных запо- минающих блоков первого и второго каналов памяти соединены с разрядным выходом адресного счетчика, объединенные входы Выбор строки всех оперативных запоминающих блоков под- Ключены к счетному входу адресного учетчика, объединенные входы Запись- Ьчитывание всех оперативных запоми- Йаклцих блоков являются вторым входом

10

блока памяти, информлцисняьк нходы оперативных запоминающих бгюког пер- вог о канала памяти являются первым входом блока памяти, первым выходом которого являются объединенные выходы оперативных запоминающих блоков первого канала памяти, информационные входы оперативных запоминающих блоков второго канала памяти являются пятым входом блока памяти вторым выходом которого являются объединенные выходы оперативных запоминающих блоков второго канала памяти.

Изобретение относится к радиотехнике. Цель изобретения - повьппе- ние достоверности контроля. Устр-во . содержит генератор 1 сигналов, амплитудный компаратор 2, формирователь (Ф) 3 импульса запуска, RS-тригге- ры 4.1, 4.2, блок 5 управления, Ф 6 опорного сигнала, индикатор 7, элементы совпадения 8.1, 8.2, дешифратор 9, элементы И 11.1, 11.2, счетчик 16, делитель 17, регистратор 19 полосовой фильтр 21, выпрямитель 22, контролируемый радиоприемник 27. С целью повышения достоверности контроля введены третий RS-триггер 4.3, три элемента ИЛИ 10.1, 10.2, 10.3, блок памяти 12, блок 13 дифференцирования, Г 14 одиночных импульсов, ключи 15.1, 15.2, умножитель 18, элемент задержки 20, два запоминающих блока 23, 24, частотомер 25, блок 26 выделения экстремума сигнала. 1 3.п. ф-лы, 2 ил. (Л

| Устройство для контроля чувствительности побочных каналов в радиоприемниках | 1984 |

|

SU1246390A2 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1988-03-23—Публикация

1986-09-29—Подача