(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Коммутатор напряжений | 1988 |

|

SU1524168A1 |

| Многоканальный коммутатор | 1985 |

|

SU1246362A1 |

| Ключевой элемент | 1986 |

|

SU1406768A1 |

| Ключ на МДП-транзисторе | 1986 |

|

SU1610597A1 |

| Аналоговый ключ | 1986 |

|

SU1406767A1 |

| Устройство преобразования уровней сигналов на КМДП-транзисторах | 1988 |

|

SU1506543A1 |

| Формирователь импульсов с преобразованием уровней сигналов | 1985 |

|

SU1378030A1 |

| Ключевой элемент | 1984 |

|

SU1202048A1 |

| Формирователь импульсов на МДП-транзисторах | 1985 |

|

SU1569973A1 |

| ГЕНЕРАТОР ТЕСТОВЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 1990 |

|

RU2034399C1 |

Изобретение относится к импульсной технике. Аналоговый переключатель содержит КМДП-ключ 1, состоящий из ВДП-транзисторов 2, 3 с каналами разного типа проводимости, формирователь 5 напряжения, состоящий из резисторов 6-10, МДП-транзисторов 11-13 р-типа, МДП- транзисторов 14-16 п-типа и диодов 17, 18, устройство 4 управления, состоящее из КМДП-инверторов 27, 28, ЩП-тpaнзиcтopoв 29-31, управляющую шину 32 шины 33, 34 питания, выходные шины 20, 25, 26, входную шину 19, общую шину 24, Аналоговый переключатель имеет расширенный диапазон коммутируемых напряжений при сохранении амплитуды управляющих напряжений К ЩП-ключа, 1 з.п. ф-лы, 1 ил.

rCLCrLEri-Cri

TJg TJ;

СА:

00

ел ю

00 00

Изобретение относится к импульсной технике и может бытьiиспользовано в устройствах электронной коммутации аналоговых сигналов, в измеритель ных системах и системах передачи данных .

Цель изобретения - расширение диапазона коммутируемых напряжений при сохранении амплитуды управляющих на- пряжений КМДП-ключа путем введения управляемого аналоговым сигналом формирователя напряжения, содержащего шесть МДП-транзисторов, пять резисторов и два диода, напряжение на выходных шинах которого регулируется в зависимости от величины и знака аналогового сигнала и используется как напряжение питания устройства управления КМДП- ключом, в результате чего на управляющие клеммы устройства управления подаются несимметричные потенциалы, обеспечивающие нормальную работу КМДП-ключа в открытом и закрытом состояниях в большем диапазоне аналоговых сигналов при одной и той же максимальной разности потенциалов на управляющих клеммах.

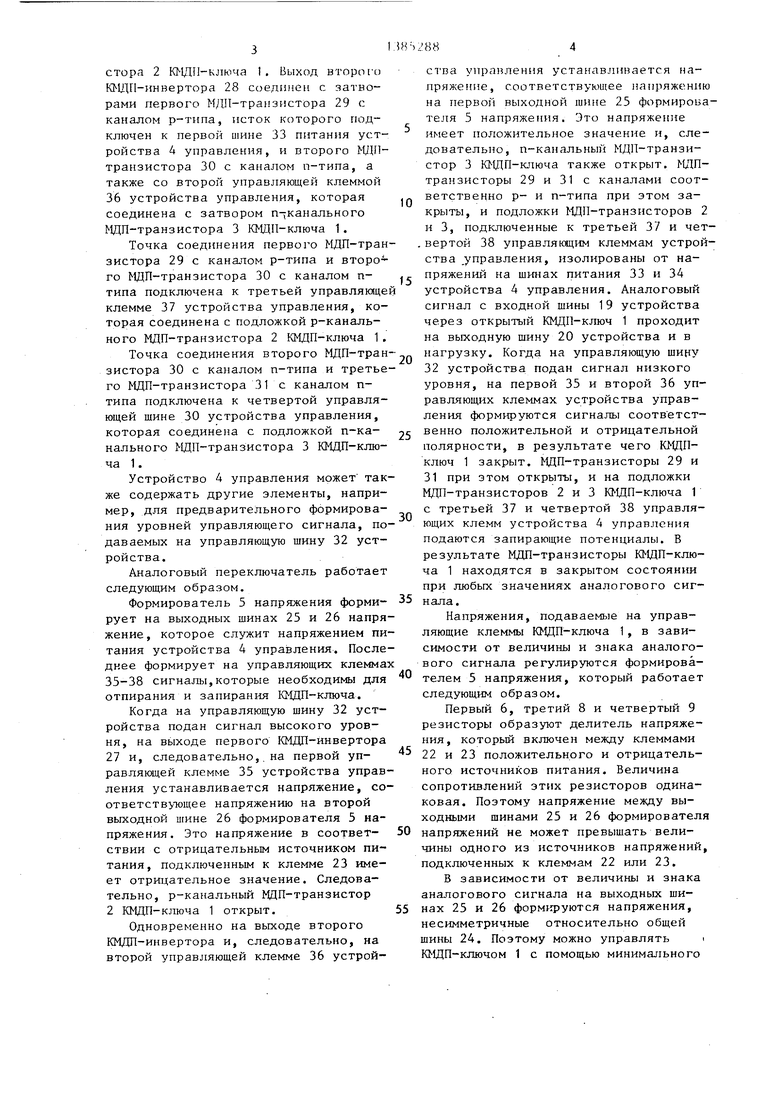

На чертеже приведена принципиальная схема устройства.

Аналоговый переключатель содержит КМДП-ключ 1, состоящий из двух МДП- транзисторов 2 и 3 с каналами разного типа проводимости, устройство 4 управления и формирователь 5 напряжений.

Формирователь 5 напряжений состоит из пяти резисторов 6-10, трех ЩП транзисторов р-типа 11-13, трех ВДП- транзисторов п-типа 14-16 и двух диодов 17 и 18.

Разноименные токовые электроды МДП-транзисторов 2 и 3 КМДП-ключа 1 объединены и подключены соответственно к входной 19 и выходной 20 шинам устройства.

Управляющая клемма 21 формирователя 5 напряжения соединена с входной шиной 19 устройства. Клемма 22 положительного источника питания подключена к первым выводам первого 6 и второго 7 резисторов, истоку и подложке первого МДП-транзистора 11 р- типа, а клемма 23 отрицательного источника питания подключена к первым вьюодам четвертого 9 и пятого 1.0 ре- зисторов, истоку и подложке второго МДП-транзистора 15 п-типа.

Истоки и подложки второго 12 и третьего 13 МДП-транзисторов p-rtina.

-

Q 5 0 5

0

.Q

5

п г

5

а также первого 14 и третьего 16 МДП-транзисторов, п-типа подключены к общей шине 14 устройства.

Второй вывод второго резистора 7 соединен с затвором первого МДП-транзистора 11 р-типа и стоком первого МДП-транзистора 14 п-типа, а второй вывод пятого резистора 10 соединен с затвором второго МДП-транзистора 15 п-типа и стоком третьего МДП-транзистора 13 р-типа.

Сток первого МДП-транзистора 11 р-типа соединен с общей точкой первого 6 и третьего 8 резисторов и подключен к первой выходной шине 25 формирователя 5 напряжения. Сток второго МДП-транзистора 15 п-типа соединен с общей точкой третьего 8 и четвертого 9 резисторов и подключен к второй выходной шине 26 формирователя 5 напряжения.

Катод первого диода 17, затвор первого МДП-транзистора 14 п-типа и сток второго МДП-транзистора 12 р-типа объединены. Анод второго диода 18, затвор третьего МДП-транзистора 13 и сток третьего МДП-транзистора 16 п-типа также объединены.

Анод и катод соответственно первого 17 и второго 18 диодов, а также затворы второго МДП-транзистора 12 р-типа и третьего МДП-транзистора 16 п-типа объединены и подключены к управляющей клемме.21 формирователя 5 напряжений.

Устройство 4 управления содержит первый 27 и второй 28 КМДП-инверто- ры и три МДП-транзистора 29-31. Вход первого КМДП-инвертора 27, являкяций- ся входом устройства управления, подключен к управлякщей шине 32 устройства. КМДП-инверторы 27 и 28 и три последовательно соединенные МДП-транзистора 29-31 включены между первой 33 и второй 34 шинами питания устройства 4 управления, которые подключены соответственно к первой 25 и второй 26 выходным шинам формирователя

5 напряжения.

I

Выход первого КМДП-инвертора 27

подключен к входу второго КМДП-инвертора 28, затвору третьего МДП-транзистора 31 с каналом п-типа, исток которого подключен к второй шине 34 питания устройства управления и к первой управляющей клемме 35 устройства управления, которая соединена с затвором р-канального МДП-транзи

стора 2 №ЩП-ключа 1 . Выход второго га ЩП-янвертора 28 соединен с затворами первого МДИ-траыэистора 29 с каналом р-типа, исток которого подключен к первой шине 33 питания устройства 4 управления, и второго ШДИ- транзистора 30 с каналом п-типа, а также со второй управляющей клеммой 36 устройства управления, которая соединена с затвором п-;канального ЬЩП-транзистора 3 КМДП-ключа 1.

Точка соединения первого МДП-тран зистора 29 с каналом р-типа и второго МДП-транзистора 30 с каналом п- типа подключена к третьей управлякще клемме 37 устройства управления, которая соединена с подложкой р-каналь- ного МДП-транзистора 2 КМДП-ключа 1.

Точка соединения второго МДП-транзистора 30 с каналом п-типа и третьего МДП-транзистора 31с каналом п- типа подключена к четвертой управляющей шине 30 устройства управления, которая соединена с подложкой п-ка

нального ЩП-транзистора 3 КМДП-ключа 1.

Устройство 4 управления может также содержать другие элементы, например, для предварительного формирования уровней управляющего сигнала, подаваемых на управляющую шину 32 устройства.

Аналоговый переключатель работает следующим образом.

25

30

ства управления ycTaHaBjniBaeTCH напряжение, соответствующее напряжени на первой выходной щине 25 формиров теля 5 напряжения. Это напряжение имеет положительное значение и, сле довательно, п-канальный МДП-транзи- стор 3 Ю-ЩП-ключа также открыт. МДП транзисторы 29 и 31 с каналами соот ветственно р- и п-типа при этом закрыты, и подложки МДП-транзисторов и 3, подключенные к третьей 37 и че . вертой 38 управляЕоцим клеммам ycTpo ства управления, изолированы от напряжений на шинах питания 33 и 34 устройства 4 управления. Аналоговый сигнал с входной шины 19 устройства через открытый КМДП-ключ 1 проходит на выходную шину 20 устройства и в нагрузку. Когда на управляющую шинУ 32 устройства подан сигнал низкого уровня, на первой 35 и второй 36 управляющих клеммах устройства управления форм1 фуются сигналы соотв етст- венно положительной и отрицательной полярности, в результате чего КМДП- ключ 1 закрыт. МДП-транзисторы 29 и 31 при этом открыты, и на подложки МДП-транзисторов 2 и 3 Ю-ЩП-ключа 1 с третьей 37 и четвертой 38 управляющих клемм устройства 4 управления подаются запирающие потенциалы. В результате МДП-транзисторы КМДП-ключа 1 находятся в закрытом состоянии при любых значениях аналогового сигФормирователь 5 напряжения форми- 35 нала. рует на выходных шинах 25 и 26 напря- Напряжения, подаваемые на управжение, которое служит напряжением питания устройства 4 управления. Последнее формирует на управляющих клеммах 35-38 сигналы,которые необходимы для отпирания и запирания КМДП-ключа.

Когда на управляющую шину 32 устройства подан сигнал высокого уровня, на выходе первого КМДП-инвертора 27 и, следовательно,, на первой уп- равлякщер клемме 35 устройства управления устанавливается напряжение, соответствующее напряжению на второй выходной игине 26 формирователя 5 напряжения. Это напряжение в соответствии с отрицательным источником питания, подключенным к клемме 23 имеет отрицательное значение. Следовательно, р-канальный МДП-транзистор 2 КМДП-ключа 1 открыт.

Одновременно на выходе второго КМДП-инвертора и, следовательно, на второй управляющей клемме 36 устрой0

0

5

0

ства управления ycTaHaBjniBaeTCH напряжение, соответствующее напряжению на первой выходной щине 25 формирователя 5 напряжения. Это напряжение имеет положительное значение и, следовательно, п-канальный МДП-транзи- стор 3 Ю-ЩП-ключа также открыт. МДП- транзисторы 29 и 31 с каналами соответственно р- и п-типа при этом закрыты, и подложки МДП-транзисторов 2 и 3, подключенные к третьей 37 и чет- . вертой 38 управляЕоцим клеммам ycTpoii- ства управления, изолированы от напряжений на шинах питания 33 и 34 устройства 4 управления. Аналоговый сигнал с входной шины 19 устройства через открытый КМДП-ключ 1 проходит на выходную шину 20 устройства и в нагрузку. Когда на управляющую шинУ 32 устройства подан сигнал низкого уровня, на первой 35 и второй 36 управляющих клеммах устройства управления форм1 фуются сигналы соотв етст- венно положительной и отрицательной полярности, в результате чего КМДП- ключ 1 закрыт. МДП-транзисторы 29 и 31 при этом открыты, и на подложки МДП-транзисторов 2 и 3 Ю-ЩП-ключа 1 с третьей 37 и четвертой 38 управляющих клемм устройства 4 управления подаются запирающие потенциалы. В результате МДП-транзисторы КМДП-ключа 1 находятся в закрытом состоянии при любых значениях аналогового сигляющие клеммы КМДП-ключа

в зави

симости от величины и знака аналогового сигнала регулируются формирователем 5 напряжения, который работает следующим образом.

Первый 6, третий 8 и четвертый 9 резисторы образуют делитель напряжения, который включен между клеммами 22 и 23 положительного и отрицательного источников питания. Величина сопротивлений этих резисторов одинаковая. Поэтому напряжение между выходными шинами 25 и 26 формирователя напряжений не может превыщать величины одного из источников напряжений, подключенных к клеммам 22 или 23.

В зависимости от величины и знака аналогового сигнала на выходных шинах 25 и 26 форм1фуются напряжения, несимметричные относительно общей шины 24. Поэтому можно управлять i К ЩП-ключом 1 с помощью минимального

p;i.faxa напряжо.яш между выходными типами 23 и 26 при коммутации аналоговых сигналов, не выходящих по величине за пределы только одного из ис- точников питания, подключенных к 22 и 23.

Коли аналоговый сигнал равен нулю или представляет величину любой полярности, меньш то, чем напряжения от- пираний МДП-транзисторов 13 или 14, то на выходных шинах 25 и 26 формируются равные по амплитуде разнополяр ные напряжения. По мере роста положительного напряжения аналогового сиг- нала на входной шине 19 устройства открывается первый диод 17 и первый МДП-транзистор 14 п-типа, который совместно со вторым резистором 7 образует делитель напряжения. По мере открывания первого МДП-транзистора 11 р-типа его сопротивление шунтирует первый резистор 6, вызывая повьшение величины положительного напряжения на первой выходной шине 25 формирователя 5 напряжения и снижение по абсолютной величине отрицательного напряжения на второй выходной шине 26,

Третий ЩП-транзистрр 16 п-типа при этом открыт, а третий МДП-тран- зистор 13 р-типа заперт, так как потенциал его затвора равен потенциалу общей шины 24.

Аналогично по мере роста отрицательного напряжения аналогового сигнала открывается второй диод 18 и соответственно третий МДП-транзистор 13 р-типа. Регулируемый делитель напряжения обеспечивает при этом уменьшение положительного напряжения на первой выходной шине 25 формирователя 5 напряжения и увеличение по абсолютной величине отрицательного напряжения на второй выходной шине 26.

Таким образом, при одной и той же максимальной разности потенциалов на управляющих клеммах устройства управления удается расширить диапазон коммутируемых аналоговых напряжений.

Формула изобретения

j 0 5

п

0

5

0

5

но к входной и выходной шинам переключателя, затворы и подложки тех же МДП-транзисторов подключены к соответствующим управляющим клеммам устройства управления, вход которого подключен к управляющей шине переключателя, о тлич ающий с я тем, что, с целью расширения диапазона коммутируемых напряжений, в переключатель введен формирователь напряжения, состоящий из трех МДП-транзисторов р-типа, трех МДП-транзисторов п-типа, пяти резисторов и двух диодов, причем управляющая клемма формирователя напряжения соединена с входной шиной переключателя, клемма положительного источника питания подключена к первым выводам первого и второго резисторов, истоку и подложке первого МДП-транзистора р-типа, а клемма отрицательного источника питания подключена к первым выводам четвертого и пятого резисторов, стоку и подложке второго МДП-транзистора п-типа, истоки и подложки второго и третьего МДП-транзисторов р-типа, а также первого и третьего МДП-транзисторов п- типа подключены к общей шине переключателя, второй вывод второго резистора соединен с затвором первого МДП- транзистора р-типа и стоком первого МДП-транзистора п-типа, а второй вывод пятого резистора соединен с затвором второго МДП-транзистора п-типа и стоком третьего МДП-транзистора р-типа, сток первого МДП транзистора р-типа соединен с общей точкой первого и третьего резисторов и подключен к первой выходной шине формирователя напряжения, сток второго МДП- транзистора п-типа соединен с общей точкой третьего и четвертого резисторов и подключен к второй выходной шине формирователя напряжения, катод первого диода, затвор первого МДП- транзистора п-типа и сток второго МДП-транзистора р-типа объединены, анод второго диода, затвор третьего МДП-транзистора р-типа и сток третьего МДП-транзистора п-типа также объединены, анод и катод соответственно первого и второго диодов, а также затворы второго МДП-транзисТора р- типа и третьего МДП-транзистора п- типа объединены и подключены к управляющей клемме формирователя напряжений, первая и вторая выходные шины устройства управления подключены к

первой и второй шинам питания устройства управления соответственно,

2, Переключатель по п. 1, отличающийся тем, что устройство управления содержит два КМДП- инвертора и три МДП-транзистора, которые соединены последовательно, исток и подложка первого МДП-транзистора с каналом р-типа подключены к первой шине питания устройства управления, а исток и подложка третьего МДП-транзистора с каналом п-типа - к второй шине питания устройства управления, затворы тех же МДП-тран- зисторов соединены соответственно с выходом второго и выходом первого ЩЦП-инверторов, вход которого является входом устройства управле

о

5

ния, выход первого КМДП-инвертора подключен также к входу второго КМДП- инвертора и к первой управляющей клемме устройства управления, а выход второго КМДП-инвертора соединен с второй управляющей клеммой устройства управления и с затвором второго МДП-транзистора с каналом п-типа, исток и подложка которого соединены со стоком третьего МДП-транзистора с каналом п-типа и с четвертой управ лякяцей клеммой устройства управления, сток первого ЦЦП-транзнстора с каналом р-типа соединен с третьей управляющей клеммой устройства управления, первый и второй КМДП-инверто- ры включены между шинами питания устройства управления.

| Патент США Р 3866064, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Промывально-чесальная машина для выделения волокон из хвои | 1920 |

|

SU590A1 |

| Аналоговые и цифровые интегральные микросхемы | |||

| М.: Радио и связь, 1985, с | |||

| Устройство для телефонирования по проводам токами высокой частоты | 1921 |

|

SU374A1 |

Авторы

Даты

1988-03-30—Публикация

1986-10-04—Подача