Изобретение относится к вычислительной технике и может быть использовано в системах сейсмических,акустических, видео- и других .игналов.

Целью изобретения является упрощение фильтра.

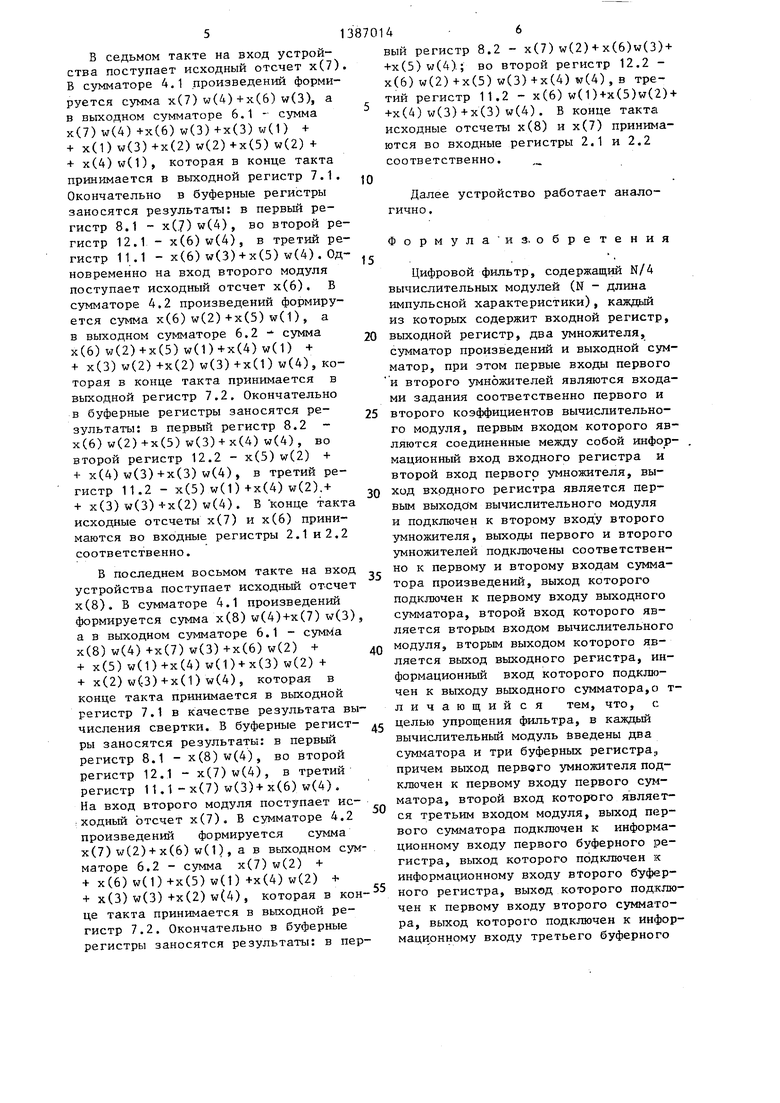

На чертеже изображена структурная схема цифрового фильтра.

Цифровой фильтр содержит N/4 вычислительных модулей 1.1, каждый из которых содержит входной регистр 2.1 (,N/4), умножитель 3.1, сумматор 4.1 произведений, сумматор 5.1 (промежуточных результатов), выходной сумматор 6.1, выходной регистр 7.1, буферный регистр 8.1, умножитель 9.1, сумматор (промежуточных результатов) 10.1, буфернь1а регистры 11.1 и 12.1.

При реализации цифровой фильтрации устройство должно вычислять выражение вида

у(п) w(i)x(n-i+1), (1)

i( где w(i) - коэффициенты импульсной

характеристики цифрового фильтpa

х(1) - входные отсчеты; у(п) - выходные отсчетыj

N - количество коэффициентов импульсной характеристики цифрового фильтра. Рассмотрим пример рабо-ты фильтра

для случая Ы 8j для этого требуется два модуля.

В первом такте на вход устройст- ва поступает исходный отсчет х (1). В первом умножителе 3.1 формируется произведение х(1) w(4), которое через сумматор 4.1 произведений поступает в выходной сумматор 6,1 ив конце такта принимается в выходной ре25 сумматора 10.1 промежуточных резуль татов, на первый вход которого поступает содержимое буферного регист- ра 12.1. В сумматоре 4.1 произведений формируется сумма х(3) w(4) + + x(2)w(3). На первый вход выходного сумматора 6.1 поступает содержимое выходного регистра 7.2, а так же сумматора 4.1 произведений и полученная сумма в конце такта принимается в выходной регистр 7.1. Одновременно во второй буферный регистр заносится произведение х(2) w(4) . В первый буферный регистр 8.1 заносится x(3)w(4), а в буферный регистр 11.1 - содержимое второго сумматора 10,1 промежуточных результатов х(2) w(3) + х(1) w(4) . Одновременна на первый вход второго модуля поступает исходный отсчет х(2). В первом

гистр 7.1. Одновременно это произведение через первый сумматор 5.1 про- 45 втором 9.2 ут ножителях форми- межуточных результатов принимается в первьш буферный регистр 8.1, В конце первого такта исходный отсчет х(1)

руются произведения соответственно х(2) w(2) и х(1) w(1), которые поступают сос гветственно в первый 5.2 и второй 10.2 сумматоры промежуточных результатов. В сумматоре 4.2 произведений формируется сумма х(2) w(2) н- x(1)w(1), которая через выходной сумматор 6.2 заносится в выходной регистр 7.2. Одновременно в бу- ферньш регистр 12.2 заносится произ ведение x(1)w(2). На второй вход второго модуля поступает содержимое с третьего выхода первого модуля и в первом сумматоре 5.2 промежуточны

принимается также во входной регистр 2.1.

Во втором такте на вход устройства поступает исходный отсчет х (2). В первом 3.1 и втором 9.1 умножителях формируются произведения соответственно х(2) w(4) и x(1)w(3), которые поступают соответственно в первый 5,1 и второй 10.1 сумматоры промежуточных результатов. В сумматоре 4.1 произведений формируется сумма

0

х(2) w(4) +х(1) w(3), которая через выходной сумматор 6.1 заносится в выходной регистр 7.1. Одновременно, в буферный регистр 12.1 заносится произведение x(1)w(4), В первый буферный регистр 8.1 принимается произведение x(2)w(4), а в буферный регистр 11.1 - x(1)w(3). Одноёремен- но на первый вход второго модуля поступает исходный отсчет х(1). В первом умножнтелеЗ.2 формируется произведение x(1)w(2), которое через сумматор 4.2 произведений поступает в вы5 ходной сумматор 6.2 и принимается в выходной регистр 7.2.

В третьем такте на вход устройства поступает исходный отсчет х(3). В первом 3.1 и втором 9.1 умножите0 лях формируются соответственно произведения х(3) w(4) и х(2) w(3), кото- рые поступают соответственно в первый сумматор 5.1 промежуточных результатов и на второй вход второго

5 сумматора 10.1 промежуточных результатов, на первый вход которого поступает содержимое буферного регист- ра 12.1. В сумматоре 4.1 произведений формируется сумма х(3) w(4) + + x(2)w(3). На первый вход выходного сумматора 6.1 поступает содержимое выходного регистра 7.2, а также сумматора 4.1 произведений и полученная сумма в конце такта принимается в выходной регистр 7.1. Одновременно во второй буферный регистр заносится произведение х(2) w(4) . В первый буферный регистр 8.1 заносится x(3)w(4), а в буферный регистр 11.1 - содержимое второго сумматора 10,1 промежуточных результатов х(2) w(3) + х(1) w(4) . Одновременна на первый вход второго модуля поступает исходный отсчет х(2). В первом

0

5

0

5 втором 9.2 ут ножителях форми-

втором 9.2 ут ножителях форми-

руются произведения соответственно х(2) w(2) и х(1) w(1), которые поступают сос гветственно в первый 5.2 и второй 10.2 сумматоры промежуточных результатов. В сумматоре 4.2 произведений формируется сумма х(2) w(2) + н- x(1)w(1), которая через выходной сумматор 6.2 заносится в выходной регистр 7.2. Одновременно в бу- ферньш регистр 12.2 заносится произведение x(1)w(2). На второй вход второго модуля поступает содержимое с третьего выхода первого модуля и в первом сумматоре 5.2 промежуточных

результатов формируется сумма x(1)w(3) + x(2)w(2), которая затем заносится в первый буферный регистр 8.2, а во второй буферный регистр 11,2 - принимается x(1)w(1). В конце такта исходные отсчеты х(2) и х (3) принимаются во входные регистры 2.1 и 2.2 соответственно. Далее работа устройства повторяется.

В четвертом такте на вход устройства поступает исходный отсчет х(4). В первый сумматор 5.1 промежуточных результатов заносится произведение x(4)w(4), в во второй сумматор 10.1 промежуточных результатов - сумма х(3) w(3) + x(2) w(4). Через сумматор

4.1произведений на второй вход выходного сумматора 6.1 заносится сумма х(4) w(4)+х(3) w(3), а на первый его вход поступает результат с выходного регистра 7.2, полученный в предьщущем такте, и сумма х(2) w(2) + + х(1) w(1) + x(4) w(4)+x(3) w(3) в конце такта принимается в выходной регистр 7.1. Одновременно на второй вход второго модуля поступает содержимое третьего буферно го регистра 11.1 а во второй буферный регистр 12.1 - содержимое первого буферного регистра 8.1. В первый 8.1 и третий 11.1 буферные регистры поступают соответственно результаты х(4)w(4) и х(3) w(3)+ х(2) w(4) . Одновременно на первый вход второго модуля поступает исходный отсчет х(3). В сумматоре

4.2произведений формируется сумма х(3) w(2)+х(2) w( 1), которая поступает на второй вход выходного .сумматора 6.2, на первый вход которого поступает содержимое третьего буферного регистра 11.2, полученное в предыдущем такте, и результат x(3)w(2) +

+ х(2) w(1) +х(1) w(1) заносится в выходной регистр 7.2. Окончательно в первый буферный регистр 8.2 заносится сумма х(3) w(2)+x(2) w(3) + + x(1)w(4), во второй регистр 12.2 сумма х(1) w(3) + х(2.) w(2), а в третий регистр) 11.2 - сумма x(2)w(1) + + х(1) w(2). В конце такта исходные отсчеты х(4) и х(3).принимаются в входшле регистры 2.1 и 2.2 соответственно.

В пятом такте на вход устройства поступает исходный отсчет х(5). В сумматоре 4.1 произведений формируется сумма х(5) w(4) + x(4) w(3), а в выходном сумматоре 6.1 - cyMMax(5)w(4)

0

5

0

5

0

5

0

5

0

5

+х(4) w(3)+х(3) w(2)+х(2) w(1) + + х(1) w(1), которая принимается в выходной регистр 7.1. Окончательно в буферные регистры принимаются результаты: в первый регистр 8.1 - х(5) w(4), во второй регистр 12.1 - x(4)w(4), а в третий регистр 11.1 - х(4) w(3)+х(3) w(4). Одновременно на первый вход второго модуля поступает исходный отсчет х(4). В сумматоре 4.2 произведений формируется сумма х(4) w(2)+х(3) w(1), а в выходном сумматоре 6.2 - сумма х(4) w(2) + + х(3) w(1)+x(2) w(1) + x(1) w(2), которая в конце такта принимается в выходной регистр 7.2. Окончательно в буферные регистры заносятся резуль- таты: в первый регистр 8.2 - x(4)w(2) + +х(2) w(3)+ х(2) w(4) , во второй регистр 12.2-x(3)w(2)+x(2)w(3) + +x(1)w(4), в третий регистр 11.2 - х(3) w(1) +х(1) w(3) +х(2) w(2). В конце такта исходные отсчеты х-(5) и X(4) принимаются во входные регистры 2.1 и 2.2 соответственно.

В шестом такте на вход устройства поступает исходный отсчет х(6). В сумматоре 4.1 произведений формируется сумма х(6) w(4) +х(5) w(3), а в выходном сумматоре 6.1 - сумма х(6) w(4) + х(5) w(3) + х(4) w(2) + + х(3) w(i) +х(2) w(1) +х(1) w(2), которая в конце такта принимается .в выходной регистр 7.1. Окончательно в буферные регистры заносятся результаты: в первый регистр 8.1 - x(6)w(4), во второй регистр 12.1 - x(5)w(4), в третий регистр 11.1 - х(5) w(3) +х(4) w(4). Одновременно на вход второго модуля поступает исходный отсчет х(5). В сумматоре 4.2 произведений формируется сумма х(5) w(2) + +x(4)w(l), а в выходном сумматоре 6.2 - сумма х(5) w(2)+х(4) w(1) + + х(3) w(1) +х(1) w(3)+x(2) w(2, которая в конце такта принимается в выходной регистр 7.2. Окончательно в буферные регистры заносятся результаты: в первый регистр 8.2 - х(5) w(2)+x(4) w(3) + x(3) w(4), во второй регистр 12.2 - x(4)w(2) + + х(3) w(3) ьх(2) w(4) , в третий регистр 11.2 - х(4) w(1)+x(3) w(2) + + х(2) w(3)+х(1) w(4). В конце такта исходные отсчеты х(6) и х(5) принимаются во входные регистры 2.1 и 2.2 соответственно.

В седьмом такте на вход устройства поступает исходный отсчет х(7) В сумматоре 4.1 произведений формируется сумма х(7) w(4)+х(6) w(3), а в выходном сумматоре 6.1 - сумма х(7) w(4)+х(6) w(3)+x(3) w(1) + + х(1) w(3) +х(2) w(2) (5) w(2) + + x(4)w(1), которая в конце такта принимается в выходной регистр 7.1, Окончательно в буферные регистры заносятся результаты: в первый регистр 8.1 - x(.7)w(4), во второй регистр 12.1 - x(6)w(4), в третий регистр 11.1 - х(6) w(3) + x(5) w(4). Од новременно на вход второго модуля поступает исходный отсчет х(6). Б сумматоре 4.2 произведений формируется сумма х(6) w(2)+х(5) w(1) , а в выходном сумматоре 6.2 сумма х(6) w(2)+x(5) w(1)+x(4) w(1) + + х(3) w(2) +х(2) w(3) +х(1) w(4), которая в конце такта принимается в выходной регистр 7.2. Окончательно в буферные регистры заносятся результаты: в первый регистр 8.2 - х(6) w(2)+x(5) w(3)-i-x(4) w(4), во второй регистр 12.2 - х(5) w(2) + + х(4) w(3)+х(3) w(4) , в третий регистр 11,2 - х(5) w(1)+х(4) w(2).+ + х(3) w(3)(2) w(4) . В конце такт исходные отсчеты х(7) и х(6) принимаются во входные регистры 2.1 и 2.2 соответственно.

В последнем восьмом такте на вход

устройства поступает исходный отсчет х(8). В сумматоре 4.1 произведений формируется сумма х(8) w(4)+x(7) w(3) , а в выходном сумматоре 6,1 - сумма х(8) w(4)+x(7) w(3)+x(6) w(2) + + х(5) w(1)+x(4) w(1) + x(3) w(2) + + x(2) w(-3)+x(1) w(4), которая в конце такта принимается в выходной регистр 7,1 в качестве результата вычисления свертки, В буферные регист- ры заносятся результаты: в первый регистр 8,1 - x(8)w(4), во второй регистр 12,1 - x(7)w(4), в третий регистр 11,1 - х(7) w(3) +к(6) w(4) . На вход второго модуля поступает ис- :ходный отсчет х(7), В сумматоре 4,2 произведений формируется сумма х(7) w(2) + x(6) w(1), а в выходном сумматоре 6,2 - сумма х(7) w(2) + + х(6) w(1)+х(5) w(1) +х(4) w(2) -ь + х(3) w(3)+х(2) w(4), которая в конце такта принимается в выходной регистр 7.2. Окончательно в буферные регистры заносятся результаты: в пер

g 0

5

0

5

О

0

вый регистр 8,2 - х(7)w(2) + x(6)w(3) + +x(5)w(4).; во второй регистр 12,2 - х(6) w(2) +х(5) w(3) +х(4) w(4) , в третий регистр 11,2 - х(6) w(1)-i-x(5)w(2) + -t-x(4) w(3)+х(3) w(4). В конце такта исходные отсчеты х(8) и х(7) принимаются во входные регистры 2.1 и 2,2 соответственно.

Далее устройство работает аналогично .

Формула из- обре тения

Цифровой фильтр, содержащий N/4 вычислительных модулей (N - длина импульсной характеристики), из которых содержит входной регистр, выходной регистр, два умножителя, сумматор произведений и выходной сумматор, при этом первые входы первого и второго умножителей являются входами задания соответственно первого и второго коэффициентов вычислительного модуля, первым входом которого являются соединенные между собой информационный вход входного регистра и второй вход первого умножителя, выход входного регистра является первым выходом вычислительного модуля и подключен к второму входу второго умножителя, выходы первого и второго умножителей подключены соответственно к первому и второму входам сумматора произведений, выход которого подключен к первому входу выходного сумматора, второй вход которого является вторым входом вычислительного модуля, вторым выходом которого является выход выходного регистра, информационный вход которого подключен к выходу выходного сумматора,о т- личающийся тем, что, с целью упрощения фильтра, в каждый вычислительньй модуль введены два сумматора и три буферных регистра,, причем выход первого умножителя подключен к первому входу первого сумматора, второй вход которого является третьим входом модуля, выход первого сумматора подключен к информационному входу первого буферного регистра, выход которого подключен к информационному входу второго ного регистра, выход которого подключен к первому входу второго сумматора, выход которого подключен к информационному входу третьего буферного

713870148

регистра, выход которого являетсятра, причем первый выход i-ro (i третьим выходом вычислительного мо-1, N/4-1) подключен к первому входу дуля, и выход второго умножителя под-(i+D-ro вычислительного модуля, вто- ключен к второму входу второго сум- jрой выход которого подключен к вто- матора, первый вход первого вычисли- рому входу i-ro вычислительного мотального модуля является первым ий-дуля, третий выход которого подклю- формационным входом фильтра, вторымчен к третьему входу (i+1)-ro вычис- информационным входом которого явля-лительного модуля, третий выход N/4-го ется третий вход первого вычислитель-iовычислительного модуля подключен к ного модуля, второй выход котороговторому ВХОДУ N/4-го вычислительного является информационным выходом филь-модуля.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цифровой фильтрации | 1987 |

|

SU1499374A1 |

| Цифровой фильтр | 1987 |

|

SU1501088A1 |

| Рекурсивный цифровой фильтр | 1987 |

|

SU1573532A1 |

| Цифровой фильтр | 1988 |

|

SU1584084A2 |

| Устройство для вычисления дискретного преобразования Фурье | 1990 |

|

SU1725228A1 |

| Устройство для цифровой фильтрации | 1986 |

|

SU1348815A1 |

| Параллельное устройство для вычисления двухмерной свертки | 1985 |

|

SU1269237A1 |

| Устройство для вычисления свертки | 1986 |

|

SU1319045A1 |

| Устройство для цифровой фильтрации | 1986 |

|

SU1377872A1 |

| Цифровой фильтр | 1985 |

|

SU1314352A1 |

Изобретение относится к области вычислительной техники и может быть использовано в системах рейсми- ческих, акустических, видео- и других сигналов. Цель изобретения-упрощение устрой.ства. Цифровой фильтр содержит N/A (N - длина импульсной характеристики) вычислительных модуля 1. Каждый из них содержит входной регистр 2.1, умножитель 3.1,сумматор 4.1 произведений, сумматор 5.1, выходной сумматор 6.. 1, выходной регистр 7.1, буферный регистр 8,1, умножитель 9.1, сумматор 10.1, буферный регистр 11.1,буферный регистр 12.1 и соответствующие связи между узлами вычислительных модулей и самими вычислительными модулями. 1 ил. 71 (Л 00 00

| Устройство для цифровой фильтрации | 1984 |

|

SU1241258A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Цифровой фильтр | 1985 |

|

SU1314352A1 |

Авторы

Даты

1988-04-07—Публикация

1986-10-20—Подача