Изобретение относится к вычислительной технике и может быть исполь- зовано в системах цифровой-обработки радиолокационных, видео-, сейсмиче С- ких и других сигналов,

Цель изобретения - повьш1ение быстродействия устройства.

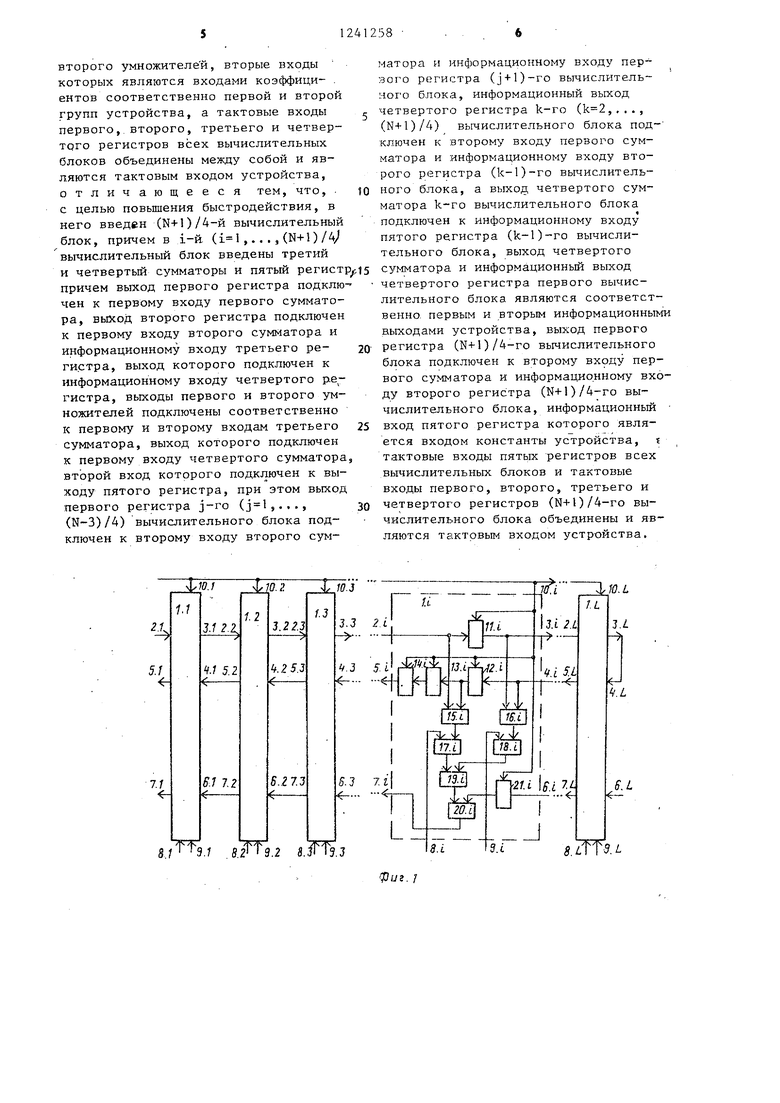

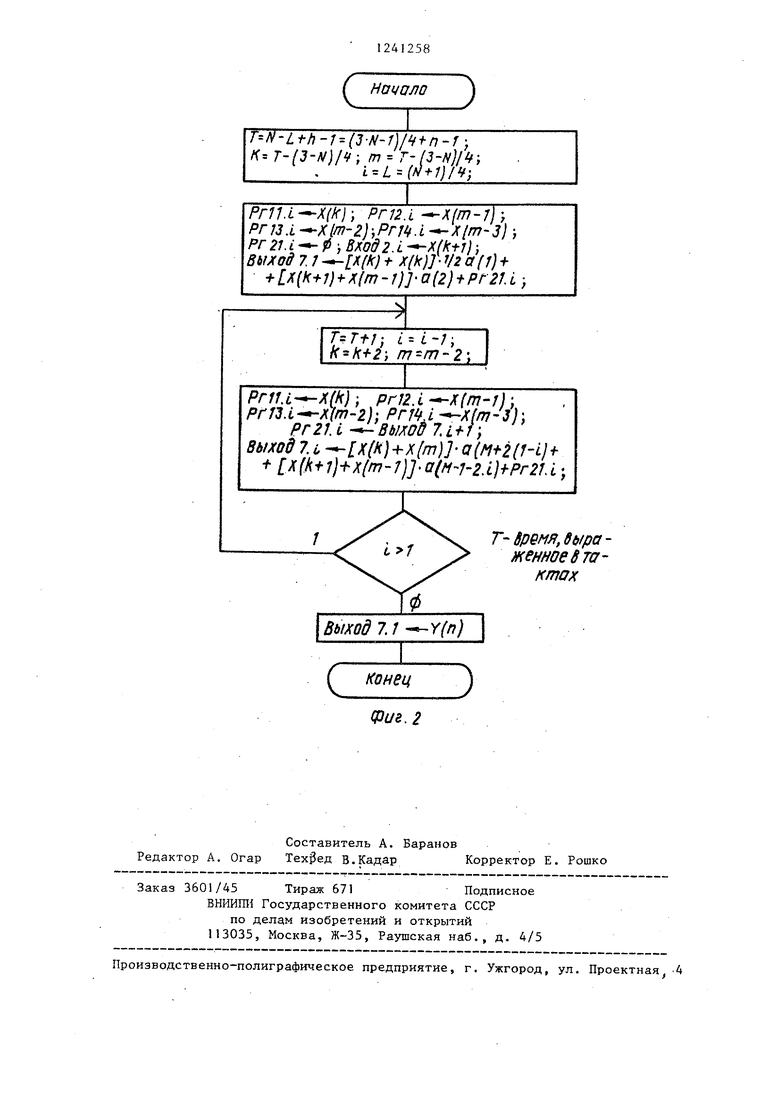

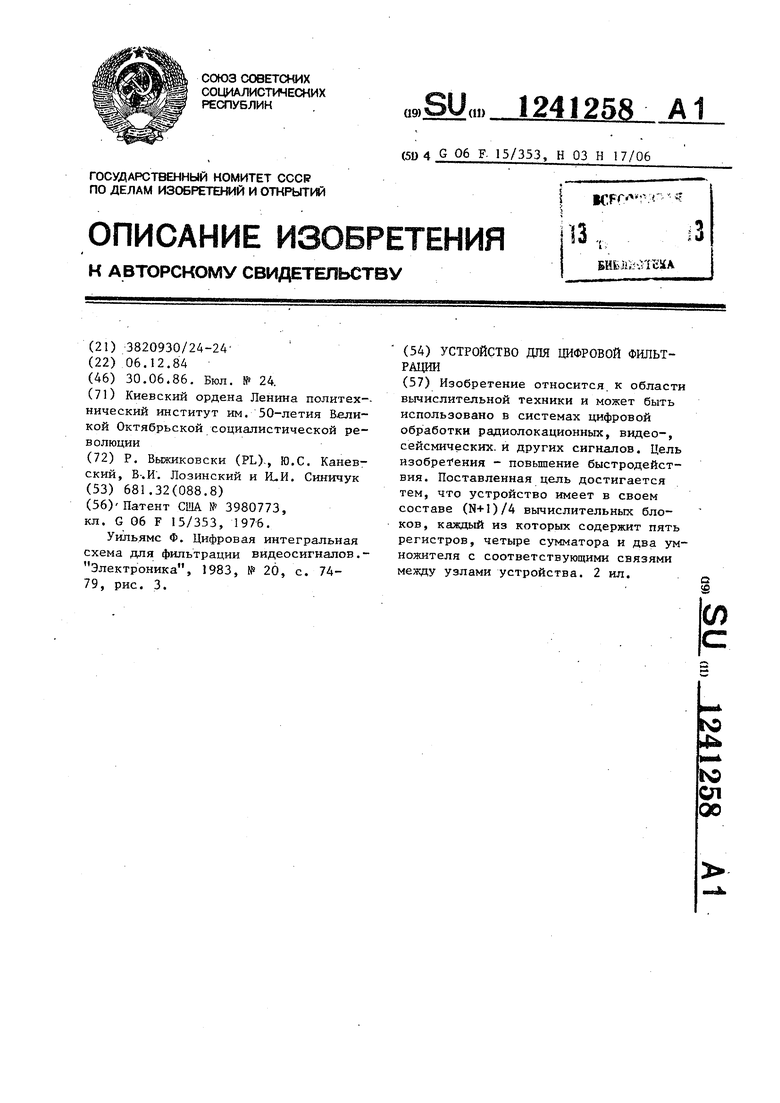

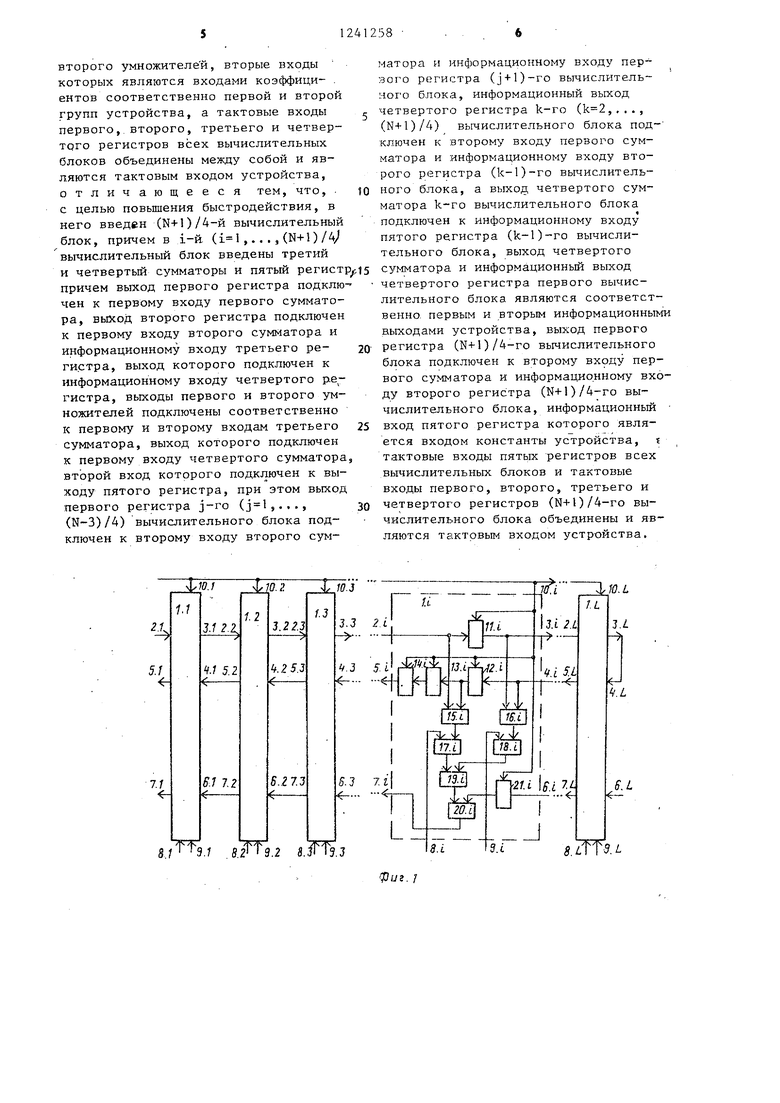

На фиг. I изображена структурная схема предлагаемого устройства; на фиг. 2 - блок-схема алгоритма форми- рования отсчета выходного сигнала Y(n).

Устройство содержит L(N+l)/4 вычислительных модуля I.1-1.L, причем первый вход 2.1 i-ro блока (i 2,3,... ,L) соединен с первым выходо 3.(1-1)-го блоки} второй вход A.i i-ro блока; ( ,2,. . . ,Ь-т1) соединен с вторым выходом 5.1+1 (1+)-го блока, пятый вход 6,1 1-го блока (1 1 , 2,... ,L-1) соединен с третьим выходом 7.1+1 (1+1)-го блока, третий- 8.1. и четвертый 9 .1 входы 1-го - блока (,2,...,L) соединены с входами весовых коэффициентов симметричной импульсной характеристики устройства Тактовые входы 10.1 (,2,..,,L) всех блоков соединены с тактовым входом устройства. При этом первый вход 2.1 и третий выход 7.1 первого моду- ля 1.1 являются соответственно выходом и входом устройства. Первый.выход 3.L последнего модуля 1.L соединен с вторым входом 4.L этого же модуля, а на пятый вход 6.L подан сиг- нал логического нуля.

Каждый вычислит,ельный блок содержит регистр 11, вход которого соединен с первым входом 2 модуля 1, а выход - с первым выходом 3 модуля 1, регистр 12, вход которого соединен с вторым входом 4 МОДУ-5Я 1 ,, а выход с входом регистра 13, выход которого соединен с входом четвертого регистра 14, выход которого соединен с вторым выходом 5 блока 1, сумматор 15, перв ый вход которого со.единен с первым входом 2 блока, а второй вход - с выходом регистра 12, сумматор 16, вход которого соединен с вы- ходом регистра II, а другой вход - с входом 4 блока 1; первый 17 и вто- -рой 18 умножители, первые входы которых соединены с выходами соответственно сумматоров 15 и 16, вторые входы - соответственно с третьим 8 и четвертым 9 входами блока 1, а выходы - соответственно с первым и

58 -2

вторым входами сумматора 19, выход которого соединен с входом сумматора 20., выход которого соединен с третьим выходом 7 блока 1, а другой вход - с выходом регистра 21, вход которого соединен с пятым входом 6 блока 1. . .

Тактовые входы всех регистров соединены с тактовым входом 10 блока 1 ,

Устройство работает следующим образом.

Правило формирования выходных отсчетов Y(n) имеет вид: У(п)а(1).Х(М+п-1)+а(2)(М+п) + +Х(М+п-25 +а(3)(М+п+1)+Х(М+п-3) + +а(4) СХ(М+п+2)+Х(М+п -4) +. . .+ +a(M)X(N+n-r)+X(n);(1)

где N - число весовых коэффициентов симметричной импульсной характеристики устройства, включая равные коэффициенты M(N+

+)/2 - количество различных коэффициентов импульсной характеристики;

а(1) - весовые коэффициенты симметричной импульсной хара1 те- ристики устройства (,М), причем а(1) - центральный весовой коэффициент;

X(j),

Y(n) - отсчеты с.оответственно на

входе и на выходе устройст-: ва (j, ,2,3,.,.), Первый двучлен а(1) X(М+п-1) формулы (1) в устройстве реализован в врще

а()

х(М+п-)+Х(М+п-1) ,

т.е. на вход центрального весового коэффициента устройства подана величина а(1)/2, так как на первый вход умножителя 18.L подается удвоенный входной отсчет Х(М+п-1).

Операцию цифровой фильтрации устройство выполняет следующим образом. На протяжении первых (N-Lтактов, где такт - отрезок времени между передними фронтами двух тактовых импульсов, поступающих на тактовый вход устройства, осуществляется заполнение регистров блоков - режим холостого хода. Новый входной отсчет поступает на вход устройства сразу после прихода переднего фрон- та тактового импульса. В (N-L)-M такте поступившие на вход устрой3

ства (N-Ы-1) входных отсчета X(j) находятся соответственно: X(N-L+I)- на входе устройства; X(N-L) - в регистре 11.1; Y(N-L-l) - в регистре 11,2; X((N-fl)/2) - в регистре 11.L; X((N+)/2-I) - в регистре 12.L; X((N+ I)/2-2) -.в регистре 13.L; X((N+l)/2-3) - в регистре l.L;,,. Х(2) - в регистре 12.2; Х(1) - в регистре 13.2.

С приходом очередного тактового импульса происходит сдвиг входных отсчетов в цепочке, образованной регистрами 11 , 1-11.L, 12.L, 13.L, 14.L, 12.L-1, I3.L-1, 14.L-1,..., 12.1, 13.1, 14.1. Таким образом, с началом каждого нового такта номера хранимых в указанных регистрах входных отсчетов X(j) увеличиваются на единицу по сравнению с предьщущим тактом.

Рассмотрим работу устройства при формировании отсчета Y(n) для случая , что соответствует различным весовым коэффициентам симметрич- ной импульсной характеристики фильтра. Устройство содержит L-(N+l) вычислительных модуля. Режим холостого хода длится N-L-1 7 тактов.

Формула (1) формирования выход- ных отсчетов для приобретает следующий вид:

Y(n) -2 x(n+5)+X(n+5)j+a(2)« x(n-f6)+X(n+4) +. . .(6)(n+10) +

X(n), (2 где , 2 , 3 ,. . .

Выходной отсчет Y(n) начинает формироваться в (N-L+n-l)(7+n)m такте причем входные отсчеты в этом такте находятся: Х(п+8) - на входе устройства; Х(п+7) - в регистре -1.1; Х() - в регистре 11.2; Х(п+5) - в регистре 11.3; Х(п+4) - в- регистре 12.3; х(п+3) - в регистре 13.3; Х() - в регистре 14.3; Х(п+1) - в регистре 12.2; Х(п) - в регистре 13.2.

Рассмотрим получение отсчета Y(n При дтом описывается работа только той части устройства, которая связана с формированием Y(n).

Такт (п+7). В третьем блоке формируются на выходах: сумматора 1 б.3 - х(п+5)+Х(п+5) 2 xU-«-5); умножителя 8.3-2-Х(п+5) / а( О (так как на второй вход умножителя

5 to

15 20

5

о

л 5

0

5

258-4

18.3 подается у а(1)); сумматора

15.3 - х(п+6)+Х(п+4) ; умножителя 17.3 - tX(n+6)+x(n+4).а(2); сумматора 19.3 - х(п+6)+Х(а+4)-а(2) + +Х(п+5), а(1); сумматора 20.3 - ;х(п+6)+Х(п+4)-а(2)+Х(п+5). а(1) (на втором входе сумматора 20.3 - сигнал логического нуля).

Такт (п+8). Третий блок-начинает формировать выходной отсчет Y(n+l) аналогично описанному, в то время как второй модуль продолжает вычисление Y(n). Б этом такте во втором блоке формируются на выходах: сумма- тора 16.2 - Х(п+7)+Х(п+3) ; умножителя 18.2 - Гх(п+7)+Х(п+3). а(3); сумматора 15.2 - ;х(п+8)+Х(п+2) ; умножителя 17.2 - X(n+8)+X(n+2)J.a(4); сумматора 19.2 (п+7)+Х(п+3).а(3) + + х(п+8)+х(п+2)-а(4) ; сумматора 20.2- Х(п+5).а(1) + х(п+6)+Х(п+4). а(2) + -((п+7)+Х(п+3) а(3)(п+8)+Х(п+25|ч . «а(4) (так как в регистре 21.2 содержится слагаемое, сформированное в предыдущем такте третьим блоком).

Такт (п+9). В третьем блоке начинается формирование отсчета Y(n+2), во втором и первом блоках продолжается формирование соответственно отсчетов Y(n+l) и Y(n). В первом блоке формируются на выходах: сумматора 16.1 - tx(n+9)(n+l) ; умножителя 18-. - Х(п+9)+Х(п+1) а(5); сумматора 15.1 - )((п+10)+Х(п) ; умножителя 17.1 - X(n+iO)+X(n)}-a(6); сумматора 19.1 - х(п+10)+Х(п).а(6) + + х(п+9)+Х(п+1)-а(5); сумматора 20.1 - Х(п+5).а(1)(п+6)+Х(п+4) а(2)(п+7)+Х(п+3).а(3)(п+8) + +X(n+2).a(4)(n+9)+X(n+l).a(5) + + х(п+10)+Х(п).а(6).

Таким образом, в каждом такте начиная с 10-го на выходе устройства появляются выходные отсчеты Y(n), сформированные в соответствии с выражением (2).

Формула изобретения

Устройство для цифровой фильтрации, содержащее (N-3)/4 вычислительных блока (N - число отсчетов импульсной характеристики, причем каждый вычислительный блок содержит четьфе регистра, первый и второй умножители, первый и второй сумматоры, выходы которых подключены к первым входам соответственно первого и

второго умножителей, вторые входы которых являются входами коэффицн- . ентов соответственно первой и второй групп устройства, а тактовые входы первого, второго, третьего и четвертого регистров всех вычислительных блоков объединены между собой и являются тактовым входом устройства, отличающееся тем, что, .

с целью повышения быстродействия, в него введен (К+1)/4-й вычислительный блок, причем в i-й ( ,.. . , (N+1)/4 вычислительный блок введены третий и четвертый сумматоры и пятый регистр причем выход первого регистра подключен к первому входу первого сумматора, выход второго регистра подключен к первому входу второго сумматора и информационному входу третьего ре- гистра, выход которого подключен к информационному входу четвертого регистра, выходы первого и второго умножителей подключены соответственно к первому и второму входам третьего сумматора, выход которого подключен к первому входу четвертого сумматора, второй вход которого подключен к выходу пятого регистра, при этом выход первого регистра j-ro (,..., ()/4) вычислительного блока подключен к второму входу второго сум0

5 0 5 о

матора и информационному входу пер- зого регистра (j+l)-ro вычислительного блока, информационный выход четвертого регистра k-ro (,,.., (N-t-l)/4) вычислительного блока под- ключен к второму входу первого сумматора и информационному входу второго регистра (k-l)-ro вьиислитель- ного блока, а выход четвертого сумматора kTo вычислительного блока подключен к информационному входу пятого регистра (k-l)-ro вычислительного блока, выход четвертого сумматора и информационный выход четвертого регистра первого вычислительного блока являются соответственно, первым и вторым информационными выходами устройства, выход первого регистра (N+l)/4-ro вычислительного блока подключен к второму входу первого сумматора и информационному входу второго регистра (N+l)/4-ro вычислительного блока, информационный вход пятого регистра которого является входом константы устройства, тактовые входы пятьк регистров всех вычислительных блоков и тактовые входы первого, второго, третьего и четвертого регистров (N+l)/4-ro вычислительного блока объединены и являются TciKTOBbiM входом устройства.

r /V-Z/-A-/ J-/V-/)/W/7-f ;

/r r-n-N lf т 7--/J-/v;/ ; -t /.

Лг77.г -/fA-j; r;.i ((/r7-7J , Pri3.L //77- ; Pnit. Pr 27.г - ;J . i X(ki-Jl;

5л/уГ 7; i- x{k)- 7/2 o //; -f +Lx{l i-i)((m-j)-a(2)-t-Pr2lL;

ГгГ-Л/; i i-/; /f

/Tr/.i-///rj; pr12.(m J}; prr3.(m-2)} /T/.i-xr//77-j;; Pr2ll Bb ;(od7.L hi

выход 7. L (f(-i-}(( a(m2{f-i -i X(ki-i}-i X(m-7) a(.l i-Pr2ll ,

Htsчaлo

T-бремя, дыра женное 8 тактах

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой нерекурсивный фильтр | 1990 |

|

SU1774349A1 |

| Параллельное устройство для вычисления двухмерной свертки | 1985 |

|

SU1269237A1 |

| Цифровой фильтр с симметричной импульсной характеристикой | 1984 |

|

SU1242988A1 |

| Устройство для цифровой фильтрации | 1985 |

|

SU1325511A1 |

| Цифровой фильтр | 1987 |

|

SU1501088A1 |

| Рекурсивный цифровой фильтр | 1987 |

|

SU1573532A1 |

| Устройство для вычисления свертки | 1984 |

|

SU1198535A1 |

| Устройство для вычисления дискретного преобразования Фурье | 1990 |

|

SU1725228A1 |

| Устройство для вычисления быстрого преобразования Фурье | 1989 |

|

SU1721610A1 |

| Устройство умножения матрицы на вектор | 1984 |

|

SU1226484A1 |

Изобретение относится, к области вычислительной техники и может быть использовано в системах цифровой обработки радиолокационных, видео-, сейсмических, и других сигналов. Цель изобретения - повьшение быстродействия. Поставленная цель достигается тем, что устройство имеет в своем составе (N+l)/4 вычислительных блоков, каждый из которых содержит пять регистров, четыре сумматора и два умножителя с соответствующими связями меяоду узлами устройства. 2 ил. о €

СконецJ

Составитель А. Баранов Редактор А. Огар Техред В.Кадар Корректор Е. Рошко

.« . «..«..B (« .« «MHi. (. . .«..

Заказ 3601/45 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная .4

Фив. 2

| Патент США № 3980773, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Уильяме Ф | |||

| Цифровая интегральная схема для фильтрации видеосигналов.- Электроника, 1983, № 20, с | |||

| Приспособление в центрифугах для регулирования количества жидкости или газа, оставляемых в обрабатываемом в формах материале, в особенности при пробеливании рафинада | 0 |

|

SU74A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-06-30—Публикация

1984-12-06—Подача