(21)4017504/24-07

(22)29.01.86

(46) 07.04.88. Бюл. № 13

(71)Мурманское высшее инженерное морское училище им. Ленинского комсомола и Научно-исследовательский институт часовой промышленности

(72)Н. И. Безгачин, В. И. Веретин и В. Б. Никитин

(53)621.314.27(088.8)

(56)Авторское свидетельство СССР № 771846, кл. Н 02 М 3/10, 1978.

Авторское свидетельство СССР № 1249603, кл. Н 02 М 3/10, 1984.

(54)УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ТРАНЗИСТОРНЫМ ПРЕОБРАЗОВАТЕЛЕМ

(57)Изобретение относится к электротехнике и может быть использовано в транзисторных преобразователях. Целью изобретения является повышение точности стабилизации выходного напряжения преобразователя. В данном устройстве погрешность стабилизации исключается тем, что высокий потенциал управляющего входа второго ключа обеспечивает подключение второго конденсатора к выходу операционного усилителя, а низкий потенциал управляющих входов соответствующих ключей отключает первый конденсатор от выхода интегратора и расшунтирует второй конденсатор. После того, как второй конденсатор подключается к выходу операционного усилителя, но еще не выключен транзистор, и на входе фильтра продолжает присутствовать напряжение, второй конденсатор начинает заряжаться до тех пор, пока не выключится транзистор. После его выключения напряжение остается постоянным и после следующего включения транзистора интегрирование начнется не с нуля, а с добавки, накопленной за счет задержки включения транзистора. 2 ил.

to

сл

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления транзисторным преобразователем | 1986 |

|

SU1387141A1 |

| Устройство для управления транзисторным преобразователем | 1985 |

|

SU1249663A1 |

| Устройство для управления транзисторным преобразователем | 1987 |

|

SU1539932A1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В ИНТЕРВАЛ ВРЕМЕНИ | 1991 |

|

RU2032269C1 |

| Способ управления транзисторным полумостовым инвертором | 1986 |

|

SU1467711A1 |

| Устройство для управления преобразователем постоянного напряжения,включающем резонансный тиристорный инвертор с транзисторным ключем на входе | 1982 |

|

SU1030945A1 |

| Устройство для управления стабилизирующим преобразователем постоянного напряжения | 1986 |

|

SU1534678A1 |

| Преобразователь постоянного напря-жЕНия B пОСТОяННОЕ дВуХпОляРНОЕ | 1979 |

|

SU843133A1 |

| СЧЕТЧИК ЭЛЕКТРИЧЕСКОЙ ЭНЕРГИИ | 2001 |

|

RU2190860C2 |

| Зарядно-пусковое устройство | 1987 |

|

SU1534632A1 |

со оо

Изобретение относится к электротехиике и может быть использовано для управления тиристорными преобразователями постоянного тока.

Целью изобретения является повышение точности стабилизации выходного напряжения преобразователя.

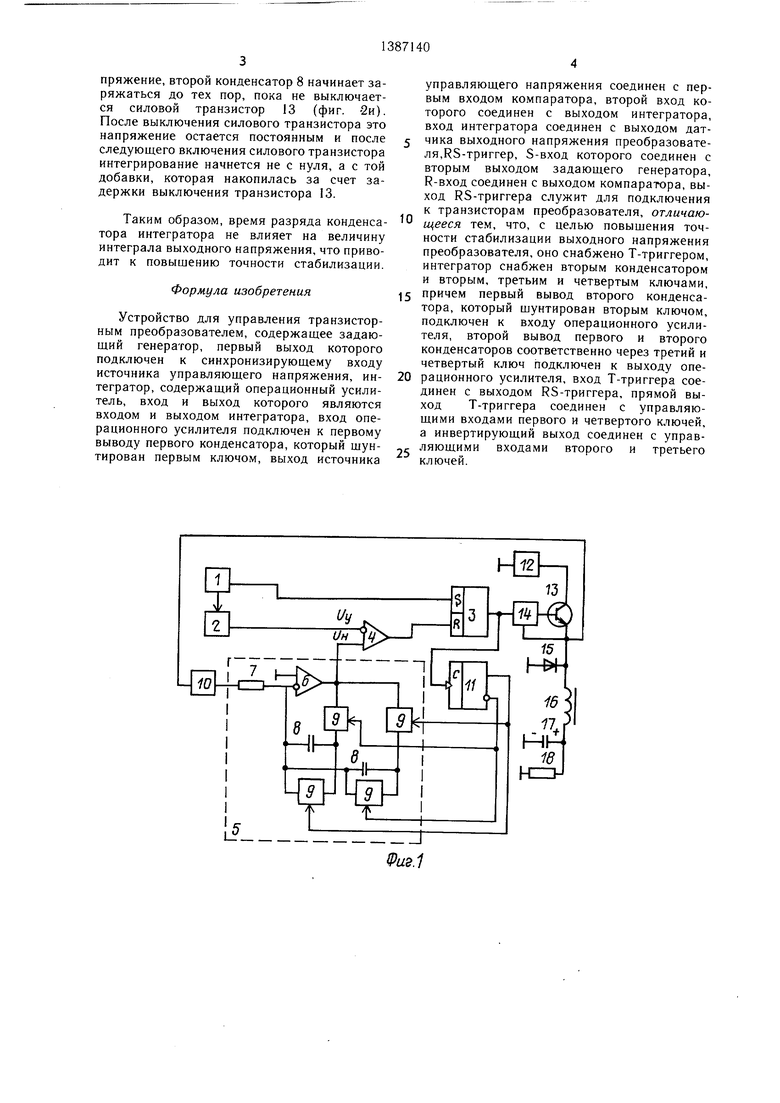

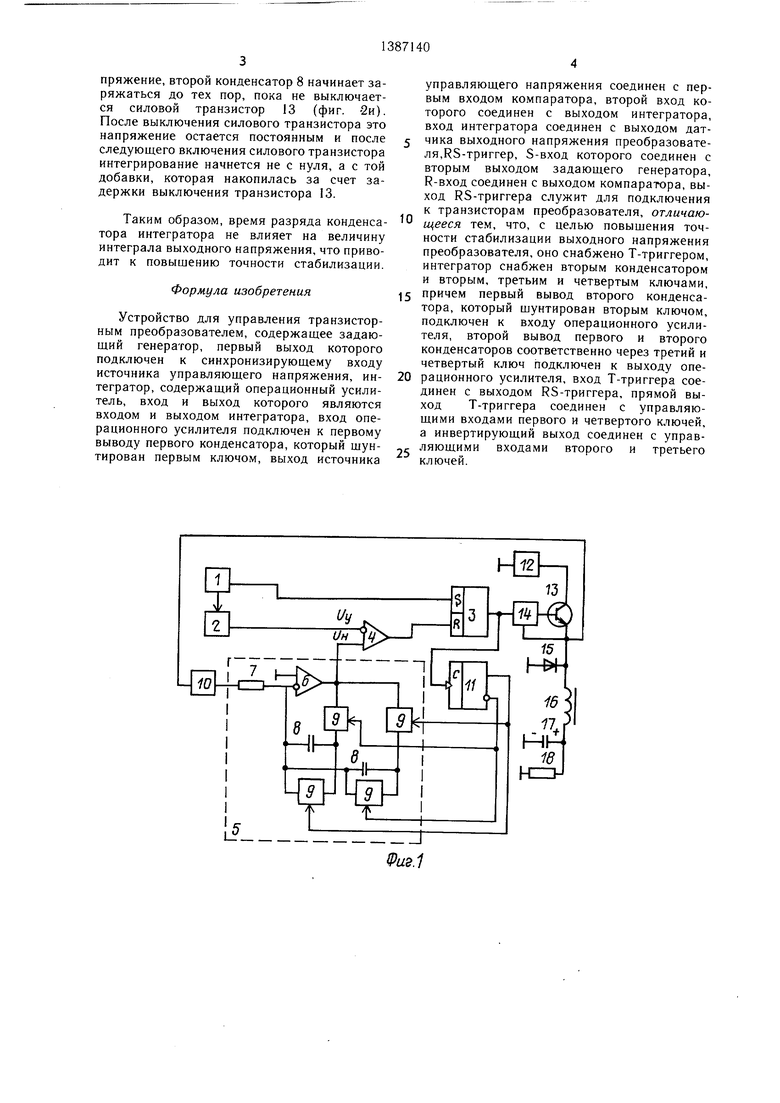

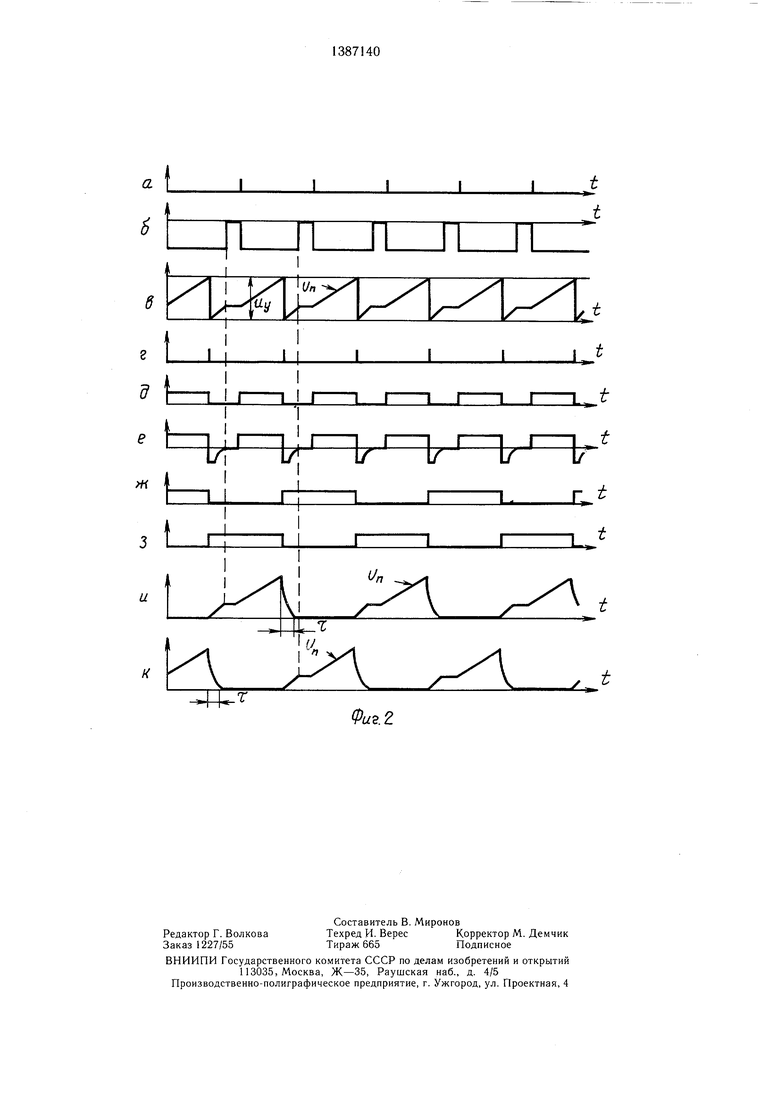

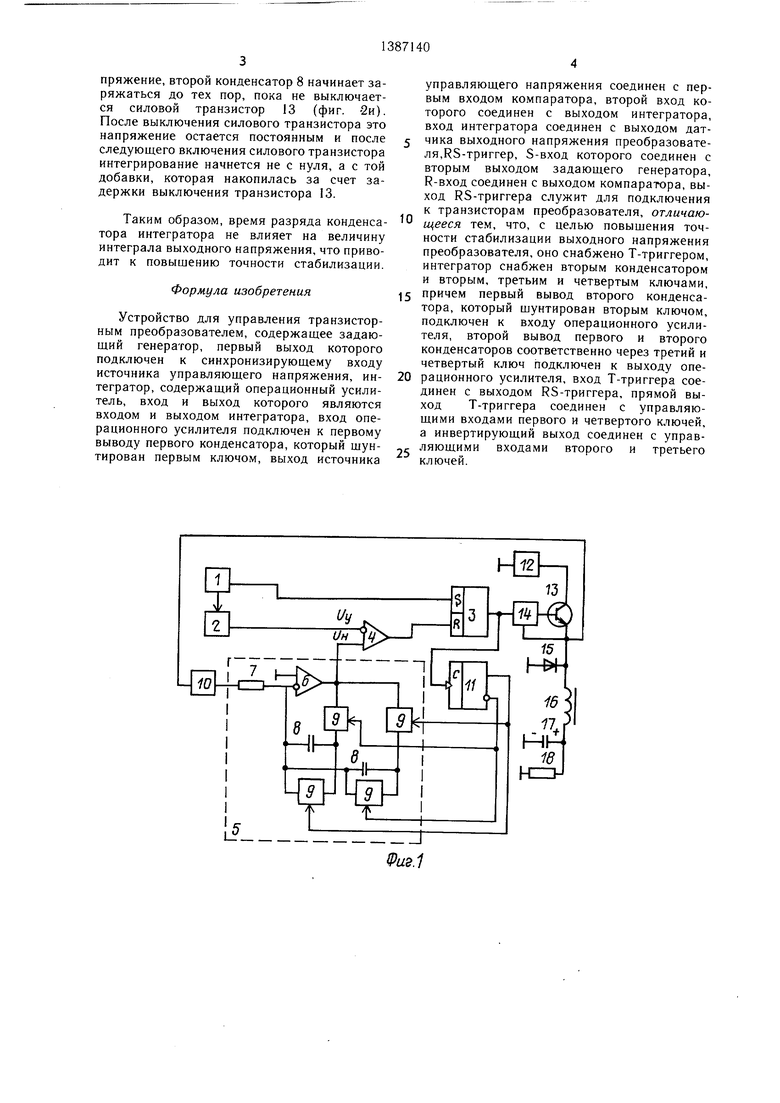

На фиг. 1 представлена функциональная схема устройства и один из вариантов схемы транзисторного преобразователя; на фиг. 2 - временные диаграммы, поясняющие работу устройства.

Устройство содержит (фиг. 1) задающий генератор 1, соединенный с источником 2 управляющего напряжения и одним входом RS-триггера 3, второй вход которого соединен с выходом компаратора 4, интегратор 5, состоящий из оперативного усилителя 6, резистора 7, конденсаторов 8, ключей 9, датчика 10 выходного напряжения преобразователя, соединенный с входом интегратора 5, Т-триггер 11, счетный вход которого подключен к выходу триггера 3, а выходы соединены с управляющими входами ключей 9.

Транзисторный преобразователь содержит источник 12 напряжения, силовой транзистор 13, усилитель 14 мощности, вход которого соединен с выходом RS-триггера, служащим для управления силовым транзистором, возвратный диод 15, дроссель 16, конденсатор 17 и нагрузку 18.

Устройство работает следующим образом.

Задающий генератор 1 вырабатывает узкие импульсы (фиг. 2а), которые подаются на вход триггера 3; переводя его в состояние с высоким потенциалом на выходе (фиг. 2д). Высокий потенциал, поступающий с выхода триггера 3 на вход усилителя 14, вызывает появление положительного тока управления силового транзистора 13 (фиг. 2е), что соответствует открытому состоянию транзистора 13 и появлению на его эмиттере положительного, а на выходе датчика 10 отрицательного напряжения, пропорционального мгновенному значению выходного напряжения (фиг. 26). Это напряжение, поступая на вход интегратора 5, приводит к линейному нарастанию напряжения на выходе интегратора (фиг. 2в). Время интегрирования определяется сопротивлением резистора 7 и емкостью конденсатора 8. Это время определяет длительность открытого состояния силового транзистора 13, необходимую для точной стабилизации выходного напряжения на уровне, заданном управляющим напряжением Uy.

Импульсы, формируемые триггером 3 (фиг. 2д), поступают на вход триггера 11, благодаря чему выходные сигналы триггера 11 переключаются в моменты спада импульсов триггера 3 (фиг. 2ж, э). Высокий потенциал выходных импульсов тригге0

ра 11 подключает вторые обкладки одного из конденсаторов 8 к выходу операционного усилителя 6 через ключи 9 и соответственно щунтирует другой конденсатор 8.

В момент времени t, когда напряжение

на выходе интегратора J« достигнет величины управляющего напряжения Uy, компаратор 4 на короткое время переходит из состояния с нулевым выходным потенциалом в состояние с высоким выходным потенциалом и на его выходе сформируется короткий импульс (фиг. 2г). Это происходит потому, что сформировавщийся на выходе компаратора 4 импульс, поступив на вход триггера 3, переводит его в состояние с

5 нулевым потенциалом на выходе (фиг. 2д), что соответствует отрицательному напряжению на базе силового транзистора 13, поступающему от усилителя 14. Ток базы меняет свое направление на противоположное (фиг. 2е) и начинается процесс рас0 сасывания избыточного заряда в базе. Процесс рассасывания избыточного заряда, в течение которого транзистор еще находится в открытом состоянии, закончится в тот момент, когда спадет практически до

5 нуля отрицательный ток базы (фиг. 2е). После этого только закроется силовой транзистор 13 и напряжение на его эмиттере и на выходе датчика 10 станет равным нулю. В этот же момент времени t нулевой потенциал на выходе тригге0 ра 3 (фиг. 2д) приводит к изменению состояния триггера 11 на противоположное (фиг. 2ж, з). Высокий потенциал управляющего входа ключа 9 (фиг. 2з) за- щунтирует первый конденсатор 8, заряженный к моменту времени t, и конденса5 тор 8 начинает разряжаться (фиг. 2к) на интервале времени т.

В предлагаемом устройстве погрещность стабилизации, возникающая из-за конечного времени разряда конденсатора, исключается тем, что высокий потенциал (фиг. 2з)

0 управляющего входа второго ключа 9 обеспечивает подключение второго конденсатора 8, разряженного в этот момент (фиг. 2и), к выходу операционного усилителя 6, а низкий потенциал управляющих входов соответствующих ключей 9 (фиг. 2ж) отклю5 чает первый конденсатор 8 от выхода интегратора 5 и подключает второй конденсатор 8. Все это приводит к резкому уменьшению напряжения на выходе интегратора 5 (фиг. 2в) и, следовательно, к очень быстрому переходу компаратора 4 опять в состояние с нулевым потенциалом на выходе независимо от инерционности цепи разряда первого конденсатора. После того как второй конденсатор 8 подключается к выходу опера5 ционного усилителя (в момент времени t фиг. 2), но еще не выключен силовой транзистор 13 и на входе фильтра преобразователя продолжает присутствовать на0

пряжение, второй конденсатор 8 начинает заряжаться до тех пор, пока не выключается силовой транзистор 13 (фиг. 2к). После выключения силового транзистора это напряжение остается постоянным и после следующего включения силового транзистора интегрирование начнется не с нуля, а с той добавки, которая накопилась за счет задержки выключения транзистора 13.

Таким образом, время разряда конденсатора интегратора не влияет на величину интеграла выходного напряжения, что приводит к повышению точности стабилизации.

Формула изобретения

Устройство для управления транзисторным преобразователем, содержащее задающий генератор, первый выход которого подключен к синхронизирующему входу источника управляющего напряжения, интегратор, содержащий операционный усилитель, вход и выход которого являются входом и выходом интегратора, вход операционного усилителя подключен к первому выводу первого конденсатора, который щун- тирован первым ключом, выход источника

0

управляющего напряжения соединен с первым входом компаратора, второй вход которого соединен с выходом интегратора, вход интегратора соединен с выходом датчика выходного напряжения преобразователя,RS-триггер, S-вход которого соединен с вторым выходом задающего генератора, R-вход соединен с выходом компаратора, выход RS-триггера служит для подключения к транзисторам преобразователя, отличающееся тем, что, с целью повыщения точности стабилизации выходного напряжения преобразователя, оно снабжено Т-триггером, интегратор снабжен вторым конденсатором и вторым, третьим и четвертым ключами,

5 причем первый вывод второго конденсатора, который шунтирован вторым ключом, подключен к входу операционного усилителя, второй вывод первого и второго конденсаторов соответственно через третий и четвертый ключ подключен к выходу опе0 рационного усилителя, вход Т-триггера соединен с выходом RS-триггера, прямой выход Т-триггера соединен с управляющими входами первого и четвертого ключей, а инвертирующий выход соединен с управляющими входами второго и третьего

5

ключей.

Ц-L

.

t-L

/ П/ 1/

L

r

и.

к

L

rt

Фи2.2.

Авторы

Даты

1988-04-07—Публикация

1986-01-29—Подача