Изобретение относится к импульсной технике и может быть использовано в системах с частотно-импульсным представлением информации и преобразователях типа аналог-цифра.

Известно устройство для преобразования напряжения в интервал времени [1], содержащее входную, выходную и общую шины, четыре компаратора, один из которых включен по схеме с двуполярным выходом, остальные - с однополярным, RS-триггер, интегрирующую RC-цепочку и источник установочного напряжения, при этом интегрирующая RС-цепочка, связанная с двуполярным компаратором, образуют управляемый RS-триггером интегратор с накопительным элементом - конденсатором.

Устройство работает следующим образом.

Когда выходное напряжение компаратора управляемого интегратора отрицательно, конденсатор интегрирующей RС-цепочки разряжается. Этому соответствует нулевое выходное напряжение RS-триггера (меньшее напряжения смещения, подаваемого на другой вход компаратора).

Когда при разряде конденсатора напряжение на нем сравняется с входным преобразуемым, компаратор, выход которого служит выходом преобразователя, включается и его выходное напряжение становится положительным, что соответствует формированию фронта выходного импульса.

Когда при продолжающемся разряде конденсатора напряжение на нем сравняется с нулем, компаратор, другой вход которого подключен к общей шине, а выход - к S-входу RS-триггера, включается, что приводит к переключению RS-триггера в единичное состояние и к превышению его выходного напряжения смещения на другом входе компаратора управляемого интегратора. Последний переключается, и его выходное напряжение становится положительным, что переключает процесс разряда конденсатора на процесс заряда.

При этом компаратор, один из входов которого подключен к общей шине, а выход - к S-входу RS-триггера, выключается (его выходное напряжение становится равным нулю).

При дальнейшем заряде конденсатора напряжение на нем сравнивается с входным преобразуемым, что выключает компаратор, другой вход которого подключен ко входной шине, а выход - к выходной шине преобразователя. В результате напряжение на выходной шине становится равным нулю. Это соответствует формированию среза выходного импульса преобразователя.

Описанное устройство-аналог имеет следующие недостатки:

1) сравнительно низкое быстродействие, обусловленное использованием линейных процессов для заряда и разряда накопительного элемента интегратора (конденсатора);

2) повышенное влияние наводок и шумов на точность преобразования, вызванное малыми углами встречи напряжения на конденсаторе с установочным напряжением и нулевым уровнем из-за необходимого выполнения при интегрировании (для получения приемлемой точности) условий

Uвых(-) << Uc(t) << Uвых(+), где Uвых(-) - выходное отрицательное напряжение компаратора управляемого интегратора;

Uвых(+) - его выходное положительное напряжение;

3) невысокую точность преобразования, обусловленную также применением в процессе формирования временного интервала четырех операций сравнения: двух - с установочным уровнем и двух - с нулевым (при малых углах встречи);

4) малую допустимую скорость изменения входного сигнала, так как она должна быть меньшей скорости изменения напряжения на конденсаторе, в то время как последняя скорость невелика из-за не- обходимого выполнения условий Uвых(-) << Uc(t) << Uвых(+), т.е. малого диапазона изменения напряжения Uc(t).

Наиболее близким по технической сущности к предложенному является устройство [2], содержащее цепь заряда накопительного элемента, цепь его разряда, схемы установки и удержания нулевых начальных условий, блок управления.

Цепь заряда накопительного элемента содержит вход с шиной преобразуемого сигнала, резистор, первый операционный усилитель, первый ключ и накопительный элемент.

Цепь разряда содержит источник опорного напряжения, второй резистор, второй операционный усилитель, второй ключ и накопительный элемент.

Схема установки нулевых начальных условий состоит из цепи разряда и нуль-органа в виде первого операционного усилителя с разомкнутыми ключами - первым и третьим.

Схема удержания нулевых начальных условий состоит из второго операционного усилителя с замкнутыми ключами - первым и четвертым, накопительного элемента, первого операционного усилителя с замкнутым третьим ключом и разомкнутым первым ключом.

Блок управления включает генератор тактовых импульсов, RS-триггер, схему И.

В работе этого устройства выделяются два чередующихся такта: первый - такт заряда накопительного элемента, второй - такт его разряда, установки и удержания нулевых начальных условий.

Тактирование осуществляется генератором тактовых импульсов.

В начале первого такта открывается первый ключ, закрывается второй и RS-триггер устанавливается в состояние "1", напряжение на его выходной шине падает до нуля, что вызывает размыкание третьего и четвертого ключей.

Размыкание третьего ключа при замкнутом первом приводит к заряду накопительного элемента - процессу интегрирования входного (преобразуемого) напряжения Ux

Ucзар(t) = -  Uxdt, (1) где R1 - сопротивление первого резистора; С - емкость накопительного элемента; Т - длительность первого такта генератора тактовых импульсов.

Uxdt, (1) где R1 - сопротивление первого резистора; С - емкость накопительного элемента; Т - длительность первого такта генератора тактовых импульсов.

По окончании первого такта первый ключ размыкается. В начале второго такта замыкается второй ключ, и накопительный элемент начинает разряжаться под воздействием опорного напряжения Uo с постоянной скоростью (-Uo/R2C):

Ucразр(t)= Ucзар(T) -

Uodt = Ucзар(T) -

Uodt = Ucзар(T) -  t, (2) где Uсзар(Т) - напряжение на накопительном элементе в конце первого такта; R2 - сопротивление второго резистора; Тх - время полного разряда.

t, (2) где Uсзар(Т) - напряжение на накопительном элементе в конце первого такта; R2 - сопротивление второго резистора; Тх - время полного разряда.

При этом длительность второго такта выбирается, исходя из обеспечения полного разряда накопительного элемента для всех значений Uсзар(Т).

В известном устройстве [2] накопительный элемент при включении его в схему разряда подключается отрицательной обкладкой к инвертирующему входу второго операционного усилителя, положительной - к его выходу, через второй ключ к инвертирующему входу первого операционного усилителя непосредственно.

Поэтому в начале процесса разряда напряжение на выходе первого операционного усилителя скачком падает до предельного отрицательного (Uвых(-)), а на выходе второго - от предельного положительного (Uвых(+)) - до напряжения Ucзар (Т) и далее линейно падает в соответствии с выражением (2) до нуля.

Время этого полного разряда Тx является результатом преобразования входного напряжения в интервал времени "Ux ->> Tx".

Когда напряжение Ucразр (t), уменьшаясь, сравняется с нулем (при t = Тх), напряжение на выходе первого операционного усилителя скачком возрастает от предельного отрицательного Uвых(-) до предельного положительного Uвых(+), т. е. данный операционный усилитель выполняет функцию нуль-органа преобразователя при разряде накопительного элемента (во втором такте).

Это скачкообразное повышение напряжения, будучи приложенным к R-входу RS-триггера, установит его в состояние "0", поэтому выходное напряжение триггера из нулевого "0" скачком превратится в единичное "1".

Последнее же напряжение откроет третий и четвертый ключи, что "заморозит" нулевые начальные условия на выходных шинах операционных усилителей, а за счет уже открытого второго ключа - и на обкладках конденсатора до начала следующего такта заряда.

После этого все описанные процессы преобразования напряжения в интервал времени повторятся: интегрирование входного напряжения в течение времени первого такта Т; полный разряд накопительного элемента в течение времени Тх; удержание и установка нулевых начальных условий.

Известное устройство (2) имеет следующие недостатки:

1) принципиальную невозможность преобразования мгновенных значений преобразуемого напряжения, так как преобразуемое напряжение должно быть постоянным, по крайней мере, в течение времени заряда накопительного элемента (первого такта преобразования);

2) ограниченный диапазон преобразуемого напряжения (только положительные значения), что вытекает из особенностей работы нуль-органа.

3) сравнительно невысокое быстродействие, определяемое линейностью обоих процессов: заряда и разряда, а также тем, что длительность разряда должна быть не менее преобразованного интервала времени;

4) совпадение частоты преобразования с частотой выходного сигнала, а не превышение ее;

5) невозможность получения высокой плотности записи, поскольку выходные импульсы преобразователя разделены временными промежутками.

Целью изобретения является обеспечение возможности преобразования мгновенных значений входного (преобразуемого) напряжения при высоком быстродействии.

Для достижения указанной цели в преобразователе напряжения в интервал времени, содержащем вход с шиной преобразуемого сигнала, цепь разряда накопительного элемента и цепь заряда накопительного элемента с общей шиной, блок управления и выход с шиной преобразованного сигнала, цепь разряда состоит из источника опорного напряжения, резистора, ключа на биполярном транзисторе, операционного усилителя, соединенного инвертирующим входом через резистор c иcточником опорного напряжения и непоcредcтвенно - c одним из выводов накопительного элемента, к другому выводу которого подключен через ключ выход операционного усилителя, неинвертирующий вход которого связан с общей шиной; цепь заряда накопительного элемента состоит из двух ключей на тиристорах, один из которых катодом соединен с общей шиной, анодом - с выводом накопительного элемента, подключенным к инвертирующему входу операционного усилителя цепи разряда, другой ключ с катодным управлением анодом подключен к "+" источника стабилизированного напряжения, катодом - к другому выводу накопительного элемента, а его шина катодного управления подключена к управляющему входу ключа цепи разряда и к выходу схемы поджига блока управления, вход которой подключен к выходу схемы запуска в блоке управления; в блоке управления неинвертирующий вход компаратора соединен с входом преобразователя с шиной преобразуемого сигнала, инвертирующий вход связан с выходом операционного усилителя цепи разряда и с одним из входов схемы запуска, другим входом через резистор связанной с генератором запуска, а через другой резистор - с "-" источника стабилизированного напряжения, выход компаратора подключен к третьему входу схемы запуска и к тактовому входу счетного триггера, выход которого является выходом преобразователя с шиной преобразованного сигнала.

Положительный эффект достигается за счет сокращения времени заряда накопительного элемента путем изменения линейного закона заряда на скачкообразный (импульсный).

На выходе преобразователя в результате получаются знакочередующиеся П-импульсы, у которых фронт каждого последующего является срезом предыдущего и которые содержат информацию в виде своей длительности о мгновенном значении преобразуемого входного напряжения на момент их окончания. Эти длительности являются суммой двух временных интервалов: малого интервала (времени заряда накопительного элемента) и много большего интервала, отражающего результат пре- образования мгновенного значения входного напряжения в его временной интервал, за счет чего практически момент окончания одного преобразования совпадает с началом следующего, что позволяет, во-первых, повысить временную плотность вырабатываемых интервалов; во-вторых, удвоить частоту преобразования по отношению к частоте следования выходных П-импульсов, каждый период следования которых, таким образом, содержит информацию о двух мгновенных значениях преобразуемого напряжения.

За счет деления частоты преобразования в два раза с помощью счетного триггера осуществлено эффективное подавление второй гармоники несущей частоты.

Известно, что частота преобразования в соответствии с теоремой отсчетов Котельникова-Шеннона должна быть выше или равна удвоенной частоте верхней спектральной составляющей преобразуемого сигнала. Отсюда следует, что частота следования выходных П-импульсов может быть выше частоты верхней спектральной составляющей или равна ей.

Поскольку величина вырабатываемого временного интервала практически совпадает с длительностью цикла преобразования, поскольку вырабатываемые временные интервалы являются максимально возможными, а ширина полосы частот выходных П-импульсов становится минимальной.

Отсюда полученные П-импульсы являются оптимальными для использования в системах магнитной записи информации и передачи ее в линиях связи с частотно-импульсным представлением сигналов.

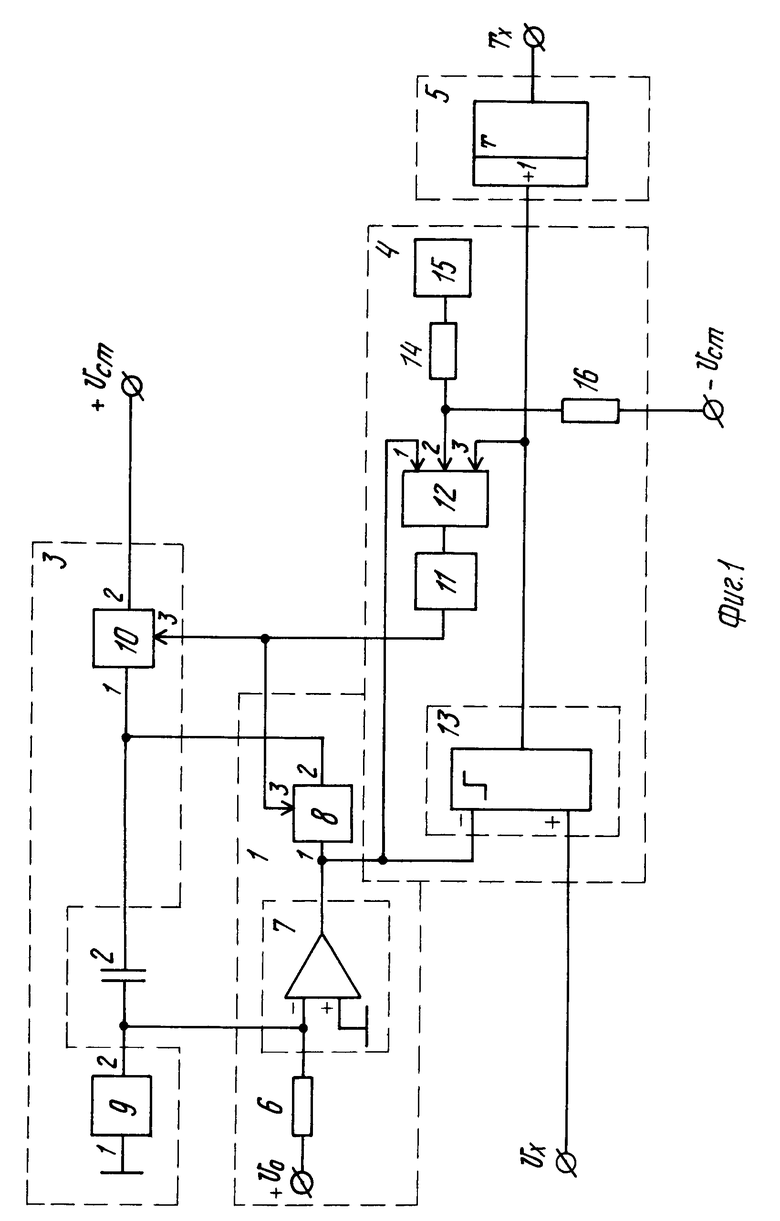

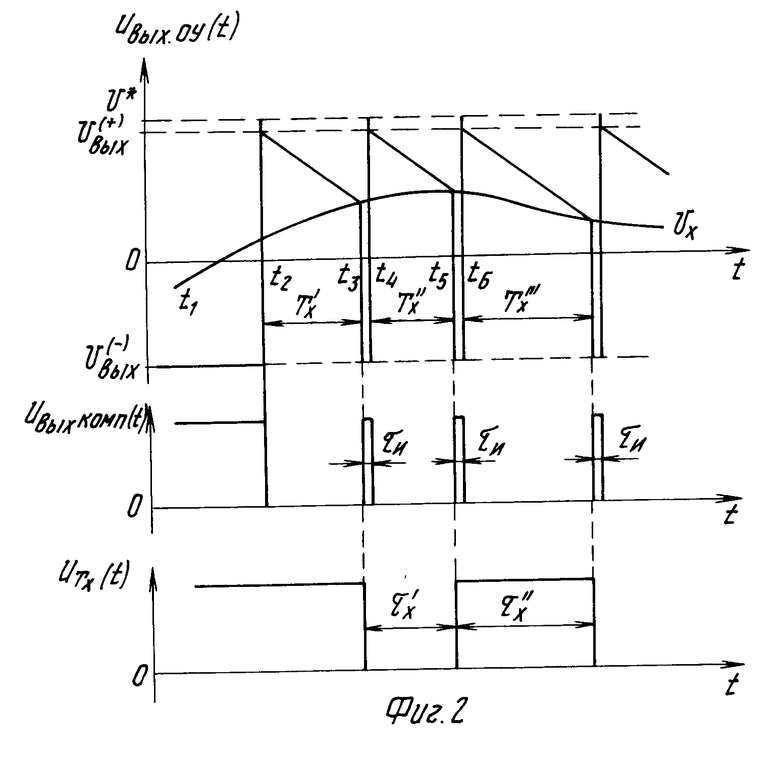

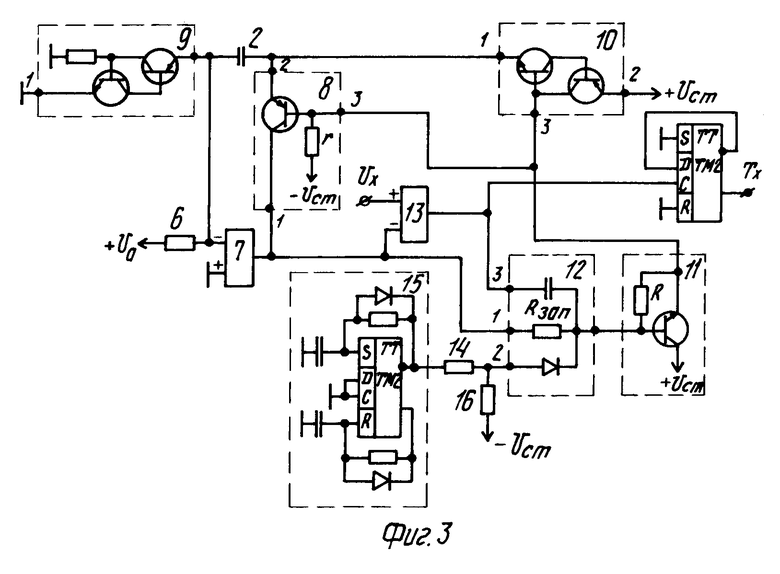

На фиг. 1 изображена блок-схема преобразователя напряжения в интервал времени; на фиг.2 - временные диаграммы работы преобразователя напряжения в интервал времени; на фиг.3 - принципиальная схема преобразователя.

Преобразователь напряжения в интервал времени (фиг.1) содержит вход с шиной преобразуемого сигнала Ux, цепь разряда 1 накопительного элемента 2 и цепь его заряда 3 с общей шиной, блок 4 управления, соединенный со счетным триггером 5, выход которого является выходом преобразователя с шиной преобразованного сигнала Тх.

Цепь разряда 1 (фиг.1,3) состоит из источника опорного напряжения Uo, соединенного через резистор 6 с инвертирующим входом операционного усилителя 7, подключенного к одному из выводов накопительного элемента 2, неинвертирующий вход операционного усилителя 7 связан с общей шиной, а выход - с другим выводом накопительного элемента через ключ 8.

Ключ 8 выполнен на биполярном p-n-p-транзисторе, у которого вывод 1 - коллектор, вывод 2 - эмиттер, вывод 3 - база, соединенная через резистор r с "-" - источника стабилизированного напряжения.

Цепь заряда 3 состоит из двух ключей 9, 10 на тиристорах, выполненных составными на биполярных транзистоpах разной проводимости с малым временем рассасывания. Один из ключей 9 катодом (вывод 1) соединен с общей шиной, анодом (вывод 2) с выводом накопительного элемента 2, подключенным к инвертирующему входу операционного усилителя 7. Другой ключ 10 с катодным управлением анодом (вывод 2) подключен к "+" источника стабилизированного напряжения (+Uст), катодом (вывод 1) - к другому выводу накопительного элемента 2, а его шина (вывод 3) катодного управления подключена к управляющему входу (вывод 3) ключа 8 цепи разряда 1 и к выходу схемы 11 поджига блока 4 управления, вход которого подключен к выходу схемы 12 запуска в блоке 4 управления.

Блок 4 управления состоит из схемы 11 поджига, схемы 12 запуска, компаратора 13, делителя напряжения на резисторах 14, 16 и генератора 15 запуска (фиг.1,3).

Схема 11 поджига состоит из усилителя мощности в виде эмиттерного повторителя, нагруженного на резистор r ключа 8 и выходом (эмиттером) подключенного к шине (вывод 3) катодного управления ключа 10 и управляющему входу (вывод 3) ключа 8, управляющим входом (базой) - к выходной шине схемы 12 запуска, коллектором - к "+" источника стабилизированного напряжения (фиг.1,3).

Схема 12 запуска (функциональная схема ИЛИ) состоит из трех раздельных входных цепей, соединенных выходами в общую точку с выходной шиной.

Первой входной цепью, подключенной ко входу 1 схемы, является резистор Rзап; второй входной цепью, соединяющей вход 2 с выходной шиной - ключ на полупроводниковом импульсном диоде с малой емкостью, подключенном анодом ко входу 2 схемы, катодом - к выходной шине схемы; в качестве третьей входной дифференцирующей цепи, соединяющей вход 3 с выходной шиной схемы, используется конденсатор малой емкости.

В блоке 4 управления неинвертирующий вход компаратора 13 соединен со входом преобразователя, инвертирующий вход связан с выходом операционного усилителя 7 цепи разряда и с одним (вывод 1) из входов схемы 12 запуска, другим входом (вывод 2) через резистор 14 связанной с генератором 15 запуска, а через резистор 16 - с "-" источника стабилизированного напряжения, выход компаратора 13 подключен к третьему входу схемы 12 запуска и к тактовому входу счетного триггера 5, выход которого является выходом преобразователя с шиной преобразованного сигнала Тх.

В преобразователе напряжения в интервал времени накопительный элемент может быть выполнен в виде конденсатора типа КМ ОЖО.460.161ТУ, ключ схемы разряда - на биполярном транзисторе типа КТ 363А(В) ШТО, ШТО.336.014ТУ; ключи в схеме заряда - составные тиристоры на биполярных транзисторах типа КТ 363А(В) ЩТО.336.014ТУ КТ 316А(В) СБО.336.030 ТУ; операционный усилитель - микросхема 544УД2; компаратор - микросхема типа К554СА3; схема запуска включает в себя резистор, импульсный диод КД 520А и конденсатор типа К10-17 ОЖО.460.167ТУ, схема поджига выполнена в виде усилителя мощности на эмиттерном повторителе на биполярном транзисторе типа 2Т316А СБО.336.О30ТУ; генератор запуска выполнен на мультивибраторе, в качестве которого использована половина микросхемы типа 564ТМ2 с делителем напряжения на резисторах, а счетный триггер выполнен в виде второй половины указанной микросхемы.

Преобразователь работает следующим образом.

При подключении преобразователя к источнику питания в момент t1 на инвертирующий вход операционного усилителя (ОУ) 7 (фиг.1) через резистор 6 подается опорное напряжение +Uо (фиг.1), открывающее ключ 9, вследствие чего на инвертирующем входе ОУ 7 устанавливается положительное напряжение Uоткр., практически ≈ 1,0 В, что меньше значения Uоткр = 1,5 В стандартных динисторов малой мощности, что приводит к установлению самого низкого отрицательного напряжения (напряжения отрицатель- ного уровня (Uвых(-)) на выходе ОУ 7 (фиг.2), которое всегда ниже любого значения преобразуемого напряжения: Uх > Uвых(-).

Следовательно, входной сигнал компаратора 13, равный разности U+-U- = Ux - Uвых(-) только положителен, компаратор 13 включен, на его выходе постоянное положительное напряжение (напряжение положительного уровня) Uвых(+), которое не в состоянии через вход 3 схемы 12 запуска осуществлять запуск схемы 11 поджига (фиг.1,2,3).

Кроме того, поскольку U(-)вых > - Uст, причем напряжение Uвых(-)подано на коллектор транзистора ключа 8, а напряжение (-Uст) - через резистор r на его базу, p-n-переход коллектор-база транзистора открывается. Последнее же приводит к отпиранию (в инверсном режиме) ключа 8, практически выравниванию потенциалов его эмиттера ϕ2 и коллектора ϕ1 и установлению на его базе потенциала ϕ3≈ϕ1= 0,7 В ≈ϕ2= 0,7 В, т.е. установлению прямого входного напряжения ключа.

А поскольку, как следует из принципиальной схемы преобразователя (фиг. 3), прямое входное напряжение ключа 8 является обратным входным ключа 10 и наоборот, ключ 10 заперт, его максимально допустимое прямое напряжение в закрытом состоянии Uпр,закр,max, Т повышено.

При этом к делителю напряжения, состоящему из резисторов Rзап схемы 12 и R схемы 11 приложено напряжение ≈ 0,7 В плюсом к резистору Rзап, минусом - к R, т.е. на входе транзистора схемы 11 поджига прямое напряжение.

Но поскольку сопротивление резистора Rзап составляет сотни кОм, а резистора R лишь десятки, т.е. в данном случае смещение +0,7 В, вырабатываемое транзистором ключа 8, мало и лишь подготавливает транзистор схемы 11 поджига к открыванию. При этом потенциалы базы и эмиттера последнего отрицательные и самые низкие: Uвых.ОУ = Uвых(-).

С дугой cтороны, делитель напряжения, cоcтоящий из резиcторов 14, 16, cконcтруирован таким образом, чтобы единичный (положительный) импульc U1 генератора был бы доcтаточен в данном cлучае (при Uвых.ОУ = Uвых(-)) для открывания ключа на диоде (по входу 2) схемы 12 запуска и последующего запуска схемы 11 поджига.

Чтобы в дальнейшем генератор 15 запуска не запускал схему 11 поджига, срывая процесс преобразования, ограничиваем снизу диапазон изменения входного сигнала Ux: 0 > Uxmin > Uвых(-). Выходное напряжение ОУ 7 Uвых.ОУ изменяется в пределах Uвых(+) ≥ Uвых.ОУ ≥ Uх, где Uвых(+) - напряжение положительного уровня.

Итак, под воздействием "единичного" импульса генератора 15 запуска (стартера) в момент времени t2 (после включения) (фиг.2) схема 11 поджига вырабатывает первичный импульс поджига, поступающий на шину (3) катодного управления тиристора 10 и вход (3) ключа 8. При этом тиристор 10 поджигается, а ключ 8 размыкается и отключает выход ОУ 7 от цепи (3) заряда накопительного элемента 2 (конденсатора).

Вследствие поджига тиристора 10 напряжение на его катоде (1) скачком возрастает от максимально отрицательного до максимально положительного U* > Uвых(+), равного разности напряжений +Uст и Uоткр., где Uоткр. - остаточное падение напряжения на открытом тиристоре 10, а Uвых(+) - максимальное положительное напряжение на выходе ОУ 7 (напряжение положительного уровня).

Поскольку ключ 9 в это же время уже открыт напряжением Uо, то создается цепь импульсного заряда конденсатора 2 (+Uст - тиристор 10 - конденсатор 2 - тиристор 9 - общая шина), причем тиристор 10 используется в транзисторном включении с катодным (3) управлением, а тиристор 9 - в динисторном. Время заряда конденсатора при такой цепи заряда измеряется десятыми долями микросекунды, а напряжение на конденсаторе 2 будет максимальным и равным Uсо = + Uст - 2Uоткр.

Во время заряда полярность напряжения на инвертирующем входе ОУ 7 остается положительной, что обеспечивает на его выходе сохранение максимального отрицательного напряжения Uвых(-).

После поджига составного тиристора ключа 10 оба его транзисторы переключаются в режим насыщения, при котором между катодом (1) тиристора 10 (эмиттером выходного транзистора) и управляющим электродом (УЭ) (его базой) возникает смещение ≈ + 0,7 В, приложенное плюсом к базе транзистора ключа 8, минусом - к эмиттеру последнего, запирающее ключ 8 и уменьшающее в дальнейшем время его выключения (фиг.2,3).

Кроме того, вхождение в режим насыщения транзистора ключа 10 приводит к скачкообразному повышению напряжения и на УЭ ключа от ≈ Uвых(-) практически до напряжения +Uст. В результате делитель напряжения, состоящий из резисторов: R схемы 11 поджига и Rзап схемы 12 запуска (где R измеряется десятками кОм, а Rзап - сотнями), оказывается под воздействием двух потенциалов: + Ucт и Uвых(-).

Это приводит к тому, что, во-первых; к входу транзистора схемы 11 поджига прикладывается обратное напряжение, ускоряющее его выключение; во-вторых, потенциал катода диода-ключа схемы 12 запуска становится и в дальнейшем остается (в силу условия Uхmin > Uвых(-)) выше потенциала его анода, и ключ на диоде запирается, отключая делитель, состоящий из ре- зисторов 14, 16, от выхода схемы 12 запуска.

Поскольку ключ на диоде (вход 2) схемы 12 запуска после поджига тиристора ключа 10 запирается, отключая делитель напряжения на резисторах 14, 16, то генератор 15 запуска никакого влияния в дальнейшем на работу преобразователя не оказывает (при соблюдении условия Uх ≥ Uxmin, где Uхmin < О - минимальное входное напряжение Ux, при котором при выбранных сопротивлениях 14 и 16 ключ на диоде схемы 12 запуска не открывается.

По окончании заряда накопительного элемента 2 оба транзистора ключа 10 закрываются: ток тиристора становится меньше тока удержания Iуд.Т, а на УЭ отсутствует управляющий импульс.

При этом, во-первых, исчезает положительное смещение ≈ + 0,7 В между УЭ (3) тиристора 10 и его катодом (1), запиравшее ключ 8; во-вторых, потенциал эмиттера транзистора ключа 8 максимален и равен U* = +Uст - Uоткр.Т, а его база подключена через резистор r к -Uст. В результате p-n-переход эмиттер-база ключа 8 открывается, подключая положительную обкладку заряженного конденсатора 2 с потенциалом U* = Uст - Uоткр. к низкоомному выходу ОУ 7 с отрицательным потенциалом Uвых(-) (фиг.1,2,3).

В результате возникает отрицательный перепад напряжения на выводе (2) ключа 8, который, пройдя через конденсатор 2 на анод (2) ключа 9 и инвертирующий вход ОУ 7, выключает ключ 9 и изменяет на обратную полярность сигнала на инвертирующем входе ОУ 7.

Спустя время задержки в ОУ 7 (tзад ≈ 1,5 мкс для выбранной микросхемы в макете) в момент t2 выходное напряжение его скачком изменится от Uвых(-) до Uвых(+) и ОУ 7 включается в качестве звена глубокой отрицательной обратной связи по току в цепь разряда накопительного 2 элемента (фиг.1,2,3).

При этом напряжение, приложенное к делителю напряжения на резисторах Rзап и R, изменяется от напряжения U' ≈ Uвых(-) - (+ Uст) << 0 до напряжения U'' ≈ + 0,7 В, причем напряжение U' превосходит напряжение U'' по величине в десятки раз. Кроме того, сопротивление резистора Rзап, как отмечалось выше, измеряется сотнями кОм, а резистора R - десятками кОм (фиг.3).

По этим причинам после включения ключа 10 на тиристоре транзистор схемы 11 поджига практически сразу же запирается обратным достаточно большим входным напряжением Uвх' ≈ - U'R/Rзап, тогда как после выключения ключа 10 и включения ключа 8 выработка им напряжения смещения U'' и изменения выходного напряжения ОУ 7 до уровня Uвых(+) входное напряжение схемы 11 поджига становится прямым Uвх'' ≈ + U''R/Rзап≈ 0, но недостаточным для ее открывания (фиг.3).

Поэтому с помощью входа (1) схемы 12 запуска осуществляется форсированное выключение транзистора схемы 11 поджига после включения ключа 10, что необходимо для сокращения длительности τи (фиг.2) и улучшения линейности пилы, вырабатываемой схемой 1 разряда накопительного 2 элемента (фиг.1,2).

После того как в момент t2 напряжение на выходе ОУ 7 станет равно Uвых(+) и произойдет включение ОУ 7 в цепь разряда накопительного 2 элемента в качестве звена глубокой отрицательной обратной связи по току (фиг. 1,2,3) при выключенных ключах 9,10, запертом транзисторе схемы 11 поджига и открытом ключе 8 схемы 1 разряда накопительного 2 элемента вместе с ним образуют интегратор опорного напряжения +Uо с ненулевыми (максимальными) начальными условиями: Uс2(0) ≈ Uвых(+) = Max.

Вследствие этого на выходе ОУ 7 появится линейно изменяющееся напряжение (фиг.2):

Uвых.ОУ(t-t2)= U

Uodt= U

Uodt= U (t-t2), (1) где τ = R6C2; Uвых(+) - выходное напряжение положительного уровня ОУ 7, а t2 ≅ t < t3 (фиг.1,2,3).

(t-t2), (1) где τ = R6C2; Uвых(+) - выходное напряжение положительного уровня ОУ 7, а t2 ≅ t < t3 (фиг.1,2,3).

Отсюда ясно, что верхний положительный предел входного напряжения Uxmax должен быть всегда ниже величины Uвых(+).

В течение времени, пока выходное напряжение ОУ 7 Uвых.ОУ (t-t2)> Ux(t), входной сигнал компаратора 13 U+ -U- = Ux(t) - Uвых.ОУ(t-t2) отрицателен, компаратор 13 выключен и его выходное напряжение равно нулю.

Когда же в момент времени t3 входной сигнал компаратора 13 сравнивается с нулем

Ux(t3) - Uвых.ОУ (t3-t2) = 0, (2) компаратор включается и на его выходе появляется положительный перепад (фиг.1,2).

Таким образом, время Tx' = t3-t2 линейного разряда конденсатора 2 до напряжения Ux(t3) можно на основании выражений (1), (2) выразить в виде

T =τ

=τ  . (3)

. (3)

Выработанный при включении компаратора 13 (фиг.1) перепад переключит счетный триггер 5 и поступит на вход (3) схемы 12 запуска, являющийся дифференцирующим.

В схеме 12 запуска положительный перепад напряжения, выработанный компаратором 13 и поступивший на вход (3) схемы 12 и тактовый вход счетного триггера 5, продифференцируется и в виде положительного остроконечного импульса малой длительности после усиления по мощности схемой 11 поджига поджигает ключ 10 на тиристоре, и далее описанные процессы повторяются, за исключением отпирания запертого ключа 9 на динисторе.

На этом первый цикл преобразования в интервал времени Tx' мгновенного значения напряжения Ux (на момент t3 - момент совпадения пилы, вырабатываемой интегратором, с напряжением Uх) заканчивается (фиг.2).

Рассмотрим процесс отпирания ключа более подробно.

После поджига тиристора ключа 10 на его катоде (1) напряжение скачком возрастает от преобразованного (текущего) значения Ux до фиксированного уровня U* = +Uст - Uоткр.

Этот перепад Δ U = U* - Uх(t3) через конденсатор 2 поступает на анод (2) ключа 9 на динисторе, потенциал которого, как и потенциал инвертирующего входа ОУ 7, равен U- = - Ux/Ku ≈ 0, где Ku > 700о - коэффициент усиления по напряжению для выбранной микросхемы ОУ.

Отсюда следует, что перепад Δ U должен быть больше импульсного отпирающего напряжения тиристора:

Δ U > Uот.и.т (4) или

Ux < U* - Uот.и.т . (5)

Отсюда условие (4) очевидно, необходимо для обеспечения непрерывности процесса преобразования путем автозапуска устройства каждый раз при выполнении условия (2), что, в свою очередь, необходимо для повышения временной плотности вырабатываемых интервалов Тх, а условие (5) - для определения максимального значения преобразуемого напряжения

Uxmax ≅ U* - Uот.и.т. (6)

Далее отметим, что, когда напряжение на выходе ОУ 7 в момент t4(фиг.2) превысит Uх (в силу описанных процессов), напряжение на выходе компаратора 13 вновь станет равно нулю, как в интервале t2 < t < t3(фиг.2).

Итак, в момент t4 напряжение на выходе ОУ 7 вновь станет максимальным и равным Uвых(+), после чего начнется второй цикл преобразования Ux(t5) ->> Tx'' (фиг.2).

Как следует из фиг.2, с момента совпадения входного сигнала компаратора 13 с нулем в момент t3 (t5,...) до момента t4 (t6,...), когда напряжение на выходе ОУ 7 становится равным Uвых(+), проходит время τи≈ const.

Это объясняется тем, что в это время происходит включение компаратора, нарастание выходного сигнала, включение ключей 10, 9, выключение ключа 8 и заряд накопительного 2 элемента, спад выходного сигнала ОУ 7 от уровня Ux t3(t5, ...) до уровня Uвых(-), выключение ключей 10, 9, включение ключа 8 и нарастание выходного сигнала ОУ 7 до уровня Uвых(+) (с последующим выключением компаратора).

В действующем макете преобразователя время τи получилось равным 2,1 мкс, т.е. условие Tх >> τи легко выполнимо путем подбора опорного напряжения +Uo и постоянной времени цепи разряда τ = R6C2.

В результате работы преобразователя на его выходной шине получаем сигнал в виде знакочередующихся П-импульсов, каждый из которых имеет длительность τx = Тх + τи≈ Тх, где τи = const.

При этом каждый П-импульс содержит информацию о мгновенном значении преобразуемого входного сигнала на момент его окончания в виде составляющей Тх длительности (интервала) τx, а не его интеграла по времени в течение такта заряда накопительного элемента, что повысило точность преобразования при изменяющемся входном напряжении Uх(t).

Кроме того, повышено быстродействие за счет изменения линейного закона заряда накопительного элемента на скачкообразный, исключения времени удержания нулевых начальных условий от момента окончания одного преобразования до начала следующего цикла преобразования, а также асинхронного характера работы преобразователя (в прототипе - синхронный характер с Тпреобр. = max, определяемым максимальным значением преобразуемого сигнала Uxmax).

Таким образом, положительный эффект при предлагаемом преобразовании достигается за счет сокращения времени заряда накопительного элемента в максимально возможной степени таким образом, чтобы время цикла преобразования практически состояло бы из времени быстрого заряда накопительного элемента до фиксированного значения и времени последующего, сравнительно медленного линейного его разряда до совпадения этого линейно-изменяющегося напряжения с текущим значением преобразуемого напряжения Ux, после чего должен снова следовать быстрый заряд накопительного элемента и последующий линейный разряд и т.д.

При таком подходе дополнительно обеспечивается возможность преобразования не только положительных, но и отрицательных напряжений Ux.

При этом при равенстве +Uст = Uип1, -Uст = Uип2 был практически достигнут следующий рабочий диапазон изменения преобразуемого напряжения Ux:

-Uст + (2,4 ± 0,10)В ≅ Ux ≅ +Uст -

(4,8 ± 0,10)В.

Для осуществления быстрого заряда накопительного элемента необходимо использовать ключи, в качестве которых можно использовать переключатели электрических сигналов (токовые ключи), например К149КТ, последовательные интегральные прерыватели, например К162КТ1, аналоговые ключи со схемами управления, например 590КН4, тиристоры например, 2У105Б, КУ101А и др.

Из всех видов ключей наибольший коммутируемый импульсный ток у тиристоров (до нескольких ампер), у всех остальных - единицы - сотни миллиампер.

Кроме того, тиристоры обладают свойством автоматически отключаться, когда ток, протекающий через них, становится меньше удерживающего тока при малых напряжениях в открытом состоянии.

Иными словами, тиристор достаточно открыть даже коротким импульсом, а закроется он автоматически только после заряда накопительного элемента до фиксированного напряжения. Во время заряда в тиристоре (тринисторе) вырабатывается (при катодном управлении) положительное смещение, которое можно использовать для удержания ключа 8 в закрытом состоянии, используя общие цепи управления этого ключа и тиристора (ключа 10), с тем чтобы короткий импульс поджига последнего закрывал одновременно ключ 8, а по окончании заряда, наоборот, ключ 8, автоматически открываясь, вырабатывал бы, в свою очередь, напряжение смещения, являющееся обратным по отношению к полярности импульса поджига и удерживающее тиристор (ключ 10) в запертом состоянии в течение всего времени выработки линейно-изменяющегося напряжения схемой 1 разряда (до выработки следующего импульса поджига).

Кроме того, поскольку тиристоры представляют собой четырехслойные структуры p-n-p-n-типа, т. е. в электрическом отношении эквивалентны двум p1-n1-p1- и n2-p2-n2-транзисторам, соединенным следующим образом: база (n1)

первого - с коллектором (n2) второго, коллектор (p1) первого - с базой (p2) второго. У полученного таким образом составного тиристора эмиттер (p1) первого транзистора является анодом, эмиттер (n2) второго - катодом, база (p2) второго, коллектор (p1) первого - управляющим электродом (УЭ) катодного управления.

Подбирая транзисторы с соответствующими параметрами, можно получать тиристоры с необходимыми свойствами, в частности, по времени включения tвкл, выключения tвыкл, по импульсному отпирающему напряжению Uот.и.Т, в том числе на УЭ тринистора Uу.от.и.Т, по максимально допустимому постоянному прямому напряжению в закрытом состоянии Uпр.закрmaxT (напряжению отпирания), по максимально допустимому импульсному току в открытом состоянии Tоткр.иmax и т.д.

За счет достигнутого положительного эффекта в результате преобразования выходные знакочередующиеся импульсы стали иметь максимально возможную плотность во времени: фронт каждого последующего импульса стал служить одновременно срезом предыдущего.

Частота Fвых сигнала на выходной шине Тх за счет деления частоты выходных импульсов компаратора 13 триггером 5 в два раза ниже частоты преобразования Fх, равной частоте выходных импульсов компаратора 13, что приводит к сужению полосы частот, вырабатываемых преобразователем сигналов (знакочередующихся П-импульсов) и, что очень важно для снижения уровня комбинационных помех, к эффективному подавлению второй гармоники несущей.

Частоту преобразования Fх = 1/τx всегда можно определить по теореме отсчетов Котельникова-Шеннона, выбирая ее по соотношению Fx ≥ 2Fв, где Fв - верхняя частота спектра входного (преобразуемого) сигнала, которая, в свою очередь, легко определяется по спектроанализатору.

Поэтому практически длительность цикла преобразования

τx = 1/Fx ≅ 1/2Fв.

Кроме того, за счет того, что τи < Тх, получаем для определенной по теореме отсчетов Котельникова-Шеннона длительности цикла преобразования τx≅ 1/2Fв и равного τx = Тх + τи , максимально возможные интервалы Тх, что также приводит к расширению каждого вырабатываемого П-импульса.

Таким образом, полученные в результате преобразования П-импульсы обладают наибольшей плотностью во времени и наиболее узким спектром частот, что дает возможность использовать преобразователь в качестве модулятора в устройствах магнитной видеозаписи и передачи информации в линиях связи с частотно-импульсным представлением данных, а также в аналого-цифровых преобразователях с высоким быстродействием при преобразовании входных напряжений Ux как положительной, так и отрицательной полярности.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ ИНТЕРВАЛА ВРЕМЕНИ В ПОСТОЯННОЕ НАПРЯЖЕНИЕ | 1990 |

|

RU2007028C1 |

| Логарифмический аналого-цифровой преобразователь | 1990 |

|

SU1725397A1 |

| Аналого-цифровой преобразователь | 1989 |

|

SU1697265A1 |

| Преобразователь напряжения в частоту | 1988 |

|

SU1522407A1 |

| Способ аналого-цифрового преобразования и устройство для его осуществления | 1990 |

|

SU1837395A1 |

| Устройство время-импульсного преобразования постоянного напряжения в код | 1982 |

|

SU1091333A1 |

| Логарифмический аналого-цифровой преобразователь | 1982 |

|

SU1042036A1 |

| Аналого-цифровой преобразователь интегрирующего типа | 1977 |

|

SU752795A1 |

| Аналого-цифровой преобразователь двухтактного интегрирования | 1988 |

|

SU1515367A2 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С ПРОМЕЖУТОЧНЫМ ПРЕОБРАЗОВАНИЕМ В ЧАСТОТУ | 1990 |

|

RU2007029C1 |

Изобретение относится к импульсной технике и может быть использовано в системах магнитной записи информации и передачи ее в линиях связи с частотно-импульсным представлением данных. Цель изобретения - обеспечение преобразования мгновенных значений входного напряжения при высоком быстродействии. С этой целью в преобразователе напряжения в интервал времени, содержащем цепь разряда накопительного элемента, включающую ключи, операционный усилитель, инвертирующий вход которого соединен с первым выводом накопительного элемента, связанного через резистор с источником опорного напряжения, неинвертирующий вход соединен с общей шиной, а выход через ключ связан с вторым выводом накопительного элемента, и цепь заряда накопительного элемента с общей шиной, блок управления, а также вход с шиной преобразуемого сигнала и выход с шиной преобразованного сигнала, цепь заряда накопительного элемента выполнена в виде двух ключей на тиристорах, один из которых катодом соединен с общей шиной, анодом - с первым выводом накопительного элемента, другой ключ анодом подключен к полюсовому выходу источника стабилизированного напряжения, катодом - к другому выводу накопительного элемента, а его шина катодного управления подключена к выводу схемы поджига блока управления в виде усилителя мощности, входом соединенной с выходом схемы запуска блока управления, в котором неинвертирующий вход компаратора соединен с шиной преобразуемого сигнала, инвертирующий вход - с выходом операционного усилителя цепи разряда накопительного элемента и с первым входом схемы запуска, вторым входом связанной через резистор с генератором запуска блока управления, а через другой резистор - с минусовым выходом источника стабилизированного напряжения, выход компаратора подключен к третьему входу схемы запуска и к тактовому входу счетного триггера, выход которого является выходом преобразователя с шиной преобразованного сигнала. Схема запуска выполнена в виде сборки из трех раздельных цепей, состоящих из резистора, ключа на диоде и конденсатора, общая точка соединения которых является выходом схемы, при этом первым входом служит вывод резистора, вторым - анод диода ключа, третьим - вывод конденсатора. 1 з.п. ф-лы, 3 ил.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Преобразователь напряжения в интервал времени | 1985 |

|

SU1474845A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1995-03-27—Публикация

1991-06-07—Подача