оо со ьо ел - со

Изобретение относится к технике связи и вычислительной технике и может быть использовано при проектировании систем передачи и обработки информации.

Целью изобретения является расширение функциональных возможностей устройства путем моделирования запоминания переда- даваемых сообщений до получения квитанций об их приеме.

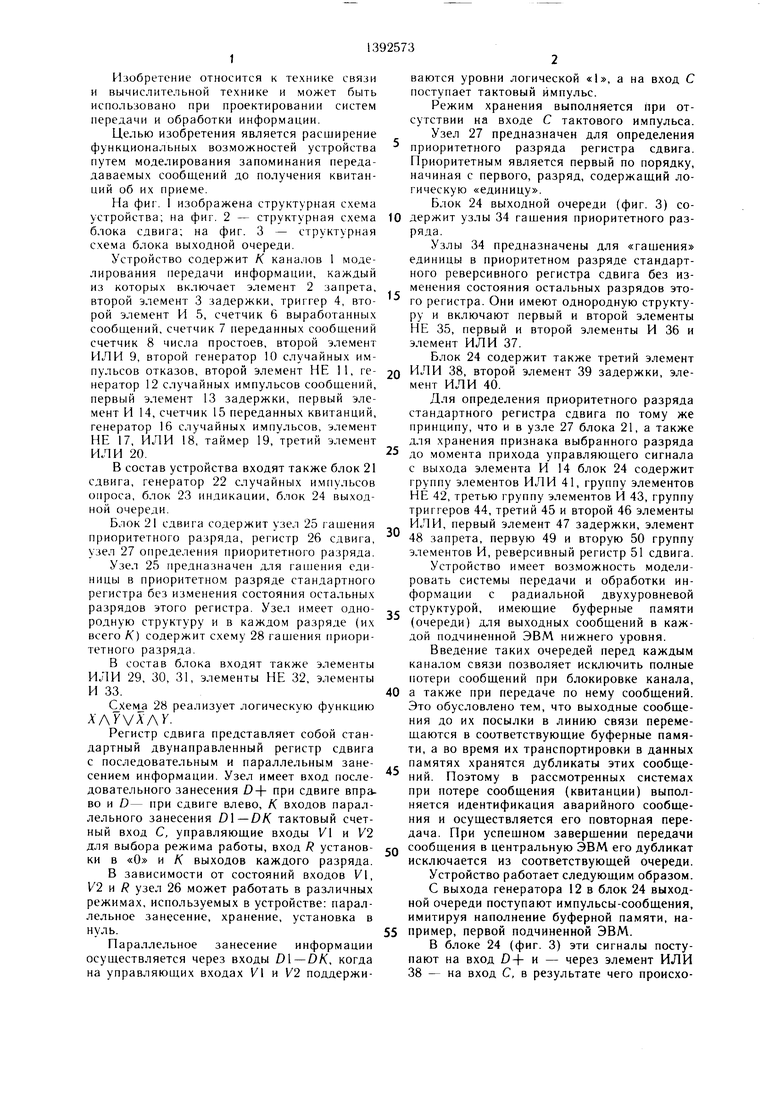

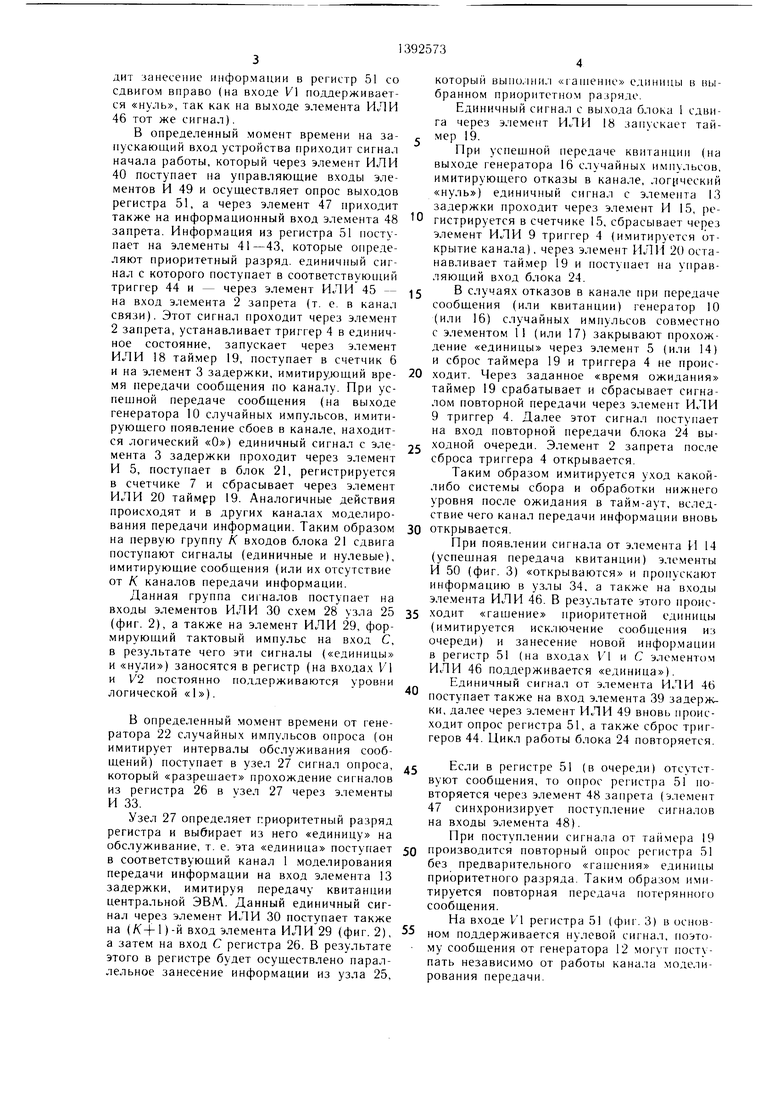

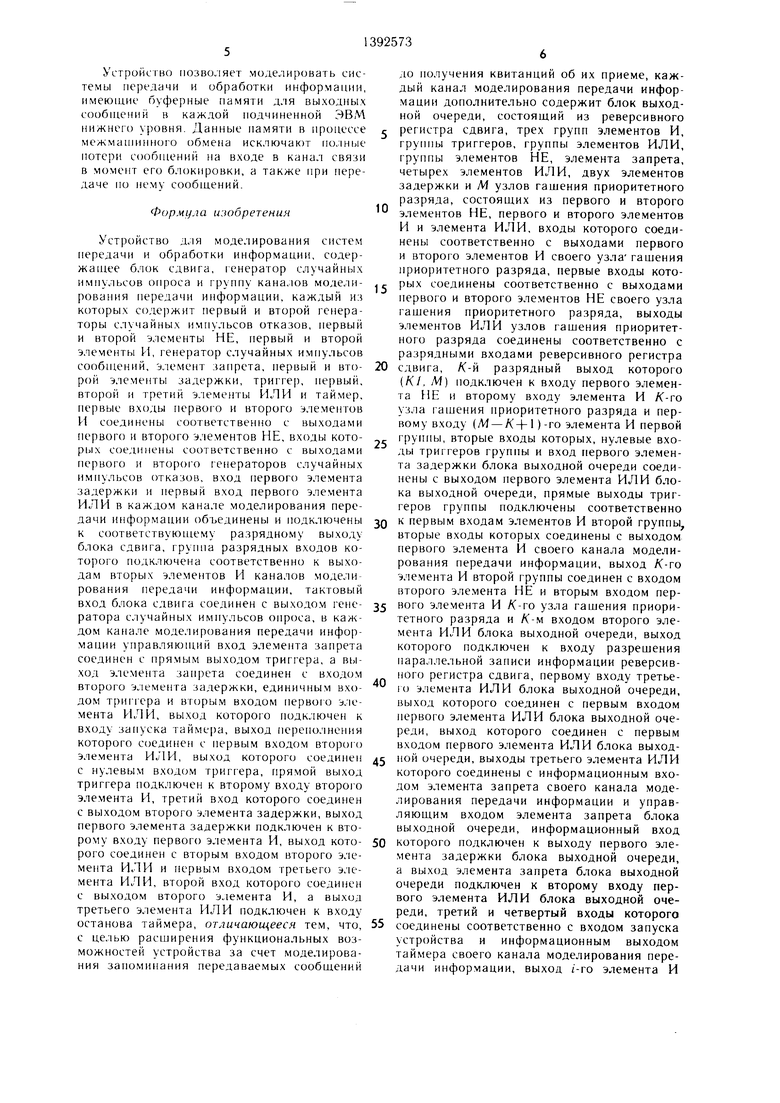

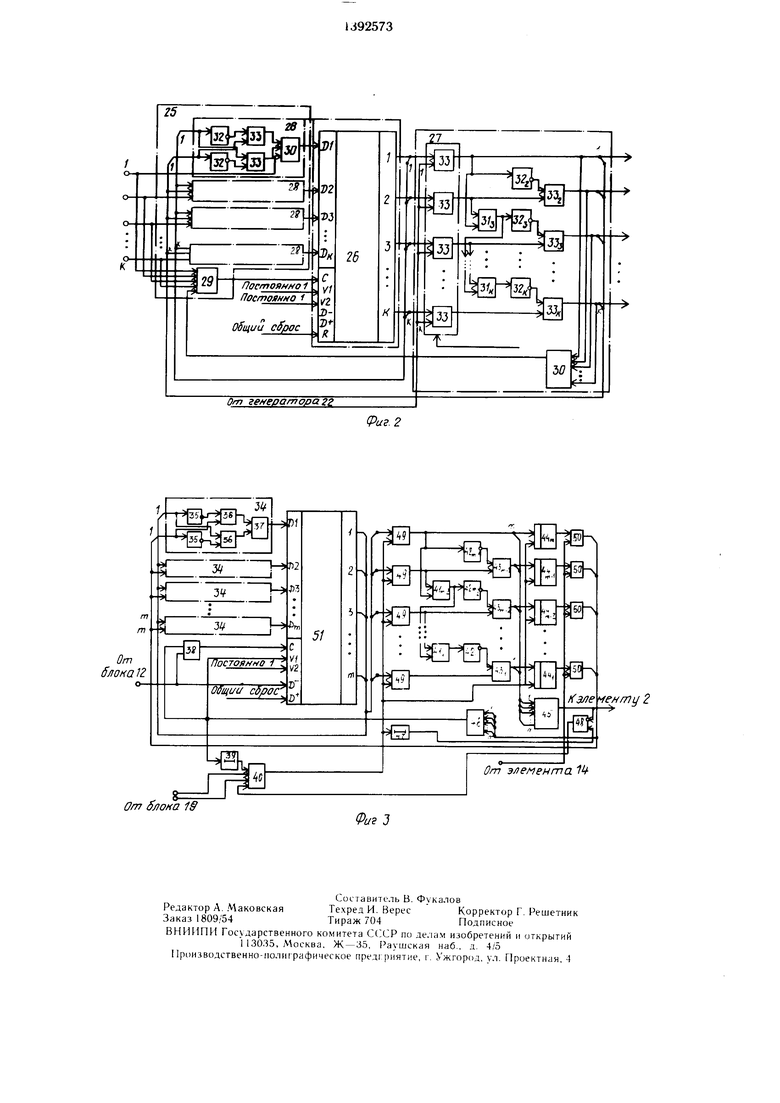

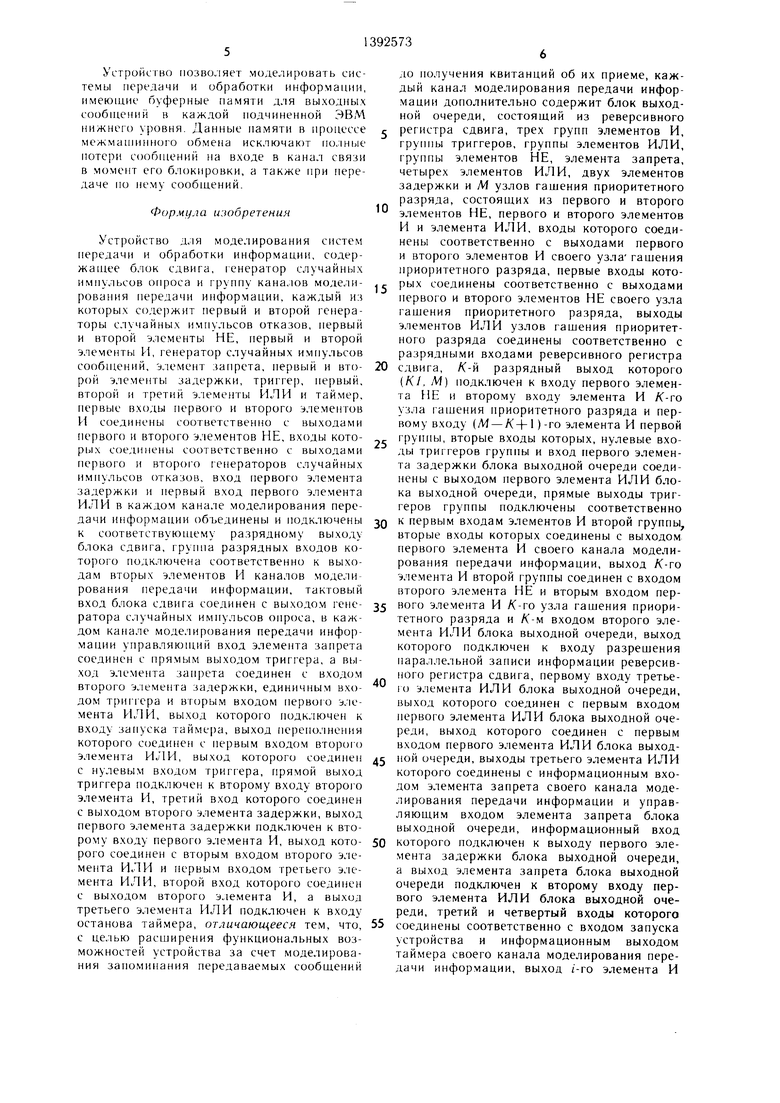

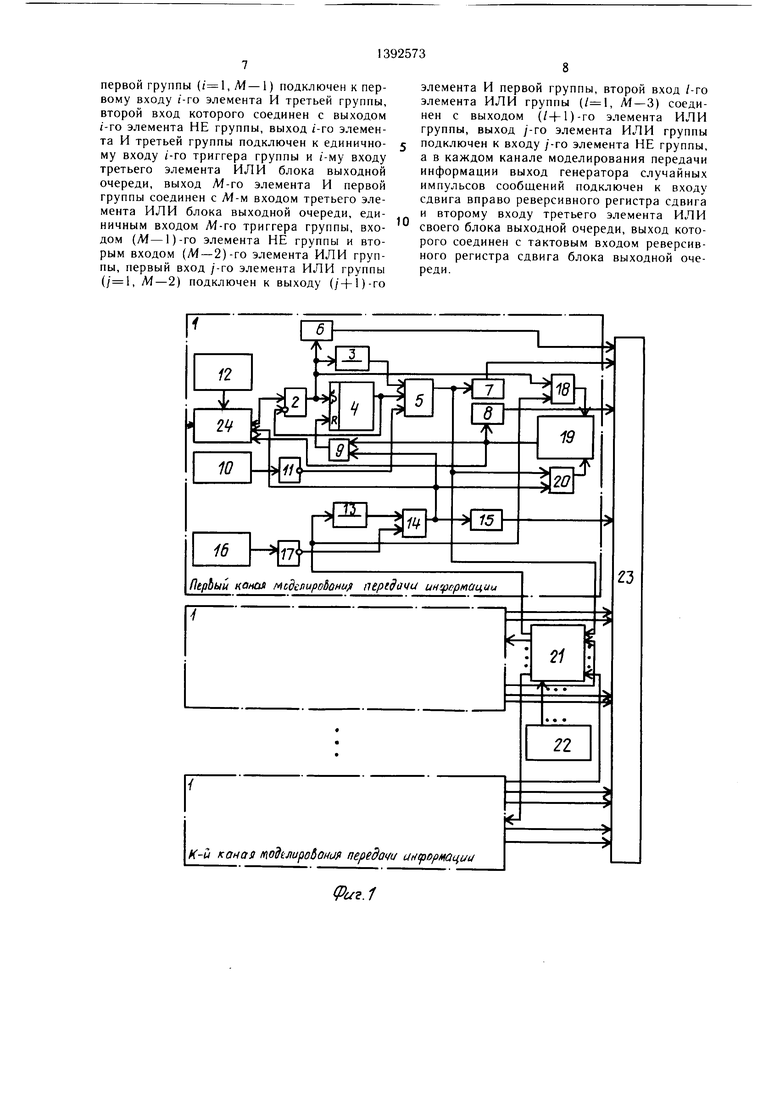

На фиг. 1 изображена структурная схема устройства; на фиг. 2 - структурная схема блока сдвига; на фиг. 3 - структурная схема блока выходной очереди.

Устройство содержит /С каналов 1 моделирования передачи информации, каждый из которых включает элемент 2 запрета, второй элемент 3 задержки, триггер 4, второй элемент И 5, счетчик б выработанных сообщений, счетчик 7 переданных сообщений счетчик 8 числа простоев, второй элемент ИЛИ 9, второй генератор 10 случайных импульсов отказов, второй элемент НЕ 11, ге- нератор 12 случайных импульсов сообщений, первый элемент 13 задержки, первый элемент И 14,счетчик 15 переданных квитанций, генератор 16 случайных импульсов, элемент НЕ 17, ИЛИ 18, таймер 19, третий элемент ИЛИ 20.

В состав устройства входят также блок 21 сдвига, генератор 22 случайных им 1ульсов опроса, блок 23 индикации, блок 24 выходной очереди.

Блок 21 сдвига содержит узел 25 гашения приоритетного разряда, регистр 26 сдвига, узел 27 определения приоритетного разряда.

Узел 25 предназначен для гашения единицы в приоритетном разряде стандартного регистра без изменения состояния остальных разрядов этого регистра. Узел имеет однородную структуру и в каждом разряде (их всего К.) содержит схему 28 гашения приоритетного разряда.

В состав блока входят также элементы ИЛИ 29, 30, 31, элементы НЕ 32, элементы И 33.

28 реализует логическую функцию .

Регистр сдвига представляет собой стандартный двунаправленный регистр сдвига с последовательным и параллельным занесением информации. Узел имеет вход последовательного занесения при сдвиге вправо и D- при сдвиге влево, К входов параллельного занесения тактовый счетный вход С, управляющие входы 1/1 и 1/2 для выбора режима работы, вход R установки в «О и К выходов каждого разряда.

В зависимости от состояний входов 1/1, V2 и R узел 26 может работать в различных режимах, используемых в устройстве; параллельное занесение, хранение, установка в нуль.

Параллельное занесение информации осуществляется через входы , когда на управляющих входах V и V2 поддержи

5

0

0

0

5

0

5

5

0

ваются уровни логической «1, а на вход С поступает тактовый импульс.

Режим хранения выполняется при отсутствии на входе С тактового импульса.

Узел 27 предназначен для определения приоритетного разряда регистра сдвига. Приоритетным является первый по порядку, начиная с первого, разряд, содержащий логическую «единицу.

Блок 24 выходной очереди (фиг. 3) содержит узлы 34 гашения приоритетного разряда.

Узлы 34 предназначены для «гашения единицы в приоритетном разряде стандартного реверсивного регистра сдвига без изменения состояния остальных разрядов этого регистра. Они имеют однородную структуру и включают первый и второй элементы НЕ 35, первый и второй элементы И 36 и элемент ИЛИ 37.

Блок 24 содержит также третий элемент ИЛИ 38, второй элемент 39 задержки, элемент ИЛИ 40.

Для определения приоритетного разряда стандартного регистра сдвига по тому же принципу, что и в узле 27 блока 21, а также для хранения признака выбранного разряда до момента прихода управляющего сигнала с выхода элемента И 14 блок 24 содержит группу элементов ИЛИ 41, группу элементов НЕ 42, третью группу элементов И 43, группу триггеров 44, третий 45 и второй 46 элементы ИЛИ, первый элемент 47 задержки, элемент 48 запрета, первую 49 и вторую 50 группу элементов И, реверсивный регистр 51 сдвига.

Устройство имеет возможность моделировать системы передачи и обработки информации с радиальной двухуровневой структурой, имеющие буферные памяти (очереди) для выходных сообщений в каждой подчиненной ЭВМ нижнего уровня.

Введение таких очередей перед каждым каналом связи позволяет исключить полные потери сообщений при блокировке канала, а также при передаче по нему сообщений. Это обусловлено тем, что выходные сообщения до их посылки в линию связи перемещаются в соответствующие буферные памяти, а во время их транспортировки в данных памятях хранятся дубликаты этих сообщений. Поэтому в рассмотренных системах при потере сообщения (квитанции) выполняется идентификация аварийного сообщения и осуществляется его повторная передача. При успещном завершении передачи сообщения в центральную ЭВМ его дубликат исключается из соответствующей очереди.

Устройство работает следующим образом.

С выхода генератора 12 в блок 24 выходной очереди поступают импульсы-сообщения, имитируя наполнение буферной памяти, например, первой подчиненной ЭВМ.

В блоке 24 (фиг. 3) эти сигналы поступают на вход D-|- и - через элемент ИЛИ 38 - на вход С, в результате чего происходит занесение информации в регистр 51 со сдвигом внраво (на входе 1/1 поддерживается «нуль, так как на выходе элемента ИЛИ 46 тот же сигнал).

В определенный момент времени на за- нускающий вход устройства приходит сигнал начала работы, который через элемент ИЛИ 40 поступает на управляющие входы элементов И 49 и осуществляет опрос выходов регистра 51, а через элемент 47 приходит также на информационный вход элемента 48 запрета. Информация из регистра 51 поступает на элементы 41-43, которые определяют приоритетный разряд, единичный сигнал с которого поступает в соответствуюпи й триггер 44 и - через элемент ИЛИ 45 - на вход элемента 2 запрета (т. е. в канал связи). Этот сигнал проходит через элемент 2 запрета, устанавливает триггер 4 в единичное состояние, запускает через элемент ИЛИ 18 таймер 19, поступает в счетчик 6 и на элемент 3 задержки, имитируд)щий вре- мя передачи сообщения по каналу. При успешной передаче сообщения (на выходе генератора 10 случайных импульсов, имитирующего появление сбоев в канале, находится логический «О) единичный сигнал с эле- мента 3 задержки проходит через элемент И 5, поступает в блок 21, регистрируется в счетчике 7 и сбрасывает через элемент ИЛИ 20 таймрр 19. Аналогичные действия происходят и в других каналах моделирования передачи информации. Таким образом на первую группу К входов блока 21 сдвига поступают сигналы (единичные и нулевые), имитирующие сообщения (или их отсутствие от К каналов передачи информации.

Данная группа сигналов поступает на входы элементов ИЛИ 30 схем 28 узла 25 (фиг. 2), а также на элемент ИЛИ 29, формирующий тактовый импульс на вход С, в результате чего эти сигналы («единицы и «нули) заносятся в регистр (на входах V и 1/2 постоянно поддерживаются уровни логической «1).

В определенный момент времени от генератора 22 случайных импульсов опроса (он имитирует интервалы обслуживания сообщений) поступает в узел 27 сигнал опроса, который «разрешает прохождение сигналов из регистра 26 в узел 27 через элементы И 33.

Узел 27 определяет приоритетный разряд регистра и выбирает из него «единицу на обслуживание, т. е. эта «единица поступает в соответствующий канал 1 моделирования передачи информации на вход элемента 13 задержки, имитируя передачу квитанции центральной ЭВМ. Данный единичный сигнал через элемент ИЛИ 30 поступает также на (К+1 )-й вход элемента ИЛИ 29 (фиг. 2), а затем на вход С регистра 26. В результате этого в регистре будет осуществлено параллельное занесение информации из узла 25,

5 0 5 О

5

0

с

0 5

который выполнил « ашенне единицы в выбранном приоритетном разряде.

Единичный сигнал с выхода блока 1 сдвига через элемент ИЛИ 18 запускает таймер 19.

При успещной передаче квитанции (на выходе генератора 16 случайных импульсов, имитирующего отказы в канале, лог11ческий «нуль) единичный сигнал с элемента 13 задержки проходит через элемент И 15, регистрируется в счетчике 15, сбрасывает через элемент ИЛИ 9 триггер 4 (имитируется открытие канала), через элемент ИЛИ 20 останавливает таймер 19 и поступает на управляющий вход блока 24.

В случаях отказов в канале при передаче сообщения (или квитанции) генератор 10 (или 16) случайных импульсов совместно с элементом 11 (или 17) закрывают прохождение «единицы через элемент 5 (или 14) и сброс таймера 19 и триггера 4 не происходит. Через заданное «время ожидания таймер 19 срабатывает и сбрасывает сигналом повторной передачи через элемент ИЛИ 9 триггер 4. Далее этот сигнал поступает на вход повторной передачи блока 24 выходной очереди. Элемент 2 запрета после сброса триггера 4 открывается.

Таким образом имитируется уход какой- либо системы сбора и обработки нижнего уровня после ожидания в тайм-аут, вследствие чего канал передачи информации вновь открывается.

При появлении сигнала от элемента И 14 (успешная передача квитанции) элементы И 50 (фиг. 3) «открываются и пропускают информацию в узлы 34, а также на входы элемента ИЛИ 46. В результате этого происходит «гашение приоритетной единицы (имитируется исключение сообщения из очереди) и занесение новой инфор.мации в регистр 51 (на входах У и С элементом ИЛИ 46 поддерживается «единица).

Единичный сигнал от элемента ИЛИ 46 поступает также на вход элемента 39 задержки, далее через элемент ИЛИ 49 вновь происходит опрос регистра 51, а также сброс триггеров 44. Цикл работы блока 24 повторяется.

Если в регистре 51 (в очереди) отсутствуют сообщения, то опрос регистра 51 повторяется через элемент 48 запрета (элемент 47 синхронизирует поступление сигналов на входы элемента 48).

При поступлении сигнала от таймера 19 производится повторный опрос регистра 51 без предварительного «гашения единицы приоритетного разряда. Таким образом имитируется повторная передача потерянного сообщения.

На входе V l регистра 5 (фиг. 3) в основном поддерживается нулевой сигнал, поэтому сообщения от генератора 12 могут поступать независимо от работы канала моделирования передачи.

Устройство нозво.чяет моделировать системы передачи и обработки информации, имеющие буферные памяти для выходных сообщений в каждой подчиненной ЭВЛА нижнего уровня. Данные памяти в ироиессе межмац ииного обмена исключают полные нотери сообн1ений на входе в канал связи в момент его блокировки, а также при передаче но нему сообщений.

Формула изобретения

Устройство для моделирования систем передачи и обработки информации, содержащее блок сдвига, генератор случайных имиульсов опроса и группу каналов моделирования передачи информации, каждый из которых содержит первый и второй генераторы случайных импульсов отказов, первый и второй элементы НЕ, первый и второй элементы И, генератор случайных импульсов сообщений, элемент запрета, первый и второй элементы задержки, триггер, иервый, второй и третий элементы ИЛИ и таймер, первые входы первого и второго элементов И соединены соответственно с выходами первого и второго элементов НЕ, входы кото- pi.ix соединены соответственно с выходами первого и второго генераторов случайных имнульсов отказов, вход первого элемента задержки и иервый вход первого эле.мента ИЛИ в каждом канале .моделирования передачи информации объединены и подключены к соответствующему разрядному выходу блока сдвига, группа разрядных входов которого подключена соответственно к выходам вторых элементов И каналов моделирования передачи информации, тактовый вход блока сдвига соединен с выходо.м генератора случайных имиульсов оироса, в каждом канале моделирования передачи информации управляюп1ий вход элемента запрета соединен с прямым выходом триггера, а ход элемента запрета соединен с входом второго э;1емента задержки, единичным входом триггера и вторым входом первого элемента ИЛИ, выход которого подключен к входу запуска таймера, выход переполнения которого соединен с первым входом второго эле.мента ИЛИ, выход которого соединен с нулевым входом триггера, прямой выход триггера подключен к второму входу BTOpoi o элемента И, третий вход которого соединен с выходом второго элемента задержки, выход первого элемента задержки подключен к второму входу первого э:1емента И, выход которого соединен с вторым входом второго элемента ИЛИ и первым входом третьего элемента ИЛИ, второй вход которого соединен с выходом второго элемента И, а выход третьего элемента ИЛИ подключен к входу останова таймера, отличающееся тем, что, с целью расщирения функциональных возможностей устройства за счет моделирования запоминания передаваемых сообщений

до получения квитанций об их приеме, каждый канал моделирования передачи информации дополнительно содержит блок выходной очереди, состоящий из реверсивного регистра сдвига, трех групп элементов И, rpyinibi триггеров, группы элементов ИЛИ, группы элементов НЕ, элемента запрета, четырех элементов ИЛИ, двух элементов задержки и М узлов гашения приоритетного разряда, состоящих из первого и второго

элементов НЕ, первого и второго элементов И и элемента ИЛИ, входы которого соединены соответственно с выходами первого и второго элементов И своего узла гащения приоритетного разряда, первые входы котос рых соединены соответственно с выходами первого и второго эле.ментов НЕ своего узла гащения приоритетного разряда, выходы элементов ИЛИ узлов гащения приоритетного разряда соединены соответственно с разрядными входами реверсивного регистра

0 сдвига, К-н разрядный выход которого (К/, М) подключен к входу первого элемента НЕ и второму входу элемента И К-го узла гащения приоритетного разряда и первому входу (М - ) -го элемента И первой

группы, вторые входы которых, нулевые входы триггеров группы и вход первого элемента задержки блока выходной очереди соединены с выходом первого элемента ИЛИ блока выходной очереди, прямые выходы триггеров группы подключены соответственно

0 к первым входам элементов И второй группы, вторые входы которых соединены с выходом первого элемента И своего канала моделирования передачи информации, выход К-го элемента И второй группы соединен с входом второго элемента НЕ и вторым входом пер5 вого элемента И К-го узла гащения приоритетного разряда и /(-м входом второго элемента ИЛИ блока выходной очереди, выход которого подключен к входу разрещения параллельной записи информации реверсивного регистра сдвига, первому входу третье- 10 элемента ИЛИ блока выходной очереди, выход которого соединен с первым входом первого элемента ИЛИ блока выходной очереди, выход которого соединен с первым входом первого элемента ИЛИ блока выход5 ной очереди, выходы третьего элемента ИЛИ которого соединены с информационным входом элемента запрета своего канала моделирования передачи информации и управляющим входом элемента запрета блока выходной очереди, информационный вход

0 которого подключен к выходу первого элемента задержки блока выходной очереди, а выход элемента запрета блока выходной очереди подключен к второму входу первого элемента ИЛИ блока выходной очереди, третий и четвертый входы которого

5 соединены соответственно с входом запуска устройства и информационным выходом таймера своего канала моделирования передачи информации, выход г -го элемента И

первой группы (, /Vf-1) подключен к первому входу 1-го элемента И третьей группы, второй вход которого соединен с выходом /-ГО элемента НЕ группы, выход /-го элемента И третьей группы подключен к единичному входу i-ro триггера группы и г -му входу третьего элемента ИЛИ блока выходной очереди, выход М-го элемента И первой группы соединен с М-м входом третьего элемента ИЛИ блока выходной очереди, единичным входом М-го триггера группы, входом (М-1)-го элемента НЕ группы и вторым входом (М -2)-го элемента ИЛИ группы, первый вход /-ГО элемента ИЛИ группы (, М - 2) подключен к выходу (/ + i)-ro

элемента И первой группы, второй вход 1-го элемента ИЛИ группы (, М-3) соединен с выходом (/-(-1)-го элемента ИЛИ группы, выход У-ГО элемента ИЛИ группы подключен к входу /-го элемента НЕ группы, а в каждом канале моделирования передачи информации выход генератора случайных импульсов сообщений подключен к входу сдвига вправо реверсивного регистра сдвига и второму входу третьего элемента ИЛИ своего блока выходной очереди, выход которого соединен с тактовым входом реверсивного регистра сдвига блока выходной очереди.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования систем передачи и обработки информации | 1986 |

|

SU1337903A1 |

| Устройство для моделирования систем передачи и обработки информации | 1987 |

|

SU1481791A1 |

| Устройство для моделирования систем массового обслуживания | 1987 |

|

SU1418740A1 |

| Устройство для моделирования систем массового обслуживания | 1986 |

|

SU1319043A1 |

| Устройство для моделирования систем массового обслуживания | 1986 |

|

SU1388886A1 |

| Устройство для моделирования систем массового обслуживания | 1983 |

|

SU1088002A1 |

| Устройство для моделирования систем массового обслуживания | 1984 |

|

SU1275459A1 |

| Устройство для моделирования систем массового обслуживания | 1987 |

|

SU1509924A1 |

| Устройство для моделирования систем массового обслуживания | 1984 |

|

SU1241251A1 |

| Устройство для моделирования систем массового обслуживания | 1986 |

|

SU1343422A1 |

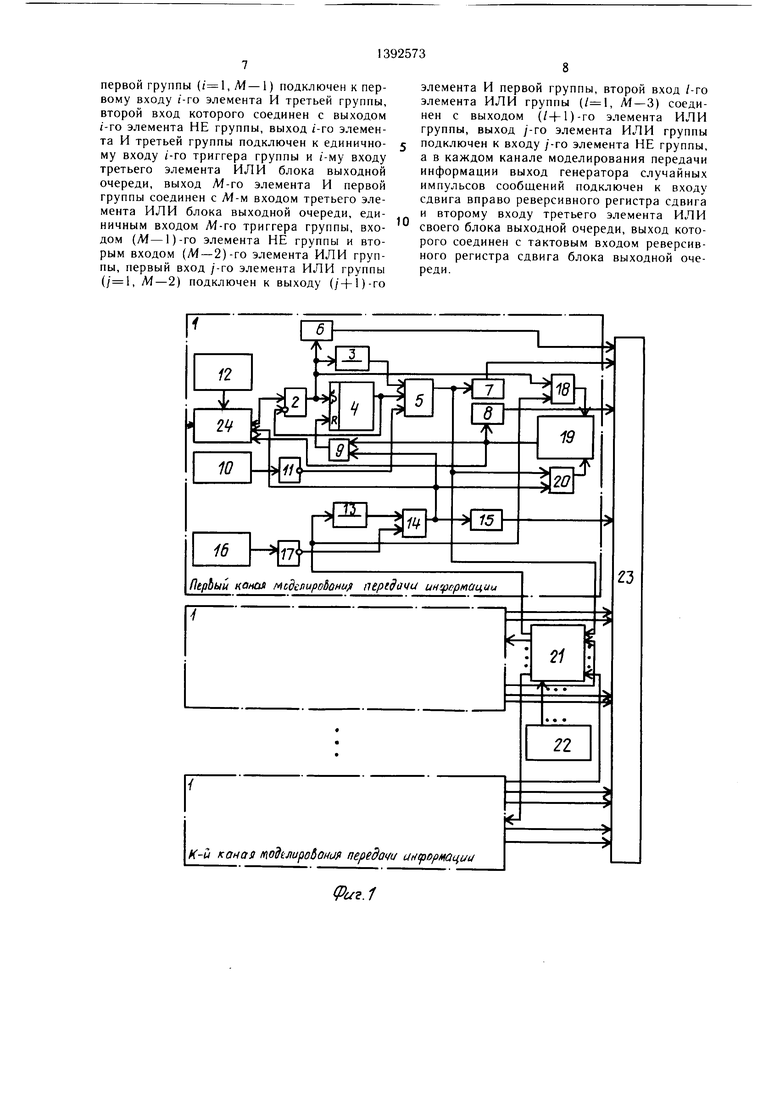

Изобретение относится к технике связи и вычислительной те.хнике и может быть использовано при проектировании систем передачи и обработки информации. Целью изобретения является расширение функцио- пальпых возможностей устройства за счет моделирования передаваемых сообщений до получения квитанций об их приеме. С этой целью каждый канал моделирования .передачи информации дополнительно содержит блок выходной очереди, состоящий из реверсивного регистра сдвига, трех групп элементов И, группы триггеров, группы элементов ИЛИ, группы элементов НЕ, элемента запрета, четырех элементов ИЛИ, двух э.чементов задержки и узлов гашения приоритетного разряда, состояпхих из первого и второго элементов НЕ, первого и второго элементов И и элемента ИЛИ. Устройство позволяет моделировать системы передачи и обработки информации, и.меющие буферные памяти д,1Я выходных сообщений в каждой подчиненной ЭВМ нижнего уровня. Данные памяти в процессе межмашинного обмена исключают полные потери сообп1ений на входе в канал связи в момент его блокировки, а также при передаче по нему сообципп1Й. 3 ил. с (Л

От 5лона 12

К эле чем ту 2

От элемента 1

| Устройство для моделирования систем передачи данных | 1983 |

|

SU1109758A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для моделирования систем передачи и обработки информации | 1986 |

|

SU1337903A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-04-30—Публикация

1986-11-04—Подача