Изобретение относится к вычисли- тельной технике и может быть использовано при проектировании систем передачи и обработки информации.

Цель изобретения - расширение фунциональных возможностей устройства за счет моделирования конвейерного протокола обмена и механизма окна. , На фиг.1 изображена структурная схема предлагаемого устройства; на фиг.2 - структурная схема блока буферной памяти.

Предлагаемое устройство (фиг.1) содержит К каналов 1 моделирования передачи информации,каждый из которых включает генератор 2 случайных импульсов сообщений, элемент 3 запрета, второй элемент 4 задержки, триггер 5, первый элемент И 6, второй элемент ИЛИ 7, блок 8 буферной памяти, первый элемент ИЛИ 9, первый генератор 10 случайных импульсов, первый элемент НЕ 11, таймер 12, первый элемент 13 задержки, второй элемент И 14, третий элемент ИЛИ 15, второй генератор 16 случайных импульсов, второй элемент НЕ 17. Кроме того, устройство содержит реверсивный блок 18 сдвига и генератор 19 случайных импульсов опроса.

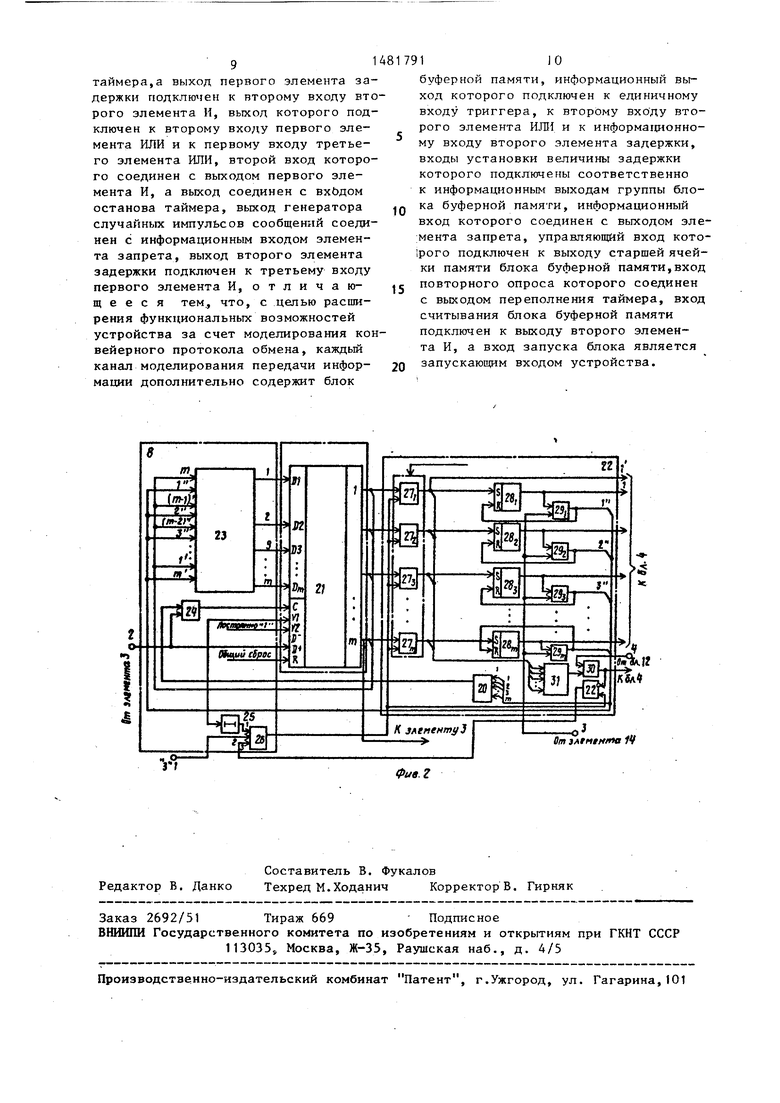

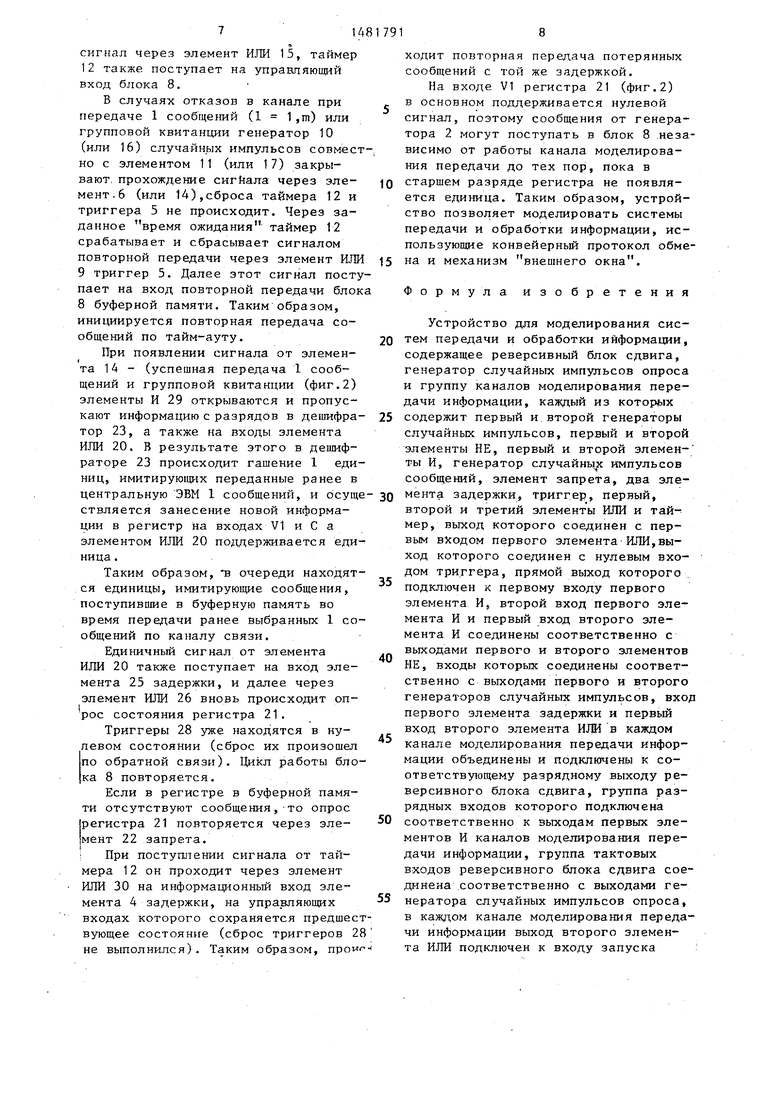

Блок 8 буферной памяти (фиг.2) содержит элемент ИЛИ 20, регистр 21 сдвига, элемент 22 запрета, дешифратор 23, элемент ИЛИ 24, элемент 25 задержки, элемент ИЛИ 26, группу элементов И 27, группу триггеров 28, группу элементов И 29, элемент ИЛИ 30 и элемент ИЛИ 31.

Устройство позволяет моделировать системы передачи и обработки информации, использующие так называемый конвейерный протокол обмена, разрешающий передачу сразу нескольких сообщений. Передающая ЭВМ блокируется до прихода подтверждающей групповой квитанции. Максимальное число сообщений,

5 которое можно сразу передать в канал, называют шириной внутреннего окна Vty . Этот параметр протокола может варьироваться в системе передачи и обработки данных от 2 до W4, где Wj 0 ширина внешнего окна, определяющая пороговое количество сообщений, которое мокет находиться в системе на обслуживании от одной подчиненной ЭВМ нижнего уровня.

5 Дешифратор 23 предназначен для гашения тех единиц в регистре 21, которые в предыдущем опросе были выбраны для передачи в канал. Например, в момент предыдущего опроса состояние

0 8-разрядного регистра было следующим: 00000111, а в момент прихода от эле- vMeHTa И 14 (фиг.1) управляющего сигнала (квитанции) - 00011111. В результате работы дешифратора 23 в регистр

21 в режиме параллельного занесения информации заносится двоичный код 00000011. Две оставшиеся единицы в регистре имитируют два сообщения,поступившие в буферную память во время передачи в центральную ЭВМ трех ране выбранных для обслуживания сообщений.

Регистр 21 предназначен для хранения поступивших в него сообщений. Элемент 4 задержки предназначен для имитации передачи сообщений по каналу связи.

Устройство работает следующим образом.

С выхода генератора 2 в блок 8 буферной памяти через элемент 3 запрета поступают импульсы-сообщения, имитируя накопление буферной памяти, например, первой подчиненной ЭВМ. Если в систему от генератора 2 поступает W4 заявок, то элемент 3 запрещает вход сообщений в канал моделирования передачи (в предлагаемом устройстве параметр Wz равен параметру W,, который в свою очередь имеет значение т). Это происходит в результате того, что со старшего разряда регистра 21 блока 8 на управляющий вход элемента 3 подается единица (фиг.2). Таким образом, имитируется в устройстве механизм внешнего окна.

В блоке 8 буферной памяти (фиг.2) Поступившие сигналы подаются на вход сдвига вправо и через элемент ИЛИ 24 на тактовый вход, в результате чего происходит занесение информации в регистр 21 со сдвигом вправо (на выходе элемента ИЛИ 20 - ноль).

В определенный момент времени на запускающий 3-й вход устройства приходит сигнал начала работы, который через элемент ИЛИ 26 поступает на управляющие входы группы 27 элементов И и осуществляет опрос выходов регистра 21, а также подается на вход элемента 22 запрета. Информация из регистра заносится соответственно в триггеры 28 и через элементы ИЛИ 31 и 30 поступает на управляющий вход элемента 22 запрета, на информационный вход элемента 4 задержки, устанавливает триггер 5 в единичное состояние и запускает через элемент ИЛИ 7 таймер 12.

Единичный сигнал с самого младшего разряда регистра поступает на

0

5

0

5

0

5

0

5

0

5

вход элемента 4, в котором имитируется время передачи всех сообщений,выбранных из регистра по каналу. Настройка элемента 4 осуществляется к его входам 1-т, которые связаны с выходами триггеров 28 блока 8 (фиг.2). Например, если из регистра поступил на триггеры 28 код 000..., в младшие разряды, то в блоке 4 будут задействованы при прохождении сигнала три элемента задержки.

При успешной передаче сообщения (на выходе генератора 10 случайных импульсов, имитирующего появление сбоев в канале, находится логический О) единичный сигнал из элемента 4 проходит через элемент И 6, поступает в блок 18, а также через элемент ИЛИ 15 срабатывает таймер 12, Аналогичные действия происходят и в других каналах моделирования передачи информации. Таким образом, на первую группу К входов реверсивного блока 18 сдвига поступают сигналы (единичные и нулевые), имитирующие группу переданных сообщений (или их отсутствие) от К каналов передачи информации.

Данная группа сигналов заносится в регистр блока 18. В определенный момент времени от генератора 19 случайных импульсов опроса (он имитирует случайные интервалы обслуживания одного или нескольких сообщений от одного канала) сигнал поступает в блок 18.

При этом определяется приоритетный разряд регистра блока 18 и выбирается из него единица на обслуживание, т.е. эта единица поступает в соответствующий канал 1 моделирования передачи информации на вход элемента 13 задержки, имитируя генерацию групповой квитанции централь- ной ЭВМ.

Единичный сигнал с элемента 13 задержки, имитирующего время передачи по каналу групповой квитанции, через элемент ИЛИ 7 запускает таймер 12.

При успешной передаче групповой квитанции (на выходе генератора 16 случайных импульсов, имитирующего отказы в канале, находится логический ноль) единичный сигнал с элемента 13 проходит элемент И 14, срабатывает через элемент ИЛИ 9 триггер 5 (имитируется открытие канала), и

сигнал через элемент ИЛИ 15, таймер 12 также, поступает на управляющий вход блока 8.

В случаях отказов в канале при передаче 1 сообщений (1 1,т) или групповой квитанции генератор 10 (или 16) случайных импульсов совместно с элементом 11 (или 17) закрывают прохождение сигнала через элемент.6 (или 14),сброса таймера 12 и триггера 5 не происходит. Через заданное время ожидания таймер 12 срабатывает и сбрасывает сигналом повторной передачи через элемент ИЛИ 9 триггер 5. Далее этот сигнал поступает на вход повторной передачи блока 8 буферной памяти. Таким образом, инициируется повторная передача сообщений по тайм-ауту.

При появлении сигнала от элемента 1 4 - (успешная передача 1 сообщений и групповой квитанции (фиг.2) элементы И 29 открываются и пропускают информацию с разрядов в дешифратор 23, а также на входы элемента ИЛИ 20. В результате этого в дешифраторе 23 происходит гашение 1 единиц, имитирующих переданные ранее в центральную ЭВМ 1 сообщений, и осуществляется занесение новой информации в регистр на входах V1 и С а элементом ИЛИ 20 поддерживается единица .

Таким образом, в очереди находятся единицы, имитирующие сообщения, поступившие в буферную память во время передачи ранее выбранных 1 сообщений по каналу связи.

Единичный сигнал от элемента ИЛИ 20 также поступает на вход элемента 25 задержки, и далее через элемент ИЛИ 26 вновь происходит опрос состояния регистра 21.

Триггеры 28 уже находятся в нулевом состоянии (сброс их произошел по обратной связи). Цикл работы блока 8 повторяется.

Если в регистре в буферной памяти отсутствуют сообщения, то опрос регистра 21 повторяется через элемент 22 запрета.

При поступлении сигнала от таймера 12 он проходит через элемент ИЛИ 30 на информационный вход элемента 4 задержки, на управляющих входах которого сохраняется предшествующее состояние (сброс триггеров 28 не выполнился). Таким образом, прои

0

5

0

5

0

5

0

5

0

5

ходит повторная передача потерянных сообщений с той же задержкой.

На входе V1 регистра 21 (фиг.2) в основном поддерживается нулевой сигнал, поэтому сообщения от генератора 2 могут поступать в блок 8 независимо от работы канала моделирования передачи до тех пор, пока в старшем разряде регистра не появляется единица. Таким образом, устройство позволяет моделировать системы передачи и обработки информации, использующие конвейерный протокол обмена и механизм внешнего окна.

Формула изобретения

Устройство для моделирования систем передачи и обработки информации, содержащее реверсивный блок сдвига, генератор случайных импульсов опроса и группу каналов моделирования передачи информации, каждый из которых содержит первый и второй генераторы случайных импульсов, первый и второй элементы НЕ, первый и второй элемен- ты И, генератор случайных импульсов сообщений, элемент запрета, два элемента задержки, триггер, первый, второй и третий элементы ИЛИ и таймер, выход которого соединен с первым входом первого элемента ИЛИ,выход которого соединен с нулевым входом триггера, прямой выход которого подключен к первому входу первого элемента И, второй вход первого элемента И и первый вход второго элемента И соединены соответственно с выходами первого и второго элементов НЕ, входы которых соединены соответственно с выходами первого и второго генераторов случайных импульсов, вход первого элемента задержки и первый вход второго элемента ИЛИ в каждом канале моделирования передачи информации объединены и подключены к соответствующему разрядному выходу реверсивного блока сдвига, группа разрядных входов которого подключена соответственно к выходам первых элементов И каналов моделирования передачи информации, группа тактовых входов реверсивного блока сдвига соединена соответственно с выходами генератора случайных импульсов опроса, в каждом канале моделирования передачи информации выход второго элемента ИЛИ подключен к входу запуска

таймера,а выход первого элемента задержки подключен к второму входу второго элемента И, выход которого подключен к второму входу первого элемента ИЛИ и к первому входу третьего элемента ИЛИ, второй вход которого соединен с выходом первого элемента И, а выход соединен с входом останова таймера, выход генератора случайных импульсов сообщений соединен с информационным входом элемента запрета, выход второго элемента задержки подключен к третьему входу первого элемента И,отличаю- щ е е с я тем, что, с целью расширения функциональных возможностей устройства за счет моделирования конвейерного протокола обмена, каждый канал моделирования передачи инфор- мации дополнительно содержит блок

JQJ520

8179110

буферной памяти, информационный выход которого подключен к единичному входу триггера, к второму входу второго элемента ИЛИ и к информационному входу второго элемента задержки, входы установки величины задержки которого подключены соответственно к информационным выходам группы блока буферной памяти, информационный вход которого соединен с выходом элемента запрета, управляющий вход которого подключен к выходу старшей ячейки памяти блока буферной памяти,вход повторного опроса которого соединен с выходом переполнения таймера, вход считывания блока буферной памяти подключен к выходу второго элемента И, а вход запуска блока является запускающим входом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования систем передачи и обработки информации | 1986 |

|

SU1392573A1 |

| Устройство для моделирования систем передачи и обработки информации | 1986 |

|

SU1337903A1 |

| Устройство для моделирования систем массового обслуживания | 1987 |

|

SU1418740A1 |

| Устройство для моделирования систем массового обслуживания | 1986 |

|

SU1388886A1 |

| Устройство для моделирования систем массового обслуживания | 1987 |

|

SU1509924A1 |

| Устройство для моделирования систем массового обслуживания | 1984 |

|

SU1275459A1 |

| Устройство для моделирования систем массового обслуживания | 1986 |

|

SU1319043A1 |

| Устройство для моделирования систем массового обслуживания | 1987 |

|

SU1460725A1 |

| Устройство для моделирования систем массового обслуживания | 1986 |

|

SU1310838A1 |

| Устройство для моделирования систем связи | 1990 |

|

SU1741148A1 |

Изобретение относится к технике связи и вычислительной технике и может быть использовано при разработке и моделировании систем передачи и обработки информации. Цель изобретения - расширение функциональных возможностей устройства за счет моделирования конвейерного протокола обмена. Устройство содержит к идентичных каналов 1 моделирования передачи информации, каждый из которых включает генератор 2 случайных импульсов сообщений, элемент 3 запрета, элемент 4 задержки, триггер 5, блок 8 буферной памяти, генераторы 10 и 16 случайных импульсов, таймер 12, элемент 13 задержки, а также реверсивный блок 18 сдвига, генератор 19 случайных импульсов опроса. При успешной передаче сообщения импульс проходит через элемент И 6 в блок 18 сдвига, в противном случае генератор 10 совместно с элементом НЕ 11 закрывают элемент И 6. Из блока 18 сообщения выбираются на обслуживание в соответствии с внесистемными приоритетами, назначенными априорно каждому каналу моделирования передачи информации. В случае отказов в канале во время передачи имитируются тайм-ауты и организуются повторные передачи потерянных сообщений. Данные возможности устройства обеспечиваются работой таймера 12, триггера 5 и блока 8 буферной памяти в каждом канале моделирования передачи информации. Блок 8 обеспечивает хранение поступивших сообщений, выдачу их в канал, а затем уничтожение дубликатов в очереди при успешной передаче сообщений. 2 ил.

От jAtfttttfa 14

Фив. г

| Устройство для моделирования систем передачи и обработки информации | 1986 |

|

SU1392573A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для моделирования систем передачи и обработки информации | 1986 |

|

SU1337903A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-05-23—Публикация

1987-10-26—Подача