со со

-4

4

Изобретение относится к вычислительной технике и может быть использовано в автоматизированных системах обработки данных и производства программ для ЭВМ.

Цель изо(5ретения - расширение функциональных возможностей анализатора за счет обеспечения бесприоритетного синтаксического анализа ис- Ходных выргикений при одновременном повышении быстродействия и упрощении..

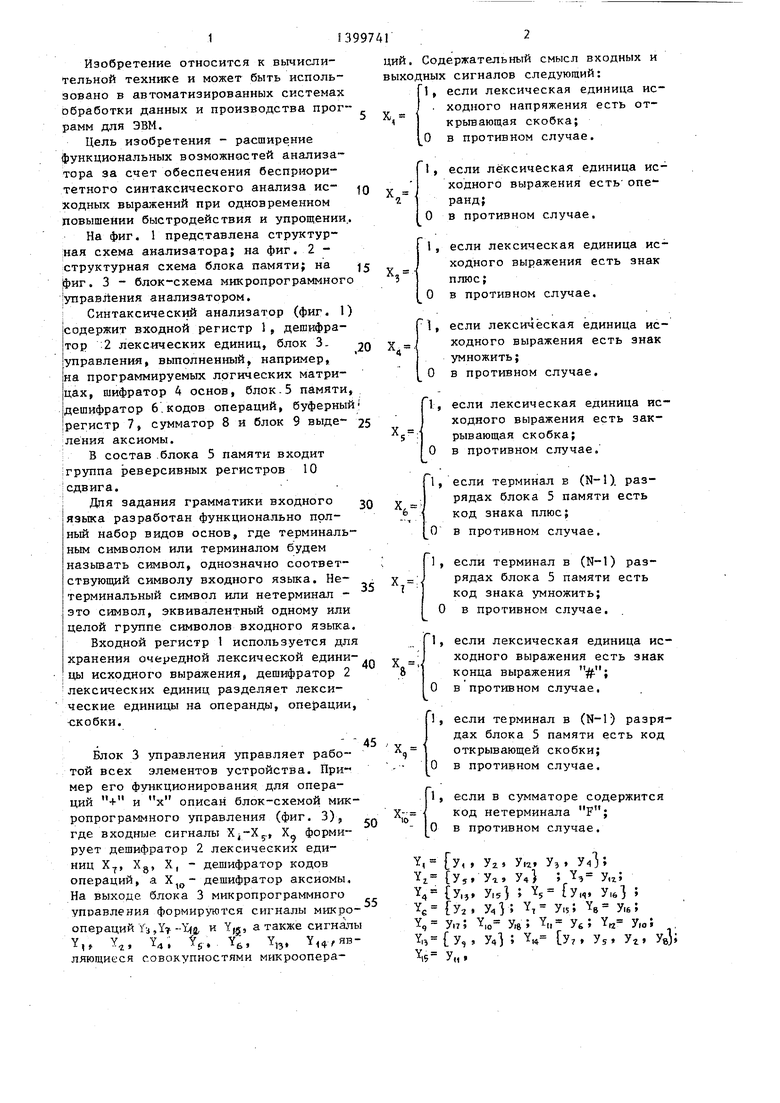

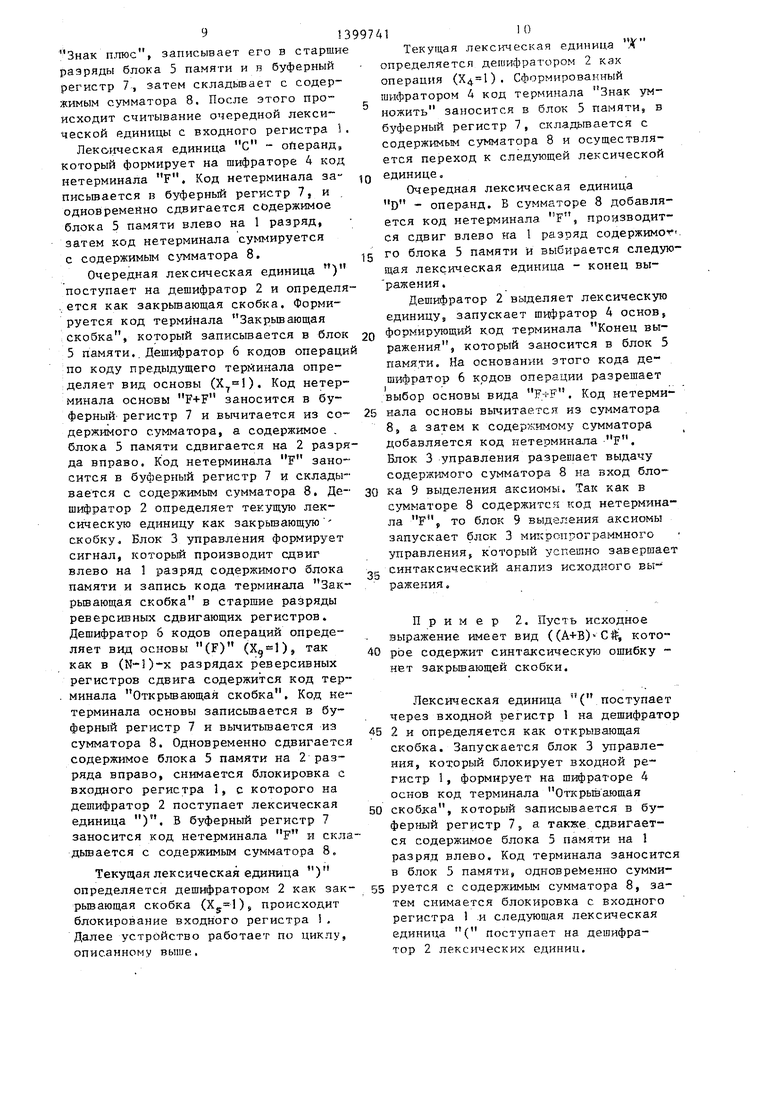

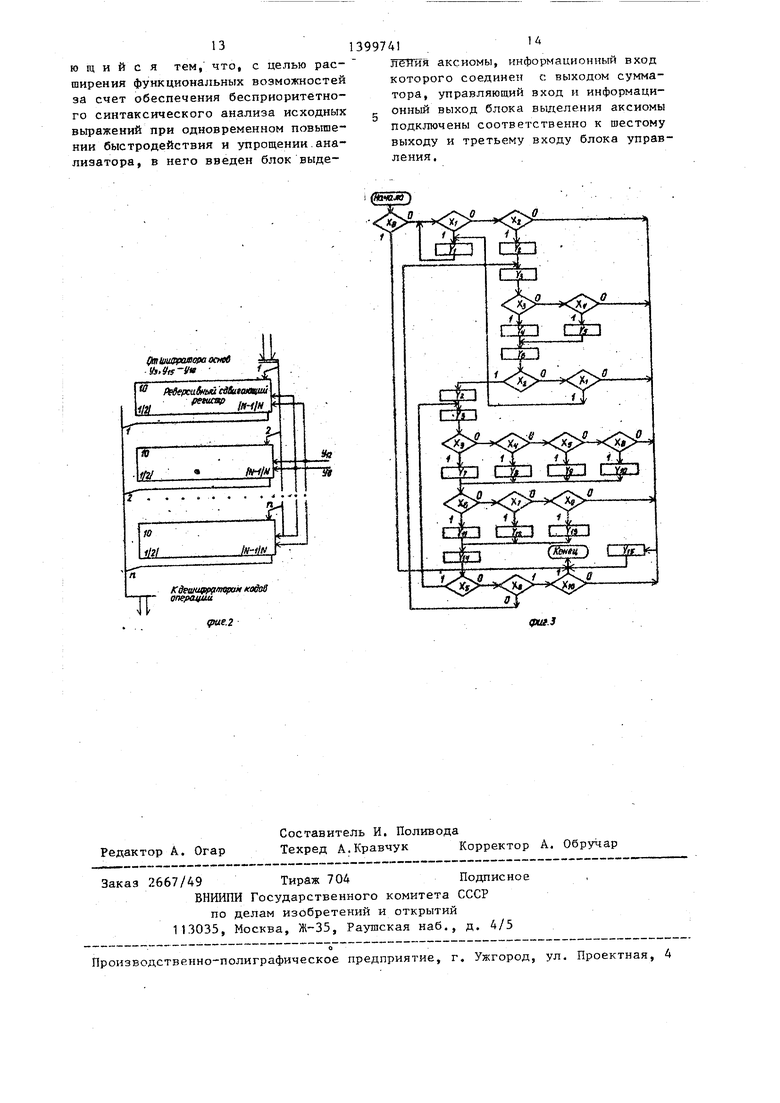

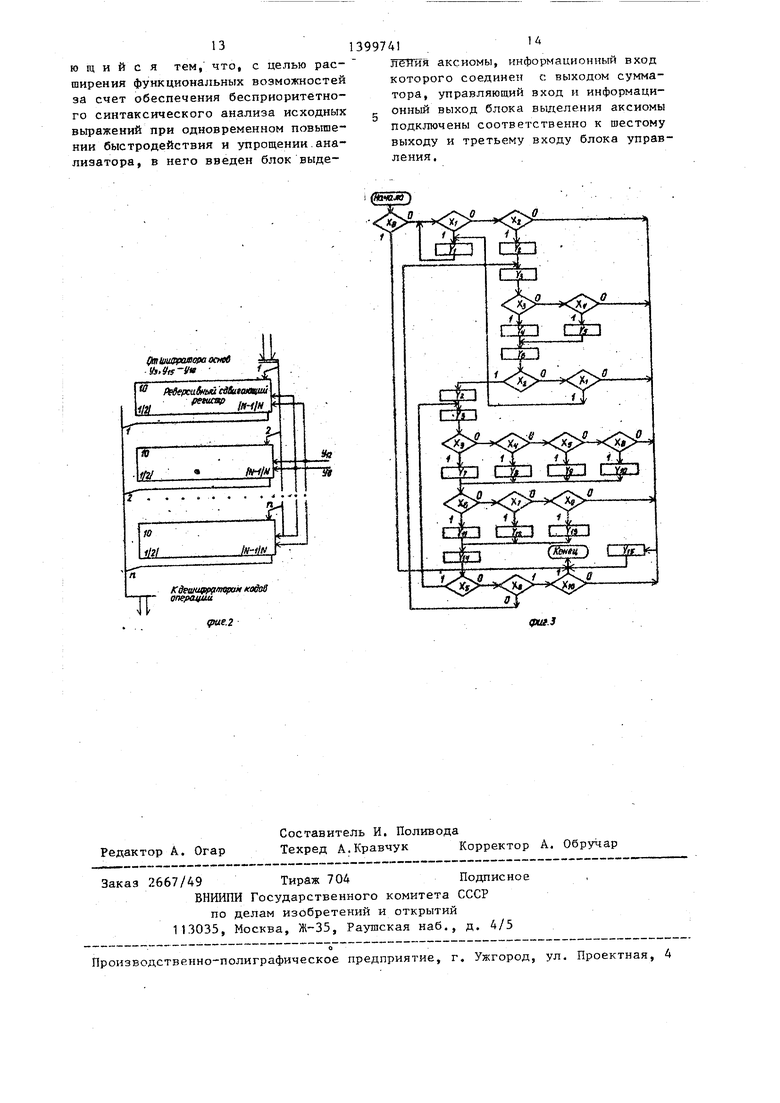

На фиг. 1 представлена структурная схема анализатора; на фиг. 2 - структурная схема блока памяти; на 1ФИГ. 3 - блок-схема микропрограммного lynpaajleHHH анализатором. ; Синтаксический анализатор (фиг. 1) |содержит входной регистр 1, дешифра- |тор :2 лексических единиц, блок 3. управления, вьтолненный, например, на программируемых логических матрицах, шифратор 4 основ, блок.5 памяти, дешифратор 6,кодов операций, буферный |регистр 7, сумматор 8 и блок 9 выде- ;лёния аксиомы.

i В состав .блока 5 памяти входит :группа реверсивных регистров 10 ; сдвига.

: Для задания грамматики входного языка разработан функционально полный набор видов основ, где терминальным символом или терминалом будем назьюать символ, однозначно соответствующий символу входного языка. Нетерминальный символ или нетерминал - это символ, эквивалентный одному или целой группе символов входного языка.

Входной регистр 1 используется для хранения очередной лексической единицы исходного выражения, дешифратор 2 лексических единиц разделяет лексические единицы на операнды, операции, скобки.

Блок 3 управления управляет работой всех элементов устройства. При- мер его функционирования для операций + и х описан блок-схемой микропрограммного управления (фиг. 3), где входные сигналы , Х„ формирует дешифратор 2 лексических единиц X.f, Xg, X, - дешифратор кодов операций, а Х дешифратор аксиомы, На выходе блока 3 микропрограммного управления формируются сигналы микроопераций Yi,Y -Yij, и Y|5, а также сигналы Y,, Y, Y, tg.. , Y, Y,3, ,HB- ляющиеся совокупностями микроопераций. Содержательный смысл входных и выходных сигналов следующий:

1, если лексическая единица ис- . ходного напряжения есть открьгаающая скобка; О в противном случае.

Х,

5 0 5

g

5

X,

х,.X.

v

1 , если лексическая единица исходного выражения есть операнд;

О в противном случае.

1, если лексическая единица исходного выражения есть знак плюс;

О в противном случае.

1, если лексическая единица исходного выражения есть знак умножить;

О в противном случае.

1, если лексическая единица исходного выражения есть закрывающая скобка;

О в противном случае,

I, если терминал в (N-1). разрядах блока 5 памяти есть код знака плюс;

О в противном случае.

1, если терминал в (N-1) разрядах блока 5 памяти есть код знака умножить; О в противном случае.

X J

к

1, если лексическая единица исходного выражения есть знак конца выражения ;

О в противном случае.

1, если терминал в (N-l) разрядах блока 5 памяти есть код открывающей скобки;

О в противном случае.

1, если в сумматоре содержится

код нетерминала О в противном случае.

5

Y, у, , г СУ5. 4 {у,

Уг УП. УЭ Уг 9 УЧ J Э У|г

Y. fy,,. у,б ;

I yis 5

Уг. Y, у,;; Ye у,б; Yq Уп1 Y|o y,g ; Y, у ; Y,2 Ую Y,,, У4 ; Y, у, У5, у,

5 У,,.

де у.

крьшаюп1ая скобка в буферный регистр 7;

сложение в сумматоре 8 кода терминала/нетерминала, поступающего из буферного регистра ,7;

запись кода терминала От- крьшающая скобка в блок 5 памяти;

чтение следующей лексической единицы исходного выражения из входного регистра 1; запись кода нетерминала F в буферный регистр 7; запись кода нетерминала основы FxF в буферный регистр 7;

вычитание кода нетерминала основы из содержимого сумматора 8;

сдвиг на два разряда эправо (в сторону старших разрядов) содержимого . блока 5 памяти;

запись кода нетерминала основы (F) в буферный регистр 7;

запись кода нетерминала основы F-vF в буферный ре- . гистр 7;

вьщача сообщения Ошибка ; сдвиг на разряд влево содержимого блока 5 памяти; - запись кода терминала Знак плюс в буферный регистр 7; запись кода терминала Зна- коумножитель в буферный per истр 7;

запись кода терминала Знак плюс в блок 5 памяти;

запись кода терминала Знак умножения в блок 5 памяти; запись кода терминала За- крьшающая скобка в блок 5 памяти;

КоIt

У- У,

.У4

у.; Уб у

УО у« y«t - у«УП - У.5 У(б У17 - У|8 запись кода терминала нец исходного выражения (знак 4J:) в блок 5 памяти.

Шифратор 4 основ формирует коды

ерминалов и нетерминалов.

Блок 5 памяти - это память с поледовательным безадресным принципом аписи и чтения. В состав блока паяти (фиг. 2) входит группа реверивных сдвигающих регистров 10. Заый

а 1399741

пись информации производится в старшие N-e разряды параметров.

Реверсивные регистры 10 сдвига блока 5 памяти поразрядно сдвигают

0

коды терминалов, а также совместно с дешифратором 6 кодов операций производят выбор основы для свертки исходного выражения.

0 Буферный 7 регистр используется для хранения кодов терминалов и нетерминалов .

Сумматор 8 вьтолняет либо функцию вычитания кодов терминалов и не- 5 терминалов, либо функцию вычитания нетерминалов основ.

Блок 9 выделения аксиомы выделяет код нетерминала F, определенный в качестве начального нетерминала 0 (или аксиомы) и соответствующей успешному завершению синтаксического анализа.

Устройство работает следующим образом.

5 Лексические единицы исходного выражения последовательно поступают на входной регистр 1, а затем на дешифратор 2 лексических единиц, ко- торый различает и выделяет операнды, операции, скобки и выражения 4|.

При поступлении лексической единицы, например, открывающей скобки (, ) дешифратор 2 лексических -единиц запускает блок 3 управления, который вырабатывает совокупность микроопераций (Y,). Управляющие сигналы с блока 3 управления поступают на вход шифратора А основ и формируют код терминала открьгаающей Q скобки, а затем разрешают запись кода терминала в буферный регистр 7 (микрооперация у и сложение его с содержимым сумматора 8 (микрооперация у), а также осуществляют сдвиг на 1 разряд влево содержимого блока 5 памяти (микрооперация у,2), запись в разряды блока 5 памяти кода терминального символа и разрешают чтение следующей лексической единицы из входного регистра 1 (микрооперация У4)..-Если следующая лексическая единица есть операнд (, Х,0, ), то блок 3 управления выполняет сое вокупность микроопераций (Y,j, Yj) : . на шифраторе 4 основ формируется код нетерминала F, производится запись кода нетерминального символа F в буферньШ регистр 7 (микрооперация

5

5

0

У-) происходит сложение кода и содержимого сумматора 8, выполняется сдвиг на 1 разряд влево содержимого блока 5 памяти (микрооперадия у,) и вырабатывается разрешающий сигнал на чтение очередной лексической еди- ниды из входного регистра 1, Если лексическая единида не была операндом (, Х,0, ), то формиру- ется управляющий сигнал об ошибке (микрооперация у,,) .

Если очередная лексическая едини™ ца есть операдия, например, знак плюс ()|, то дешифратор 2 логи- ческих единид запускает блок 3 управления, входные сигналы ( Yg) которого формируют на шифраторе 4 основ код терминала Знак плюс, запись Кода в буферный регистр 7 (микроопе™ рация у,) и в старшие разряды блока 5 памяти (микрооперадия-у,з) J сложени Кода терминального символа с содер жимым сумматора 8 (микрооперация у) И сбрасывает запрет на чтение оче- редной единицы из входного регистра 1, Если лексическая единица не операдия (Х., ), то происходит формирование сигнала (Yjj)« сообщающего об ошибке.

Если следующая лексическая единица есть открывающая скобка ( Х,1), то дешифратор 2 лексических единид запускает блок 3 управления, Который вырабатьгоает совокупность Микроопераций (Y) , и работа устройства повторяется.

Если очередная лексическая единица есть не операнд и не открьша- Ьщая скобка (, Х,0), то форми- руется управляющий сигнал об ошибке микрооперация, у,) .

Если очередная лексическая единица есть операнд (), то блок 3 управления вьшолняет совокупность микроопераций (Y, Y.) на шифраторе 4 основ формируется код нетерминала F, производится запись кода нетерминального символа F в буферный регистр 7 (микрооперация Ус.)з проис™

ходит сложение содержимого сумматора

8 и кода, выполняется сдвиг на i разряд влево содержимого блока 5 памя- ти (микрооперация у,) и вырабатывается разрешающий сигнал на чтение очередной лексической единицы из входного регистра 1,

Если очередная лексическая единица не знак операции, не закрьшаю

5 Q

„

0

В

5

щая скобка и не конец выражения (Х,0, , , ), то в блоке 3 управления формируется управляющий сигнал выдачи ошибки (микрооперация у,) .

Если очередная лексическая единица есть знак (X,), или знак (), или закрьгеающая скобка (Xg 1) , или конец выражения 4 (Х 1) , то блок микропрограммного управления формирует на шифраторе 4 основ код терминала Знак плюс, Знак умножить, Закрьгоающая скобка, Конец выражения соответственно, затем происходит запись соответствующего кода в N-й разряд блока 5 памяти.

После записи кода терминала в старшие разряды реверсивных регистров сдвига блока 5 памяти содержимое (N-l)-x разрядов блока 5 памяти поступает на вход дешифратора 6 кодов операций, который формирует сигнал, определяющий вид основы для свертки исходного выражения. Деши|)ратор 6 кодов операций запускает блок 3 управления, который разрешает-выполнение операций (Y,,-Y,4) . Если в ()x разрядах реверсивных сдви- - гающих регистров находится, например, код терминала Знак плюс (Xgi Oj ), то в буферный регистр 7 запи- сьюается код нетерминала основы ; F + F (микрооперадия У|д) , затем из содержимого сумматора 8 вычитается код нетерминала основы (микрооперация у), а в буферный регистр 7 заносится код нетерминала F (микрооперация У5), после чего производится сложение кода нетерминала с содержимым сумматора 8 (микрооперация y-j) и осуществляется сдвиг на 2 разряда вправо содержимого реверсивных сдвигающих регистров блока 5 памяти (микрооперация у„),

Если в (N-l)-x разрядах реверсивных сдвигающих регистров находится код терминала Знак умножения (), то в буферный регистр 7 записьшается ко д нетерминала основы F«P и следует операция Y}(}.,

Если в (N-l)-x разрядах реверсивных сдвигающих регистров находится код терминала Закрьюающая скобка (, XT.O, ), то в буферный регистр 7 запись1вается код нетерминала основы (F) и следуют разрешение на чтение очередного символа на входной

регистр I (микрооперация у) и операция Y,.

Если выбрана несуществующая основа (, ,-Х,0), то в блоке 3 управления формируется управляющий сигнал выдачи ошибки (Y.g).

Если очередная лексическая единица есть закрывающая скобка (), то дешифратор 2 лексических единиц д запускает блок 3 управления, который вьшолняет (Y) сдвиг на 1 разряд влево содержимое реверсивных сдвигающих регистров (микрооперация у),

ходит сдвиг на 1 разряд влево содержимого реверсивных сдвигающих регистров, в старшие разряды которых за- письгвается код терминала, после чего записьшается чтение с входного регистра I следующей лексической едини- ць1 исходного выражения.

Лексическай единица А дешифруется дешифратором 2 как операнд (), и выдается сигнал на запуск блока 3 управления, который разрешает формирование на шифраторе 4 основ кода нетерминала F, заносит его в

затем на шифраторе А основ происходит 5 буферный регистр 7, суммирует содерформирование кода терминала Закрывающая скобка и запись (Y) кода терминала в.блок 5 памяти микрооперация у). Далее работа устройства повторяется.

Если очередная лексическая единица не закрьгоающая скобка (), не конец выражения :Jf (), то, дешифратор 2 лексических единиц запускает блок 3 управления, который вьшолняет (YJ) сдвиг ,на 1 разряд влево содержимого реверсивных сдвигающих регисл ров (микрооперация у) . Далее работа устройства повторяется.

Если очередная лексическая единица е.сть конец выражения (, ), то блок 9 выделения аксиомы осуществляет проверку содержимого

сумматора 8. .1

Если сумматор 8 содержит код нетерминала F (, , ), то - входное выражение синтаксически правильно.

Если сумматор 8 содержит код другого символа (, ), то блок 3 управления формирует сигнал об ошибке ().

Пример 1. Пусть входное вы- ражение имеет вид {A+(B+C) D f.Процесс синтаксического анализа происходит следующим образом. На входной регистр 1 поступает лексическая единица (, которая дешифратором 2 лекси- , ческих единиц определяется как открывающая скобка (X.I), и происходит запуск блока 3 управления, формирующего совокупность микроопераций, которая блокирует входной регистр 1, запускает шифратор 4 основ на формирование кода терминала Открьгоающая скобка. Затем происходят запись кода терминала в буферный регистр 7, сложение кода терминала с содержимым сумматора 8. В блоке 5 памяти проис20

жимое сумматора 8 с кодом нетерминала производит сдвиг на 1 разряд влево содержимого блока 5 памяти и снимает блокировку на чтение с входного регистра 1, с которого поступает очередная лексическая единица +. ,

Дешифратор 2 лексических единиц распознает ее как операцию () и возбуждает блок 3 управления, ко- 25 торый запускает шифратор основ, фор- мирующий код.терминала Знак плюс, записьшаемый в буферный регистр 7 и в N-e разряды реверсивных сдвигающих регистров блока 5 памяти, происходит сложение кода терминала с содержимым сумматора 8 и дается с блока 3 управления разрешение на чтение очередной лексической единицы.

Лексическая единица, поступающая на дешифратор 2, определяется как открывающая скобка. С помощью блока 3 управления шифратор 4 основ формирует код терминала о.ткрывающей скобки, которьй заносится в буферный регистр 7, .складьтается с содержимьм сумматора 8, а также производится сдвиг на 1 разряд влево содержимого блока 5 памяти и разрешается считьгоа- ние следующей лексической единицы В

30

35

40

45

из входного регистра.

Дешифратор 2 лексических единиц

(Х,

определяет ее как операнд (,х 1) и запускает блок 3 управления, выходные сигналы с которого разрешают шифрато- 50 РУ основ формирование кода нетерминала F, запись его в буферный регистр 7, сложение кода с содержимым сумматора 8 и чтение очередной лексической единицы с входного регист55 Ра 1.

Поступившая на дешифратор 2 лекйИческая единица + есть операция (Х, «О. Блок 3 управления на тт.1фра-- торе 4 основ формирует код т(рмннала

ходит сдвиг на 1 разряд влево содержимого реверсивных сдвигающих регистров, в старшие разряды которых за- письгвается код терминала, после чего записьшается чтение с входного регистра I следующей лексической едини- ць1 исходного выражения.

Лексическай единица А дешифруется дешифратором 2 как операнд (), и выдается сигнал на запуск блока 3 управления, который разрешает формирование на шифраторе 4 основ кода нетерминала F, заносит его в

0

жимое сумматора 8 с кодом нетерминала, производит сдвиг на 1 разряд влево содержимого блока 5 памяти и снимает блокировку на чтение с входного регистра 1, с которого поступает очередная лексическая единица +. ,

Дешифратор 2 лексических единиц распознает ее как операцию () и возбуждает блок 3 управления, ко- 5 торый запускает шифратор основ, фор- мирующий код.терминала Знак плюс, записьшаемый в буферный регистр 7 и в N-e разряды реверсивных сдвигающих регистров блока 5 памяти, происходит сложение кода терминала с содержимым сумматора 8 и дается с блока 3 управления разрешение на чтение очередной лексической единицы.

Лексическая единица, поступающая на дешифратор 2, определяется как открывающая скобка. С помощью блока 3 управления шифратор 4 основ формирует код терминала о.ткрывающей скобки, которьй заносится в буферный регистр 7, .складьтается с содержимьм сумматора 8, а также производится сдвиг на 1 разряд влево содержимого блока 5 памяти и разрешается считьгоа- ние следующей лексической единицы В

0

5

0

5

из входного регистра.

Дешифратор 2 лексических единиц

(Х,

определяет ее как операнд (,х 1) и запускает блок 3 управления, выходные сигналы с которого разрешают шифрато- 0 РУ основ формирование кода нетерминала F, запись его в буферный регистр 7, сложение кода с содержимым сумматора 8 и чтение очередной лексической единицы с входного регист5 Ра 1.

Поступившая на дешифратор 2 лекйИческая единица + есть операция (Х, «О. Блок 3 управления на тт.1фра-- торе 4 основ формирует код т(рмннала

1399741

Знак п.шос, записывает его в старшие разряды блока 5 памяти и Б буферный регистр 7, затем складьшает с содержимым сумматора 8. После этого происходит считывание очередной лексической единицы с входного регистра 1.

Лексическая единица С - оЛеранд, который формирует на шифраторе 4 код нетерминала F, Код нетерминала записывается в буферньй регистр 7, и , одновременно сдвигается содержимое блока 5 памяти влево на 1 разряд, затем код нетерминала суммируется с содержимым сумматора 8.

Очередная лексическая единица поступает на дешифратор 2 и определя- ется как закрьшающая скобка. Формируется код терминала Закрьшающая скобка, который записывается в блок 5 памяти.. Дешифратор 6 кодов операций по коду предыдущего терйинала определяет вид основы (). Код нетерминала основы F+F заносится в буферный регистр 7 и вычитается из содержимого сумматора, а содержимое . блока 5 памяти сдвигается на 2 разряда вправо. Код нетерминала F заносится в буферный регистр 7 и складывается с содержимым сумматора 8, Дешифратор 2 определяет текущую лексическую единицу как закрьшагощую скобку. Блок 3 управления формирует сигнал, которьй производит сдвиг влево на 1 разряд содержимого блока памяти и запись кода терминала Закрьшающая скобка в старшие разряды реверсивных сдвигающих регистров. Дешифратор & кодов операций определяет вид основы (F) (), так как в (N-})x разрядах реверсивных регистров сдвига содержится код тер- минала Открьвающая скобка. Код нетерминала основы записьшается в буферный регистр 7 и вычитьшается из сумматора В, Одновременно сдвигается содержимое блока 5 памяти на 2 разряда вправо, снимается блокировка с входного регистра 1, с которого на дешифратор 2 поступает лексическая единица ). В буферный регистр 7 заносится код нетерминала F и складывается с содержимым сумматора 8,

Текущая лексическая единица ) определяется дешифратором 2 как зак- рьюающая скобка ()5 происходит блокирование входного регистра . Далее устройство работает по циклу, описанному выше.

10

Текущая лекс1-гческая единица , определяетсп дешифратефом 2 как операция (Х4 О Сформированный шифратором 4 код терминала Знак умножить заносится в блок 5 памяти, в буферный регистр 7, складьгоается с содержимым сумматора 8 и осуществляется переход к следующей лексической

единице.

Очередная лексическая единица D - операнд. Б сумматоре 8 добавляется код нетерминала F, производится сдвиг влево на 1 разряд содержимого

го блока 5 памяти и выбирается следующая лексическая единица - конец вы- ражения,

Дешифратор 2 выделяет лексическую единицу, запускает шифратор 4 основ,

формирующий код терминала Конец выражения, который заносится в блок 5 памяти. На основании этого кода дешифратор 6 кодов операции разрешает .выбор основы вида F-i-F. Код нетерминала основы вычитается из сумматора 8, а затем к содержимому сумматора добавляется код нетерминала- F. Блок 3 управления разрешает выдачу содержимого сумматора 8 на вход блока 9 выделения аксиомы. Так как в

сумматоре 8 содержится код нетерминала F % то блок 9 выделения аксиомы запускает блок 3 мшсропрограммного управления, который успешно завершает синтаксический анализ исходного вы

ражения.

Пример 2. Пусть исходное выражение имеет вид ((А+В)С#, кото- рое содержит синтаксич.ескую ошибку нет закрьшающей скобки.

Лексическая единица (поступает через входной регистр 1 на дешифратор

2 и определяется как открывающая скобка. Запускается блок 3 управления, который блокирует входной регистр 1, формирует на шифраторе 4 основ код терминала Открыв ающая

скобка, который записывается в буферный регистр 7 р а такзке. сдвигается содержимое блока 5 памяти на 1 разряд влево. Код терминала заносится в блок 5 памяти, одновременно суммируется с содержимым сумматора 8, затем снимается блокировка с входного регистра 1 .и следующая лексическая единица ( поступает на дешифратор 2 лексических единиц.

Лексическая единица ( otKpbraa ющая скобка, и цикл устройства повторяется.

Очередная .лексическая единица А дешифрируется как операнд. На шифраторе 4 формируется код нетерминала F, который поступает в буферньй регистр 7, суммируется с содержимым сумматора 8, содержимое блока 5 памяти сдвигается на 1 разряд влево, и происходит чтение очередной лексической единицы. +, + - это операция, формируется код соответствующего терминала, которьш заноситсА в блок 5 памяти. Код терминала запй- сьшается в буферный регистр 7 и складывается с содержимым сумматора 8, после чего выбирается очередная лексическая единица В.

Дешифратор 2 определяет ее как операнд. Содержимое сумматора уве- :личивается на значение кода нетерминала F, блок 5 памяти подготавливается к приему очередного кода терминала.

Следующая лексическая единица ) дешифрируется как закрьшающая скобка. Шифратор основ формирует код терминала Закрьшающая скобка, который записьшается в блок 5 памяти. Дешифратор 6 кодов операций разрешает блоку 3;управления выбор основы F+F, Код нетерминала основы вычитается из сумматора 8, н в блоке 5 памяти содержимое сдвигается на 2 разряда вправо, содержимое сумматора складьшается с кодом нетерминала F . Дешифратор определяет текущую лексическую единицу как закрывающую скобку. Код терминала Закрьшающая скобка заносится в блок 5 памяти. Дешифратор 6 кодов операций разрешает выбор основы (F). Блок 3 управления считьшает очередную лексическую единицу х, одновременно из содержимого сумматора 8 вычитается код нетерминала основы, сбрасьгаается содержимое 2 старших разрядов в блоке 5 памяти, и к содержимому сумматора 8 добавляется код нет ерминала F.

Текущая лексическая единица Код терминала Знак

операция,

умножить записывается в блок 5 памяти, складьшается с содержимым сумматора 8, и происходит пере-ход к анализу следующей лексической единицы С. С - это операнд, код нетерминала

F суммируется с содержимым сумматора 8, а блок 5 памяти сдвигает содержимое на 1 разряд влево.

Очередная лексическая единица - конец выражения :#:. Код терминала записьшается в блок 5 памяти. Возбуждается блок 3 управления и выбирается основа F+F, код нетерминала которой вычитается из содержимого сумматора 8, сбрасьшаются 2 старших разряда блока 5 памяти, а содержимое сумматора 8 увеличивается на код нетерминала,F.

Дешифратор 2 определяет, что текущая лексическая единица - .конец выражения, и содержимое сумматора 8 по сигналу с блока 3 управления поступает на вход блока 9 выделения аксиомы, который определяет, что содержимое сумматора отлично от кода нетерминала F, и возбуждает в блоке 3 управления сигнал ошибки.

Формула изобретения

Синтаксический анализатор, содержащий входной регистр, дешифратор лексических единиц, блок управления,

шифратор основ, блок памяти, дешифратор кодов операций, буферный регистр и сумматор, причем информационный вход входного регистра является входом анализатора, выход внодного регистра подключен к входу дешифратора лексических единиц, выход которого подключен к первому входу блока управления, первый выход которого соединен с входом синхронизации

входного регистра, второй выход блока управления соединен с входом шифратора основ, выход которого соединен с информационными входами блока памяти и буферного регистра,

третий выход блока управления соединен с управляющим входом блока памяти, выход которого подключен к входу дешифратора кодов операций, вы-; ход которого соединен с вторым входом блока управления, четвертый

выход которого соединен с входом синхронизации буферного регистра, выход которого подключен к информационному входу сумматора, управляющий вход

которого соединен с пятым выходом блока управления, седьмой и восьмой

выходы которого являются соответственно выходами

Ошибка и Конец

анализа анализатора, о т л и ч а 13

ю щ и и с я тем, что, с целью расширения функциональных возможностей за счет обеспечения бесприоритетно

U

ления аксиомы, информационный вход которого соединен с выходом сумматора, управляющий вход и информаци

| название | год | авторы | номер документа |

|---|---|---|---|

| Синтаксический анализатор | 1986 |

|

SU1334149A1 |

| Синтаксический анализатор | 1987 |

|

SU1439594A1 |

| Синтаксический анализатор | 1987 |

|

SU1439591A1 |

| Устройство для перевода выражений в польскую инверсную запись | 1988 |

|

SU1571616A1 |

| Параллельный синтаксический анализатор | 1987 |

|

SU1465894A1 |

| Синтаксический анализатор | 1987 |

|

SU1439593A1 |

| Устройство для синтаксического контроля | 1986 |

|

SU1396146A1 |

| Устройство для перевода арифметических выражений в линейные регулярные префиксные формы | 1988 |

|

SU1742832A1 |

| Устройство для синтаксического контроля | 1986 |

|

SU1392563A1 |

| Устройство для преобразования выражений в польскую инверсную запись | 1985 |

|

SU1290358A1 |

Изобретение относится к вьиис- лительной технике и может быть ., пользовано в автоматизированных системах обработки данных и производства программ для ЭВМ, для поддержки процессов трансляции языков высокого уровня. Цель изобретения - расширение функциональных возможностей за счет обеспечения бесприоритетного синтаксического анализа исходных выражений при одновременном повышении быстродействия и упрощении устройства Для достижения указанных целей в устройство дополнительно введен блок 9 выделения аксиомы. Реализация бесприоритетного синтаксического анализа сокраТцает аппаратурные затраты и увеличивает быстродействие синтаксического анализатора. Кроме того, введение блока 9, управляемого блоком 3 микропрограммного управления, повьппает надежность и устойчивость работы синтаксического анализатора. 3 ил. (Л

го синтаксического анализа исходных ,. онный выход блока выделения аксиомы

выражений при одновременном повышении быстродействия и упрощении.анализатора, в него введен блок выдеподключены соответственно к шестому выходу и третьему входу блока управления.

Кдеши9Р(наоаамкави8

-п опералии

puf.2

подключены соответственно к шестому выходу и третьему входу блока управления.

уха.З

| Устройство для синтаксического контроля программ и данных | 1976 |

|

SU637818A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Синтаксический анализатор | 1986 |

|

SU1334149A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-05-30—Публикация

1986-07-11—Подача