bw

i4

о

4

сд tc

Изобретение относится к цифровой электроизмерительной технике и может найти применение при измерении интегральных характеристик переменного напряжения.

Цель изобретения - увеличение точности.

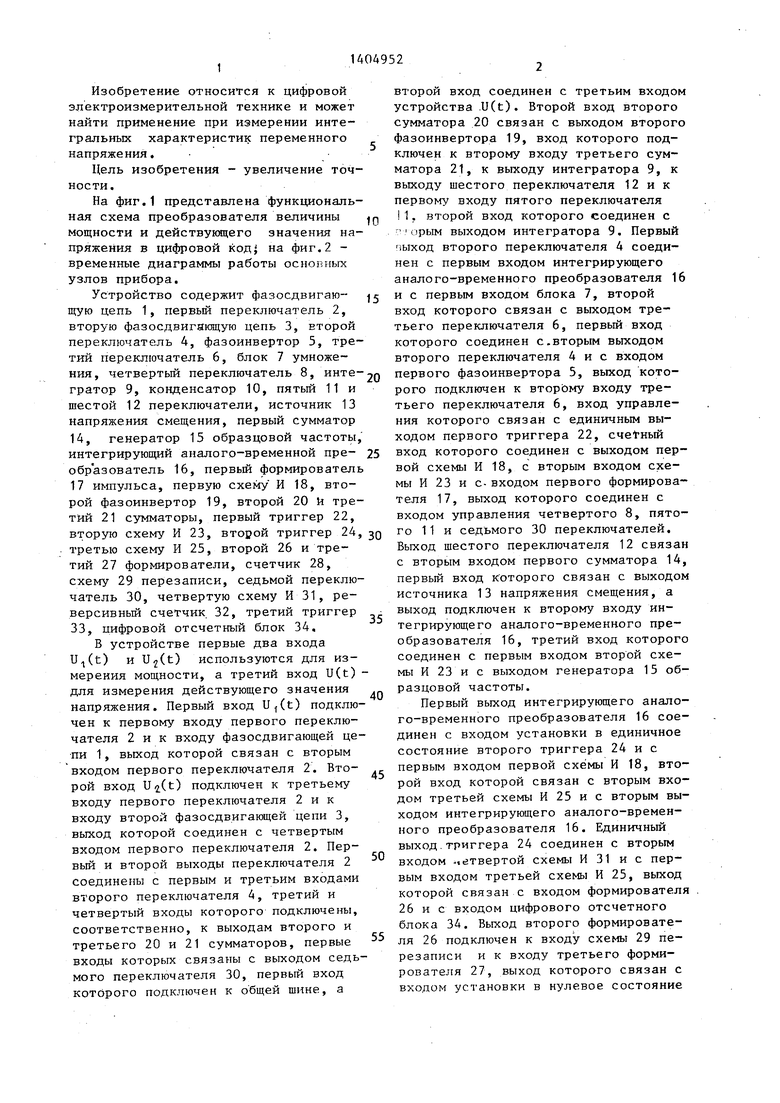

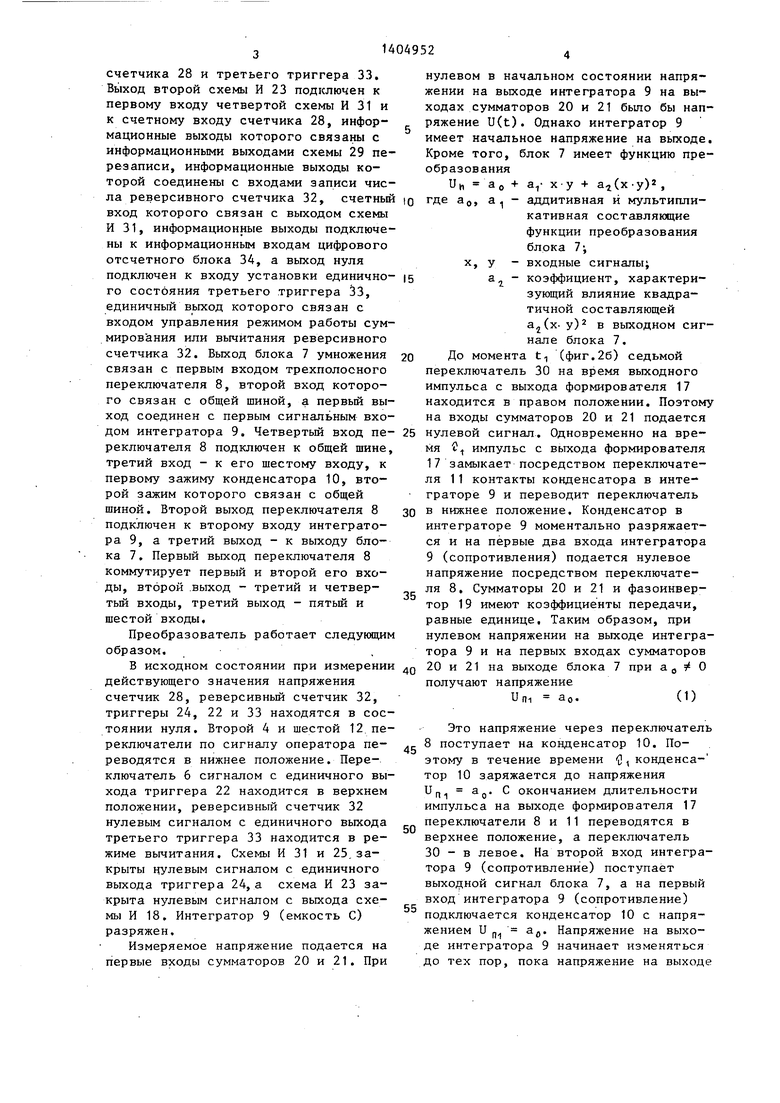

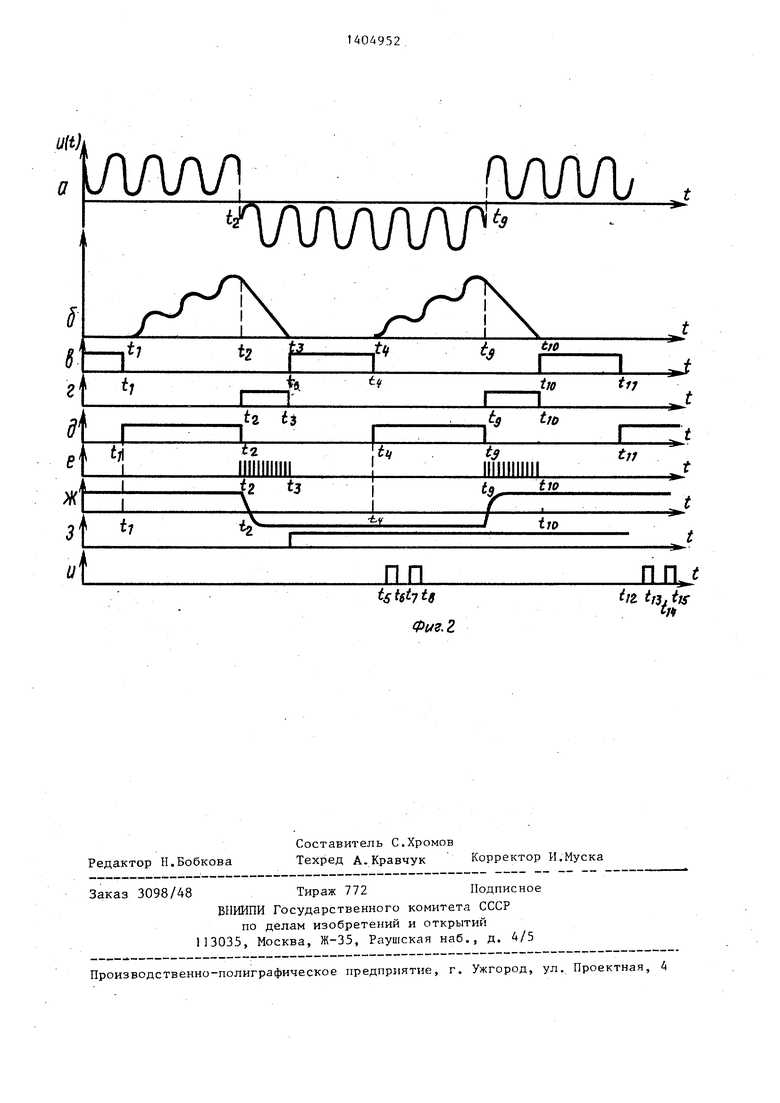

На фиг.1 представлена функциональная схема преобразователя величины мощности и действующего значения напряжения в цифровой код} на фиг.2 - временные диаграммы работы осногишгх узлов прибора.

Устройство содержит фазосдвигаю- щую цепь 1, первый переключатель 2, вторую фазосдвигающую цепь 3, второй переключатель 4, фазоинвертор 5, третий переключатель 6, блок 7 умножения, четвертый переключатель 8, интегратор 9, конденсатор 10, пятый 11 и шестой 12 переключатели, источник 13 напряжения смещения, первый сумматор 14, генератор 15 образцовой частоты, интегрирующий аналого-временной преобразователь 16, первый формирователь 17 импульса, первую схему И 18, второй фазоинвертор 19, второй 20 h третий 21 сумматоры, первый триггер 22, вторую схему И 23, второй триггер 24, третью схему И 25, второй 26 и третий 27 формирователи, счетчик 28, схему 29 перезаписи, седьмой переключатель 30, четвертую схему И 31, реверсивный счетчик 32, третий триггер 33, цифровой отсчетный блок 34.

В устройстве первые два входа U(t) и UjCt) используются для измерения мощности, а третий вход U(t) - для измерения действующего значения напряжения. Первый вход U,(t) подключен к первому входу первого переключателя 2 и к входу фазосдвигающей цепи 1, выход которой связан с вторым входом первого переключателя 2. Второй вход U(t) подключен к третьему входу первого переключателя 2 и к входу второй фазосдвигакяцей цепи 3, выход которой соединен с четвертым входом первого переключателя 2. Пер- вьй и второй выходы переключателя 2 соединены с первым и третьим входами второго переключателя 4, третий и четвертый входы которого подключены, соответственно, к выходам второго и третьего 20 и 21 сумматоров, первые входы которых связаны с выходом седьмого переключателя 30, первый вход которого подключен к о бщей шине, а

второй вход соединен с третьим входом устройства .U(t). Второй вход второго сумматора 20 связан с выходом второго фазоинвертора 19, вход которого подключен к второму входу третьего сумматора 21, к выходу интегратора 9, к выходу шестого переключателя 12 и к первому входу пятого переключателя

д И. второй вход которого соединен с - орым выходом интегратора 9. Первый пыход второго переключателя 4 соединен с первым входом интегрирующего аналого-временного преобразователя 16

5 и с первым входом блока 7, второй вход которого связан с выходом третьего переключателя 6, первый вход которого соединен с.вторым выходом второго переключателя 4 и с входом

0 первого фазоинвертора 5, выход которого подключен к второму входу третьего переключателя 6, вход управления которого связан с единичным выходом первого триггера 22, счетный

5 вход которого соединен с выходом первой схемы И 18, с вторым входом схемы И 23 и с- входом первого формирователя 17, выход которого соединен с входом управления четвертого 8, пятого 1 1 и седьмого 30 переключателей. Выход шестого переключателя 12 связан с вторым входом первого сумматора 14, первый вход которого связан с выходом источника 13 напряжения смещения, а выход подключен к второму входу интегрирующего аналого-временного преобразователя 16, третий вход которого соединен с первым входом второй схемы И 23 и с выходом генератора 15 образцовой частоты.

Первый выход интегрирующего аналого-временного преобразователя 16 соединен с входом установки в единичное состояние второго триггера 24 и с первым входом первой схемы И 18, второй вход которой связан с вторым входом третьей схемы И 25 и с вторым выходом интегрирующего аналого-временного преобразователя 16. Единичный выход.триггера 24 соединен с вторым входом 1етвертой схемы И 31 и с первым входом третьей схемы И 25, выход которой связан с входом формирователя 26 и с входом цифрового отсчетного блока 34. Выход второго формировате5 ля 26 подключен к входу схемы 29 перезаписи и к входу третьего формирователя 27, выход которого связан с входом установки в нулевое состояние

0

5

0

5

0

счетчика 28 и третьего триггера 33, Выход второй схемы И 23 подключен к первому входу четвертой схемы И 31 и к счетному входу счетчика 28, информационные выходы которого связаны с информационными выходами схемы 29 перезаписи, информационные выходы которой соединены с входами записи числа реверсивного счетчика 32, счетный вход которого связан с выходом схемы И 31, информационные выходы подключены к информационным входам цифрового отсчетного блока 34, а выход нуля подключен к входу установки единично- го состояния третьего триггера 33, единичный выход которого связан с входом управления режимом работы сум- миров ания или вьиитания реверсивного счетчика 32. Выход блока 7 умножения связан с первым входом трехполосного переключателя 8, второй вход которого связан с общей шиной, а первый выход соединен с первым сигнальным входом интегратора 9. Четвертый вход пе- реключателя 8 подключен к общей шине, третий вход - к его шестому входу, к первому зажиму конденсатора 10, второй зажим которого связан с общей шиной. Второй выход переключателя 8 подключен к второму входу интегратора 9, а третий выход - к выходу блока 7. Первый выход переключателя 8 коммутирует первый и второй его входы, второй .выход - третий и четвер- тьй входы, третий выход - пятый и шестой входы.

Преобразователь работает следующим образом,.

5 0 5

0

5

нулевом в начальном состоянии напряжении на выходе интегратора 9 на выходах сумматоров 20 и 21 было бы напряжение U(t), Однако интегратор 9 имеет начальное напряжение на выходе. Кроме того, блок 7 имеет функцию преобразования

UH ао + а,- х-у + ), где а о, а - аддитивная и мультипликативная составляющие функции преобразования блока 7; X, у - входные сигналы;

а - коэффициент, характеризующий влияние квадратичной составляющей у) в вьгходном сигнале блока 7,

До момента t (фиг,2б) седьмой переключатель 30 на время выходного импульса с выхода формирователя 17 находится в правом положении. Поэтому на входы сумматоров 20 и 21 подается нулевой сигнал. Одновременно на время С импульс с выхода формирователя 17 замыкает посредством переключателя 11 контакты конденсатора в интеграторе 9 и переводит переключатель в нижнее положение. Конденсатор в интеграторе 9 моментально разряжается и на первые два входа интегратора 9 (сопротивления) подается нулевое напряжение посредством переключателя 8, Сумматоры 20 и 21 и фазоинвер- тор 19 имеют коэффициенты передачи, равные единице. Таким образом, при нулевом напряжении на выходе интегратора 9 и на первых входах сумматоров

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой измеритель параметров комплексного сопротивления | 1986 |

|

SU1437799A1 |

| Цифровой измеритель RLC-параметров | 1986 |

|

SU1357874A1 |

| Цифровой измеритель температуры | 1985 |

|

SU1278622A1 |

| Цифровой измеритель составляющих комплексных сопротивлений | 1987 |

|

SU1456907A1 |

| Цифровой измеритель параметров комплексных сопротивлений | 1985 |

|

SU1302211A1 |

| Цифровой измеритель RLC-параметров | 1986 |

|

SU1337820A1 |

| Цифровой измеритель температуры | 1985 |

|

SU1303849A1 |

| Цифровой термометр | 1986 |

|

SU1404844A1 |

| Цифровой измеритель мощности переменного тока | 1988 |

|

SU1511702A1 |

| Устройство для измерения сопротивления | 1986 |

|

SU1429050A1 |

Изобретение относится к цифровой электроизмерительной технике и может быть применено при измерении интегральных характеристик переменного напряжения. Устройство содержит генератор 15 образцовой частоты, блок 7 умножения, интегрирующий аналого-вре- менной преобразователь 16, переключатель 2 и интегратор 9. Введение фазо- сдвигающих цепей 1 и 3, фазоинверто- ров 5 и 19, триггеров 22, 24 и 33, счетчика 28, источника 13 напряжения смещения, сумматоров 14, 20 и 21, переключателей 4, 6, 8, 11, 12 и 30, формирователей 17, 26 и 27 импульсов, схем И 18, 23, 25 и 31, схемы 29 перезаписи, конденсатора 10, реверсивного счетчика 32 и цифрового отсчет- ного блока увеличивает точность пре-i образования. 2 ил. Q S сл

В исходном состоянии при измерении Q 20 и 21 на выходе блока 7 при а э О

(1)

действующего значения напряжения счетчик 28, реверсивный счетчик 32, триггеры 24, 22 и 33 находятся в состоянии нуля. Второй 4 и шестой 12 переключатели по сигналу оператора переводятся в нижнее положение. Переключатель 6 сигналом с единичного выхода триггера 22 находится в верхнем положении, реверсивный счетчик 32 нулевым сигналом с единичного выхода третьего триггера 33 находится в режиме вычитания. Схемы И 31 и 25. закрыты нулевым сигналом с единичного выхода триггера 24, а схема И 23 закрыта нулевым сигналом с выхода схемы И 18, Интегратор 9 (емкость С) разряжен.

Измеряемое напряжение подается на первые входы сумматоров 20 и 21, При

получают напряжение Um ао.

45

50

55

Это напряжение через переключатель 8 поступает на конденсатор 10, Поэтому в течение времени О, конденса- тор 10 заряжается до напряжения UHI 0 окончанием длительности импульса на выходе формирователя 17 переключатели 8 и 11 переводятся в верхнее положение, а переключатель 30 - в левое. На второй вход интегратора 9 (сопротивление) поступает выходной сигнал блока 7, а на первый вход интегратора 9 (сопротивление) подключается конденсатор 10 с напряжением и р ад. Напряжение на выходе интегратора 9 начинает изменяться до тех пор, пока напряжение на выходе

получают напряжение Um ао.

Это напряжение через переключатель 8 поступает на конденсатор 10, Поэтому в течение времени О, конденса- тор 10 заряжается до напряжения UHI 0 окончанием длительности импульса на выходе формирователя 17 переключатели 8 и 11 переводятся в верхнее положение, а переключатель 30 - в левое. На второй вход интегратора 9 (сопротивление) поступает выходной сигнал блока 7, а на первый вход интегратора 9 (сопротивление) подключается конденсатор 10 с напряжением и р ад. Напряжение на выходе интегратора 9 начинает изменяться о тех пор, пока напряжение на выходе

блока 7 не станет равным нулю, выполняется равенство

т.е.

ао+ aJU(t) - (t) +U,,, Uni 0.

Отсюда

) - U2J О и

и

К1

(2) (3)

и

kf

U4t), е 0(t) - усредненное значение

квадрата напряжения U(t) ; - напряжение на выходе интегратора 9. При этом на первый вход блока 7 ступает напряжение

и, (t) U(t) - UKI, (4). на второй вход с выхода переключателя 6

1г

(k-U,

bt(tj t,)fo

где tj- t - длительность второго такта интегрирования i tj-t| - длительность первого

такта интегрирования преобразователя 16.

Временной интервал tjTtj выделяется схемой И 18, исходя из напряжений (фиг.2в и д) на выходе блока 14, на время ее выходной сигнал поступает на второй вход схемы И 23, первый вход которой подключен к выходу -генератора 15 образцовой частоты. Поэтому к моменту tз на вход счетчика 28 поступает число импульсов (фиг,2е)

Nf fo(4- Ч

. kUki

где b и b - константы, определяемые конструкцией интегрирующего аналого-временного преобразователя 16; f(5 - частота следования импульсов генератора 15 образцовой частоты, В момент t триггер 22 опрокидывается в единичное состояние, и переводит переключатель 6 в нижнее положение. Одновременно запускается первый формирователь 17, который замыкает на короткое время 2, посредством переключателя 11 контакты конденсаи,, (t) tuCt) + UK, . (5) Напряжение (3) поступает на вход первого сумматора 14, выходное напря- жение которого равно

Ui k(UcM + UM) + Цдр, (6) где Цдр - дрейф нуля сумматора 14;

k - коэффициент передачи сумматора 14, Ucy, - напряжение источника 13,

Это напряжение (фиг,2а) совместно с напряжением помехи поступает на второй вход интегрирующего аналого- временного преобразователя 16, ив процессе двухтактного интегрирования (фиг,2б) на выходе схемы И 18 получают временной интервал (фиг.2г), пропорциональный значению U-j:

р)ас - k-U,(t, - t,)

0

h f (

b

тора в интеграторе 9 и переводит переключатель 30 в правое положение, а переключатель 8 - в нижнее. Это разряжает конденсатор С до нулевого напряжения (рис,2ж) и заряжает конденсат тор 10 до иП1 Эр. В момент t, сигналом с выхода интегрирующего анало- го-временного преобразователя 16 (фиг.2в) триггер 24 устанавливается в единичное состояние (фиг,2з), от- крывая схему И 25 по первому входу, а схему И 31 по второму входу. За время ll действия импульса на выходе формирователя 17 конденсатор 10 успевает зарядиться до напряжения U „

0

5

0

а, (фактически заряжается при изменении а,), К моменту t заканчивается переходной процесс в блоках 19-21, 7, 5 и 9, напряжение на выходе интегратора 9 принимает отрицательное значение вследствие введения на второй вход блока 7 фазоинвертора 5. Б момент равновесия напряжение на выходе блока 7 равно нулю, т.е.

а, a,U4t) - U2 3- и,, 0 (9)

или

о.

(10)

-a,U4t) - Отсюда

Uk -fu4t).

5 На сумматора 14 получают напряжение

иг k(-U К2+ UCM) + идр , (11) которое на время tg-t (фиг.2д) подается к входу интегрирующего аналогоtg-t

временного преобразователя 16. Одновременно импульс длительностью (фиг,2д) поступает через открытую схему И 25 на вход цифрового отсчет- ного блока 34 и вход второго формирователя 26 импульса. Его выходной импульс длительностью tj-tj- (фиг.2и) записывает в реверсивный счетчик 32 код числа N, и запускает формирователь 27 импульса, выходной импульс которого сбрасывает в нуль счетчик 28 и подтверждает, нулевое состояние триггера 33. К моменту t. к входу интегрирующего аналого-вре- менного преобразователя 16 прикладывается напряжение Uj, а от момента t | - до момента t - напряжение U цд, противоположной полярности к и, причем

tgЧ

чt п Т. в про-

цессе двухтактного интегрирования Ig

CM

t

ч- j b,f,(t9 - t)dt

+ U«) + UAP dt Hна вход счетчика 28 и через схему

И 31 на вход реверсивного счетчика 32

в вычитающем за время

ts 10r

25 тояние и своим выходным импульсом опрокидывает триггер 33 в единично состояние. Выходной сигнал на его единичном выходе переводит реверси ньй счетчик 32 в режим суммировани

30 и последующие N - N импульсы чис

b - 3 dt (tj-tp ла Ni зафиксируются в реверсивном

счетчике 32. В момент окончания ин грирования число N - N импульсов сигналом с выхода схемы И 25 зафик руется в цифровом отсчетном блоке Таким образом,, в каждом последующе цикле формируется результат измере ния в реверсивном счетчике 32 и те самым в цифровом отсчетном блоке

поступает числ о импульсов

9

b - j(k-U, + UAp)dt N, )

kUKz

b,

.(13)

Поскольку и K7 -yU(t), TO, подставляя это значение в выражение (13),

в (В), имеют

N,

NI

так как t., - t t , - t

bi(t, - ti) .

t. U и, и тем самьЕ N N , менту t д в реверсивном сче зафиксируется код числа

Nvi - N

г

- I i/Fct), °1

пропорциональный действующему значеI2k

нию напряжения U(t) при g- кратном

„ 10, где m О, 1, 2,

висящий от и,-, и

см

и

ftp -о

и не за- п-Т, а,

В счетчике 28 к MOMeHTv t,- за20

10

фиксируется код числа N (15). В момент tj триггер 22 опрокинется в нулевое состояние и переведет переключатель 6 в верхнее положение. В момент в цифровой отсчетный блок 34

10 записывается код числа N,- Nj. Импульс ()j t,j t fj с выхода формирователя 26 переписывает код числа N в реверсивный счетчик 32, а импульс длительностью IJi t - tj

15 с выхода формирователя 27 сбрасывает в нулевое состояние счетчик 28 и подтверждает нулевое состояние триггера 33. В процессе двухтактного преобразования напряжения U, (6) на вход счетчика 28 и реверсивного счетчика 32 поступает код числа N. Поскольку N, то к моменту прихода NJ импульсов числа N, реверсивный счетчик 32 переходит в нулевое сос25 тояние и своим выходным импульсом опрокидывает триггер 33 в единичное состояние. Выходной сигнал на его единичном выходе переводит реверсив- ньй счетчик 32 в режим суммирования

30 и последующие N - N импульсы числа Ni зафиксируются в реверсивном

ла Ni зафиксируются в реверсивном

35

,

40

45

50

55

счетчике 32. В момент окончания интегрирования число N - N импульсов сигналом с выхода схемы И 25 зафиксируется в цифровом отсчетном блоке 34. Таким образом,, в каждом последующем цикле формируется результат измерения в реверсивном счетчике 32 и тем самым в цифровом отсчетном блоке 34.

При измерении активной Р и реактивной Q мощности предлагаемое устройство работает следующим образом.

При измерении активной мощности по сигналу оператора переключатели 2, 4 и 12 переводятся в верхнее положение. Первый сомножитель U,(t) kj-i(t), пропорциональньй значению тока i(t) в нагрузке, поступает на первый вход блока 7 умножения и первый вход интегрирующего анапого-вре- менного преобразователя 16. Второй сомножитель U.2(t) k|.( U(t), пропорциональный значению напряжения U(t) на сопротивлении нагрузки, поступает в первом цикле непосредственно на второй вход блока 7 при нахождении переключателя 6 в исходном состоянии в верхнем положении, . k, ky- коэф- фициенты преобразования тока и напряжения соответственно. Счетчики 28 и 32, триггеры 22, 24 и 33 сброшены в состояние нуля в исходном положении как и при измерении действующего значения напряжения. Во втором цикле напряжение ) поступает на блок 7 через фазоинвертор 5 и переключатель 6, который )В этом случае находится

15

в нижнем положении. На выходе блока 7 ю время соседних двух циклов преобразо- в первом цикле получают напряжение (фиг,2а, моменты O..tj)

и,( (t) ао + ,U(t)i(t), (17) а во втором цикле (фиг.2а, моменты 12. t j)

(t) а„ - a,k«ki.U(t).i(t).(18)

Знак - появился за счет включения фазоинвертора 5, коэффициент передачи которого равен -1 (повторитель напряжения с инверсией полярности) , На выходе сумматора 14 получают в первом и втором циклах напряжения

и + ао + a,kukvU(t)i(t) + UAp;

(19)

Uj + ао- aikuk4U(t)i(t)j + Ндр ;

(20)

аналогично как при измерении действующего значения напряжения.

вания. В дальнейшем работа устройства аналогична его работе как н. при измерении действующего значения напряжения.

При измерении реактивной мощности переключатель 2 посредством оператора переводится в нижнее положение, а схема в исходное состояние, при котором счетчики 28 и 32 и триггеры 22,

20 24 и 3.3 сбрасываются в нуль, схемы И 18, 25 и 31 закрыты, фазосдвигающие цепи 1 и 3 образуют фазорасщепляющую цепь на 90°, причем коэффициенты передачи напряжения U .,(t) и V(t ) оди25 наковы в диапазоне частот и равны единице.

Поэтому в процессе двухтактного преобразования выходных напряжений

сумматора 14, аналогично как и при В процессе двухтактного преобразо- зо измерении активной мощности, получают вания напряжений в выражениях (19) и (20) число импульсов

N(

fo(t3 - ta)

b - (UCM + a.,) + UApJdt - kkukjai/ U(t)i(t)dt

b (ta - tO N, f o(t ,0 - tg)

4 I y

b - )k(Uc + a) + UApj.dt

L...--

.a (t)i(t)dt

+ b7Tt--- t7T

так как ti-ti t9-t

К моменту t ,g аналогично как измерении действующего значения ряжения, в реверсивном счетчике

п-Т

зафиксируется код числа

1

.a, J U(t)i(t)dt

XT XT - ....«iv.-...«.

2kir b,(e, -t,) ----bf- (23)

Результат измерения не зависит от частоты входных колебаний, параметро ао, с, и др. см блоков 7 и 13. Зна- 55 чение U при измерении U, Р и g вы

где Р --- U(t)i(t)dt - значе- бирается достаточно большим, чтобы ... „„1..1:.,.. пбегпечить однополярное напряжение

ние активной мощности; , - коэффициент преоб- разовання мощности.

обеспечить однополярное

на выходе сумматора 14 в двух циклах

измерения.

При выборе

10

2kkukia t 2kkp Ь7

10

где m О, 1, 2, 3, ... вьфажение (23) пропорционально активной мощности Р и не зависит от значения параметров

п-Т, Ц

см

и

Ар

цепи аналогоцифрового преобразования. Их стабильность требуется обеспечить лишь на

время соседних двух циклов преобразо-

вания. В дальнейшем работа устройства аналогична его работе как н. при измерении действующего значения напряжения.

При измерении реактивной мощности переключатель 2 посредством оператора переводится в нижнее положение, а схема в исходное состояние, при котором счетчики 28 и 32 и триггеры 22,

24 и 3.3 сбрасываются в нуль, схемы И 18, 25 и 31 закрыты, фазосдвигающие цепи 1 и 3 образуют фазорасщепляющую цепь на 90°, причем коэффициенты передачи напряжения U .,(t) и V(t ) одинаковы в диапазоне частот и равны единице.

Поэтому в процессе двухтактного преобразования выходных напряжений

40

а в реверсивном счетчике 32 зафикси- 45 руется код числа

N, -N,

bi

при

0

ti-t, t9-t

n.T, 2k. Ъ

(26) 10..

Результат измерения не зависит от частоты входных колебаний, параметров ао, с, и др. см блоков 7 и 13. Зна- 55 чение U при измерении U, Р и g выj-g чение и при и.) д .. - -.

бирается достаточно большим, чтобы пбегпечить однополярное напряжение

бирается достаточно большим, чтобы пбегпечить однополярное напряжение

обеспечить однополярное

на выходе сумматора 14 в двух циклах

измерения.

Формула изобрете ни

Преобразователь величины мощности и действукицего значения напряжения в цифровой код, содержащий генератор образцовой частоты, блок умножения, интегрирующий аналого-временной преобразователь, переключатель, интегратор, отличающийся тем, что, с целью увеличения точности, в него дополнительно введены две фазо- сдвигающие цепи, два фазоинвертора, три триггера, счетчик, источник напряжения смещения, три сумматора, шесть переключателей,, три формирователя импульсов, четыре схемы И, схема перезаписи, конденсатор, реверсивный счетчик, цифровой отсчетный блок, причем первый и второй входы по изме- рению мощности соединены с первым и третьим входами первого переключателя и с входами первой и второй фазосдви- гающих цепей, выходы которых соединены соответственно с вторым и четвертым .входами первого переключателя, первый и второй выходы его соединены с первым и третьим входами второго переключателя соответственно, а второй и четвертый входы подключены к выходам первого и второго сумматоров соответственно, первый выход второго предохранителя соединен с первым входом блока умножения и первым входом аналого-временного преобразователя, а второй выход второго переключателя подключен к первому входу третьего переключателя и через фазоинвертор - к второму входу третьего переключате-

входом блока умножения, выход которого подключен к первому входу четвертого переключателя, к третьему его выходу и второму входу шестого переключателя, второй и четвертый входы четвертого переключателя соединены с общей шиной, а третий и шестой его входы подключены к одной обкладке конденсатора, а вторая его обкладка соединена с общей шиной, первый и второй выходы четвертого переключателя соединены с первым и вторым входами интегратора, выход которого подключен через второй фазоинвертор к первому входу первого сумматора, к первому входу второго сумматора и к первому входу шестого переключателя, выход которого соединен со вторым входом третьего сумматора, первый

5

0

о

вход которого подключен к выходу источника напряжения смещения, а выход- к второму входу аналого-временного преобразователя, третий вход которог о соединен с генератором образцовой частоты и первым входом второй схемы И, первый выход аналого-временного преобразователя подключен к первому входу первой схе1- ы И и первому входу второго триггера, выход которого соединен с первым входом третьей схемы И и вторым входом четвертой схемы И, второй выход аналого-временного преобразователя соединен с вторым входом первой схемы И и вторым входом третьей схемы И, выход первой схемы И соединен со счетным входом первого триггера, с вторым входом второй схе мы И и с входом первого формирователя импульса, выход которого соединен с управляющими входами четвертого, пятого и седьмого переключателей, первый вход которого связан с входом

5 по измерению действующего значения напряжения, второй его вход соединен с общей шиной, а выход - с вторыми входами первого и второго сумматоров,

выход второй схемы И подключен к первому ВХОДУ четвертой схемы И и к с счетному входу счетчика, вход установки в О которого подключен к выходу третьего формирователя импульса и к входу установки в О третьего триггера, а информационные выходы счетчика связаны с информационными входами схемы перезаписи, вход управления которой подключен к выходу второго формирователя импульса и к входу третьего формирователя импульса, а информационные выходы схемы перезаписи соединены с входами записи числа реверсивного счетчика, выход нуля которого подключен к входу установки в 1 третьего триггера, еди- ничньш выход которого соединен с вхо - дом управления режимом суммирования и вычитания реверсивного счетчика, счетный вход которого связан с выходом четвертой схемы И, а информационные выходы подключены к информационным входам цифрового отсчетного блока, вход управления которого соединен с входом второго формирователя импульса и с выходом третьей схемы И, а пятьш переключатель своим входом подключен к управляющему входу интегратора, а выходом - к выходу интегратора.

5

5

0

5

u(th

.1ЛАА/1

3

I

ОАЛЛЛЛЛ

олл/ъ

.2

| 1972 |

|

SU468159A1 | |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Пасынков Ю.А | |||

| Об одном способе построения преобразователей интегральных характеристик переменных напряжений и мощности в интервал времени.- Контрольно-измерительная техника, 1969, № 7, с | |||

| Прибор для равномерного смешения зерна и одновременного отбирания нескольких одинаковых по объему проб | 1921 |

|

SU23A1 |

Авторы

Даты

1988-06-23—Публикация

1986-11-04—Подача