1П

H;io6peTeiiHe относится к :злектрот мерител1 иой технике и может быть ис- пол1,зс)ва11о при измерении RLC-парамет роп в широком частотном диапазоне,

Црлью изобретения является повышение точ)1ости измерений RLC-napa- метров в широком диапазоне частот при обеспечении высокой чувствительности и быстродействия путем введени эффективных адаптивно-мультипликативных коррекций и режима накопления и формирования результатов после каждого цикла измерений.

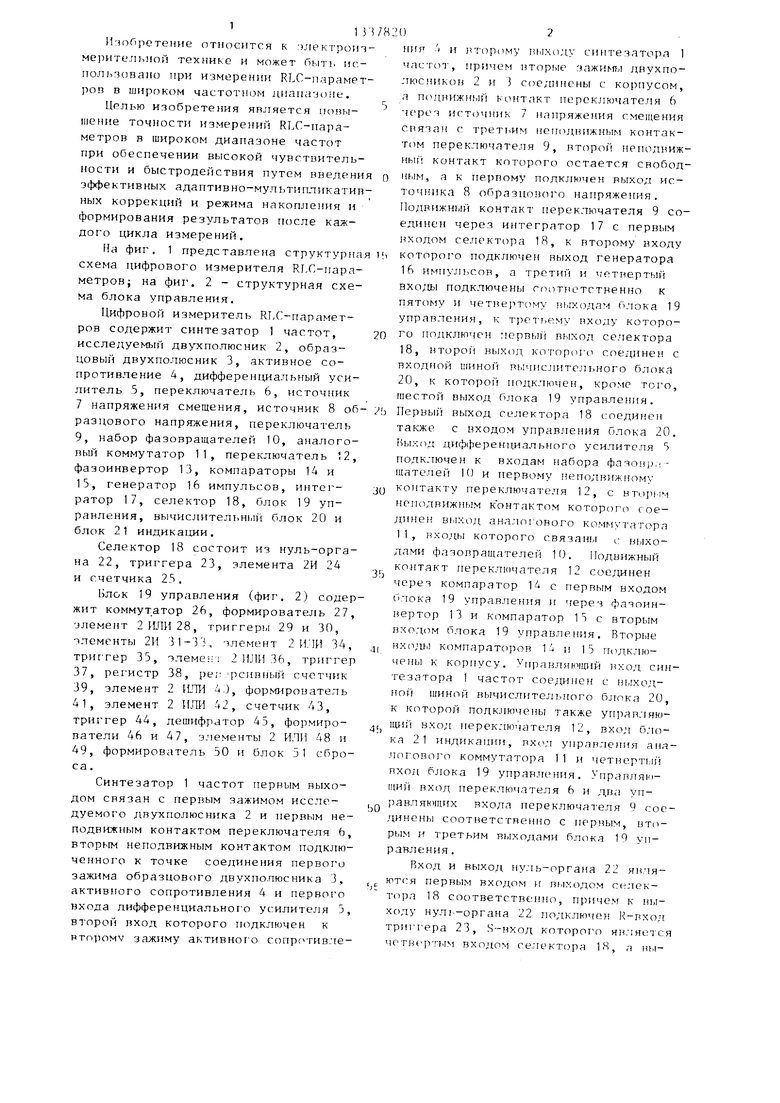

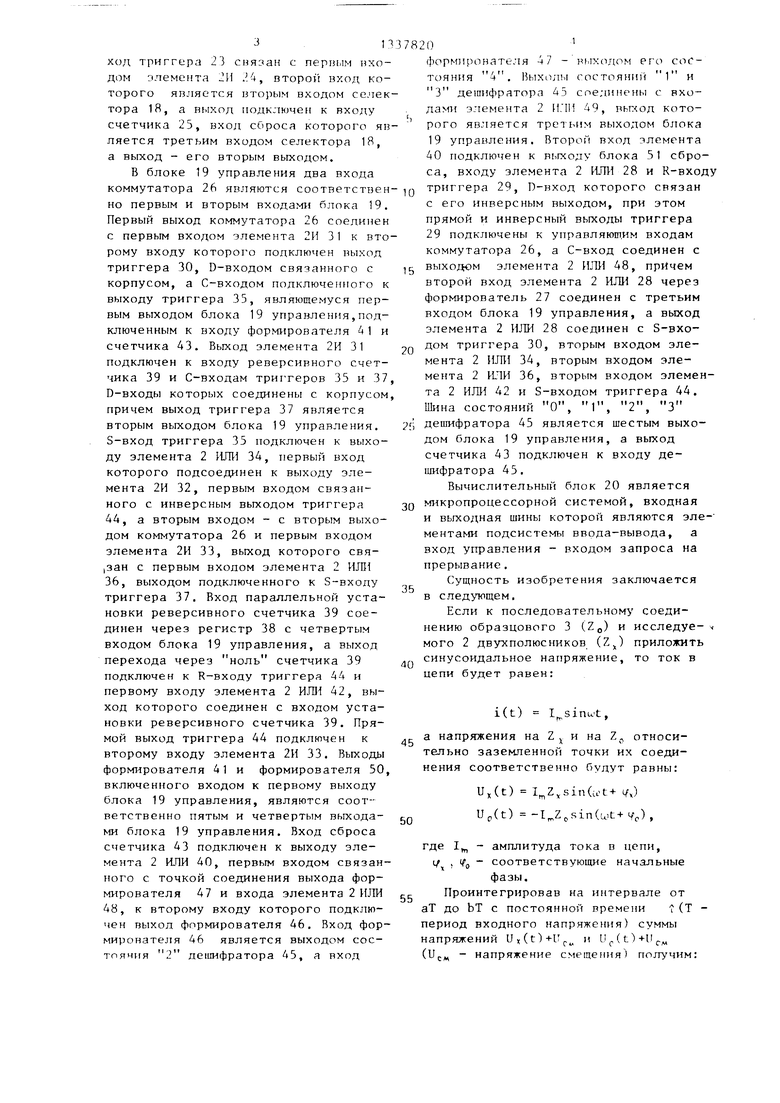

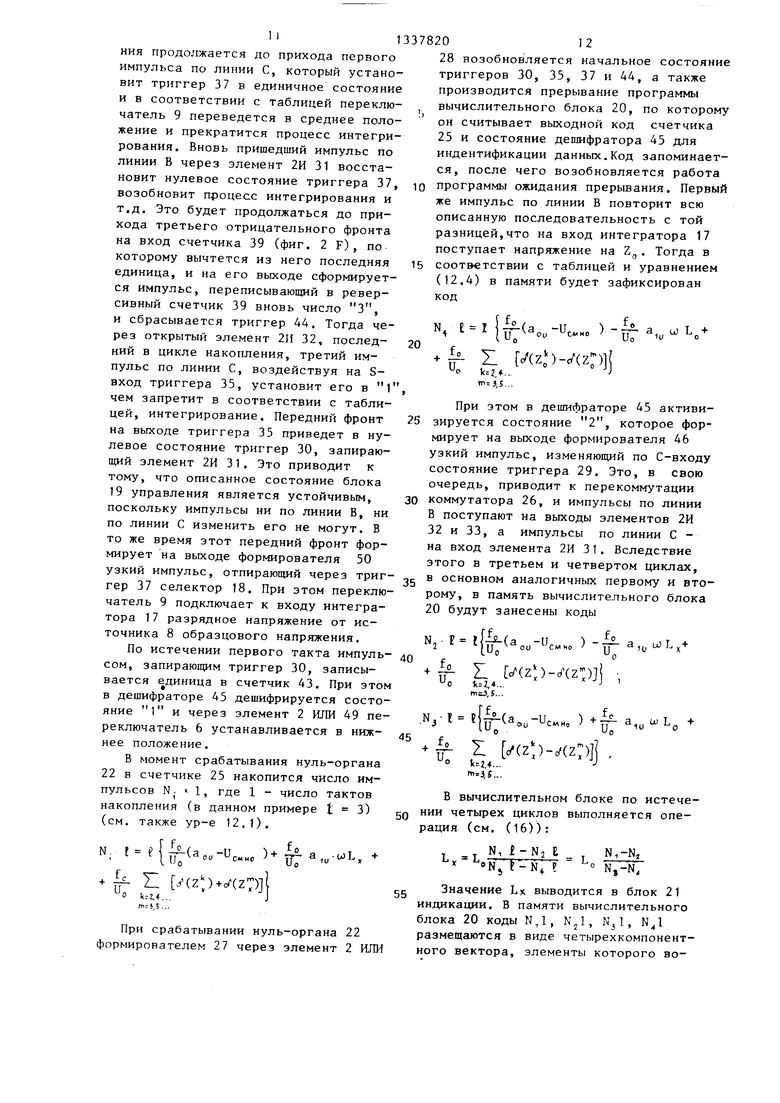

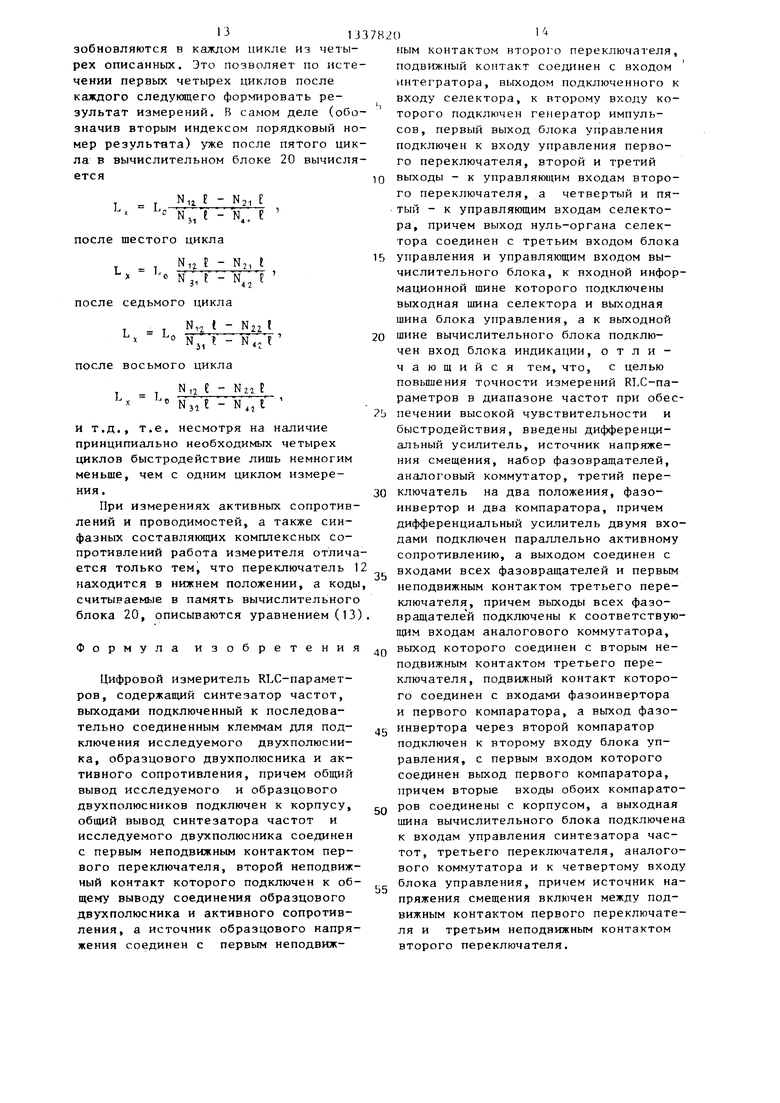

fia фиг. 1 представлена структурна схема цифрового измерителя RLC-лара- метров; на фиг. 2 - структурная схема блока управления.

Цифровой измеритель RT.C-парамет- ров содержит синтезатор 1 частот, исследуемый дв тсполюсник 2, образцовый двухполюсник 3, активное сопротивление 4, дифференидеальный усилитель 5, переключатель 6, источник 7 напряжения смещения, источник 8 образцового напряжения, переключатель 9, набор фазовращателей 10, аналоговый коммутатор 11, переключатель 12, фазоинвертор 13, компараторы 14 и 15, генератор 16 импульсов, интегратор 17, селектор 18, блок 19 управления, вычислительный блок 20 и блок 21 индикации.

Селектор 18 состоит из нуль-органа 22, триггера 23, злемента 2И 2Д и счетчика 25.

Блок 19 управления (фиг. 2) содержит коммутатор 26, формирователь 27, элемент 2 ИЛИ 28, триггеры 29 и 30, злеме нты 2И 31-33, -элемент 2 ИЛИ 34, тригтер 35, элеме:-; 2 ИЛИ 36, триггер 37, регистр 38, ре;: /рсивньй счетчик 39, элемент 2 ШТИ 4:), форм фонатель 41, элемент 2 Ш 42, счетчик 43, триггер 44, дешифратор 45, формирователи 46 и 47, элементь 2 ИЛИ 48 и 49, формирователь 50 и блок 51 сброса .

Синтезатор 1 частот первым выходом связан с первым зажимом исследуемого двухполюсника 2 и первым неподвижным контактом переключателя 6, вторым неподвижным контактом подключенного к точке соединения первого зажима образцового двухполюсника 3, активного сопротивления 4 и первого входа дифференциального усилителя 5, второй вход которого подключен к второму зажиму активног о сопротивле

0

Ь

О2

иия 4 и }ггорому гилхилу синтезатора 1 частот, причем nTopi)ie двухпо- :тюсников 2 и 3 соединены с корпусом, а ПОДВИЖНЫ контакт переключателя 6 через ист(чник 7 напряжения смещения связан с трет11им неггодвижным контактом переключателя 9, второй неподвижный контакт которого остается свобод- HF.IM, а к первому подключен выход источника 8 образцового напряжения. Подвижный контакт переключателя 9 соединен через интегратор 17 с первым ходом селектора 18, к второму входу которого подключен выход генератора 16 импульсов, а третий и четвертый входы подключены соответственно к пятому и четвертому выходам плока 19 управления, к третьему входу которого подключен перпыГг в.|ход селектора 18, второй выход которого соединен с вxoдF oй шиной В1,1числительного блока 20, к которой подключен, кроме того, шестой выход блока 19 управления. Первый выход селектора 18 соединен также с входом управления блока 20. Выход диф(}1еренциального усилителя S подключен к входам набора фазоп ; :;- щатслей И) и первому неподвижному

30

контакту переключателя .

с BTOpt-IM

1.

Ь

О

не11(1движным к онтактом которого соединен выход анало1-ового кoм yтa ropa 11, входы которого связаны с выходами фазовращателей 10. Подвижный контакт переключателя 12 соединен через компаратор 14 с первым входом б;гока 19 управления и через фазоинвертор 13 и компаратор 15 с вторым входом блока 19 управления. Вторые BX( Uii компаратс)ров 14 и 15 ггодклю- чены к корпусу. Управляюпхий вход синтезатора 1 частот соединен с выходной шиной вычислительного блока 20, к которой подключены также упрявляю- 1ЦИЙ вход переключателя 12, вход 6;io- ка 21 индикации, управления апя- логового коммутатора 1 1 и четш ртыГ вход блока 19 управления. Управляк - щиГ вход переключателя 6 и два управляющих входа переключателя 9 соединены соответстве1ню с первым, вто- р|лм и третьим выходами блока 19 управления .

Вход и выход нуль-органа 22 являются первым входом и п(.1ходом селектора 18 соответственно, причем к выходу нуль-органа 22 подключен R-BXO/I триггера 23, S-вход которого является четвертым входом селектора 1Я, л иь131

ход триггера 23 связан с першлм нхо- дом элемента 2И 24, BTOpoJi вход которого является вторым входом селектора 18, а выход подключен к входу счетчика 25, вход сброса которого является третьим входом селектора 18, а выход - его вторым выходом.

В блоке 19 управления два входа коммутатора 26 являются соответствен но первым и вторым входами блока 19. Первый выход коммутатора 26 соединен с первым входом элемента 2И 31 к второму входу которого подключен выход триггера 30, D-входом связанного с корпусом, а С-входом подключенного к выходу триггера 35, являющемуся первым выходом блока 19 управления,подключенным к входу формирователя 41 и счетчика 43. Выход элемента 2И 31 подключен к входу реверсивного счетчика 39 и С-входам триггеров 35 и 37 D-входы которых соединены с корпусом причем выход триггера 37 является вторым выходом блока 19 управления. S-вход триггера 35 подключен к выходу элемента 2 ИЛИ 34, первый вход которого подсоединен к выходу элемента 2И 32, первым входом связанного с инверсным выходом триггера 44, а вторым входом - с вторым выходом коммутатора 26 и первым входом элемента 2И 33, выход которого свя- |3ан с первым входом элемента 2 ИЛИ 36, выходом подключенного к S-входу триггера 37. Вход параллельной установки реверсивного счетчика 39 соединен через регистр 38 с четвертым входом блока 19 управления, а выход перехода через ноль счетчика 39 подключен к R-входу триггера 44 и первому входу элемента 2 ИЛИ 42, выход которого соединен с входом установки реверсивного счетчика 39. Прямой выход триггера 44 подключен к второму входу элемента 2И 33. Выходы формирователя 41 и формирователя 50, включенного входом к первому выходу блока 19 управления, являются соответственно пятым и четвертым выхода- ми блока 19 управления. Вход сброса счетчика 43 подключен к выходу элемента 2 ИЛИ 40, первым входом связанного с точкой соединения выхода формирователя 47 и входа элемента 2 ИЖ 48, к второму входу которого подключен выход формирователя 46. Вход формирователя 46 является выходом состояния

дешифратора 45, а вход

20

формирор ателя 4 7 - НЫУ.ОДОМ его состояния 4. IShixdjibi состояний 1 и 3 дешифратора 45 соелинены с входами элемента 2 ИЛИ 49, выход которого является третьим выходом блока 19 управления. Второй вход элемента 40 подключен к выходу блока 51 сброса, входу элемента 2 ИЛИ 28 и R-вхо триггера 29, D-вход которого связан с его инверсным выходом, при этом прямой и инверсный выходы триггера 29 подключены к управляющим входам коммутатора 26, а С-вход соединен с выходом элемента 2 ИЛИ 48, причем второй вход элемента 2 ИЛИ 28 через формирователь 27 соединен с третьим входом блока 19 управления, а выход элемента 2 ИЛИ 28 соединен с S-вхо- дом триггера 30, вторым входом элемента 2 ИЛИ 34, вторым входом элемента 2 НИИ 36, вторым входом элемета 2 ИЛИ 42 и S-входом триггера 44. Шина состояний О, 1, 2, 3 дешифратора 45 является шестым выходом блока 19 управления, а выход счетчика 43 подключен к входу дешифратора 45.

Вычислительный блок 20 является микропроцессорной системой, входная и выходная шины которой являются эле ментами подсистемы ввода-вывода, а вход управления - входом запроса на прерывание.

Сущность изобретения заключается в следующем.

Если к последовательному соединению образцового 3 (ZQ) и исследуе- мого 2 двухполюсников (Z,) приложить синусоидальное напряжение, то ток в цепи будет равен:

i(t) I sinu t,

а напряжения на Z и на Z,, относительно заземленной точки их соединения соответственно будут равны:

) .sinCu t-t- I/O Up(t) ,sin(u t+i/),

где I - амплитуда тока в цепи, I/ , If3 - соответствую1аие начальные

фазы.

Проинтегрировав на интервале от аТ до ЬТ с постоянной времени 7(Т период входного напряжения) суммы напряжений Ux(t)-t-Uj, и и,(ь) ( - напряжение смещения) похгучим:

Ьт t,T 13378206

и . -li Т Z,sin(cot4V.)dtn( U,,dt Учитывая (1)-(8). можно избрать

ат Т J пределы интегрирования для перечистт 01/1.4 гт,ленных случаев.

2IN . (b-a) , fwT х ч 1rr

-л-- - (b-a)+tfj, и- (-Пределы интегрирования являются

фазовыми значениями в цепи, началь+ J. и ) фаза которого выбрана равной нулю.

t Таким образом, выбирая пределы

Ы 4,тинтегрирования, на выходе интегра„ 1(т„., ч.If 10тора можно получить:

Ч ° Т (t )dt-bT5 1 Uc;« dt

21 ufl:Cb-a) 1Uy,, а„у+а, Z,sin Lf, +

.|k3in(,(b-a)..,., i:;V(z;).c.(z:) (9.1)

+ 4u,T(b-a). 5U J ,- a,,-a,yZ sinc/, +

+ Z Zh- (z)(9.2)

Рассмотрим случаи, когда Uy про- Л.ч..

порционально Z,.sin ч ... а U,. пропор-i7 v

г, Д о и,; a.,,;-t-a,L, ZpSin u +

ционально -ZpSin i/. Для этого необ-

ходимо, чтобы 20 ZjAZ)+ (Z) (9.3)

i 0u;:;f a.-a,,Z,sin..

. .T(b-a) , - , (o) (9.A)

sin -.™. 0 25l- l

Uu,, ap +aioZ cos c/ +

Отсюда b -a ,2) (Z) (ю.)

0 T(b-a):i iVv.

2 1 U, 30,-a,, Z,cos .,

Учитывая coT 2,+ Ц c/(z|;)- (Z) (10.2)

.-.

0 -2a ir jrm.3,s...

(2)U,j acy+a,ZoCos , +

-4- a 0+ Z -(Z )+ (z:)J (10.3)

т ,-...

.is...

Выражения (1) и (2) дают правилоUy ,j у, +

для определения пределов интегриро- S (2)- (z ) (10 4)

ВаНИЯ. Ь2.4-.. °

Рассуждая аналогично, получим ус-fn s.s..

ловия когда Up пропорционально А ц

(Г,, а Uu - Z.sin (/,: ou - и,„ ;

b 1-а, (3). 21,

, т;г

о а j , (4) g(/(zlj), c/ (Z) - нелинейная погрешДля и,. Z,cos с/,и и, -Z.cosc/ « интегратора

необходимо, чтобы. , .ч

(/(Z,), «(Zj,) - нелинейная погрешjj J. g. (5)I ность интегратора не2 gчетных степеней.

4 (Преобразовав напряжения (9) и (10)

процедурой двухтактного интегрироваи для 1/ и Uy ( ZpCos в числа импульсов, получим необходимо, чтобы

1 ,,, 3..a,,Z,sinc/,-b Г LV(z;;)Лz:)- b - -я- - а, (7)... TiiS.S,.

3 1 ,,

Т - 4 - 1 Uodt и,„„, ;

713378208

а„,-а,, Z sinc/, Z -XZ;;)-AZ:)- ,,,-U,,,. ) - a,, Z, cos f V „ .. ,, - I (z:) (13.4)

J - ;и„ ,4..

о

(11) a,+a,, Z.sinL Z (Z;)AZ:) .t ..

,f... где fg - частота заполнения

г опорное разрядное напря- j Updt UC.,H,;жение,

° .-r- r,v ,/ тч1Uc « - напряжение смещения нульa.-a.Z sinM-,1. Hz)-c/(Z)- р,

t -. Образуя разности , ,

Nj-N,, и вычисляя отноше- L/n u С - и ,

1Ni -N, NC-NI

™ y-

откуда3 ч т 11

N,,,-U..,,)..Z.sin., ° N.-N. . . , ; ...

. , (,2.,) .,

° k.2,4..(1A)

mr Vf...

N,- (а„-и,... )- ,,Z,sin,, ,, (г,со8у,)-21н.а,,.1г-Гд(г:)

r Иг ,(,2.2, ..

o k-,4.-.X J.(,5)

hiTlS...

30

„ fо / ,, fc „ .Как видим В выражениях (14) и (15),

N- ,(-u,,,, )+ 77 3. Z.,sinu + 3 DOUo « исключены аддитивная составляющая

,.погрешности, а также все нелинейные

/ Lo 4Z(j)+ (Z(,), (12,3) члены погрешности четных степеней. wi j f ..Полагая сумму нелинейных членов

.-,погрешности нечетных степеней начиN - (Зр )- а иZgsint/ + ная с третьего ничтожно малой, полуи ftи о

°°чим

1 Z KZ ,-.(Z:4(,2.«, Z..in«..(Z,sb..,,(,6)

п.гл--

и аналогично для синфазной составляю-Z,cos(/.. (Z,cos i/ ) (17)

X к о TO N,-N, щей

fо / . )+ 7 + 45 Следовательно, выполнив измере- 5 Uo U7 ° cos 1/ получения N,-N, и вычисли fo Y Гс/(7)+ (z) (13 1) тельные операции (16) и (17), можно Up X « J 1 получить значения синфазной и квадратурной составляющих исследуемых

fo / .. 0 7 4-Rn комплексных двухполюсников. При этом

i U7 U7 результаты не зависят от f., U,, а,„,

+ 1 Z /(Z)-c/(Z) , (13.2) .. . S- 7 У f7 . Uo Uj , , 2- cAZ,), 2- ° (Z ), a

m;}...,«... ,-.

при однородности Z и Zp в случае

N., тр(а(,, )+ тр a, Zj cos i/ + измерения LC-параметров - и от их

° °частоты.

+ o (z )+c/ (z) , (13.3) В пределах получения пар резуль- ° .татов (N,,Nj), (N,, N,), (Nj,N,),

(tJ.,N ) входной измеряемый параметр изменяет только знак, сохраняя неизменным свое абсолютное значение. Это гарантирует стабильность аддитивных погрешностей, поскольку режим работы входных цепей (в частности, обратные токи) не изменяется. Поэтому при образовании разностей N,-N , N -N , , N,-Nj обеспечивается их эф- фективная коррекция.

Поскольку для определения N.-N.

I о

используется процесс двухтактного интегрирования, то для того, чтобы избежать сложностей при определении знака, введено напряжение U , смещающее все напряжения в положительную область. Величина Uj, на результаты измерений не влияет, ее стабильность необходимо обеспечить на время измерений, что просто технически реализуется.

Цифровой измеритель Ю С-парамет- ров работает следующим образом.

Рассмотрим работу измерителя на произвольной частоте в случае измерения индуктивности двухполюсника, представляемого последовательной RL- схемой замещения. В качестве Z подключается образцовая индуктивность L. Вектор тока для формирования пределов интегрирования снимается с активного сопротивления 4. Для измерения реактивных составляющих на различных частотах фазу управляющего на пряжения поворачивают на 90 с помощью набора фазовращателей 10, обеспечивающих -стабильность своих характеристик в конкретном диапазоне частот.

С целью увеличения чувствительности на высоких частотах в блоке 19 управления введены регистр 38, реверсивный счетчик 39, элемент 2 ИЛИ 42 и триггер 44, обеспечивающие режим накопления проинтегрированных напряжений.

В процессе начальных установок в регистр 38 программно заносится числ тактов накопления. Это число заносит ся в счетчик 39, из которого по истечении одного такта вычитается единица. Переходом через О счетчика 39 заканчивается цикл накопления. В рассматриваемом примере в счетчик 39 записано число 3. Кроме того, при начальном диапоге вычислительным блоком в синтезатор 1 заносится код частоты и посредством коммутатора 11 вы

ду

бирается необходимый фазовращатель и набора 10 фазовращателей. При измерении реактивных составляющих переключатель 12 устанавливается в верхнее положение.

После начальных установок программа вычислительного блока 20 зацикливается на ожидание внешнего прерывания .

Из напряжения, пропорционального lnvsin (wt-t- (точка А), посредством фазоинвертора 13 и компараторов 14 и 15 формируется две последовательности импульсов (В и С), по которым выбираются необходимые пределы интегрирования.

При начальном сбросе (точка D) сбрасываются в нуль счетчик 43 и триггер 29, а триггеры 30, 35, 37 и 44 устанавливаются в 1 по S-входам

При этом коммутатор 26 соединяет выход компаратора 14 (точка В) с входом элемента 2И 31, а выход компаратора 15 (точка С) - с входами элементов 2И 32 и 33. Если первым приходит импульс по линии С, то он состояния блока 19 управления не изменяет, поскольку поступает на S-вход находящегося в единичном состоянии триггера 37, Приход первого импульса по линии В после сброса соответствует началу первого такта накопления.Этот импульс через элемент 2И 31 по С-вхозаписывает в триггеры 35 и 37 нули. Выходы этих триггеров (Е и F) управляют состоянием переключателя 9, для которого таблица истинности имеет вид:

III

Положение переключателя

В соответствии с этой таблицей на вход интегратора 17 (после начальных установок переключатель 6 находится в верхнем положении) прикладывается напряжение Z.. Процесс интегрирования продолжается до прихода первого импульса по линии С, который установит триггер 37 в единичное состояние и в соответствии с таблицей переключатель 9 переведется в среднее положение и прекратится процесс интегрирования. Вновь пришедший импульс по линии В через элемент 2И 31 восстановит нулевое состояние триггера 37, возобновит процесс интегрирования и т.д. Это будет продолжаться до прихода третьего отрицательного фронта на вход счетчика 39 (фиг. 2 F), по которому вычтется из него последняя 15 единица, и на его выходе сформируется импульс, переписывающий в реверсивный счетчик 39 вновь число 3, и сбрасывается триггер 44. Тогда через открытый элемент 2If 32, послед- 20 НИИ в цикле накопления, третий импульс по линии С, воздействуя на S- вход триггера 35, установит его в 1, чем запретит в соответствии с таблицей, интегрирование. Передний фронт 2S на выходе триггера 35 приведет в нулевое состояние триггер 30, запирающий элемент 2И 31. Это приводит к тому, что описанное состояние блока 19 управления является устойчивым, зо поскольку импульсы ни по линии в, ни по линии с изменить его не могут. В то же время этот передний фронт формирует на выходе формирователя 50 узкий импульс, отпирающий через триггер 37 селектор 18. При этом переключатель 9 подключает к входу интегратора 17 разрядное напряжение от источника 8 образцового напряжения. N, По истечении первого такта импуль28 возобновляется начал триггеров 30, 35, 37 и производится прерывание вычислительного блока 2 он считывает выходной к 25 и состояние дешифрат индентификации данных.К ся, после чего возобнов программы ожидания прер же импульс по линии В п описанную последователь разницей,что на вход ин поступает напряжение на соответствии с таблицей (12.4) в памяти будет з код

)

35

N, 1 {(а,,-и,„, - Г fc/(z:)-.4z:)(

о ,4...

,5...

При этом в дешифрато зируется состояние 2, мирует на выходе формир узкий импульс, изменяющ состояние триггера 29. очередь, приводит к пер коммутатора 26, и импул В поступают на выходы эл 32 и 33, а импульсы п на вход элемента 2И 31. этого в третьем и четвер в основном аналогичных рому, в память вычислите 20 будут занесены коды

tf

и

i2-(a,,-U,

) } истечении nepeoi o такта импуль- 40 f запирающим триггер 30, записы- ТГ )-(/(Z )j|

сом,

вается единица в счетчик 43. При этом в дешифраторе 45 дешифрируется состояние 1 и через элемент 2 ИЛИ 49 переключатель 6 устанавливается в нижнее положение.

В момент срабатывания нуль-органа 22 в счетчике 25 накопится число импульсов N. « 1, где 1 - число тактов накопления (в данном примере t 3) (см. также ур-е 12.1).

,4... mi3,5...

45

,N,1

и„

aou) -Ь

I /(z;)-c/(z:)i 1.

,4... ,S...

50

В вычислительном блок нии четырех циклов выпол рация (см. (16)):

f е

о / ,, п 01) I и о

fe

Г .4z)w(z:)jj

0 k:H...J

При срабатывании нуль-органа 22 формирователем 27 через элемент 2

N,

28 возобновляется начальное состояние триггеров 30, 35, 37 и 44, а также производится прерывание программы вычислительного блока 20, по которому он считывает выходной код счетчика 25 и состояние дешифратора 45 для индентификации данных.Код запоминается, после чего возобновляется работа программы ожидания прерывания. Первый же импульс по линии В повторит всю описанную последовательность с той разницей,что на вход интегратора 17 поступает напряжение на Z . Тогда в соответствии с таблицей и уравнением (12.4) в памяти будет зафиксирован код

N,

)- Uo

10 -с

N, 1 {(а,,-и,„, - Г fc/(z:)-.4z:)(

о ,4...

,5...

При этом в дешифраторе 45 активизируется состояние 2, которое формирует на выходе формирователя 46 узкий импульс, изменяющий по С-входу состояние триггера 29. Это, в свою очередь, приводит к перекоммутации коммутатора 26, и импульсы по линии В поступают на выходы элементов 2И 32 и 33, а импульсы по линии С - на вход элемента 2И 31. Вследствие этого в третьем и четвертом циклах, в основном аналогичных первому и второму, в память вычислительного блока 20 будут занесены коды

tf

и

i2-(a,,-U,

) )-(/(Z )j|

а , и L ,+

,4... mi3,5...

5

,N,1

и„

aou) -Ь

I /(z;)-c/(z:)i, 1.

10 0

,4... ,S...

50

В вычислительном блоке по истечении четырех циклов выполняется операция (см. (16)):

Ь,

, N. i-N, E NVr-N,

55

22 2

ИЛИ

N.-N-i N,-N,

Значение Lx выводится в блок 21 индикации. В памяти вычислительного блока 20 коды N,1, , , размещаются в виде четырехкомпонент- ного вектора, элементы которого возобновляются в каждом цикле из четырех описанных. Это позволяет по истечении первых четырех циклов после каждого следующего формировать результат измерений. В самом деле (обозначив вторым индексом порядковый номер результата) уже после пятого цикла в вычислительном блоке 20 вычисляется

L.

N., - N

21

N31 f - N,, Е

после шестого цикла

L.

Ni, t - N,, (

MZ N3, f N

42

седьмого цикла N,. t Ч

2Z

N., I - N,jf

восьмого цикла

Ng С L,

Nzi е

N

за

- N,,t

И т.д., т.е. несмотря на наличие принципиально необходимых четырех циклов быстродействие лишь немногим меньше, чем с одним циклом измерения .

При измерениях активных сопротивлений и проводимостей, а также синфазных составляющих комплексных сопротивлений работа измерителя отличается только тем, что переключатель 1 находится в нижнем положении, а коды считываемые в память вычислительного блока 20, описываются уравнением (13)

Формула изобретения

Цифровой измеритель RLC-парамет- ров, содержащий синтезатор частот, выходами подключенный к последовательно соединенным клеммам для подключения исследуемого двухполюсника, образцового двухполюсника и активного сопротивления, причем общий вывод исследуемого и образцового двухполюсников подключен к корпусу, общий вывод синтезатора частот и исследуемого двухполюсника соединен с первым неподвижным контактом первого переключателя, второй неподвижный контакт которого подключен к общему выводу соединения образцового двухполюсника и активного сопротивления, а источник образцового напряжения соединен с первым неподвиж0

5

Ь

ным контактом BTopoi o переключателя, подвижный контакт соединен с входом интегратора, выходом подключенного к входу селектора, к второму входу которого подключен генератор импульсов, первый выход блока управления подключен к входу управления первого переключателя, второй и третий выходы - к управляющим входам второго переключателя, а четвертый и пятый - к управляющим входам селектора, причем выход нуль-органа селектора соединен с третьим входом блока управления и управляющим входом вычислительного блока, к входной информационной шине которого подключены выходная шина селектора и выходная шина блока управления, а к выходной шине вычислительного блока подключен вход блока индикации, отличающийся тем, что, с целью повышения точности измерений RLC-na- раметров в диапазоне частот при обеспечении высокой чувствительности и быстродействия, введены дифференциальный усилитель, источник напряжения смещения, набор фазовращателей, аналоговый коммутатор, третий переключатель на два положения, фазо- инвертор и два компаратора, причем дифференциальный усилитель двумя входами подключен параллельно активному сопротивлению, а выходом соединен с входами всех фазовращателей и первым неподвижным контактом третьего переключателя, причем выходы всех фазо- вращателе й подключены к соответствую- mjiM входам аналогового коммутатора, выход которого соединен с вторым неподвижным контактом третьего переключателя, подвижный контакт которого соединен с входами фазоинвертора и первого компаратора, а выход фазо- 5 инвертора через второй компаратор подключен к второму входу блока управления, с первым входом которого соединен выход первого компаратора, причем вторые входы обоих компараторов соединены с корпусом, а выходная шина вычислительного блока подключена к входам управления синтезатора частот, третьего переключателя, аналогового коммутатора и к четвертому входу блока управления, причем источник напряжения смещения включен между подвижным контактом первого переключателя и третьим неподвижным контактом второго переключателя.

0

5

0

0

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой измеритель RLC-параметров | 1986 |

|

SU1357874A1 |

| Цифровой измеритель составляющих комплексных сопротивлений | 1987 |

|

SU1456907A1 |

| Устройство для измерения сопротивления | 1986 |

|

SU1429050A1 |

| Устройство для измерения геометрических параметров заготовок волоконных световодов | 1985 |

|

SU1295227A1 |

| Устройство для измерения температуры | 1984 |

|

SU1232961A1 |

| АНАЛИЗАТОР СПЕКТРА | 1992 |

|

RU2054682C1 |

| Цифровой измеритель температуры | 1985 |

|

SU1278622A1 |

| Цифровой вольтметр | 1985 |

|

SU1273825A1 |

| Цифровой измеритель RLc-параметров | 1980 |

|

SU868629A1 |

| Устройство для измерения частоты гармонического сигнала | 1987 |

|

SU1525607A1 |

Изобретение относится к электроизмерительной технике и может быть использовано при измерении RLC-napa- метров в широком диапазоне частот. Цель изобретения - повышение точности измерений при обеспечении высокой чувствительности и быстродействия достигается путем адаптивно-мультипликативных коррекций и режима накопления, а также формирования результатов после каждого цикла измерений. Для этого в устройство дополнительно введены дифференциальный усилитель 5, источник 7 напряжения смещения, набор фазовращателей 10, аналоговый коммутатор 11, переключатель 12, фаяоинвертор 13 и компараторы 14 и 15. Кроме того, устройство содержит синтезатор 1 частот, исследуемый двухполюсник 2, образцовый двухполюсник 3, активное сопротивление 4, переключатели 6 и 9, источник 8 образцового напряжения, генератор 16 импульсов, интегратор 17, селектор 18, блок 19 управления, вычислительный блок 20 и блок 21 индикации. 1 табл. 2 ил. (Л (Л со 00 00 to фиг

| Цифровой измеритель сопротивления,емкости и индуктивности | 1972 |

|

SU467302A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Цифровой измеритель RLc-параметров | 1980 |

|

SU868629A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1987-09-15—Публикация

1986-04-08—Подача