(21)4162752/24-21

(22)18.12,86

(А6) 30.06.88. Бкш. № 24 (75) С.И.Капустин

(53)621.374.5 (088.8)

(56)Авторское свидетельство СССР № 917347, кл. Н 03 К 17/28, 1981.

Авторское свидетельство СССР № 1211871, кл. Н 03 К 17/28, 1984.

(54)РЕЛЕ ВРЕМЕНИ

(57)Изобретение может быть использовано в системах автоматического управления. Реле времени содержит интегратор 1, включающий операционный усилитель 2, резисторы , время- задающий конденсатор 4 и ключ 5, источники 6,-6п опорного напряжения, резисторы 7,-7п, 8,-8, компараторы на операционньг 4 усилителях ,, устройства 10,-10„ блокировки. Устройство просто по конструкции за счет введения новых электрических связей между функциональными элементами. 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Реле времени | 1984 |

|

SU1211871A1 |

| Ждущий генератор временного интервала | 1983 |

|

SU1167704A1 |

| Устройство для выявления режима включения трансформатора | 1983 |

|

SU1176408A1 |

| Функциональный аналого-цифровой преобразователь | 1986 |

|

SU1310855A1 |

| УСТРОЙСТВО И СПОСОБ ИЗМЕРЕНИЯ ПЕРЕМЕННОЙ ВЕЛИЧИНЫ | 2010 |

|

RU2437064C1 |

| Преобразователь емкости во временной интервал | 1988 |

|

SU1636793A1 |

| Устройство для управления четырехфазным двигателем переменного тока | 1983 |

|

SU1138918A2 |

| Реле переменного тока | 1986 |

|

SU1332443A1 |

| Устройство выдержки времени | 1976 |

|

SU587520A1 |

| Реле времени | 1979 |

|

SU836700A1 |

0 Вых. 1

с 9

сл

ивы к. 2

Од

ИВых.п

-0 Off рос

Фи&. 1

Изобретение относится к устройствам автоматики и может быть использовано в системах автоматического управления/

Цель изобретения - упрощение устройства.

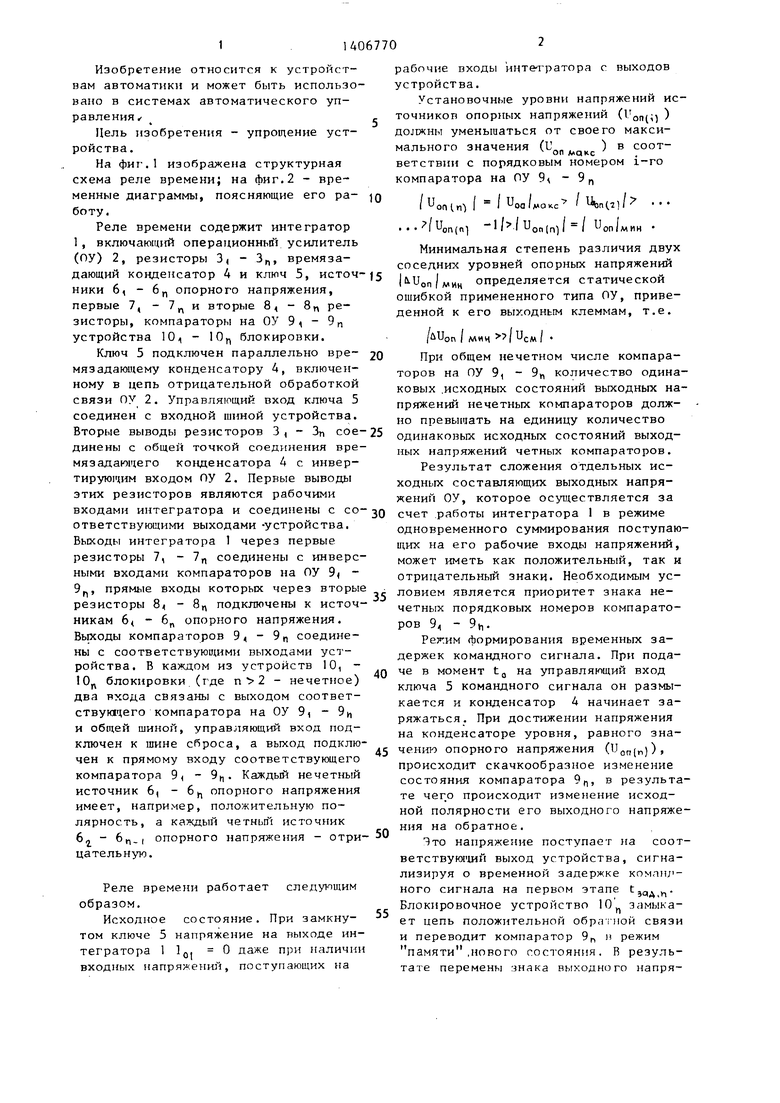

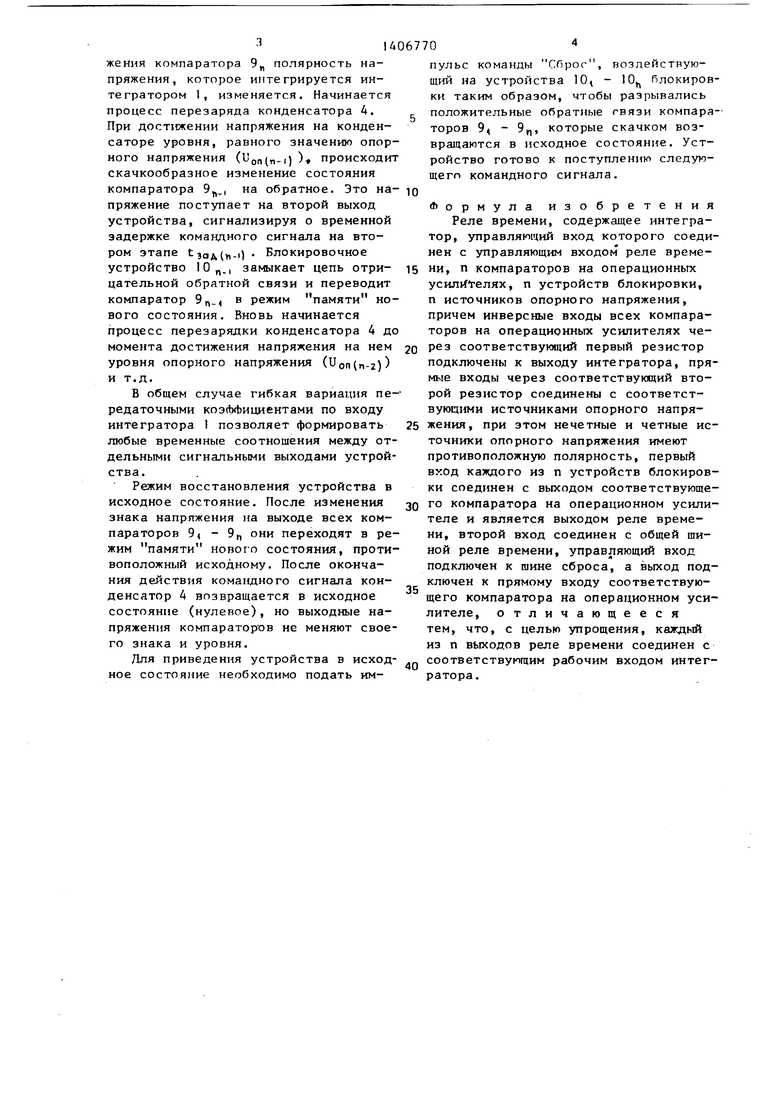

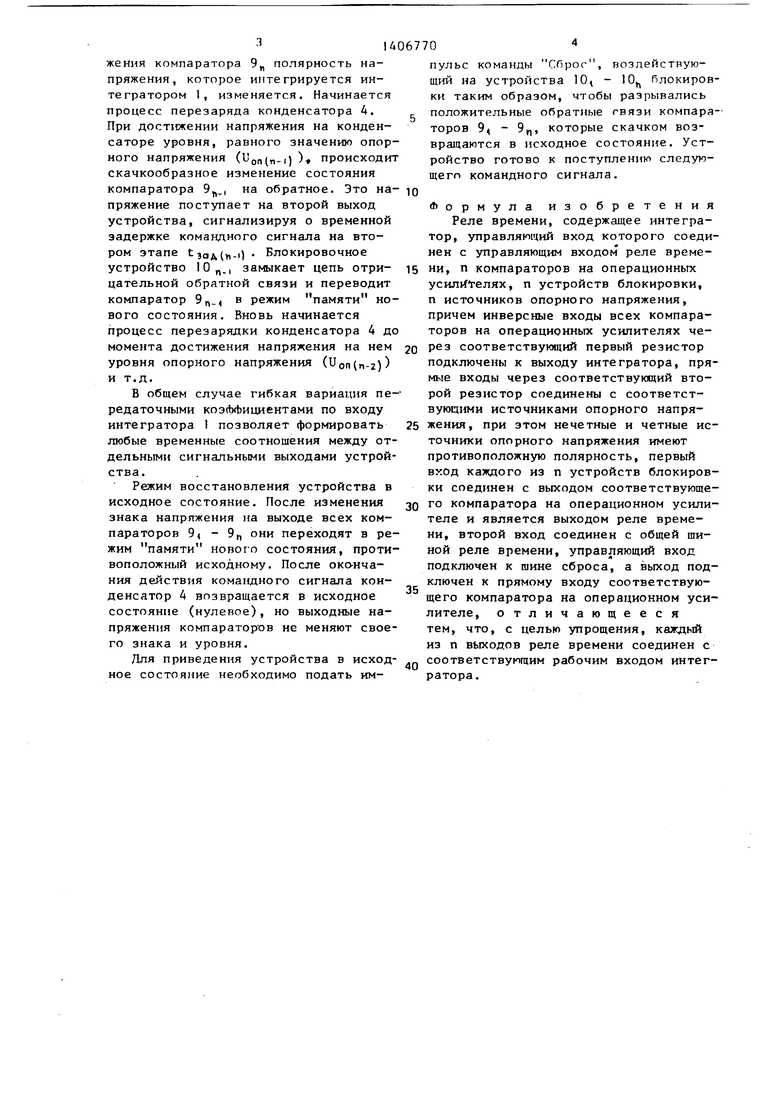

На фиг.1 изображена структурная схема реле времени; на фиг.2 - временные диаграммы, поясняющие его ра- боту.

Реле времени содержит интегратор 1, включающий операпионньп усилитель (ОУ) 2, резисторы 34 - 3, времяза- дающий конденсатор 4 и ключ 5, источНИКИ 6, 6f, опорного напряжения, первые 7, - 7 и вторые 8, - 8, резисторы, компараторы на ОУ 9 - 9„ устройства 10, - 10 блокировки.

Ключ 5 подключен параллельно вре- мязадающему конденсатору 4, включенному в цепь отрицательной обработкой связи ОУ 2. Управляющий вход ключа 5 соединен с входной шиной устройства. Вторые выводы резисторов 3 , - Зп соединены с общей точкой соединения вре- мязсщающего конденсатора 4 с инвертирующим входом ОУ 2. Первые выводы этих резисторов являются рабочими входами интегратора и соединены с со- ответствующими выходами -устройства. Выходы интегратора 1 через первые резисторы 7, - 7 соединены с инверсными входами компараторов на ОУ 9( - , прямые входы которых через вторые резисторы 8 - 8 подключены к источникам 6 - 6„ опорного напряжения. Вьрсоды компараторов 9 - 9п соединены с соответствующими выходами устройства. В каждом из устройств 10,

два входа связаны с выходом соответ- ствуицего компаратора на ОУ 9, - 9ц и общей шиной, управляющий вход подключен к шине сброса, а выход подключен к прямому входу соответствующего компаратора 9, - 9ц. Каждый нечетный источник 6, 6 опорного напряжения имеет, например, положительную полярность, а каждый четньш источник 6 - 6.1 опорного напряжения - отри- цательную.

Реле времени работает следующим образом.

Исходное состояние. При замкну- том ключе 5 напряжение на выходе интегратора 1 IQI 0 даже при наличии входных напряжений, поступающих на

Q .

0

5

0

рабочие входы интегратора с выходов устройства.

Установочные уровни напряжений источников опорных напряжений (Uon(;5 должны уменьшаться от своего максимального значения (U ) в соответствии с порядковым номером i-ro компаратора на ОУ 9 п

/Uooin f lUoaUKc /UbnUl/ ..(ni ( Uon/мпи

Минимальная степень различия двух соседних уровней опорных напряжений JMJonlvHH определяется статической ощибкой примененного типа ОУ, приведенной к его выходным клеммам, т.е.

/uUon/мич |UcMl

При общем нечетном числе компараторов на ОУ 9, - 9у, количество одинаковых .исходных состояний выходных напряжений нечетных компараторов должно превышать на единицу количество одинаковых исходных состояний выходных напряжений четных компараторов.

Результат сложения отдельных исходных составляющих выходных напряжений ОУ, которое осуществляется за счет работы интегратора 1 в режиме одновременного суммирования поступающих на его рабочие входы напряжений, может иметь как положительный, так и отрицательный знаки. Необходимым условием является приоритет знака нечетных порядковых номеров компараторов 9, - 9ц.

Режим формирования временньрс задержек командного сигнала. При подаче в момент tj на управляющий вход ключа 5 командного сигнала он размыкается и конденсатор 4 начинает заряжаться. При достижении напряжения на конденсаторе уровня, равного значению опорного напряжения (Ugf,(n)) происходит скачкообразное изменение состояния компаратора 9, в результате происходит изменение исходной полярности его выходного напряжения на обратное.

Это напряжение поступает на соот- ветствую1адй выход устройства, сигнализируя о временной задержке комппл- ного сигнала на первом этапе СЗРДЛ Блокировочное устройство 10 замыкает цепь положительной обратной связи и переводит компаратор 9,, и режим памяти .нового состояния. В результате перемены знака выходного напряження компаратора 9„ полярность напряжения, которое интегрируется интегратором I, изменяется. Начинается процесс перезаряда конденсатора 4. При достижении напряжения на конденсаторе уровня, равного значению опорного напряжения (Uon.,) ) происходит скачкообразное изменение состояния компаратора 9., на обратное. Это на- пряжение поступает на второй выход устройства, сигнализируя о временной задержке командного сигнала на втором этапе t3aA(i-i) Блокировочное устройство lOn.i замыкает цепь отрицательной обратной связи и переводит

компаратор Э., в режим памяти нового состояния. Вновь начинается процесс перезарядки конденсатора 4 до момента достижения напряжения на нем уровня опорного напряжения (Uon(n-2)) и т.д.

В общем случае гибкая вариация передаточными коэффициентами по входу интегратора 1 позволяет формировать любые временные соотношения между отдельными сигнальными выходами устройства.

Режим восстановления устройства в исходное состояние. После изменения знака напряжения на выходе всех компараторов 9 - 9 они переходят в режим памяти нового состояния, противоположный исходному. После око-нча- ния действия командного сигнала конденсатор 4 возвращается в исходное состояние (нулевое), но выходные напряжения компараторов не меняют своего знака и уровня.

71ля приведения устройства в исходное состояние необходимо подать им

пульс команды Сброг, возлействую- щий на устройства 10 - 10 блокировки таким образом, чтобы разрывались положительные обратные гвязи компара-- торов 9, - 9, которые скачком возвращаются в исходное состояние. Устройство готово к поступлению следующего командного сигнала.

ормула изобретения Реле времени, содержащее интегратор, управляюрдий вход которого соединен с управляющим входом реле времени, п компараторов на операционных усил1 гелях, п устройств блокировки, п источников опорного напряжения, причем инверсные входы всех компараторов на операционных усилителях через соответствующий первый резистор подключены к выходу интегратора, прямые входы через соответствующий второй резистор соединены с соответствующими источниками опорного напря- жения, при зтом нечетные и четные источники опорного напряжения имеют противоположную полярность, первый вход каждого из п устройств блокировки соединен с вькодом соответствующего компаратора на операционном усилителе и является выходом реле времени, второй вход соединен с общей щи- ной реле времени, управляющий вход подключен к шине сброса, а выход подключен к прямому входу соответствующего компаратора на операционном усилителе, отличающееся тем, что, с целью упрощения, каждый из п выходов реле времени соединен с соответствующим рабочим входом интегратора.

Л

Фаг.2

Авторы

Даты

1988-06-30—Публикация

1986-12-18—Подача