изобретение относится к автоматике и может быть использовано в системах автоматического управления а также для построения программных устройств.

Цель изобретения - увеличение времени задержки.

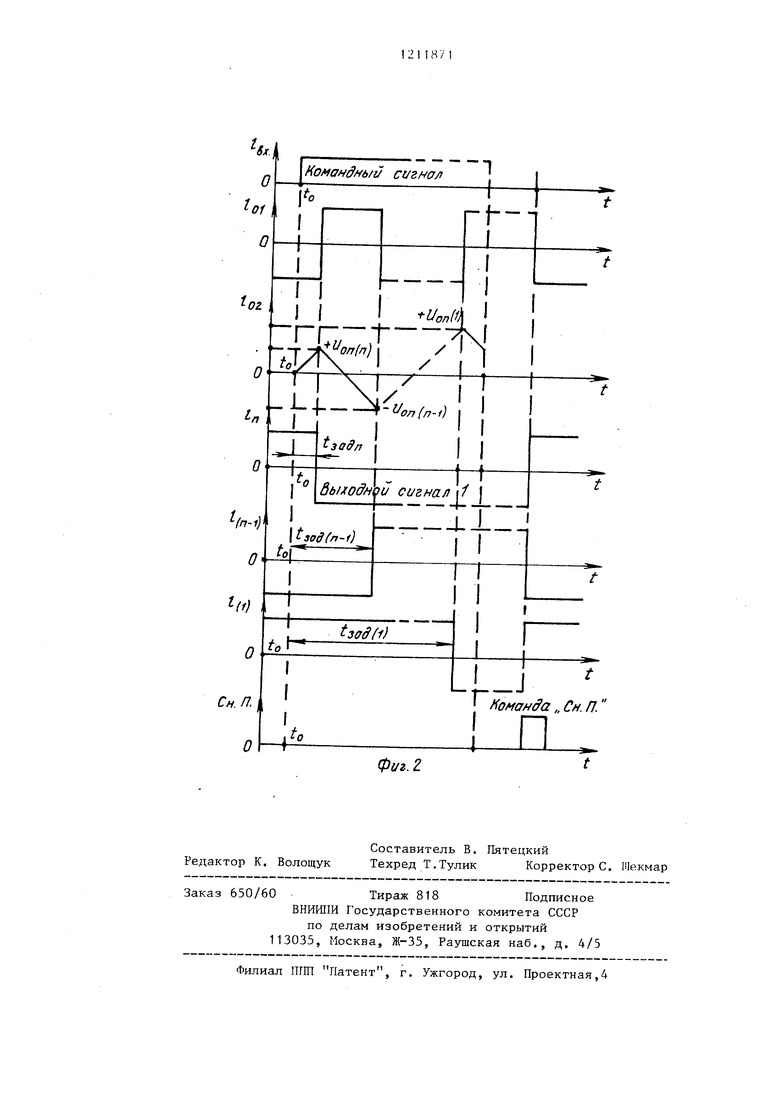

На фиг.1 представлена структурная схема устройстваj на фиг,2 - временная диаграмма работы устройства.

Устройство содержит интегратор 1 на операционном усилителе 2, резистор 3, конденсатор 4, ключ 5, источники опорного напряжения 6,-6, первый резистор 7,-7,, второй резистор 8,-8 компараторы на операционных усилителях , устройства блокировки 10,-10г,, каждое из которых содержит диод 11, третий резистор 12, ключ 13 и сумматор 14

Устройство содержит интегратор 1 в виде операционного усилителя Z с времязадаюощм конденсатором 4 в цепи отрицательной обратной связи, параллельно которому включен ключ 5, управляющий вход которого соединен с входной тиной устройства Выход интегратора 1 через резистор 7, -7f, связан с инверсными входами компараторов на операционных усилителях 9,-9,, прямые входы которых через резисторы 8,-8„ подключены к источникам 6, -б, опорного напряжения выходы связаны с выходами устройства.

В устройстве источники опорного напряхсения ) через резисторы 8,-8f, с прямыми входами компараторов на операционных усилителях 9,-9г1, инверсные входы которых через резисторы 7, -7fi соединены с ВЕ)1- ходом интегратора 1, В каждом из устройств блокировки (где И 2, нечетное) 10,-10,, два входа связаны с выходом соответствую1чего компаратора на операционном усилителе 9,-9f, и общей шиной устройства, управляющий вход подключен к шине сброса, а выход подключен к прямому входу соответствующего компаратора 9,-9f,. При этом, выходы каждого компаратора 9 -9 г, подключены к входам сумматора 14, выход, которого подключен к рабочему входу интегратора 1 , выходы каждого из п I :OM- параторов ,, подключены к донсхтт- нительным выходам Вых.1-Вых. h устройства.

5 ™я

2118712

Каждый нечетньй источник опорного напряжения, 6,-6 f, имеет например, положительную полярность,а каждый четный источник о порного напряже- отрицательную.

Каждое из устройств , блокировки . содерш-ит последовательные диод 11 и резистор 12, соединенный, в свою очередь, с первым входом 10 устройства блокировки. Диод 11 соединен с выходом устройства блокировки, общая точка соединения диода и резистора через замыкающий ключ 13 подключена к второму входу (5 устройства блокировки, при этом управляющий вход ключа 13 связан с. управляющим входом устройства блокировки.

Работа реле времени происходит 2Q следующим образом.

1. Исходное состояние.

При замкнутом ключе 5 напряжение на выходе интегратора 1 - Ро2 О даже при наличии входного на- 25 пряжения РО, поступающего на его выходе сумматора 14.

Полярность исходного напряжения на выходах дифференциальных операционных усилителей 9 (-9 г (где h 2, нечетное число) определяется полярностью источников опорных напряжений 6,-6 и,, а уровень выходного напряжения - ( Е) определяется применеиньм типом операционного усилителя и уровнем биполярного напряжения источников постоянного тока, питающего устройство.

Установочные уровни напряжений ИСТОЧ1П1КОВ опорных напряжений (UQ,; ) должны уменьшаться от своего максимального значения (lJ(,n)nax соответствии с порядковь м номером 1-го компаратора на операционном усилителе 9,-9п

35

45

|iJonJ /fJon/ / on2 - /fJonn-, /Uonl iin .

Минимальная степень различия двух соседних уровней опорных на- пряжений /uUonj/min определяется статической ошибкой примененного ТИПУ операционного усилителя, при- веден} ой к его выходным клеммам, т.е. /йи„„/п1,-п /U / .

При общем нечетном числе компараторов на операционных усилителях 9,-9 количество одинаковых исходных состояний выходных напряжений

55

нечетных компараторов должно превышать Fia единицу количество одинаковых исходных состояний выходных напряжений четных компараторов.

Результат сложения отдельных исходных составляющих выходных напряжений операционных усилителей может быть как положительного, так и отрицательного знака. Р1еобходимым условием является приоритет знака нечетных порядковых номеров компараторов 9, -9 .

В исходном состоянии уровень и полярность выходного напряжения компараторов 9,-9п -(Р;/ /(JQ,,-/ таковы, что диод 11 находится в запер- том состоянии и цепь положительной обратной связи разомкнута.

Резистор 12 является ограничительным элементом, препятствующим увеличению выходного тока компараторов 9 вьше предельного значения в момент поступления команды Сброс осуществляющей обрыв цепи положительной обратной связи замыканием общей точки coeдинe tия резистора 12 и диода 11 на общую тину устройства.

Выходное напряжение - (Ур,) суы- матора 14 определяется выражением:

lfo,l - e;/V( гJ г eз ч----.en-,(k „.,.eJ к,

где С,- ЕП - выходные напряжения компараторов 9, К, передаточные коэффициенты по отдельным м входам сумматора 14 В частном случае, при

4 .. n Me,/ /ej .,./ej.)ei /ео,1 /в1к (2)

,Тля схемы на фиг.1 напряжение Р-01 будет отрицательного знака.

В качестве времязадающего устройства 1 на фиг.1 представлена схема интегратора, содержащего RC -цепь и операционный усилитель, конденсатор А расположен в обратной связи операционного усилителя 2, а входной резистор 3 является входным сопротивлением интегратора.

2. Режим формирования временных задержек командного сигнала tзo|д.

При подаче в момент t,, на управляющий вход ключа 5 командного сиг- наиа он размыкается и конденсатор

1211871Л

4 начинает заряжаться в соответствии с выражением:

02 ог у 7

СЗ)

т

где fp,; - напряжение на выходе интегратора 1 ;

постоянная времени интегратора; текущее значение времени.

При достижении текущим уровнем напряжения ) равного значению опорного напряжения (И , нроис- ходит скачкообразное изменение сос- тояния компаратора 9ц, в результате чего происходит изменение исходной полярности его выходного напряжения на обратное.

Это напряжение поступает на соот- ветствующий выход устройства, сигна- 1П1зируя о временной задержке командного сигнала на I этапе:

25

on 11

Х

(4)

Диод 11 блокировочного устройства Юр отпирается и замыкает цепь положительной обратной связи, переводя компаратор 9, в режим памяти но- 30 вого состояния.

Для устойчивости работы компараторов в режиме памяти необходимо выполнение двух условий:

:e;l, UoJniax--ieo,,

(5)

ипа X

R:,... R7, ,R8,... (6)

Pbl ITIO

в результате перемены знака выхо 40 ного н апряжения компаратора 9, полярность управляющего напряжения на выходе сумматора 14 изменяется.

Начинается процесс перезаряда, конденсатора 4 в соответствии с выр 45 жением

oa-/Uonn/-eo,7 (7)

При достижении текущим уровнем напряжения (oj) значения опорного 2Q напряжения (U р,, происходит скачкообразное изменение состояния компаратора 9,, на обратное.

Это напряжение поступает на второй выход устройства, сигнализируя о временной задержке командного сигнала на II этапе:

2/и,п /и„„„.,(

55

Jae n-t

,

Т. (8)

Диод 11 устройства Ю,., блокировки отпирается и замыкает цепь положительной обратной связи, переводя компаратор 9 ,, в режк1М памяти нового состояния.

Вновь начнется процесс перезарядки конденсатора 4 до момента достижения текущим уровнем напряжения (йо,) значения опорного напряжения ( Ug 2 ) и ТоД.

Временная задержка командного сигнала на 1-м выходе 1-го компаратора определяется выражением:

2z:/и,,|.

i

(9)

зад ,

В общем случае, гибкая вариация передаточными коэффициентами по входам сумматора 1А позволит формировать любые временные соотношения между отдельными сигнальными выходами устройства.

3. Режим восстановления устройства в исходное состояние.

После изменения знака напряжения на выходе всех компараторов 9,-9ц они переходят в режим памяти нового состояния, противоположный исходному.

После окончания действия командного сигнала конденсатор 4 возвращается в исходное нулевое значение, н выходные }1апряжения компараторов не МЕ1НЯЮТ своего знака

уровня. I

Для приведения устройства в исходное рабочее состояние необходимо подать импульс команды Сброс, воздействующей на ключи 13 каждого устройства блокировки, при этом общие точки соединения диода 11 и резистора 12 в каждом устройстве блокировки соединяются шиной, раз- рьгоая тем самым цепи положительных обратных связей компараторов 9,-9п которые скачком возвращаются в исходное состояние.

Формула II я о О ) е т е fi и я

1.Реле врсме1ги, ссхдержащее интегратор, управляющий вход которого соеди1 ен с управляющим входом устройства, источник опорного напряжения и компаратор на операционном усилителе, отличающееся

тем, что, с целью увеличения времени задержки, в него введены (п-1) источников опорного напряжения (где п 2, нечетное), сумматор с п-входами, П устройств блокировки, Г| -1 КОМ

параторов на операционных усилителях, причем инверсные входы всех компараторов на операционных усилителях через соответствующий первый резистор.-подключены к выходу интегратора, прямые входы через соответствующий второй резистор соединены с соответствуюш ми источниками опорного напряжения, при этом нечетные и четные источники опорного налряжения имеют противоположную полярность, первый вход каждого из п устройств блокировки соединен с одним из П -входов сумматора, с выходом соответствующего компаратора на

операционном усилителе и является выходом устройства, второй вход соединен с общей шиной устройства, управляющий вход подключен к шине сброса, а выход подключен к прямому

входу соответствующего компаратора на операционном усилителе, выход сумматора соединен с рабочим входом интегратора.

2.Реле ПОП.1, о тли ч а ющ е е с я тем, что устройство блокировки содержит последовательную цепочку из третьего резистора и диода, диод соединен с выходом устройства блокировки, третий резистор

соединен с первым входом, точка сое- .динения диода и третьего резистора через замыкающий ключ соединена с вторым входом, управляюш;ий вход замыкающего ключа соединен с управляю- ш;им входом устройства блокировки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Реле времени | 1986 |

|

SU1406770A1 |

| ДЕФИБРИЛЛЯТОР | 1999 |

|

RU2153901C1 |

| Устройство для импульсного намагничивания ферромагнитных изделий | 1985 |

|

SU1317497A1 |

| Преобразователь ток-частота с импульсной обратной связью | 1987 |

|

SU1552377A1 |

| ДЕФИБРИЛЛЯТОР | 2001 |

|

RU2196616C1 |

| Устройство для направленной защиты от однофазного замыкания на землю в сети с изолированной нейтралью | 1981 |

|

SU1034115A1 |

| Устройство для управления четырехфазным двигателем переменного тока | 1983 |

|

SU1138918A2 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В ЧАСТОТУ | 1989 |

|

RU2024195C1 |

| Генератор напряжения ступенчатой формы | 1981 |

|

SU1029191A1 |

| МНОГОКАНАЛЬНЫЙ ИСТОЧНИК ПИТАНИЯ ДЛЯ ИЗМЕРИТЕЛЯ УГЛОВОЙ СКОРОСТИ ВОЛОКОННО-ОПТИЧЕСКОГО | 1996 |

|

RU2115211C1 |

Изобретение относится к автоматике и может быть использовано в системах автоматического управления. Цель изобретения - увеличение времени задержки. Устройство содержит интегратор 1, включающий операционный усилитель 2, резистор 3, конденсатор 4 и ключ 5. Источники

| Устройство задержки | 1974 |

|

SU600730A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство временной задержки | 1979 |

|

SU917347A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-02-15—Публикация

1984-04-04—Подача