гг

Ы

со

Изобретение относится к вычислительной технике и микроэлектронике и предназначено для реализации всех логических функций четырех переменных.

Цель изобретения - повышение быст- .родействия универсального логического модуля.

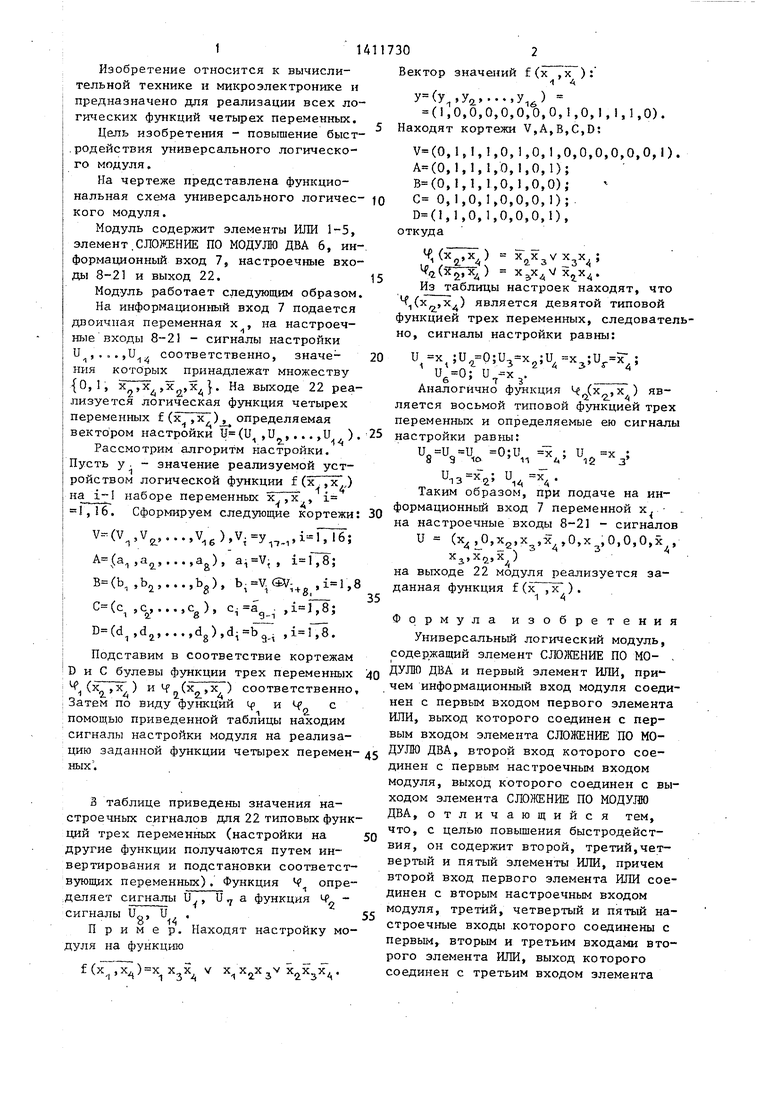

На чертеже представлена функциональная схема универсального логичес- кого модуля.

Модуль содержит элементы ИЛИ 1-5, элемент.СЛОЖЕНИЕ ПО МОДУЛЮ ДВА 6, информационный вход 7, настроечные входы 8-21 и выход 22.

Модуль работает следующим образом

На информационный вход 7 подается двоичная переменная х , на настроеч 1

ные входы 8-21 - сигналы настройки и,...,и соответственно, значе- кия которых принадлежат множеству {0,1, ,х,. На выходе 22 реализуется логическая функция четырех переменных f(х ,х) определяемая вектором настройки U(U л

Рассмотрим алгоритм настройки. Пусть у . - значение реализуемой устройством логической функции f (х ,х.,) на i-J наборе переменных х,, х , i 1,16. Сформируем следзлющие кортежи:

V-(V,V,...,V,),V.y,, А(,а,а,...,), , , ,8; B(b ,b2,...,bg), b-vav- g,,8 C (c , c,, ..., Cg ) , с ag. , i JTS;

Универсальный логический модуль, содержащий элемент СЛОЖЕНИЕ ПО МО- ,

2. 2.2. Затем по виду функций if и Ц с

помощью приведенной таблицы находим

I ,,d2,...,dg),,, ,,8.

I Подставим в соответствие кортежам D и С булевы функции трех переменных 40 первый элемент ИЛИ, при- Ч (зГТЗГ ) и Ч (х ,х ) соответственно, . чем информационный вход модуля соеди- 1 2. 4jjgjj первым входом первого элемента

ИЛИ, выход которого соединен с персигналы настройки модуля на реализа- вым входом элемента СЛОЖЕНИЕ ПО МО- цию заданной функции четырех перемен-45 ДВА, второй вход которого сое- ных .динен с первым настроечным входом

модуля,

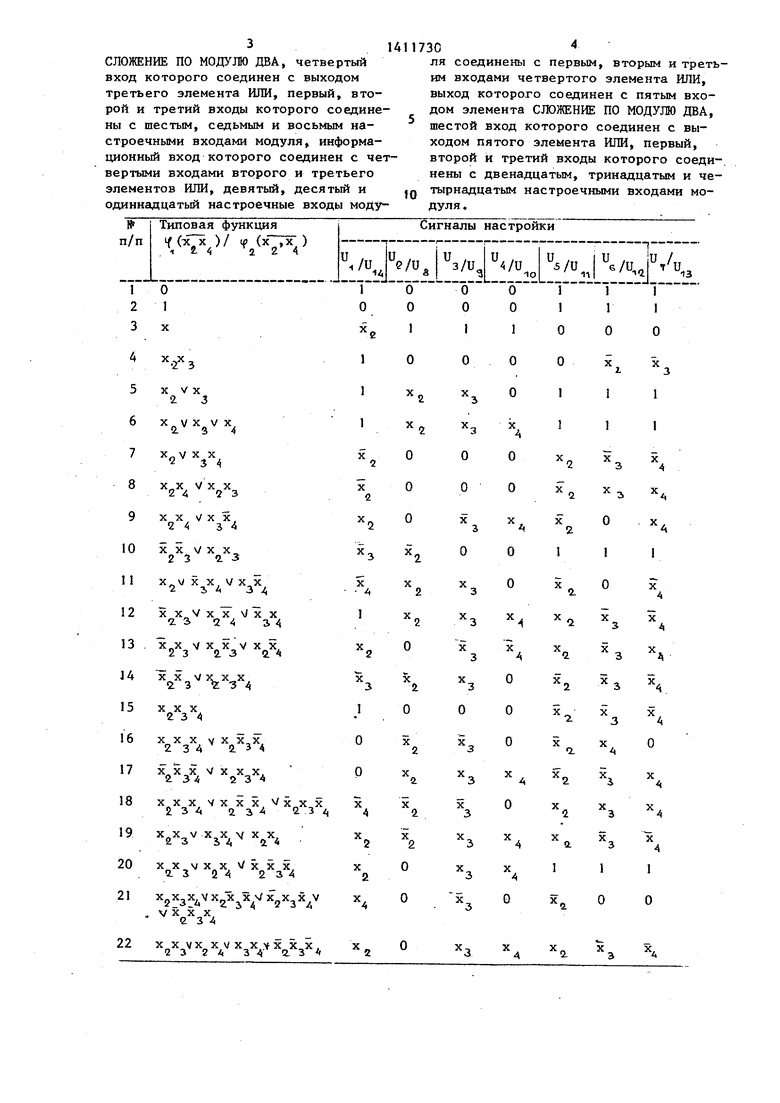

3 таблице приведены значения настроечных сигналов для 22 типовых функций трех переменных (настройки на 50 другие функции получаются путем инвертирования и подстановки соответствующих переменных). Функция Ч определяет сигналы и., и ,j а функция Ч сигналы UQ, и Пример.

55

Находят настройку мовыход которого соединен с выходом элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА, отличающийся тем, что, с целью повышения быстродействия, он содержит второй, третий,четвертый и пятый элементы ШШ, причем второй вход первого элемента ИЛИ соединен с вторым настроечным входом модуля, третий, четвертый и пятый настроечные входы которого соединены с первым, вторым и третьим входами второго элемента ИЛИ, выход которого соединен с третьим входом элемента

дуля на функцию

f () х V х;х,х jv ,

Вектор значений f(х ,х ):

1 л

У- / Y у (,0,0,0,0,0,0,1,0,1,1,1,0).

Находят кортежи V,A,B,C,D;

V(О,1,1,1,0,1,0,1,0,О,О,О,О,0,1). А(0,1,1,1,0,1,0,1); В(0,1,1,1,0,1,0,0); С 0,1,0,1,0,0,0,1);. D(l,l,0,l,0,0,0,l), откуда

JJV)

4,2. (2, Х ) - X V/ .

Из таблицы настроек находят, что ,х.) является девятой типовой функцией трех переменных, следователно, сигналы настройки равны:

и

.;

и,0;

Аналогично функция Ч(х , х ) является восьмой типовой функцией трех переменных и определяемые ею сигналы настройки равны:

, O;L;

ТТ --LT .

12 3

13 2

и x, .

1 4

Таким образом, при подаче на информационный вход 7 переменной х. на настроечные входы 8-21 - сигналов и (х ,0,Х2,х.,х,0,х,0,0,0,х,

3 Ч

на выходе 22 модуля реализуется заданная функция f(х ,х ).

Формула изобретения

Универсальный логический модуль, содержащий элемент СЛОЖЕНИЕ ПО МО- ,

первый элемент ИЛИ, при- чем информационный вход модуля соеди- jjgjj первым входом первого элемента

модуля,

0

5

выход которого соединен с выходом элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА, отличающийся тем, что, с целью повышения быстродействия, он содержит второй, третий,четвертый и пятый элементы ШШ, причем второй вход первого элемента ИЛИ соединен с вторым настроечным входом модуля, третий, четвертый и пятый настроечные входы которого соединены с первым, вторым и третьим входами второго элемента ИЛИ, выход которого соединен с третьим входом элемента

31411730

СЛОЖЕНИЕ ПО МОДУЛЮ ДВА, четвертый ля соединены с первым, вторым и треть- вход которого соединен с выходом им входами четвертого элемента ИЛИ,

выход которого соединен с пятым входом элемента СЛОЖЕНИЕ ПО МОДУЛЮ ДВА, шестой вход которого соединен с выходом пятого элемента ИЛИ, первый, второй и третий входы которого соеди-.

третьего элемента ИЖ, первый, второй и третий входы которого соединены с шестым, седьмым и восьмым настроечными входами модуля, информационный вход которого соединен с чет

| название | год | авторы | номер документа |

|---|---|---|---|

| Универсальный логический модуль | 1987 |

|

SU1536370A1 |

| Универсальный логический модуль | 1986 |

|

SU1319018A1 |

| Универсальный логический модуль | 1984 |

|

SU1242930A1 |

| Универсальный логический модуль | 1986 |

|

SU1319019A1 |

| Универсальный логический модуль | 1984 |

|

SU1251064A1 |

| Универсальный логический модуль | 1984 |

|

SU1234825A1 |

| Устройство для вычисления симметрических булевых функций | 1989 |

|

SU1684792A1 |

| Устройство для полиномиального разложения логических функций | 1988 |

|

SU1550507A1 |

| Многофункциональный логический модуль | 1984 |

|

SU1196846A1 |

| Устройство для вычисления симметрических булевый функций | 1988 |

|

SU1689943A1 |

Изобретение относится к вычислительной технике и микроэлектронике и предназначено для реализации всех логических функций четырех перемен-, ных. Цель изобретения - увеличение быстродействия универсального логи- . ческого модуля,-Поставленная цель достигается тем, что модуль содержит пять элементов ИЛИ 1-5, один элемент СЛОЖЕНИЕ ПО МОДУЛЮ ДВА 6, один информационный . 7 и четырнадцать настроечных входов 8-21, выход 22. При подаче на информационный вход переменной х, на настроечные входы сигналов настройки, принадлежащих множеству {о, 1, х„,,х, x,j,,x , на выходе модуля реализуется логическая функция четырех переменных f (х ,хр, определяемая вектором настройки 1 ил., 1 табл.

вертыми входами второго и третьего элементов ИЛИ, девятый, десятый и одиннадцатый настроечные входы моду

V X X X

0. 3 4

22

иены с двенадцатым, тринадцатым и че- JQ тырнадцатым настроечными входами модуля .

О

3 4 а

X,

| Универсальное логическое устройство | 1984 |

|

SU1166095A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Универсальный логический модуль | 1986 |

|

SU1319018A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-07-23—Публикация

1987-01-12—Подача