I Изобретение относится к цифровой вычислительной технике и может быть Использовано при исследовании разли Иых технологий программирования.

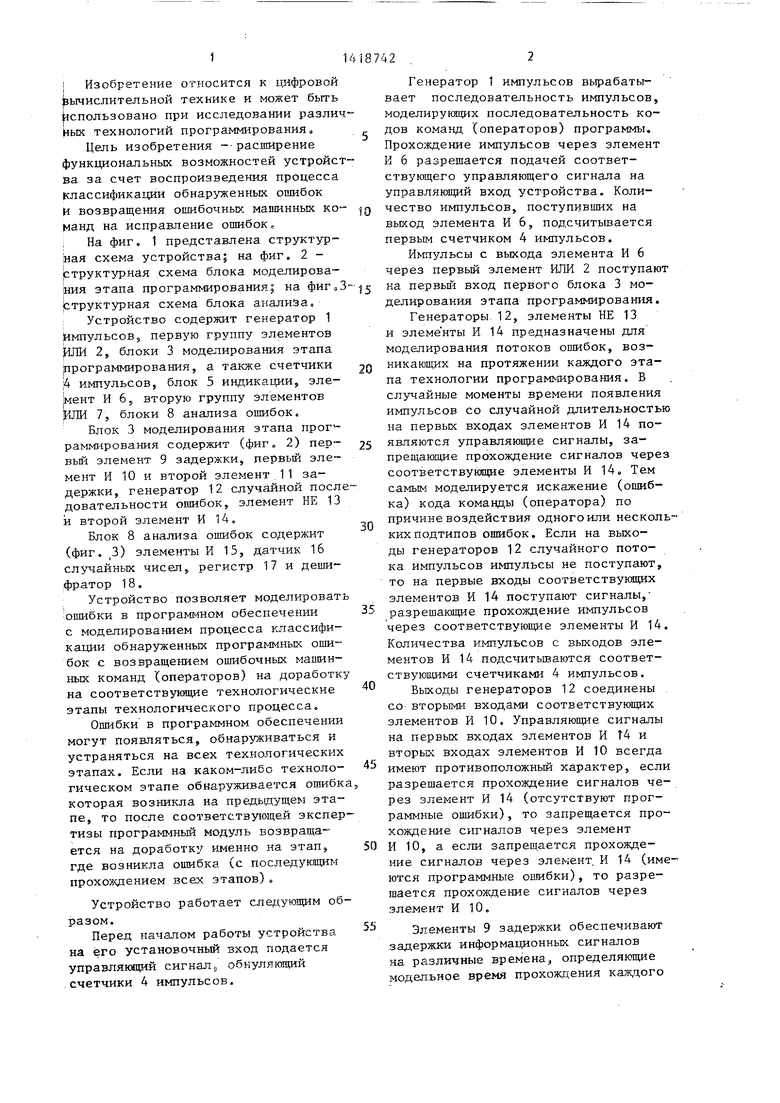

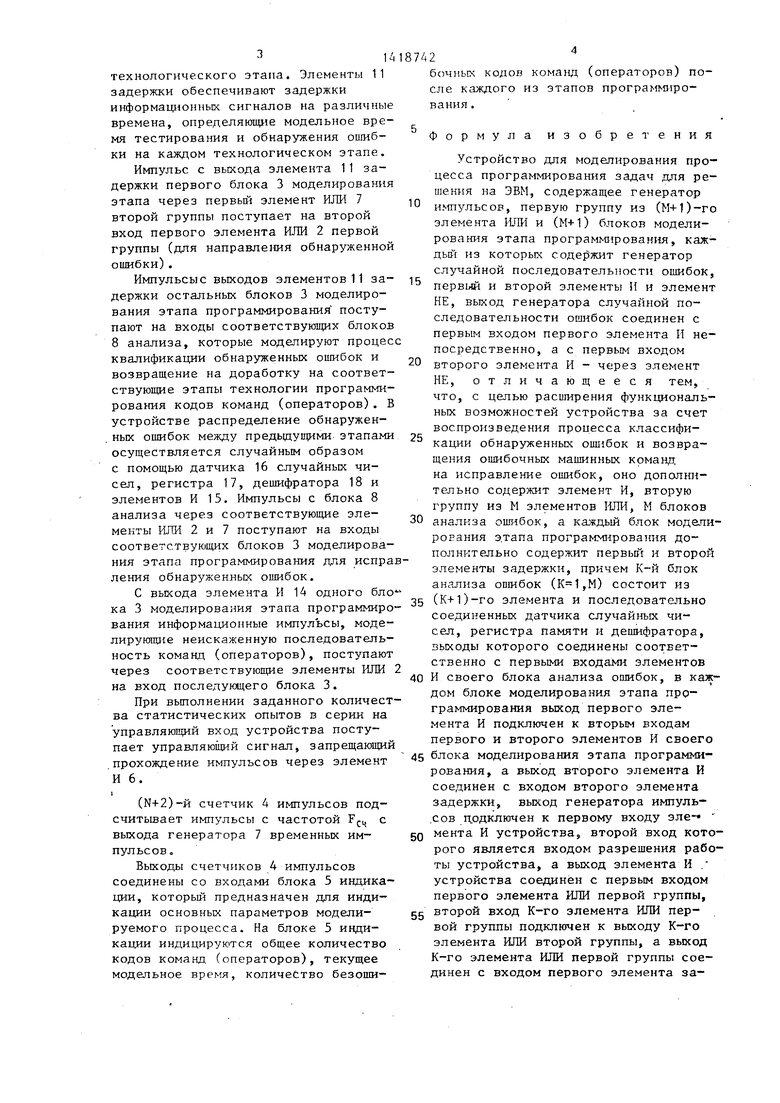

Цель изобретения --расширение функциональных возможностей устройс ва за счет воспроизведения процесса классификации обнаруженных ошибок И возвращения ошибочных машинных команд на исправление ошибок, : На фиг, 1 представлена структурная схема устройства; на фиг. 2 - структурная схема блока моделирова- рия этапа программирования; на фиг, Структурная схема блока анализа, : Устройство содержит генератор 1 Импульсов5 первую группу элементов ИЛИ 2, блоки 3 моделирования этапа Программирования, а также счетчики импульсов, блок 5 индикации, эле- 1мент И 6, вторую группу элементов 7, блоки 8 анализа ошибок.

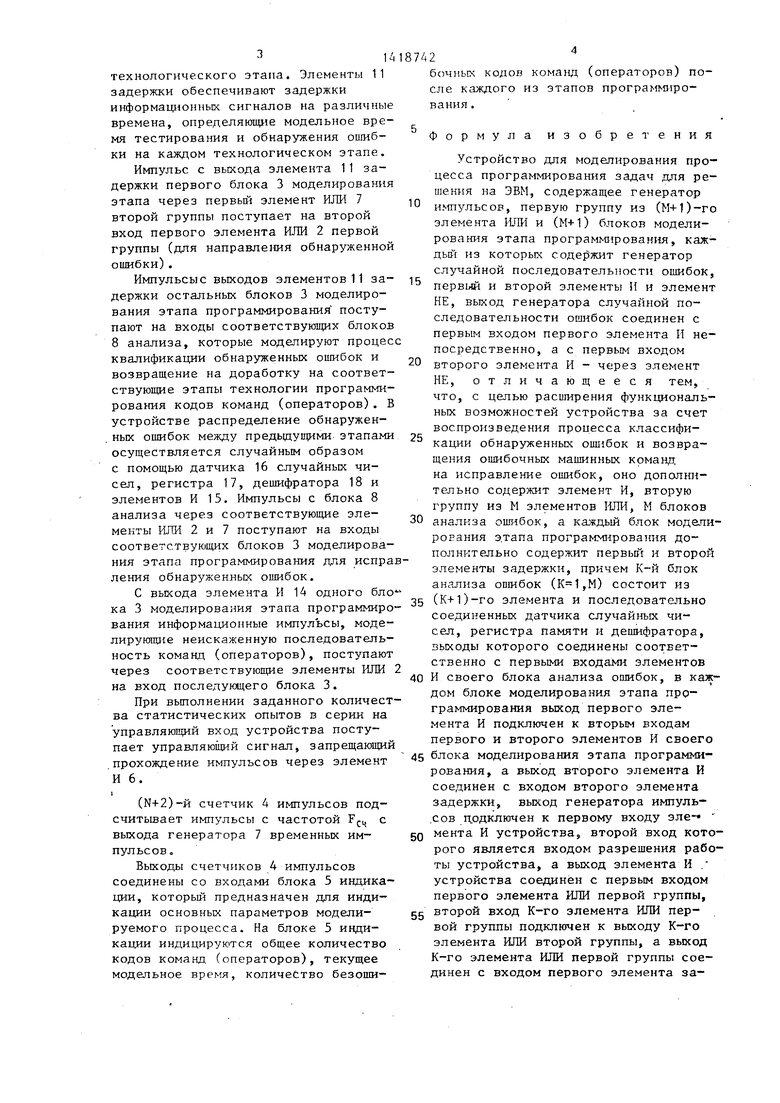

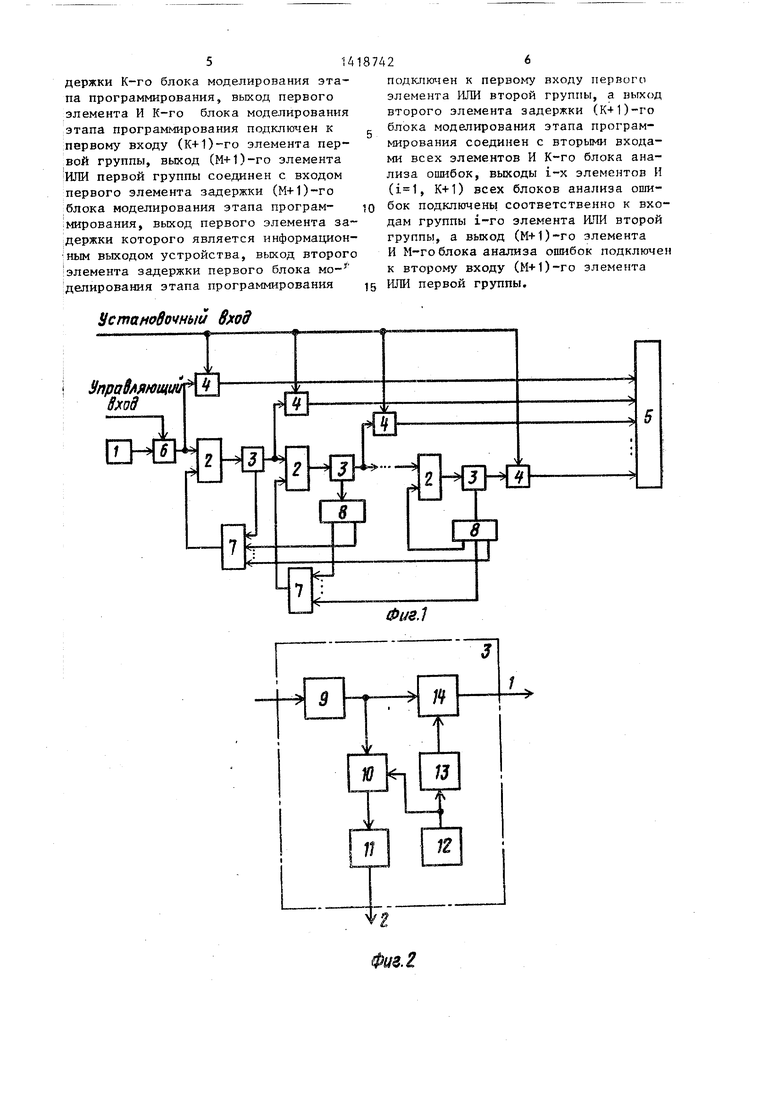

Блок 3 моделирования этапа раммирования содержит (фиг, 2) пер- вьм элемент 9 задержки, первый элемент И 10 и второй элемент . 11 задержки, генератор 12 случайной послдовательности ошибок, элемент НЕ 13 и второй элемент И 14,

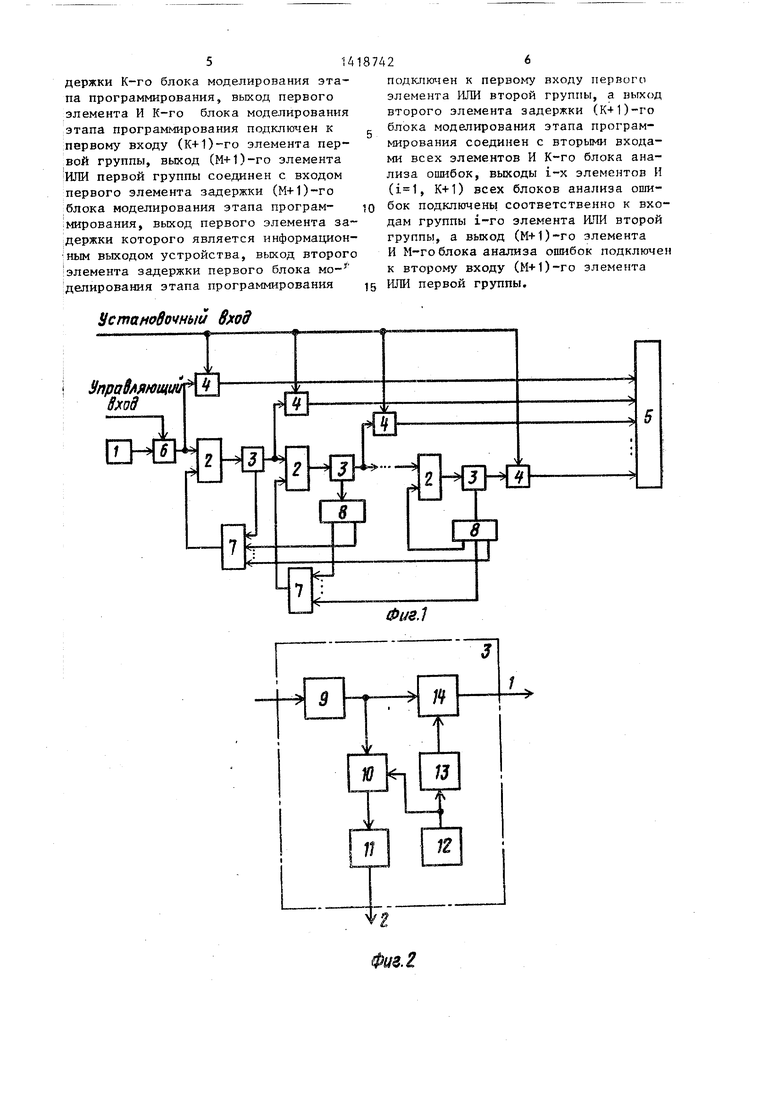

Блок 8 анализа ошибок содержит (фиг. 3) элементы И 15, датчик 16 случайных чисел, регистр 17 и дешифратор 18.

Устройство позволяет моделировать ошибки в программном обеспечении с модепированием процесса классификации обнаруженных nporpaNJMHbix ошибок с возвращением ошибочных машинных команд (операторов) на доработку на соответствукицие технологические этапы технологического процесса.

Ошибки в программном обеспечении могут Появляться, обнаруживаться и устраняться на всех технологических этапах. Если на каком-либо технологическом этапе обнаруживается опмбк которая возникла на предьщущем этапе, то после соответствующей экспертизы программньй модуль возвращается на доработку именно на этап, где возникла оимбка (с последукщим пр ох общением всех этапов) «

Устройство работает след,ующим образом.

Перед началом работы устройства на его установочный вход подается управляющий сигналр обнуляющий счетчики 4 импульсов.

Генератор 1 импульсов вырабатывает последовательность импульсов, моделирукщих последовательность ко- ,- дов комазд (операторов) программы. Прохождение импульсов через элемент И 6 разрешается подачей соответствующего управляющего сигнала на управляющий вход устройства. Коли1Q чество импульсов, поступивших на выход элемента И 6, подсчитывается первым счетчиком 4 импульсов.

Импульсы с выхода элемента И 6 через первый элемент ИЛИ 2 поступают

5 иа первьй вход первого блока 3 моделирования этапа программирования.

Генераторы 12, элементы НЕ 13 и элеме нты И 14 предназначены для моделирования потоков ошибок, возQ никающих на протяжении каждого этапа технологии программирования. В случайные моменты времени появления импульсов со случайной длительностью на первых входах элементов И 14 по5 являются управляюшре сигналы, запрещающие прохождение сигналов через соответствующие элементы И 14„ Тем самым моделируется искажение (ошибка) кода команды (оператора) по причине воздействия одного или несколь - кихподтипов ошибок. Если на выходы генераторов 12 случайного потока импульсов импульсы не поступают, то на первые входы соответствующих элементов И 14 поступают сигналы, разрешающие прохождение импульсов через соответствуюш 1е элементы И 14. Количества импульсов с выходов элементов И 14 подсчитьшаются соответствующими счетчиками 4 импульсов.

Выходы генераторов 12 соединены . со вторыми входами соответствуюш их элементов И 10. Управляющие сигналы на первых входах элементов И Т4 и вторых входах элементов И 10 всегда имеют противоположный характер, если разрешается прохождение сигналов через элемент И 14 (отсутствуют программные ошибки), то запрещается прохождение сигналов через элемент

0 И 10, а если запрещается прохождение сигналов через элемент. И 14 (имеются программные ошибки), то разрешается прохояодение сигналов через элемент И 10.

- Элементы 9 задержки обеспечивают задержки информационных сигналов на различные временаj определяющие модельное время прохождения каж,дого

0

5

0

5

1

технологического этапа. Элементы 11 задержки обеспечивают задержки информационных сигналов на различные времена, определяющие модельное время тестирования и обнаружения ошибки на каждом технологическом этапе.

Импульс с выхода элемента 11 задержки первого блока 3 моделирования этапа через первьш элемент ИЛИ 7 второй группы поступает на второй вход первого элемента ИЛИ 2 первой группы (для направления обнаруженной ошибки).

Импульсы с выходов элементов 11 за- держки остальных блоков 3 моделирования этапа программирования поступают на входы соответствующих блоков 8 анализа, которые моделируют процес квалификации обнаруженньк ошибок и возвращение на доработку на соответствующие этапы технологии программирования кодов команд (операторов). В устройстве распределение обнаружен- , ных ошибок между предыдущими этапами осуществляется случайным образом с помощью датчика 16 случайных чисел, регистра 17, дешифратора 18 и элементов И 15. Импульсы с блока 8 анализа через соответствующие эле- менты ИЛИ 2 и 7 поступают на входы соответствующих блоков 3 моделирования этапа программирования для испраления обнаруженных ошибок.

С выхода элемента И 14 одного бло

ка 3 моделирования этапа программирования информационные импульсы, моде- лирунзщие неискаженную последовательность команд (операторов), поступают через соответствующие элементы ИЛИ на вход последукщего блока 3.

При выполнении заданного количества статистических опытов в серии на управляющий вход устройства поступает управляющий сигнал, запрещающий прохождение импульсов через элемент И 6.

(Н+2)-й счетчик 4 импульсов под- считьшает импульсы с частотой , с выхода генератора 7 временных им- пульсов о

Выходы счетчиков 4 импульсов соединены со входами блока 5 индикации, который предназначен для индикации основных параметров модели- руемого процесса. На блоке 5 индикации индицируются общее количество кодов команд (операторов), текущее модельное время, количество безоши

5 0 5 Q

с

0

5

0

5

бочньгх кодов команд (операторов) после каждого из этапов программирования .

Формула изобретения

Устройство для моделирования процесса программирования задач для решения на ЭВМ, содержащее генератор импульсов, первую группу из (М+1)-го элемента ИЛИ и (М+1) блоков моделирования этапа программирования, каждый из которых содержит генератор случайной последовательности ошибок, первый и второй элементы И и элемент НЕ, выход генератора случайной последовательности ошибок соединен с первым входом первого элемента И непосредственно, а с первым входом второго элемента И - через элемент НЕ, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет воспроизведения процесса классификации обнаруженньк ошибок и возвращения ошибочных машинных команд, на исправление ошибок, оно дополнительно содержит элемент И, вторую группу из М элементов 1-ШИ, М блоков анализа ошибок, а каждый блок моделирования этапа программирования дополнительно содержит nepBbDi и второй элементы задержки, причем К-й блок ансгпиза опшбок (,М) состоит из (К+1)-го элемента и последовательно соединенных датчика случайных чисел, регистра памяти и дешифратора, выходы которого соединены соответственно с первыми входами элементов И своего блока анализа ошибок, в каждом блоке моделирования этапа прр граммирования вькод первого элемента И подключен к вторым входам первого и второго элементов И своего блока моделирования этапа программирования, а выход второго элемента И соединен с входом второго элемента задержки, выход генератора импульсов п.одключен к первому входу эле- мента И устройства, второй вход которого является входом разрешения работы устройства, а выход элемента И / устройства соединён с первым входом первого элемента ИЛИ первой группы, второй вход К-го элемента ИЛИ первой группы подключен к выходу К-го элемента ИЛИ второй группы, а вькод К-го элемента ИЛИ первой группы соединен с входом первого элемента заЗпра9АЛН1Щ(

Физ,1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования ошибок программного обеспечения | 1986 |

|

SU1365092A1 |

| Устройство для моделирования процесса программирования задач на ЭВМ | 1987 |

|

SU1418741A1 |

| Устройство для моделирования системы связи | 1986 |

|

SU1399762A1 |

| Устройство для моделирования ошибок программного обеспечения вычислительных систем | 1986 |

|

SU1357973A1 |

| Устройство для моделировавания технологии программирования | 1987 |

|

SU1465892A1 |

| Модель дуги сети | 1987 |

|

SU1499372A1 |

| Устройство для моделирования процесса контроля программного обеспечения | 1989 |

|

SU1612312A1 |

| Устройство для моделирования систем сбора данных | 1986 |

|

SU1325504A1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ ТЕХНОЛОГИИ ПРОГРАММИРОВАНИЯ | 1990 |

|

RU2041487C1 |

| Устройство для моделирования ошибок программного обеспечения вычислительных систем | 1986 |

|

SU1325499A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано при исследовании различных технологий программирования. Цель изобретения - расширение функциональных возможностей устрой- ства за счет воспроизведения процесса классификации обнаруженных ошибок и возвращения ошибочных машинных команд на исправление ошибок. Цель достигается введением в устройство элемента И, группы элементов И, блоков анализа ошибок и введением в блок моделирования этапа програм- ьдарования двух элементов задержки. В блоке индикации индицируются общее количество кодов команд (операторов), текущее, модельное время, количество безошибочных кодов команд (операторов) после каждого из этапов программирования. 3 Ш1. с и (Л

0UQ,

| Устройство для моделирования работыСиСТЕМы СВязи | 1979 |

|

SU805331A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для моделирования ошибок программного обеспечения вычислительных систем | 1986 |

|

SU1357973A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-08-23—Публикация

1987-02-16—Подача