5.1 5.1

S

(Л

00

00 05

ФигЛ

Изобретение относится к устройствам для автоматического контроля оборудования и может быть использовано для контроля исправности сигнальных ламп аэропортов. Цель изобретения - повышение точноси работы и производительности устройства утем последовательного контроля нескольих групп сигнальных ламп.

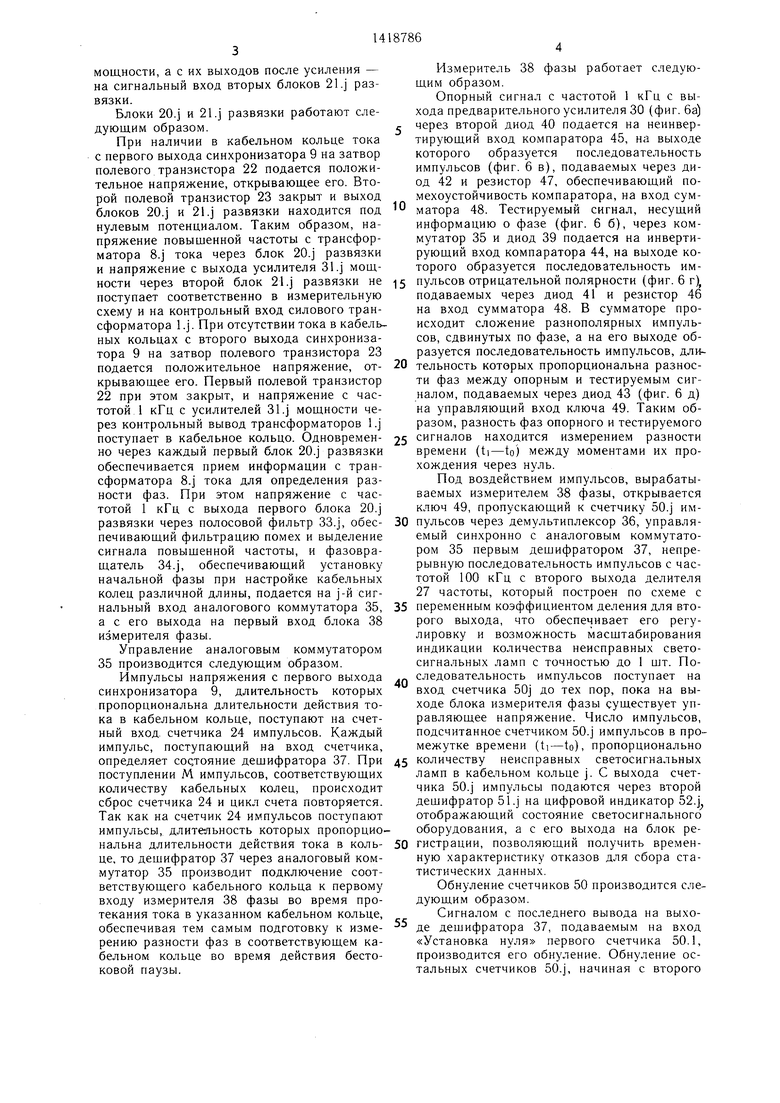

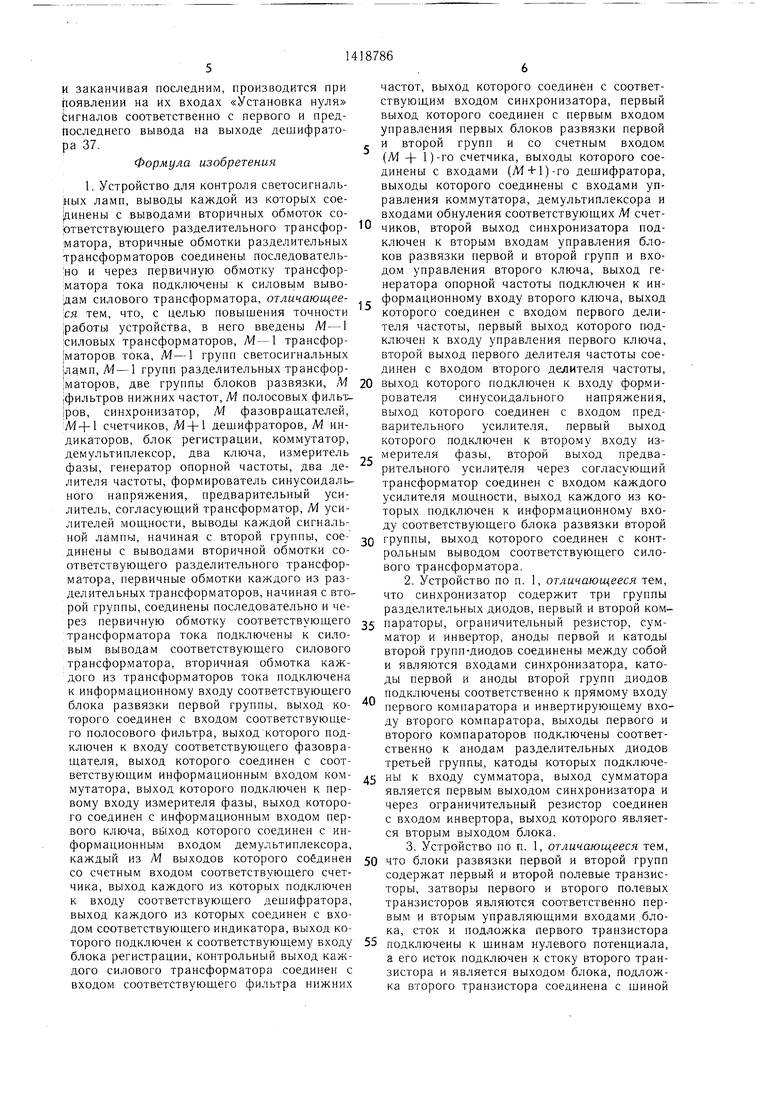

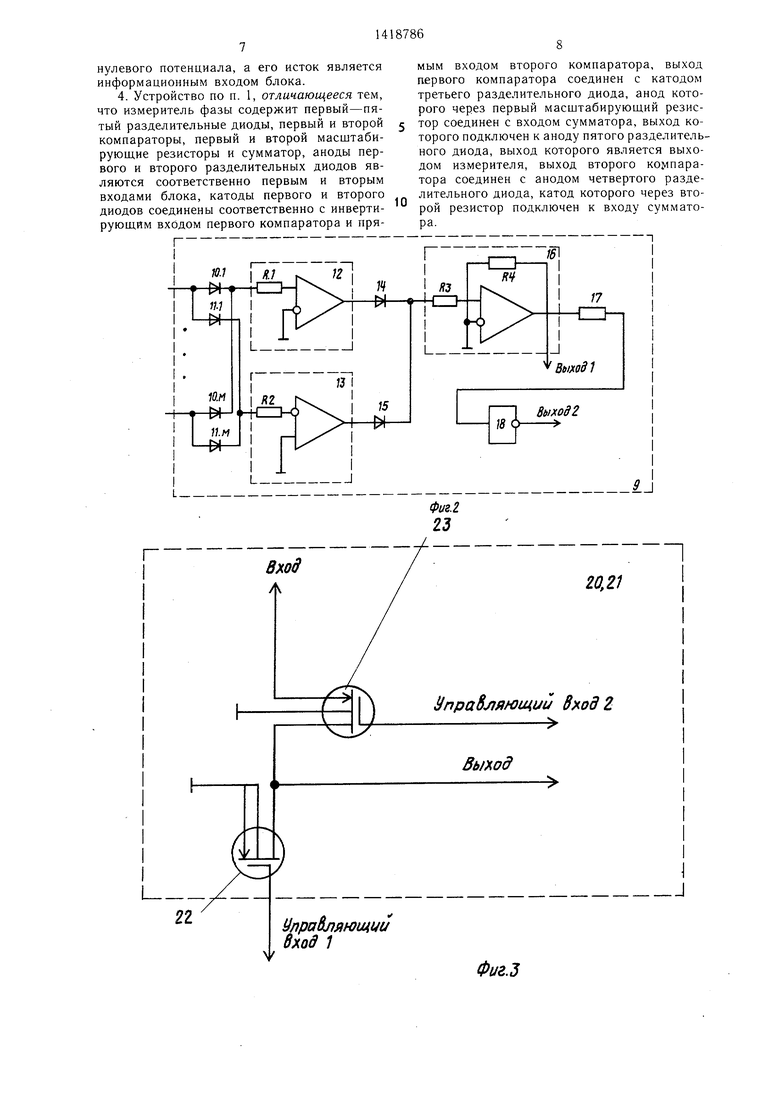

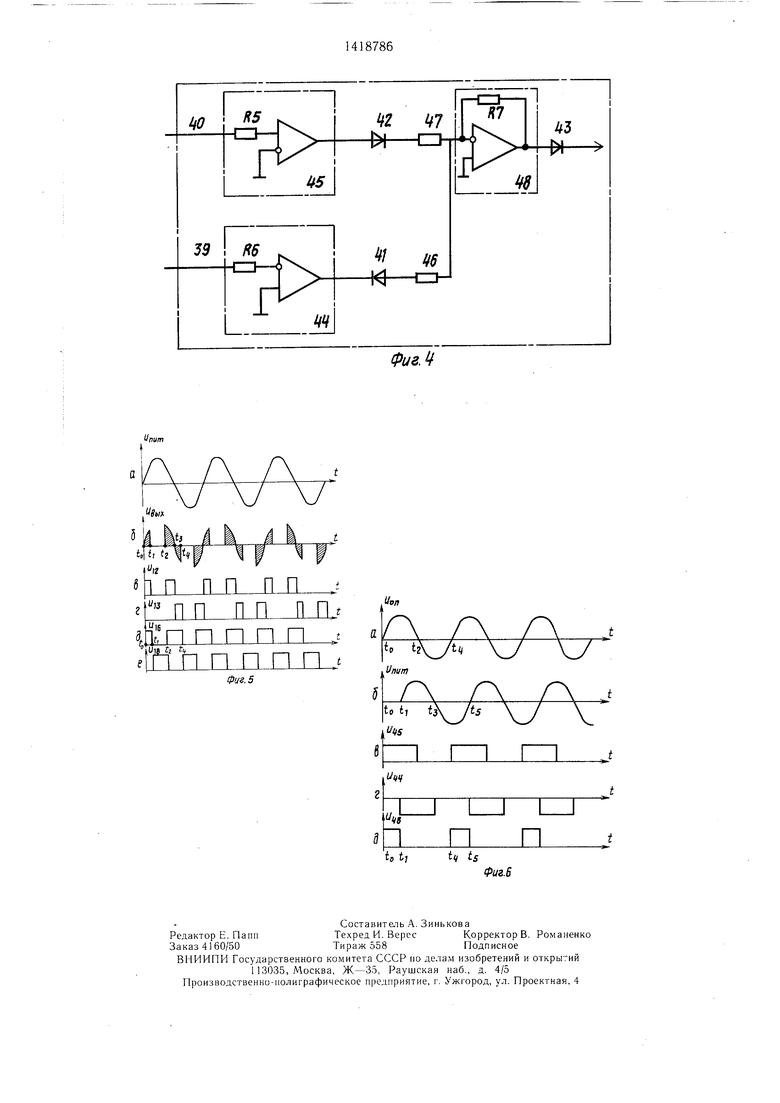

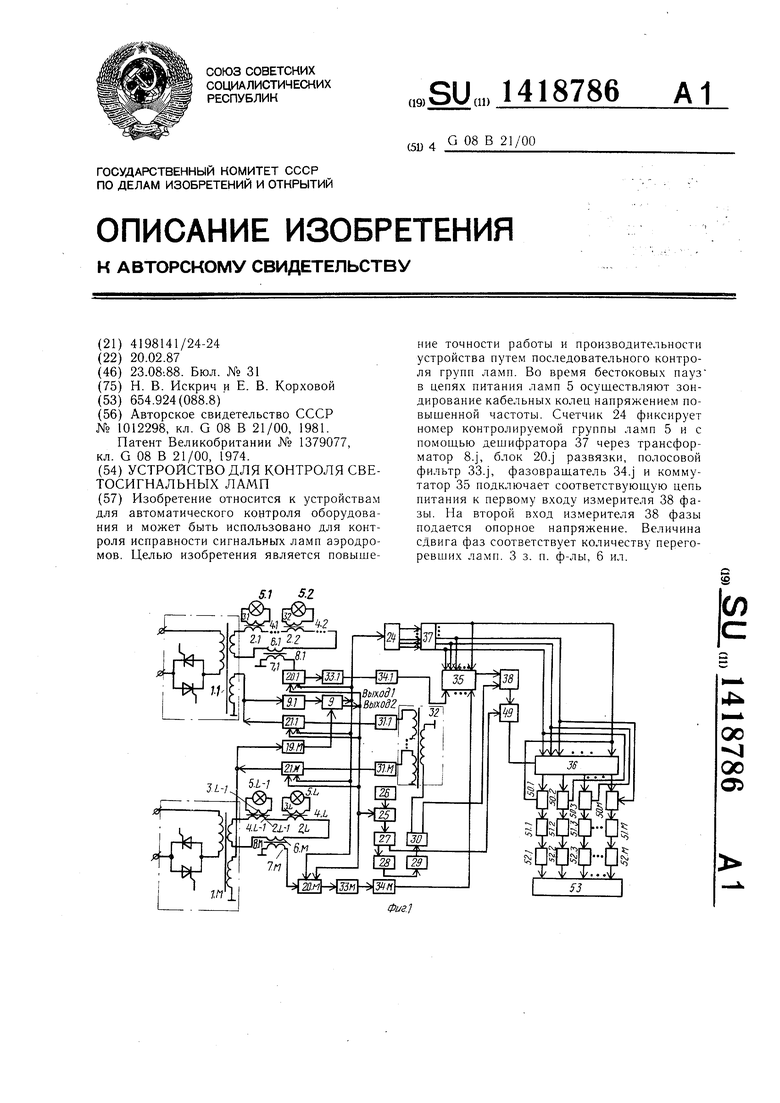

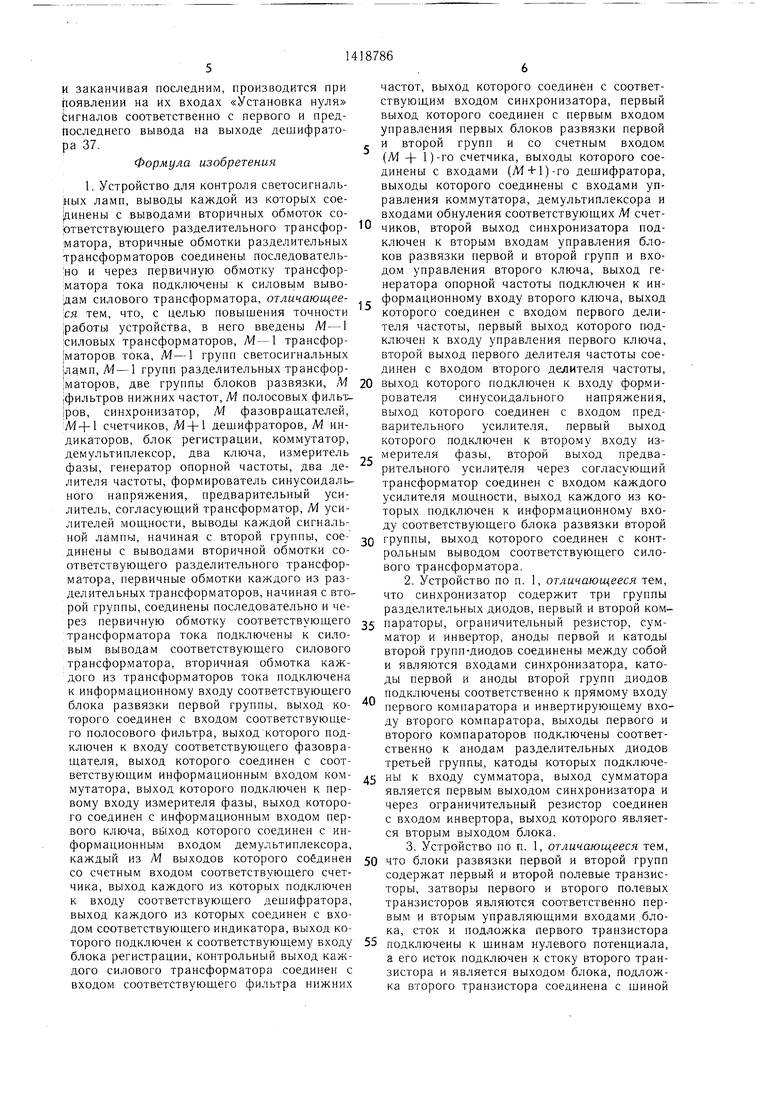

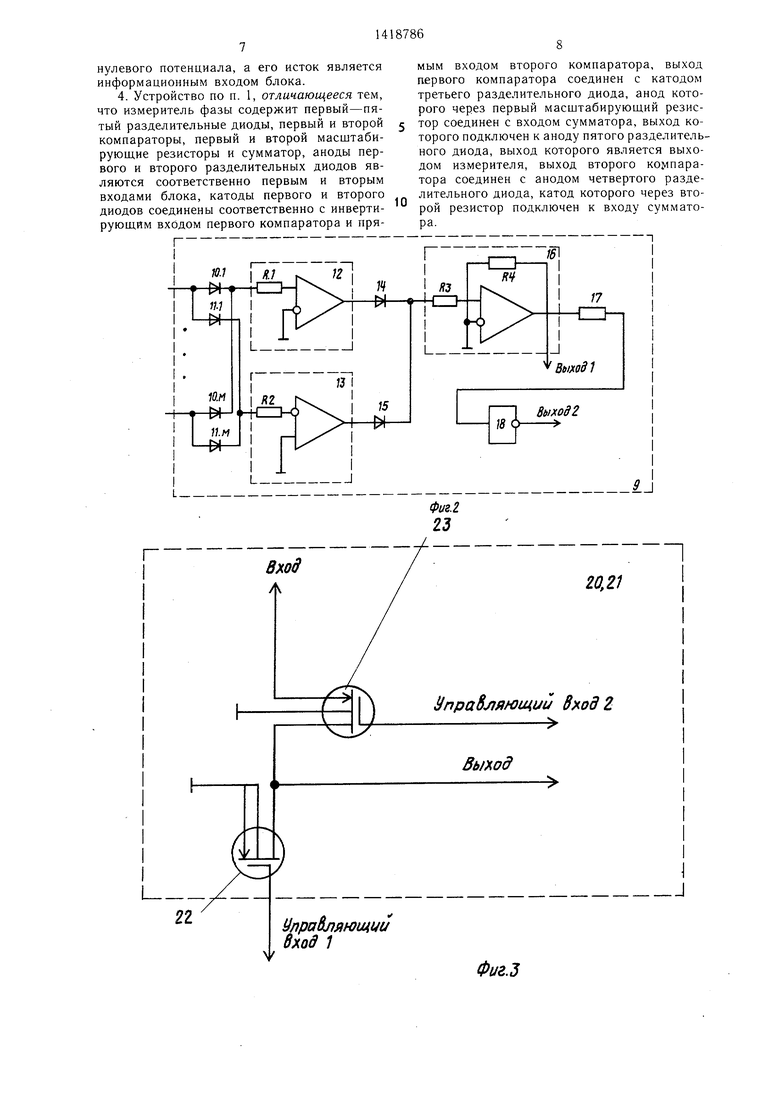

На фиг. 1 изображена функциональная хема устройства; на фиг. 2 - функциональная схема синхронизатора; на фиг. 3 - функциональная схема блоков развязки; на фиг. 4 - функциональная схема измеритея фазы; на фиг. 5 и 6 - временные диаграммы сигналов, поясняющие работу синхронизатора и измерителя фазы соответственно.

Устройство содержит силовые трансформаторы 1.1 - 1.М, первичные 2.1-2.L и вторичные 3.1-3.L обмотки разделительных трансформаторов 4.1-4.L света, сигнальные лампы 5.1-5.L, первичные 6.1-6.М и вторичные 7.1-7.М обмотки трансформаторов 8.1-8.М тока, синхронизатор 9, разделительные элементы 10.1 - Ю.М и 11.1 - 11.М, выполненные в виде диодов, компараторы 12 и 13, разделительные элементы 14 и 15, выполненные в виде диодов, сумматор 16, ограничительный элемент 17, выполненный в виде резистора, инвертор 18, фильтры 19.1 -19.М нижних частот, первые 20.1 - 20.М, вторые 21.1-21.М блоки развязки, полевые транзисторы 22 и 23, счетчик 24, ключ 25, генератор 26 опорной частоты, де- лители 27 и 28 частоты, формирователь 29 синусоидального напряжения, предварительный усилитель 30, усилители 31.1-3.Л мощности, согласуюплий трансформатор 32, полосовые фильтры 33.1-33.М, фазовращатели 34.1-34.М, аналоговый коммутатор 35, де- му; ьтиплексор 36, дешифратор 37, измеритель 38 фазы, разделительные элементы 39- - 43, выполненные в виде диодов, компараторы 44 и 45, масштабирующие элементы 46 и 47, выполненные в виде резисторов, сумматор 48, ключ 49, счетчики 50.1-50.М, дешифраторы 51.1-51.М, индикаторы 52.1 - 52.М, блок 53 регистрации, где М - число групп сигнальных ламп 5.1-5.L, L - общее число сигнальных ламп.

Для выявления неисправных сигнальных ламп 5.1 (1 1,...,.) используется метод зондирования цепи последовательного питания ламп накаливания током повьппенной частоты во зремя бестоковых пауз в нагрузке.

На повышенной частоте, например 1 кГц, полное сопротивление кабельного кольца последовательного питания ламп 5.1 через разделительные трансформаторы 4.1 минимально и практически равно чисто активному при всех исправных лампах 5.i. При перегорании ламп резко возрастает полное сопротивление всего кольца и образуется разность фаз между током и напряжением в кольце за счет изменения индуктивного сопротивления разделительных трансформаторов 4, работающих на холостом ходу. При этом сдвиг фаз между током и напряжением увеличивается пропорционально количеству перегоревщих ламп.

Устройство работает следующим .образом. На вход синхронизатора 9 с контрольных выходов силовых трансформаторов l.j х X (j- 1-М) через фильтр 19 нижних час,. тот, подавляющий сигнал зондирующей частоты, подается напряжение, действующее в кольце (фиг. 5 б). При этом положительное значение напряжения через диод 10.j поступает на неинвертирующий вход компаратора 12, па выходе которого формируют5 ся положительные импульсы прямоугольной формы, показанные на фиг. 5 в. Их длительность пропорциональна длительности токовых пауз в кольце в положительный полупериод. Отрицательное значение напряжения, действующее в кольце питания ламп

0 5.i, через диод 11.J подается па инвертирующий вход компаратора 13, на выходе которого формируются положительные импульсы напряжения прямоугольной формы, показанные па фиг. 5 г.

5 С выходов компараторов 12 и 13 импульсы напряжения через диоды 14 и 15 подаются на неинвертирующий вход сумматора 16, на выходе которого формируются импульсы напряжения, показанные на фиг. 5 д. Значение интервала времени ti-iz соответ0 ствует бестоковой паузе в нагрузке, а значение времени t2-14 - токовой паузе. Выходные импульсы напряжения сумматора 16 через резистор 17 поступают на инвертор 18, па выходе которого формируются прямоугольные импульсы, длительность которых

5 пропорциональна бестоковым паузам в нагрузке.

Длительность импульсов напряжения па выходе синхронизатора 9 определяется длительностью бестоковых пауз в нагрузке ми- Р нималыюй величины, соответствующих максимальному току нагрузки в кабельном кольце, что обеспечивает возможность подключения к входам блока синхронизатора через фильтры 19.j нижних частот любого количества кабельных колец, например М, с раз5 личной длительностью бестоковых пауз в нагрузке.

С второго выхода синхронизатора 9 им- нульсы напряжения, пропорциональные бес- токовы.ч паузам в нагрузке, открывают ключ

0 25, через который напряжение с частотой 1 кГц генератора 26 опорной частоты подается на делитель 27 частоты, с первого выхода которого напряжение с частотой, например, 100 кГц подается на делитель 28 частоты, а с его выхода с частотой i кГц

на формирователь 29 синусоидального напряжения. Синусоидальное напряжение с формирователя 29 после усиления в предварительном усилителе 30 поступает через трансформатор 32 на вход усилителей 31.J

мощности, а с их выходов после усиления - на сигнальный вход вторых блоков 21.J развязки.

Блоки 20. и 21.j развязки работают следующим образом.

При наличии в кабельном кольце тока с первого выхода синхронизатора 9 на затвор полевого транзистора 22 подается положительное напряжение, открывающее его. Второй полевой транзистор 23 закрыт и выход блоков 20.j и 21.j развязки находится под нулевым потенциалом. Таким образом, напряжение повышенной частоты с трансформатора 8.J тока через блок 20.J развязки и напряжение с выхода усилителя 31.j мощИзмеритель 38 фазы работает следующим образом.

Опорный сигнал с частотой 1 кГц с выхода предварительного усилителя 30 (фиг. 6а) с через второй диод 40 подается на неинвертирующий вход компаратора 45, на выходе которого образуется последовательность импульсов (фиг. 6 в), подаваемых через диод 42 и резистор 47, обеспечивающий помехоустойчивость компаратора, на вход сум- матора 48. Тестируемый сигнал, несущий информацию о фазе (фиг. 6 б), через коммутатор 35 и диод 39 подается на инвертирующий вход компаратора 44, на выходе которого образуется последовательность имности через второй блок 21. развязки не 5 пульсов отрицательной полярности (фиг. 6 г), поступает соответственно в измерительнуюподаваемых через диод 41 и резистор 46

схему и на контрольный вход силового тран-на вход сумматора 48. В сумматоре просформатора l.j. При отсутствии тока в кабель- исходит сложение разнополярных импуль- ных кольцах с второго выхода синхрониза-сов, сдвинутых по фазе, а на его выходе обтора 9 на затвор полевого транзистора 23 разуется последовательность импульсов, длиот- 20 тельность которых пропорциональна разности фаз между опорным и тестируемым сигналом, подаваемых через диод 43 (фиг. 6 д) на управляющий вход ключа 49. Таким образом, разность фаз опорного и тестируемого сигналов находится измерением разности времени (ti-to) между моментами их проподается положительное напряжение, крывающее его. Первый полевой транзистор 22 при этом закрыт, и напряжение с частотой 1 кГц с усилителей 31.J мощности через контрольный вывод трансформаторов l.j поступает в кабельное кольцо. Одновременно через каждый первый блок 20.J развязки обеспечивается прием информации с трансформатора 8.J тока для определения разности фаз. При этом напряжение с частотой 1 кГц с выхода первого блока 20.j

25

хождения через нуль.

Под воздействием импульсов, вырабатываемых измерителем 38 фазы, открывается ключ 49, пропускающий к счетчику 50.j имразвязки через полосовой фильтр 33.J, обес- 30 пульсов через демультиплексор 36, управляпечивающий фильтрацию помех и выделение сигнала повыщенной частоты, и фазовращатель 34.j, обеспечивающий установку начальной фазы при настройке кабельных колец различной длины, подается на j-й сигнальный вход аналогового коммутатора 35, а с его выхода на первый вход блока 38 измерителя фазы.

Управление аналоговым коммутатором 35 производится следующим образом.

Импульсы напряжения с первого выхода синхронизатора 9, длительность которых пропорциональна длительности действия тока в кабельном кольце, поступают на счетный вход счетчика 24 импульсов. Каждый импульс, поступающий на вход счетчика, определяет состояние дешифратора 37. При поступлении М импульсов, соответствующих количеству кабельных колец, происходит сброс счетчика 24 и цикл счета повторяется. Так как на счетчик 24 импульсов поступают импульсы, длительность которых пропорциональна длительности действия тока в кольце, то дешифратор 37 через аналоговый коммутатор 35 производит подключение соответствующего кабельного кольца к первому входу измерителя 38 фазы во вре.мя протекания тока в указанном кабельном кольце, обеспечивая тем самым подготовку к измерению разности фаз в соответствующем кабельном кольце во время действия бестоковой паузы.

35

40

45

50

55

емый синхронно с аналоговым коммутатором 35 первым дешифратором 37, непрерывную последовательность импульсов с частотой 100 кГц с второго выхода делителя 27 частоты, который построен по схеме с переменным коэффициентом деления для второго выхода, что обеспечивает его регулировку и возможность масштабирования индикации количества неисправных светосигнальных ламп с точностью до 1 шт. Последовательность импульсов поступает на вход счетчика 50j до тех пор, пока на выходе блока измерителя фазы существует управляющее напряжение. Число импульсов, подсчитанное счетчиком 50.j импульсов в промежутке времени (ti-to), пропорционально количеству неисправных светосигнальных ламп в кабепьном кольце j. С выхода счетчика 50.j импульсы подаются через второй дешифратор 51.j на цифровой индикатор 52.j отображающий состояние светосигнального оборудования, а с его выхода на блок регистрации, позволяющий получить временную характеристику отказов для сбора статистических данных.

Обнуление счетчиков 50 производится следующим образом.

Сигналом с последнего вывода на выходе дешифратора 37, подаваемым на вход «Установка нуля первого счетчика 50.1, производится его обнуление. Обнуление остальных счетчиков 50.j, начиная с второго

Измеритель 38 фазы работает следующим образом.

Опорный сигнал с частотой 1 кГц с выхода предварительного усилителя 30 (фиг. 6а) с через второй диод 40 подается на неинвертирующий вход компаратора 45, на выходе которого образуется последовательность импульсов (фиг. 6 в), подаваемых через диод 42 и резистор 47, обеспечивающий помехоустойчивость компаратора, на вход сум- матора 48. Тестируемый сигнал, несущий информацию о фазе (фиг. 6 б), через коммутатор 35 и диод 39 подается на инвертирующий вход компаратора 44, на выходе которого образуется последовательность им5 пульсов отрицательной полярности (фиг. 6 г), подаваемых через диод 41 и резистор 46

20

25

хождения через нуль.

Под воздействием импульсов, вырабатываемых измерителем 38 фазы, открывается ключ 49, пропускающий к счетчику 50.j импульсов через демультиплексор 36, управля0 пульсов через демультиплексор 36, управля5

0

5

0

5

емый синхронно с аналоговым коммутатором 35 первым дешифратором 37, непрерывную последовательность импульсов с частотой 100 кГц с второго выхода делителя 27 частоты, который построен по схеме с переменным коэффициентом деления для второго выхода, что обеспечивает его регулировку и возможность масштабирования индикации количества неисправных светосигнальных ламп с точностью до 1 шт. Последовательность импульсов поступает на вход счетчика 50j до тех пор, пока на выходе блока измерителя фазы существует управляющее напряжение. Число импульсов, подсчитанное счетчиком 50.j импульсов в промежутке времени (ti-to), пропорционально количеству неисправных светосигнальных ламп в кабепьном кольце j. С выхода счетчика 50.j импульсы подаются через второй дешифратор 51.j на цифровой индикатор 52.j отображающий состояние светосигнального оборудования, а с его выхода на блок регистрации, позволяющий получить временную характеристику отказов для сбора статистических данных.

Обнуление счетчиков 50 производится следующим образом.

Сигналом с последнего вывода на выходе дешифратора 37, подаваемым на вход «Установка нуля первого счетчика 50.1, производится его обнуление. Обнуление остальных счетчиков 50.j, начиная с второго

и заканчивая последним, производится при появлении на их входах «Установка нуля Ьигналов соответственно с первого и пред- noCv eднeгo вывода па выходе дешифратора 37.

Формула изобретения

1. Устройство для контроля светосигнальных ламп, выводы каждой из которых сое- Динены с выводами вторичных обмоток соответствующего разделительного трансформатора, вторичные обмотки разделительных трансформаторов соединены последователь- но и через первичную обмотку трансформатора тока подключены к силовым выводам силового трансформатора, отличающееся тем, что, с целью повышения точности |работы устройства, в него введены М-1 1СИЛОВЫХ трансформаторов, М - 1 трансформаторов тока, М-1 групп светосигнальных 1лцмп, М - 1 групп разделительных трансфор- |маторов, две группы блоков развязки, М фильтров нижних частот, М полосовых фильт- ipOB, синхронизатор, М фазовращателей, М-|-1 счетчиков, M-f-1 дещифраторов, М индикаторов, блок регистрации, коммутатор, демультиплексор, два ключа, измеритель фазы, генератор опорной частоты, два делителя частоты, формирователь синусоидального напряжения, предварительный усилитель, согласующий трансформатор, М усилителей мощности, выводы каждой сигнальной лампы, начиная с второй группы, сое- динены с выводами вторичной обмотки соответствующего разделительного трансформатора, первичные обмотки каждого из разделительных трансформаторов, начиная с второй группы, соединены последовательно и через первичную обмотку соответствующего трансформатора тока подключены к силовым выводам соответствующего силового трансформатора, вторичная обмотка каждого из трансформаторов тока подключена к информационному входу соответствующего блока развязки первой группы, выход которого соединен с входом соответствующего полосового фильтра, выход которого подключен к входу соответствующего фазовращателя, выход которого соединен с соответствующим информационным входом коммутатора, выход которого подключен к первому входу измерителя фазы, выход которого соединен с информационным входом первого ключа, ВЙ1ХОД которого соединен с информационным входом демультиплексора, каждый из М выходов которого соединен со счетным входом соответствующего счетчика, выход каждого из которых подключен к входу соответствующего дешифратора, выход каждого из которых соединен с входом соответствующего индикатора, выход которого подключен к соответствующему входу блока регистрации, контрольный выход каждого силового трансформатора соединен с входом соответствующего фильтра нижних

0

5

0

5

0

5

0

5

0

5

частот, выход которого соединен с соответствующим входом синхронизатора, первый выход которого соединен с первым входом управления первых блоков развязки первой и второй групп и со счетным входом (М -|- 1)-го счетчика, выходы которого соединены с входами {УИ + 1)-го дещифратора, выходы которого соединены с входами управления коммутатора, демультиплексора и входами обнуления соответствующих М счетчиков, второй выход синхронизатора подключен к вторым входам управления блоков развязки первой и второй групп и входом управления второго ключа, выход генератора опорной частоты подключен к информационному входу второго ключа, выход которого соединен с входом первого делителя частоты, первый выход которого подключен к входу управления первого ключа, второй выход первого делителя частоты соединен с входом второго делителя частоты, выход которого подключен к входу формирователя синусоидального напряжения, выход которого соединен с входом предварительного усилителя, первый выход которого подключен к второму входу измерителя фазы, второй выход предварительного усилителя через согласующий трансформатор соединен с входом каждого усилителя мощности, выход каждого из которых подключен к информационному входу соответствующего блока развязки второй группы, выход которого соединен с контрольным выводом соответствующего силового трансформатора.

2.Устройство по п. 1, отличающееся тем, что синхронизатор содержит три группы разделительных диодов, первый и второй компараторы, ограничительный резистор, сумматор и инвертор, аноды первой и катоды второй групп-диодов соединены между собой и являются входами синхронизатора, катоды первой и аноды второй групп диодов подключены соответственно к прямому входу первого компаратора и инвертирующему входу второго компаратора, выходы первого и второго компараторов подключены соответственно к анодам разделительных диодов третьей группы, катоды которых подключены к входу сумматора, выход сумматора является первым выходом синхронизатора и через ограничительный резистор соединен с входом инвертора, выход которого является вторым выходом блока.

3.Устройство по п. 1, отличающееся тем, что блоки развязки первой и второй групп содержат первый и второй полевые транзисторы, затворы первого и второго полевых транзисторов являются соответственно первым и вторым управляющими входами.блока, сток и подложка первого транзистора подключены к щинам нулевого потенциала, а его исток подключен к стоку второго транзистора и является выходом блока, подложка второго транзистора соединена с шиной

нулевого потенциала, а его исток является информационным входом блока.

4. Устройство по п. 1, отличающееся тем, что измеритель фазы содержит первый-пятый разделительные диоды, первый и второй компараторы, первый и второй масштабирующие резисторы и сумматор, аноды первого и второго разделительных диодов являются соответственно первым и вторым входами блока, катоды первого и второго диодов соединены соответственно с инвертирующим входом первого компаратора и пря1

мым входом второго компаратора, выход первого компаратора соединен с катодом третьего разделительного диода, анод которого через первый масштабирующий резистор соединен с входом сумматора, выход которого подключен к аноду пятого разделительного диода, выход которого является выходом измерителя, выход второго ко}лпара- тора соединен с анодом четвертого разделительного диода, катод которого через второй резистор подключен к входу сумматора.

Г ,-:: /51

| название | год | авторы | номер документа |

|---|---|---|---|

| Система автоматического пожаротушения | 1987 |

|

SU1461486A1 |

| Устройство для контроля светосигнальных ламп | 1984 |

|

SU1256067A1 |

| Импульсная лазерная установка для обработки материалов | 1989 |

|

SU1683937A1 |

| Резервированное устройство для синхронизации | 1984 |

|

SU1195489A1 |

| Устройство для многопостовой контактной сварки | 1981 |

|

SU998053A1 |

| Устройство для контроля воспроизведения цифровой информации с носителя магнитной записи | 1985 |

|

SU1282213A1 |

| Устройство для контроля сигнальных ламп | 1979 |

|

SU955149A1 |

| Устройство для отображения информации на газоразрядной индикаторной панели | 1981 |

|

SU1008782A1 |

| СЕЛЕКТИВНОЕ УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ОДНОФАЗНЫХ ЗАМЫКАНИЙ В КАБЕЛЬНЫХ ЛИНИЯХ | 2006 |

|

RU2316010C1 |

| Устройство для управления сигнальными лампами светофора | 1988 |

|

SU1674214A1 |

Изобретение относится к устройствам для автоматического контроля оборудования и может быть использовано для контроля исправности сигнальных ламп аэродромов. Целью изобретения является повышение точности работы и производительности устройства путем последовательного контроля групп ламп. Во время бестоковых пауз в цепях питания ламп 5 осуществляют зондирование кабельных колец напряжением повышенной частоты. Счетчик 24 фиксирует номер контролируемой группы ламп 5 и с помощью дешифратора 37 через трансформатор 8.J, блок 20.j развязки, полосовой фильтр 33.J, фазовращатель 34.J и коммутатор 35 подключает соответствующую цепь питания к первому входу измерителя 38 фазы. На второй вход измерителя 38 фазы подается опорное напряжение. Величина сдвига фаз соответствует количеству перегоревших ламп. 3 3. п. ф-лы, 6 ил.

УлраВляющчи дход 1

п

20,21

прабляющий 6)oд 2

Вы.од

.J

Фиг.З

.I/to 5 A kt,

i,i, tzWil

«h n П

Фиг. 5

Фиг. 14

г ./л. г

У W 17

Ипит

г г г

to tl у

i/«J

V

| Устройство для контроля сигнальных ламп | 1981 |

|

SU1012298A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Поддон для сифонной разливки стали | 1986 |

|

SU1379077A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1988-08-23—Публикация

1987-02-20—Подача