Влод

I

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМА ДЛЯ НЕПРЕРЫВНОГО СЛЕЖЕНИЯ ЗА ДЕЯТЕЛЬНОСТЬЮ СЕРДЦА | 2004 |

|

RU2281026C2 |

| Измеритель частоты | 1980 |

|

SU935806A1 |

| Осциллографический анализатор спектра | 1988 |

|

SU1626241A1 |

| СИСТЕМА ДИСПЕТЧЕРСКОГО КОНТРОЛЯ И УПРАВЛЕНИЯ ИНКАССАТОРСКИМИ МАШИНАМИ | 2011 |

|

RU2463665C1 |

| ИНДИКАТОРНОЕ УСТРОЙСТВО | 1991 |

|

RU2005994C1 |

| Индикаторное устройство | 1990 |

|

SU1796905A2 |

| Индикаторное устройство | 1990 |

|

SU1744473A1 |

| Индикаторное устройство | 1990 |

|

SU1796906A1 |

| АНАЛИЗАТОР ХАРАКТЕРИСТИЧЕСКОЙ ФУНКЦИИ СИГНАЛА | 2002 |

|

RU2231798C2 |

| ПАНОРАМНЫЙ ПРИЕМНИК | 1992 |

|

RU2030750C1 |

Изобретение относится к радиотехническим измерениям и предназначено для измерения частот двух сигналов, одновременно поступающих на вход измерителя. Цель изобретения - расширение функциональных возможностей устройства. Измеритель частоты содер

Чё|

Ф -InL.JT

, IР/7 I

I л

ц

ч:

НЗгИfHfE

I

15 Фиг.;

11

и ы 1

S4)

15 Фиг.;

жит линию 2 задержки, группу А,-4, из п фазовых -детекторов, группу 6,-б, из п пороговых элементов, группу 7,- 7д из полосовых фильтров и регистратор 12, Введение полосовых фильтров 1 и 5, блока 3 возведения сигналов в квадрат, групп 8,-8г, и 14,-14„, фазовых детекторов, групп 9,-9, и 13,13,

пороговых элементов, п перемножителей 10i-10 знаков постоянных напряжений, блока 11 логической обра- |ботки и п+1 отводную линию 15 задержки позволяет получить в устройстве

1

Изобретение относится к радиотехническим, измерениям и может быть использовано для измерения частот двух сигналов, одновременно поступающих на вход измерителя.

Цель изобретения - расширение фун- кционаг{ьных возможностей измерителя частоты путем обеспечения возможности измерения частот двух сигналов, одновременно поступающих на вход измерителя частоты.

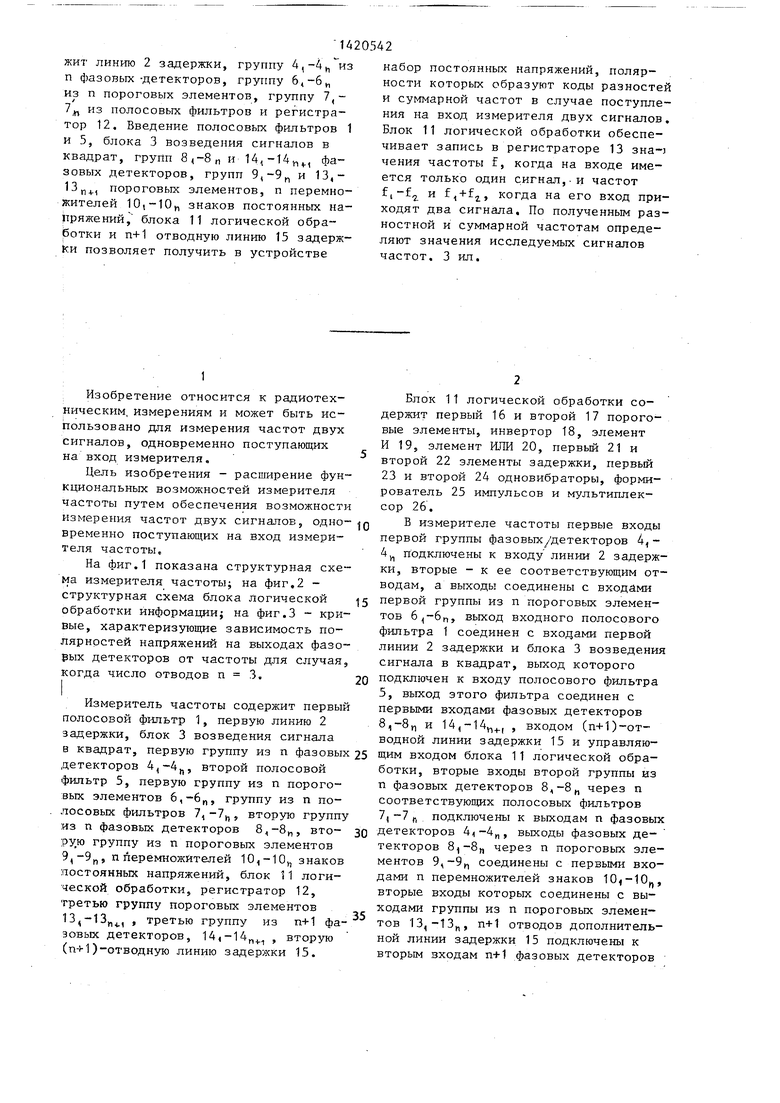

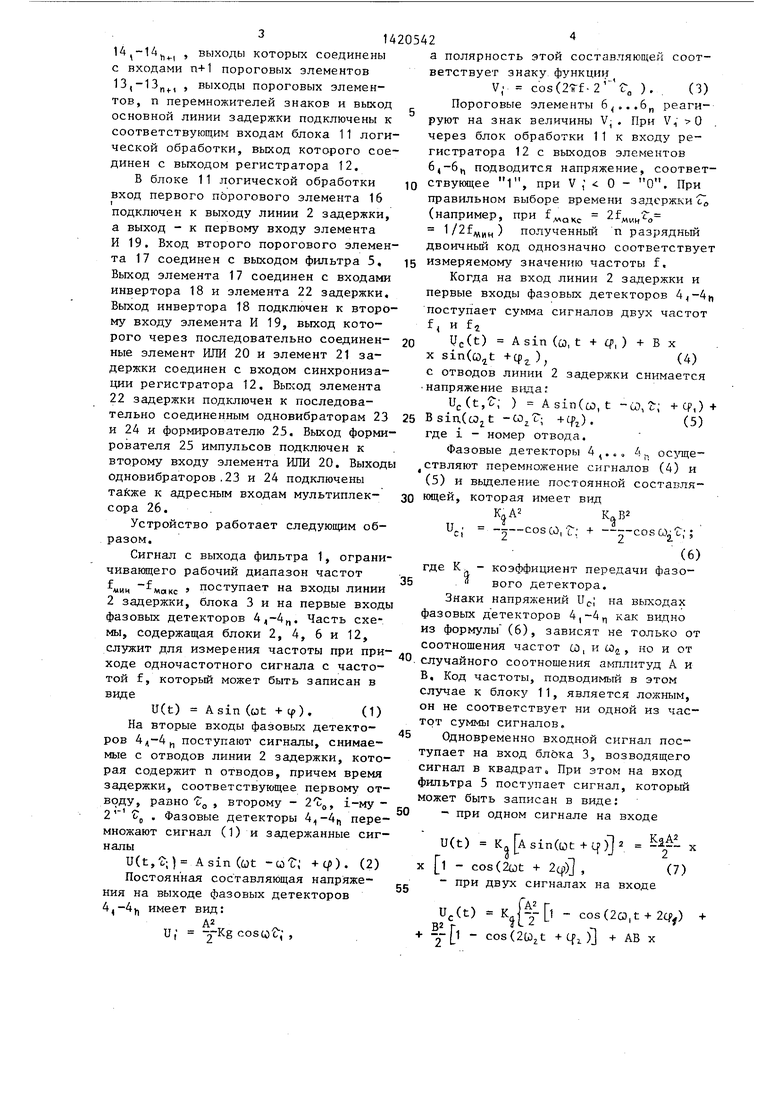

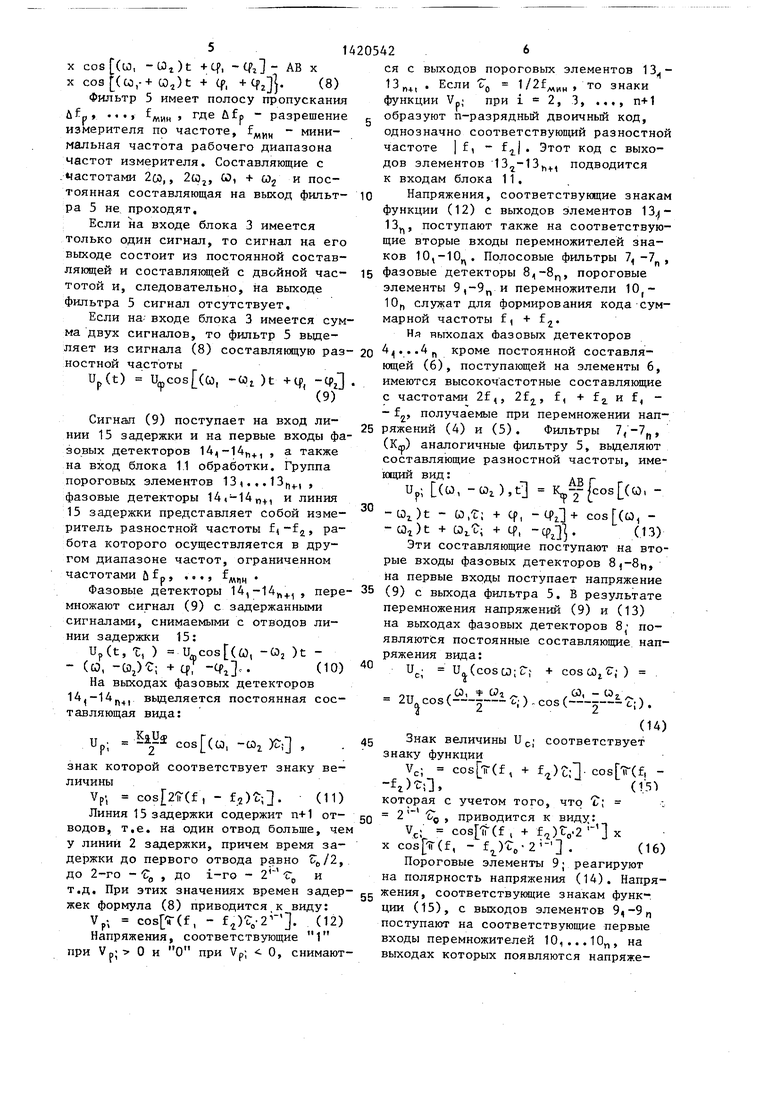

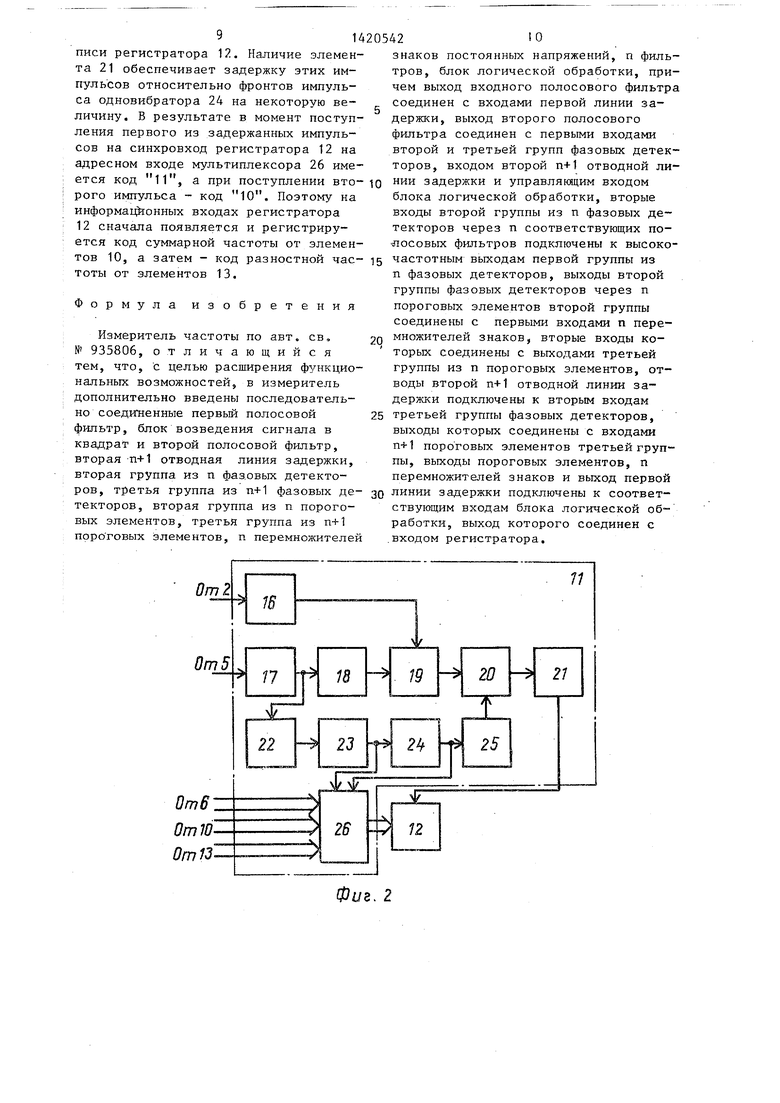

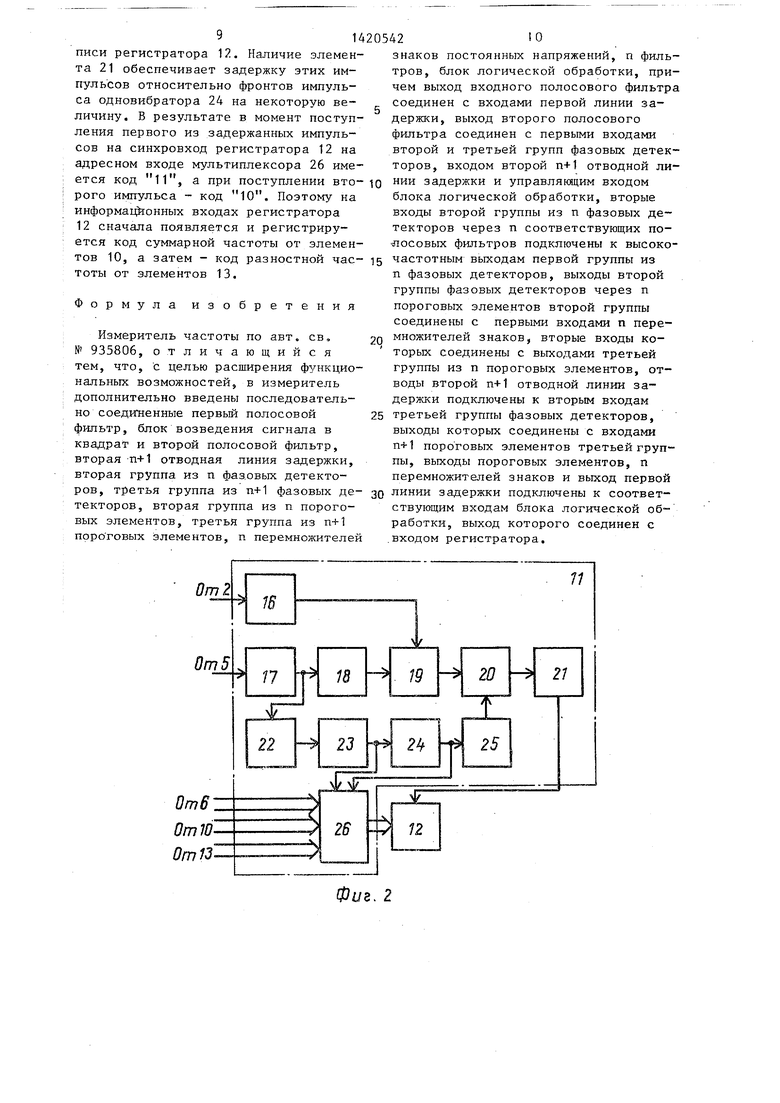

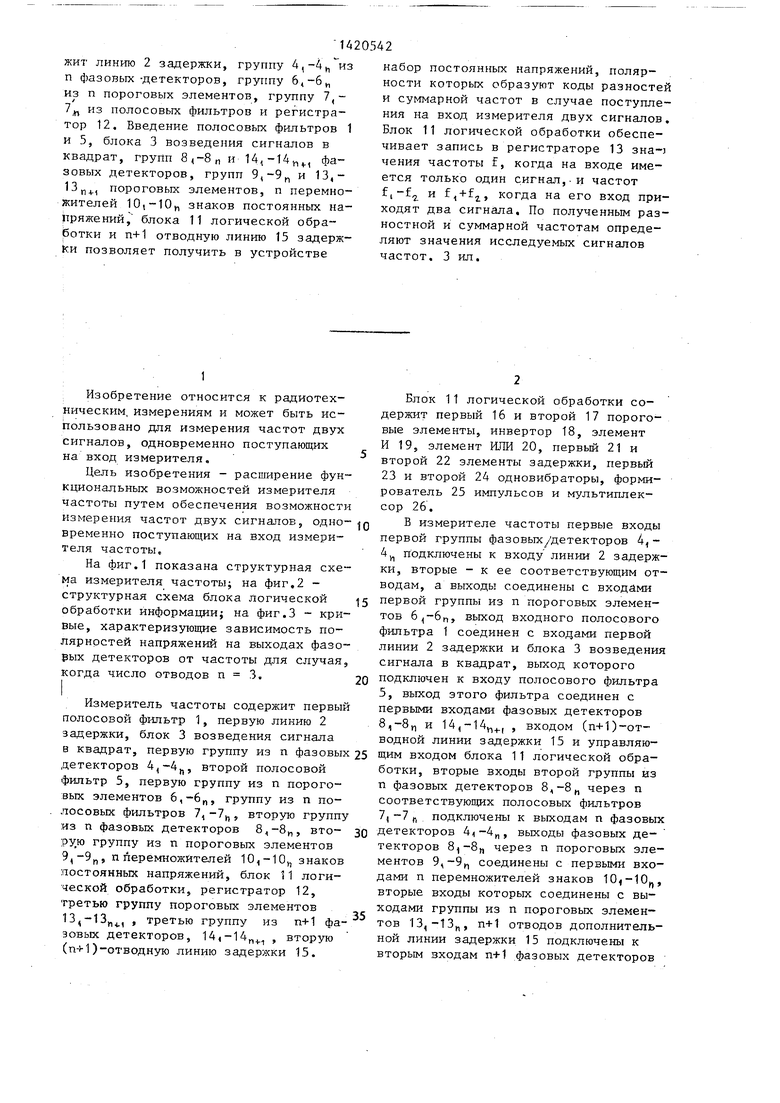

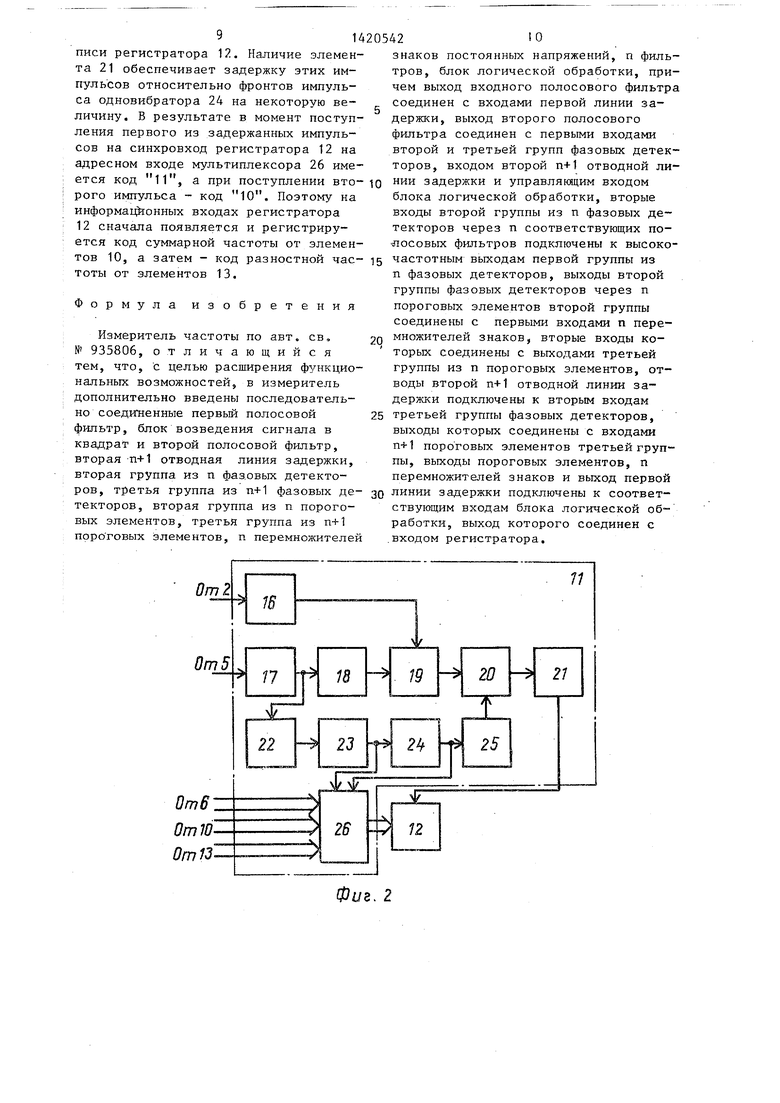

На фиг.1 показана структурная схема измерителя частоты; на фиг.2 - структурная схема блока Логической обработки информации; на фиг,3 - кривые, характеризующие зависимость полярностей напряжений на выходах фазо- рых детекторов от частоты для случая, когда число отводов п 3.

Измеритель частоты содержит первый полосовой фильтр 1, первую линию 2 задержки, блок 3 возведения сигнала в квадрат, первую группу из п фазовых детекторов 4,-4, второй полосовой фильтр 5, первую группу из п пороговых элементов 6,-6„, группу из п полосовых фильтров 7, -7у,, вторую группу из п фазовых детекторов 8,-8н, вто- ру,ю группу из п пороговых элементов 9,-9„, пперемножйтелей 10,-10„ знаков постоянных напряжений, блок 11 логической обработки, регистратор 12, третью группу пороговых элементов 13,-13„, , третью группу из п+1 фазовых детекторов, , , вторую (п-г1)-отводную линию задержки 15,

набор постоянных напряжений, полярности которых образуют коды разностей и суммарной частот в случае поступления на вход измерителя двух сигналов. Блок 11 логической обработки обеспечивает запись в регистраторе 13 зна-) чения частоты f, когда на входе имеется только один с.игнал,-и частот f,-f и f,+fj, когда на его вход приходят два сигнала. По полученным разностной и суммарной частотам определяют значения исследуемых сигналов частот, 3 ил.

Блок 11 логической обработки содержит первый 16 и второй 17 пороговые элементы, инвертор 18, элемент И 19, элемент ИЛИ 20, первьш 21 и второй 22 элементы задержки, первый 23 и второй 24 одновибраторы, формирователь 25 импульсов и мультиплексор 26,

В измерителе частоты первые входы первой группы фазовых/детекторов 4, - 4 подключены к входу линии 2 задержки, вторые - к ее соответствующим отводам, а выходы соединены с входами первой группы из п пороговых элементов 6,-бг,, выход входного полосового фильтра 1 соединен с входами первой линии 2 задержки и блока 3 возведения сигнала в квадрат, выход которого подключен к входу полосового фильтра 5, выход этого фильтра соединен с первыми входами фазовых детекторов 8,-8„ и , , входом (п+1)-отводной линии задержки 15 и управляющим входом блока 11 логической обработки, вторые входы второй группы из п фазовых детекторов 8,-8„ через п соответствующих полосовых фильтров 7j -7„ подключены к выходам п фазовых детекторов , выходы фазовых детекторов через п пороговых элементов 9,-9 соединены с первыми входами п перемножителей знаков 10i-10, вторые входы которых соединены с выходами группы из п пороговых элементов 13,-13„, п+1 отводов дополнительной линии задержки 15 подключены к вторым входам п+1 .фазовых детекторов

10

,i выходы которых соединены с входами п+1 пороговых элементов 13,-13„, , выходы пороговых элементов, п перемножителей знаков и выход основной линии задержки подключены к соответствующим входам блока 11 логической обработки, выход которого соединен с выходом регистратора 12.

В блоке 11 логической обработки вход первого порогового элемента 16 подключен к выходу линии 2 задержки, а выход - к первому входу элемента И 19. Вход второго порогового элемента 17 соединен с выходом фильтра 5, Выход элемента 17 соединен с входами инвертора 18 и элемента 22 задержки. Выход инвертора 18 подключен к второму входу элемента И 19, выход которого через последовательно соединенные элемент ИЛИ 20 и элемент 21 задержки соединен с входом синхронизации регистратора 12, Выход элемента 22 задержки подключен к последовательно соединенным одновибраторам 23 25 Вз1д(

а полярность этой составляю ветствует знаку функции

V; cos(2 rf-2 r

Пороговые элементы 6... руют на знак величины V, . П через блок обработки 11 к в гистратора 12 с выходов эле 6,-6 подводится напряжение ствующее 1, при V ; О - правильном выборе времени з (например, при f,aKc l2f.f) полученньй п р двоичный код однозначно соо 15 измеряемому значению частот

Когда на вход линии 2 за первые входы фазовых детект

поступает сумма сигналов дв f. и f,

20

и 24 и формирователю 25. Выход формирователя 25 импульсов подключен к второму входу элемента ИЛИ 20. Выходы одновибраторов .23 и 24 подключены тайже к адресным входам мультиплек- зо ющей, которая имеет вид сора 26. .К,,А2 К,,Б2

J п J.2

Uc(t) А sin (а, t + Cf, ) X sin( +ср ),

с отводов линии 2 задержки напряжение в}зда:

U(,(t, ) Asin(w, t -u

+ Ч г).

где 1 - номер отвода.

Фазовые детекторы 4., сТВляют перемножение сигнал (5) и выделение постоянной

Устройство работает следующим образом.

Сигнал с выхода фильтра 1, ограни- чиванлцего рабочий диапазон частот «ин - VOIKC поступает на входы линии 2 задержки, блока 3 и на первые входы фазовьк детекторов . Часть схемы, содержащая блоки 2, 4, 6 и 12, служит для измерения частоты при приходе одночастотного сигнала с частотой f, который может быть записан в виде

U(t) А sin (cDt + (f ). (1)

На вторые входы фазовых детекторов 4д-4 поступают сигналы, снимаемые с отводов линии 2 задержки, которая содержит п отводов, причем время задержки, соответствующее первому отводу, равно tg , второму - ,, i-му - Oj . Фазовые детекторы 4;,-4|, перемножают сигнал (1) и задержанные сигналы

U(t, 2-;) Asin (Ot -uT +c/)). (2)

Постоянная составляющая напряжения на выходе фазовых детекторов имеет вид:

А и/ cos со ; ,

,-4

Вз1д(

а полярность этой составляющей соответствует знаку функции

V; cos(2 rf-2 r ). (3)

Пороговые элементы 6...6„ реагируют на знак величины V, . При V 0 . через блок обработки 11 к входу регистратора 12 с выходов элементов 6,-6 подводится напряжение, соответствующее 1, при V ; О - О. При правильном выборе времени задержки с (например, при f,aKc l2f.f) полученньй п разрядный двоичный код однозначно соответствует измеряемому значению частоты f,

Когда на вход линии 2 задержки и первые входы фазовых детекторов (,

Вз1д(

поступает сумма сигналов двух частот f. и f,

ющей, которая имеет вид К,,А2 К,,Б2

J п J.2

Uc(t) А sin (а, t + Cf, ) + В X X sin( +ср ),(4)

с отводов линии 2 задержки снимается напряжение в}зда:

U(,(t, ) Asin(w, t -u), г; +Cf,) +

+ Ч г).(5)

где 1 - номер отвода.

Фазовые детекторы 4., 4, сТВляют перемножение сигналов (4) и (5) и выделение постоянной составля-

5

0

5

0

5

с. + -2-cosW2. . 5

(6)

где К - коэффициент передачи фазо- вого детектора.

Знаки напряжений Uc, на выходах фазовых детекторов 4,-4,, как видно из формулы (6), зависят не только от соотношения частот со, и w/j, но и от случайного соотношения амплитуд А и В, Код частоты, подводимый в этом случае к 11, является ложным, он не соответствует ни одной из частот суммы сигналов.

Одновременно входной сигнал поступает на вход блока 3, возводящего сигнал в квадрат. При этом на вход фильтра 5 поступает сигнал, который может быть записан в виде:

- при одном сигнале на входе

U(t) K.fAsin(ut+CJ) X

Г°-1

X 1 - cos(2ot + 2ф ,(7)

- при двух сигналах на входе U(t) К - cos(2o,t + R2 t-J - -,

+ - ll - cos( +q i)J + AB X

X COS (со, -Wt)t +q , (г1 AB X X COS (co,-+ C0,j)t + tf, (8)

Фильтр 5 имеет полосу пропускания ufp, .... , , где ufp - разрешение измерителя по частоте, f,j, - минимальная частота рабочего диапазона частот измерителя. Составляющие с -Частотами 2оэ,, 2cOj, СО, + Wj и постоянная составляющая на выход фильтра 5 не проходят,

Если на входе блока 3 имеется только один сигнал, то сигнал на его выходе состоит из постоянной составU205426

ся с выходов пороговых элементов

10

13„, . Если Тд , то знак функции Vpj при i 2, 3, ..«, п образуют п-разрядный двоичный код однозначно соответствушпа1й разнос частоте | f, - f). Этот код с вы дов элементов ,,., подводитс к входам блока 11,

Напряжения, соответствующие зн функции (12) с выходов элементов 13j, поступают также на соответст щие вторые входы перемножителей з ков 10,-10. Полосовые фильтры 7,

Напряжения, соответствующие знак функции (12) с выходов элементов 13 13j, поступают также на соответству щие вторые входы перемножителей зна ков 10,-10. Полосовые фильтры 7,-7

ляющей и составляющей с двойной час- 15 фазовые детекторы ,, пороговые

тотой и, следовательно, на выходе фильтра 5 сигнал отсутствует.

Если на- входе блока 3 имеется сумма двух сигналов, то фильтр 5 вьще- ляет из сигнала (8) составляющую раз- 20 ностной частоты

элементы 9,-9„ и перемножители , служат для формирования кода сум марной частоты f, + fj.

Ня выходах базовых детекторов ..4р кроме постоянной составляющей (6), поступающей на элементы 6,

Up(t) UgjCOsKCO, г )t +(f Ч г имеются высокочастотные составляющие

г/л .. О-С О i: f j 4Г „ г

(9)

Сигнал (9) поступает на вход линии 15 задержки и на первые входы фазовых детекторов ,, , а также на вход блока 1.1 обработки. Группа пороговых элементов 13 (.,.13,,, , фазовые детекторы 14(-14„, и линия 15 задержки представляет собой измеритель разностной частоты , работа которого осуществляется в другом диапазоне частот, ограниченном

30

с частотами 2f,, 2f, , f, + fj и f, --г

- f j, получаемые при перемножении нап- 25 ряжений (4) и (5). Фильтры 7,-7,, (Km) аналогичные фильтру 5, вьщеляют составляющие разностной частоты, име ющий вид:АВ Г г

Up; (О, -Qi),t (CO, -C0i)t - (О,Т; + Cf, - tpil + cos (со, - -cai)t + + Cf, -(. (13)

Эти составляющие поступают на вто рые входы фазовых детекторов 8,-8,, На первые входы поступает напряжение (9) с выхода фильтра 5, В результате перемножения напряжений (9) и (13) на выходах фазовых детекторов появляются постоянные составляющие нап

частотами U fp.

МММ

Фазовые детекторы 14,-14,,, , пере- множают сигнал (9) с задержанными сигналами, снимаемыми с отводов линии задержки 15:

Up(t, Т, ) ифсо8(и, -Oj )t - - (со, -СЗ,)(Г; +CF: -CfJ.. (10)

На выходах фазовых детекторов , выделяется постоянная составляющая вида:

U,

cos(Q, -CO, ), ,

c;), (14)

P 2

знак которой соответствует знаку ве личины

45

Знак величины соответствует

+ f)C;l- (f, 50

знаку функции

(f,

-fz).

которая с учетом того, что Т; 2 С , приводится к виду:

(f . + f)t,.

X (f, - f.,) .

Пороговые элементы 9; реагируют на полярность напряжения (14), Напря- т,д. При этих значениях времен задер- gg жения, соответствуннцие знакам функ- жек формула (8) приводится к виду: ции (15), с выходов элементов 9,-9п (f, - . (12)

Vp. (f , - 2);. (11) Линия 15 задержки содержит п+1 отводов, т,е, на один отвод больше, чем у линии 2 задержки, причем время задержки до первого отвода равно Го/2,

(ГЗ)

(16)

до 2-го - €

о

ДО

i-ro - 2

1и

Р

Напряжения, соответствующие 1 при Vp; О и О при Vp; О, снимаютпоступают на соответствующие первые входы перемножителей 101,,.10„, на выходах которых появляются напряжеся с выходов пороговых элементов

13,

13„, . Если Тд , то знаки функции Vpj при i 2, 3, ..«, п+1 образуют п-разрядный двоичный код, однозначно соответствушпа1й разностной частоте | f, - f). Этот код с выходов элементов ,,., подводится к входам блока 11,

Напряжения, соответствующие знакам функции (12) с выходов элементов 13j, поступают также на соответствующие вторые входы перемножителей знаков 10,-10. Полосовые фильтры 7,-7, ,

фазовые детекторы ,, пороговые

фазовые детекторы ,, пороговые

элементы 9,-9„ и перемножители , служат для формирования кода суммарной частоты f, + fj.

Ня выходах базовых детекторов ..4р кроме постоянной составляющей (6), поступающей на элементы 6,

имеются высокочастотные составляющие

имеются высокочастотные составляющие

.. О-С О i: f j 4Г „ г

0

5

с частотами 2f,, 2f, , f, + fj и f, --г

- f j, получаемые при перемножении нап- 5 ряжений (4) и (5). Фильтры 7,-7,, (Km) аналогичные фильтру 5, вьщеляют составляющие разностной частоты, имеющий вид:АВ Г г

Up; (О, -Qi),t (CO, -C0i)t - (О,Т; + Cf, - tpil + cos (со, - -cai)t + + Cf, -(. (13)

Эти составляющие поступают на вторые входы фазовых детекторов 8,-8,, На первые входы поступает напряжение (9) с выхода фильтра 5, В результате перемножения напряжений (9) и (13) на выходах фазовых детекторов появляются постоянные составляющие нап

ряжения вида:

и

и„(со8СО;г ;

+ cos COj , )

2U cos( d

G3t

; ) - cos (

CO, - COj

c;), (14)

45

Знак величины соответствует

+ f)C;l- (f, (ГЗ)

(16)

Пороговые элементы 9; реагируют на полярность напряжения (14), Напря жения, соответствуннцие знакам функ- ции (15), с выходов элементов 9,-9п

поступают на соответствующие первые входы перемножителей 101,,.10„, на выходах которых появляются напряжения,

71420542

соответствующие знакам произве10

В исходном состоянии при отсутствии сигналоэ на входе измерителя на выходах пороговых элементов 16 и 17 имеется- низкий потенциьш. Е результате на вход синхронизации регистратора 12 никаких сигналов не пос тупает, поэтому в нега не записывается и информация.

Если на измеритель поступает одиночный сигнал, длительность которого превышает время задержки линии 2 за держки, то срабатывает пороговый элемент 16 и на его выходе появляется высокий потенциал, который через открытый элемент И 19, элемент ИЛИ 20 и элемент 21 задержки поступает на вход синхронизации регистратора 12 и разрешает запись кода частоты сигнала по шине от элементов б. Выбор информационной пины мультиплексором 26 производится в соответствии с кодом адреса, формируемым одновибраторами 23 и 24. При нагхичии на входе нзме- рителя одного сигнала значание кода адреса равно 00,, так KSK одновибра- торы 23 и 24 находятся в исходном (нулевом) состоянии„

Если на вход измеритепя построгаю + fj получаются в виде двоичных кодов, зо Я сигнала одновременно, то под воз- однозначно соответствующих номеру уча- действием сигнала разностной частоты.

дения функций (12) и (16), Знак произведения Vp; Vj.; определяется знаком множителя

cos(f, + f) , (17) поскольку . ,

( , - f.j) 2 О,

Соответствующий формуле (17) код частоты f , + f2, формируемый на выходе перемножИт елей ,, подводится к входам блока 11 обработки,

Для выяснения принципа работы устройства на фиг.З изображены нормированные по амплитуде кривые зависи- ,15 мости напряжений от измеряемых частот при использовании трех отводов от линии 2 задержки. Синусоидальные кривые на фиг.З условно изображены отрезками прямых линий.

Расчет кривых, изображенных на фиг.За, б, в, проводился соответственно по формулам (1), (11) и (17), При этом диапазон измеряемых частот выбран так, что 2, а время задержки Г, до первого отвода в линии задержки 2 равно .

Значения частот f,, f, - fj, f,

20

25

стков, на которые диапазон измеряемых частот- ( при измерении частоты f одиночного сигнала, О - мин измерении разности частот двух сигналов и f MoiKc 2f д,ц,с при измерении суммы частот двух сигналов) делится точками пересечения кривых

и V.

от часзависимостей V,-, Vp; тоты.

Указанные коды частот поступают на вход блока 11 обработки совместно с сигналом с выхода фильтра 5, существующего, когда в полосу частот измерителя поступают два сигнала с разными частотами, и отсутствующего, если сигнал только один.

Блок 11 логической обработки предназначен для совместной обработки поступакшщх кодированных значений частот с целью обеспечения записи в регистратор 12 значения частоты f, когда на входе измерителя имеется только один сигнал, и частот f, + f и fj - f, когда на его вход приходя два сигнала.

Блок 11 работает следующим образом.

10

15

20

25

35

постлгпающего с выхода фильтра ., c.ja- батьтает пороговый элемент 17, и высокий потенциал напряжения с его выхода инвертируется элементом 18 и перекрывает логический элемент И 19 для сигнала с выхода порогового элемента 16. Одновременно сигнал с выхода элемента 17, задержанный элсмен40

том 22 на время Т, макс С

ЗЛлт.

Д злз-г 5 л315 время задержки элементов 2 и 15 соответственно, запускает первый одновибра- тор 23. Длительность импульса на его выходе равна времени, необходимому для записи двух значений кода частоты в регистратор,

По переднему фронту иьшульса одно- вибратора 23 запускается одновибра- тор 24, который также генерирует одиночный положительный импульс длительностью, равной половине длительности импульса одновибратора 23, Формирователь 25 обеспечивает формирование по переднему и заднему фронтам импульса , одновибратора 24 двух коротких положительных импульсов, которые через элемент ИЛИ 20 и элемент 21 задержки поступают на вход синхронизации за0

5

9

писи регистратора 12. Наличие элемента 21 обеспечивает задержку этих импульсов относительно фронтов импульса одновибратора 24 на некоторую величину. В результате в момент поступления первого из задержанных импульсов на синхровход регистратора 12 на адресном входе мультиплексора 26 имеется код 11, а при поступлении вто- рого импульса - код 10. Поэтому на информационных входах регистратора 12 сначала появляется и регистрируется код суммарной частоты от элемен14

тов 10, а затем - код разностной час- 15 частотным выходам первой группы из тоты от элементов 13.

п фазовых детекторов, выходы второй группы фазовых детекторов через п пороговых элементов второй группы соединены с первыми входами п пере множителей знаков, вторые входы ко- торых соединены с выходами третьей группы из п пороговых элементов, от воды второй п+1 отводной линии задержки подключены к вторым входам 25 третьей группы фазовых детекторов, выходы которых соединены с входами n-J-1 пороговых элементов третьей гру пы, выходы пороговых элементов, п перемножителей знаков и выход перво

Формула изобретения

Измеритель частоты по авт. ев, № 935806, отличающийся тем, что, с целью расширения функциональных возможностей, в измеритель дополнительно введены последовательно соединенные первый полосовой фнпьтр, блок возведения сигнала в квадрат и второй полосовой фильтр, вторая -n+l отводная линия задержки, вторая группа из п фаз.овых детекторов, третья группа из п+1 фазовых де- зо линии задержки подключены к соответ- текторов, вторая группа из п порого- ствующим входам блока логической об- вых элементов, третья группа из п+1 работки, выход которого соединен с поро говых элементов, п перемножителей .входом регистратора.

Фиг. 2

-JQ20542 О

знаков постоянных напряжений, п фильтров, блок логической обработки, причем выход входного полосового фильтра соединен с входами первой линии задержки, выход второго полосового фильтра соединен с первыми входами второй и третьей групп фазовых детекторов, входом второй п+1 отводной линии задержки и управлякщим входом блока логической обработки, вторые входы второй группы из п фазовых детекторов через п соответствующих полосовых фильтров подключены к высокочастотным выходам первой группы из

п фазовых детекторов, выходы второй группы фазовых детекторов через п пороговых элементов второй группы соединены с первыми входами п перемножителей знаков, вторые входы ко- торых соединены с выходами третьей группы из п пороговых элементов, отводы второй п+1 отводной линии задержки подключены к вторым входам третьей группы фазовых детекторов, выходы которых соединены с входами n-J-1 пороговых элементов третьей группы, выходы пороговых элементов, п перемножителей знаков и выход первой

пин

J 2 3 ft 5 S 7 %S

2T -Г-Г

паке

fer/ - /

,

fhOKC

Авторы

Даты

1988-08-30—Публикация

1986-12-10—Подача