4ib

со

О1

Изобретение относится к импульсной технике, в частности к импульсньп1 измерительным устройствам, работающим со статистически распределенными входными сигналами (например, амплитудным спектрометрическим измерительным -трактом), и может быть использовано в ядерном приборостроении, в многоканальных амплитудных анализато- pax импульсов.

Целью изобретения является повышение точности.

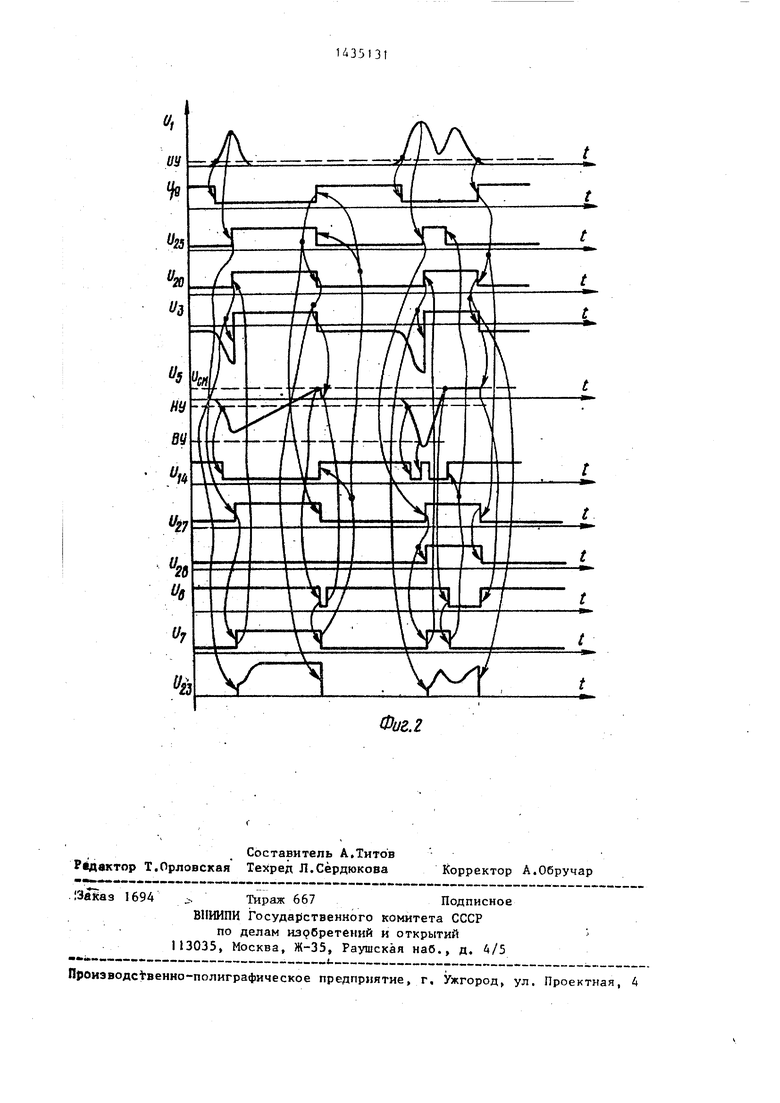

На фиг.1 приведена функциональная Схема устройства; на фиг,2 - временные диаграммы работы преобразователя.

Преобразователь (фиг,1) содержит . входную шину 1, токоограничивающий элемент 2, выполненньп } на резисторе, дифференциальный усилитель 3, выпрямительный элемент 4, повторитель 5 напряжения, дискриминатор 6 временного интервала, элемент И 7, преобразователь 8 время-код блок 9 ключей, выходные шины 10, накопительный элемент 11 , вь.толненный tsa конденсаторе, генератор 12 начального тока, генератор 13 разрядного тока, дискриминатор 1А уровней сигнала 9 третий вход 15 блока 16 выбора уровней сигнала, второй вход 17 блока 16, дискриминатор 18 исходного уровня сигнала, первый вход 19 элемента 20 управления, выполненного на RS-триггере, управляемый генератор 21 тока, инвертирующий вход 22 дифференциального усилителя, вьшрямительный эл гмент 23, выполненный на диоде, токоограничиватощий элемент 24, выполненный на резисторе, дискриминатор 2 максимального уровн сигнала, першй вход 26 блока 16, первый и второй выходы 27, 28 блока 16, второй вход 29 управления генера тора 13, вход 30 6лок1-фовки преобразователя время-код, первый вход 31 управления генератора 13, второй выход 32 преобразователя 8, второй Bxcto 33 элемента 20.

Преобразователь 8 время-код выполнен на генераторе ЗА импульсон,блоке 35 синхронизации, элементе И -36, счетчике 37 импульсов.

::; Блок 16 выполнен на двух-В-тригге

;; рах 38, 39,i

На временной Диаграмме (фиг,2) обозначено U - напряжение на входной шине .1; U,9,Ujj, Ut,U т - напряжения на выходах соот-

ветствующих блокоя; U - ток через

rv «-чjt 3

диод 2J.

Преобразователь работает следующим образом.

При отсутствии сигнала на входной шине 1 током генератора 12 петля обратной связи дифференциального усилителя 3 поддерживается замкнутой через выпрямительный элемент А (например, диод, один из переходов транзистора), повторитель 5 (истоковый или эмиттер- ный повторитель, а также другие устройства, имеющие высокое входное и низкое выходное сопротивления) и резистор 24. Значение начального тока выбирается из условия

нич

Ы.

(1)

О

0

5

5

где Uyj „яке максимальная амплитуда шумов в аналоговом тракте I

f р - граничная частота усиления дифференциального . усилителя 3 или максимальная частота спектра шумов;

С --емкость конденсатора 11. Таким образом создаются постоянные начальные условия для полезного сигнала и поддерживается линейный режим работы дифференциального усилителя 3 при отсутствии сигнала. Благодаря этому время заряда конденсатора 11 определяется только длительностью фронта входного импульса и не зависит от времени выхода дифференциального усилителя 3 из насыщения и времени нарастания его выходного сигнала до 1Омента замыкания петли общей обрат - ной связи.

Входной сигнал через дифференциальный усилитель 3 и выпрямительный элемент 4 заряжает конденсатор 11, Обратная связь при этом замыкается по той же петле, что и при начальных условиях, т,е, через резистор 24. Инвертирующее включение дифференциального усилителя 3 позволяет устранить крмпоненту ди(ференциальной нелинейности, связанную с конечным ослаблением входного импульсного синфазного сигнала дифференциальным усилителем 3.

После прохождения верши1кы сигйала выпрямительный элемент 4 закрывается и размыкается петля обратной связи через повторитель 5 и резистор 24,

остью токов Ucr

рс

И

SV

р ос

14351 , гяе

(2)

11, - амплитуда входного сигнала; 5 ос сопротивление резистора 24;

Вх

УС. R

to

15

20

25

Uc, -напряжение входного сигнала;

R - сопротивление резистора 2, замыкается петля местной обратной спязи дифференциального усилителя 3 через диод 23, подцерживакядая линейный режим работы дифференциального усилителя 3. Срабатывает дискриминатор 25. Сигнал с его выхода поступает на блок 16. Блок 16 в зависимости от состояния дискриминатора 14 на входе 15 устанавливает сигнал на выходе 27, свидетельствующий о наличии сигнала на входе устройства, и, если входной сигнал не подошел по условиям отбора (был ниже нижнего порогового уропня или выше верхнего порогового уровня), устанавливает сигнал на выходе 28 .

Сигнал с выхода 27 блока 16 через элемент И 7 переводит устройство в режим преобра зования. Сигнал, с выхода элемента И 7 поступает на стробирую- щие входы дискриминаторов 25, 18, 14 и поддерживает их на все время преобразования в состоянии, соответствуюг щем наличию входного сигнала, удовлетворяющего условиям отбора. Таким образом исключается возможность их

срабатьгоания во время преобразования и исключаются соответствукяцие помехи увеличивающие дифференциальную нелинейность устройства. Кроме того,

Сигнал с выхода элемента И 7 поступает на вход 33 элемента 20, который срабатывает н включает своим выходным сигналом управляемый reliepaTOp

21, Выходной ток управляемого генератора 21 поддерживает замкнутой местную обратную связь дифференциального усилителя 3 через дкод 23.

31шчение тока 1 управляемого генератора 21 выбирается из условия

и

IfA

где Uj ддацс максимально возможная амплитуда сигнала на входе устройства Таким образом, изменение сигнала на входе устройства или, пoctyплeииe

35

40

50

ег.млке. R

55

5

to

15

20

25

5

0

0

5

3t.4

нового входного сигнала во время преобразования приводит только к иэмеке- нию тока через диод 23 не влияет на процесс разряда конденсатора 11, изолированного от выхода дифференциального усилителя 3 закрытым выпрямительным элементом 4, Выход управляемого генератора 21 и катод диода 23, подключенные к инвертирующему входу 22 дифференциатьного усилителя, на процесс заряда влияния .не оказывают и не вносят нелинейности.

Включение управляемого генератора 21 и диода 23 вместе с инвертирующим включ ением дифференциального ус1Шите- ля 3 позволяет исключить из аналогового тракта линейно-пропускающее устройстио, вносящее значительную дифференциальную нелинейность, а также исключает нелинейный режим работы дифференциального усплителл 3 во вре мя преобразования, вызывающ й{ эввиси мость его коэффициента передачи от предыстории (импульсы стабильной амп литуды дают различньй заряд иа конденсаторе 11 в зависимости от амплй- туды и Ьремени поступления предьщущв го статистического импульса (из-за изменения температуры транзисторов дифференциальной ьходной пары, что эквивалентно увеличению собственных шумов преобразования и его дифференциальной нелинейности.

Орновременно с этим сигнал с выхода элемента И 7 поступает на вход блока 35 преобразователя 8, где этот сигнал фазируется с частотой генератора 34 и разрешает прохождение импульсов генератора 34 через элемент 36 на вход счетчика 37.

Сигнал с выхода элемента 7 поступает также на вход блокировки блока 9 При этсж входы ключей блока 9 переводятся в высоко11мпедансное состояние и не вызывают асимметрии триг- геров счетчика 37 во время преоора- зования время-код, а также срабатывания внутренних несимметричных элементов ключей.

Сигнал с выхода 32 преобразователя 8 включает генератор разр|здыого тока 13, который начинает линейный разряд кондеясаторА If. Линейный разряд продолжается до тех пор, пока ; напряжение иа выходе повторителя 5 не станет равно напряжению U, подаваемому на второй вход дискримняа- тора б. Обычно на этот вход подается

10

15

опредс. постоянное. 1 а 1ряжеН11е Ш1И оп заземляется, В момент равенства напряжения на выходе повторителя 5 и U;, срабатывает дискриминатор 6, снглап с выхода которого полается на первый вход элемента 7 и прекращает преобразование. Таким образом, код счетчика 37 оказывается пропорцио- Нальньм амплитуде входного сигнала И через блок 9 поступает на выходные и|ины 10, разблокируются дискриминаторы 25, 18 и 14, выключается генератор 13 и ;нимается сигнал с входа 33 элемента 20. Если в этот момент на входе устройства присутствует сигнал, дискриминатор 18 не поменяет своего состояния, т.е, сигнал на его выходе (Снимается только при отсутствии сигналов, на входе устройства.

Таким образом, исключается возмож-г, Ность деблокирования входа устройства за время действия входного сигнала И осуществляется режекция наложенных (т.е. пришедших во время действия обрабатываемого сигнала или во время Преобразования) входных сигналов. Снятие сигнала с выхода дискриминатора 18 через элемент 20 выключает уп- |||авляемый генератор тока 21 , вход устройства деблокируется, и оно при.водится в -исходное состояние. Если импульс не подошел по условиям отбора, преобразование происходит (Диалогичным -образом, но сигнал с вы- 28 блока 16 подается на вход 29 35 генератора 13, а также блокирует про-, хождение импульсов с генератора 34 через элемент 36 на вход cчeтJ икa 37. азряд конденсатора 11 производится

435131 .6

ограничивающий 3j;( NfenT, выполпениыГ на резисторе, соединен с инвертирую- щим входом дифференциального усилителя и непосредственно - с информационным входом дискриминатора уровней сигнала, накопительный элемент, выполненный на конденсаторе, первая обкладка которого соединена с выходами первого выпрямительного элемента генератора разрядного тока, а вторая является общей шиной, первый вход управления генератора разрядного тока соединен со вторым выходом преобразователя время-код, дискриминаторы максимального уровня сигнала и исходного уровня сигнала, информационные входы которых объединены и являются входной ип1ной, блок выбора уровней сигнала, первьй, второй и третий входы которого соединены соответственно с выходами дискриминаторов максимального уровня сигнала, исходного уровня сигнала и уровней сигнала, первый йыход блока выбора у{)овней .сигнала соединен со вторьм входом элемента И, второй выход соединен со входом блокировки преобразователя время-код и вторым входом управления генератора разрядного Тока, элемент управления, выполненный на RS-триггере, первый вход которого соединен с выходом дискриминатора исходного уровня, -второй вход - с выходом элемента И, о т - ли чающийся тем, что, с целью повышения точно,сти путем унень- шения дифференциальной нелинейности, в него введены управляемый генератор тока, генератор начального тока, второй токоограничивающий элемент, вы20

2S

при этом увеличенным током генератора О полненный на резисторе, второй выпря

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1984 |

|

SU1234972A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1970 |

|

SU287422A1 |

| Емкостно-электронный преобразователь перемещения | 1989 |

|

SU1721434A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ СРЕДНЕКВАДРАТИЧЕСКОГО ЗНАЧЕНИЯ НАПРЯЖЕНИЯ | 2000 |

|

RU2198410C2 |

| Преобразователь время-амплитуда | 1976 |

|

SU657599A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU780048A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1358094A1 |

| Восстановитель постоянной составляющей импульсных сигналов напряжения | 1982 |

|

SU1069148A1 |

| Время-импульсный амплитудный преобразователь | 1978 |

|

SU752796A1 |

| Устройство считывания информации для доменной памяти | 1990 |

|

SU1751813A1 |

Изобретение относится к импульсной технике и может быть использовано в ядерном приборостроении, в многоканальных амплитудных анализаторах им-- пульсов. Изобретение позволяет повысить точность. Это достигается-тем, что в преобразователь; содержащий дифференциальный усилитель 3, выпрямительный элемент 4, повторитель 5 напряжения, дискриминаторы 14,18,25 уровня сигнала, исходного уровня сйг- нала, максимального уровня сигнала, .блок 16 выбора уровней сигнала, элемент И 7, элемент 20 управления, преобразователь 8 время-код, блок 9 клю чей, токоограничивающий элемент 24, выполненный на резисторе, накопительный элемент 1t, выполненный н конденсаторе, введены второй токоограничи- вакяций элемент 2, выполненный на резисторе, второй выпрямительный мент, выполненный на диоде генератор 12 начального тока управляемый генератор 21 тока. 2 з.п. ф-лы, 2 ил. сл с

13 за меньшее время. Фармула изобретения

О

5

мительный элемент, выполнекньй на диоде, анод которого соединен с выходом дифференциального усилителя, а катод объединен с первым выводом рого резистора, инвертирующим входом дифференциального усилителя и соединен с выходом управляемого генератора тока, неиивертирующий вход дифференциального усилителя является общей шиной, второй вывод второго резистора является входной юиной, причем вход управления управляемого гене ратора тока соединен с выходом элемента управления, вход управления генератора начального тока соединен с выходом дискриминатора исходного уровня сигнала, а выход соединен с входом повторителя напряжения, стробирующие входы дискриминаторов максимального

уровня сигнала, исходного уровня сигнала и уровней сигнала объединены ,со вторым входом элемента управления и входом блокировки блока ключей,

при этом второй вход дискриминатора временного интерсала является шиной напряжения смещения.

2, Преобразователь по п.1, о т - личающийся тем, что блок выбора уровней сигнала выполнен на двух D-триггерах, D-вход первого D-триггера является третьим входом блока, R-вход объединен с 8 входом второго D-триггера и является вторым входом €лока, первым входом которого является С-вход второго р-триггера, D-вход которого является общей шиной выход второго D-TTpHrrepa соединен с входом первого D-триггера и является первым выходом блока, вторым выходом

тд

Biiiwe

которого является выход первого D- триггера,

3, Преобразователь по п.1, о т - л и ч а ю щ и Гт с я .тем, что преоб- разователь время-код выполнен -на генераторе импульсов, блоке синхронизации, счетчике импульсов и элементе И первый вход которого является входом блокировки преобразователя время-код второй вход соединен с выходом блока синхронизации и является вторым выходом преобразователя время-код, третий вход элемента И объединен с первым входом блока синхронизации и соединен с выходом генератора импульсов, второй вход блока синхронизации явПЯ- ется информационным входом преобразователя время-код, первыми выходами которого являются выходы счетчика импульсов, вход которого соединен с выходом элемента И.

9

Фиг.2

| Глушковский М.Е | |||

| Быстродействующие амплитудные анализаторы в современной ядерной физике и технике | |||

| М.:, Энергоатомиздат, 1986, с.64-75, рис | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Анализаторы SERIES ,1:0 и 20, блок АДС | |||

| Каталог фирмы Canberra | |||

| USA,Edi - .tion SiXt -1986. | |||

Авторы

Даты

1990-04-30—Публикация

1986-11-15—Подача