4 4

Изобретение относится к неразрушающим методам контроля и может быть использовано при исследовании физических свойств различных изделий.

Целью изобретения является повьше- ние достоверности измерений за счет исключения потери информации в на- чальньй момент затухания колебаний.

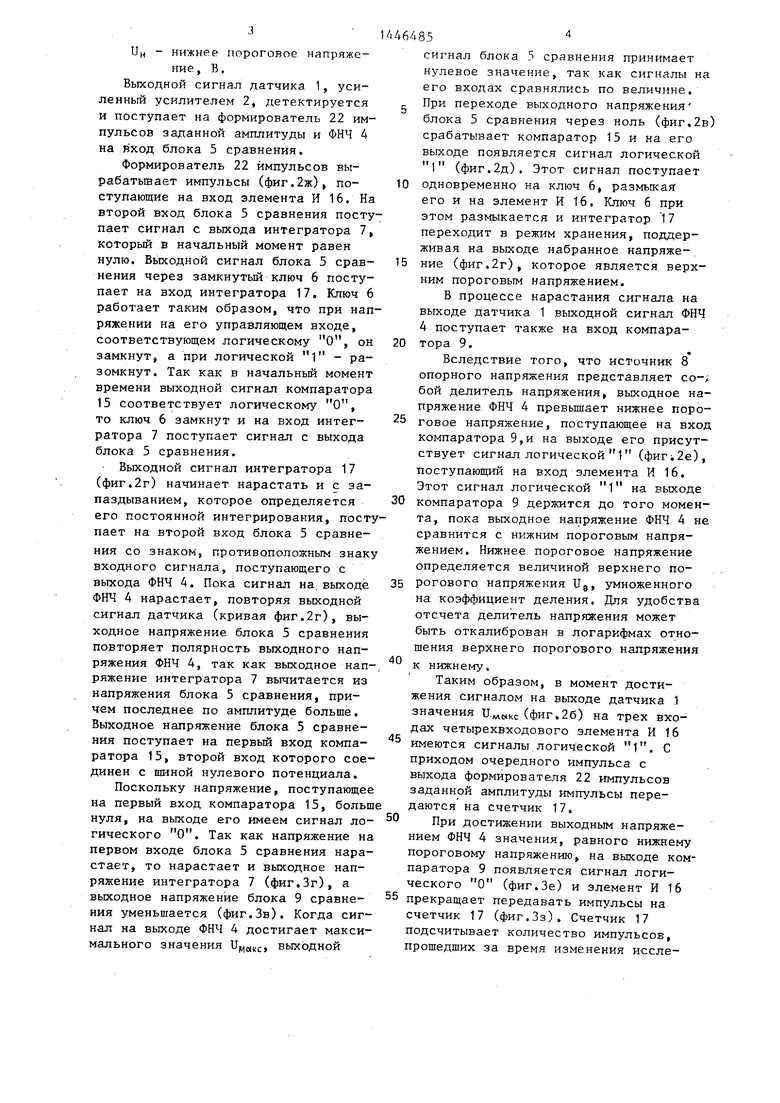

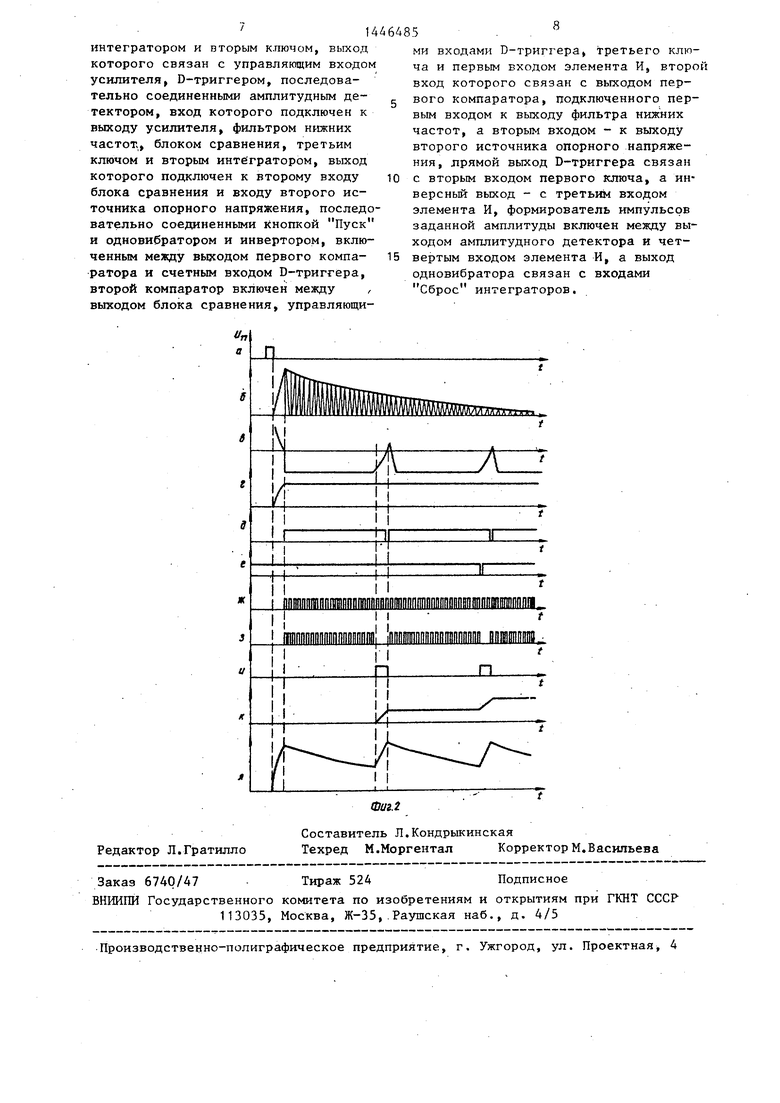

На фиг.1 представлена блок-схема устройства для измерения логарифмического декремента затухания; на фиг.2 - временные диаграммы, поясняющие работу устройства.

Устройство содержит последовательно соединенные датчик 1, усилитель 2, амплитудный детектор 3, фильтр 4 нижних частот (ФНЧ), блок 5 сравнения, ключ 6, интегратор 7, выход которого связан с вторым входом бло- ка 5 сравнения, источник 8 опорного . напряжения, компаратор 9, инвертор 10 D-триггер 11, ключ 12, интегратор 13 и ключ 14, выход которого подключен к управляющему входу уси- лителя 2,

Устройство содержит последовательно соединенные компаратор 15, первый вход которого связан с выходом блока 5 сравнения, а второй вход зазем- лен, элемент И 16, счетчик 17 и регистратор 18, последовательно соединенные кнопку 19 Пуск и одновиб- ратор 20, выходы которого подключены к входам Сброс интеграторов 7 и 13 источник 21 опорного напряжения, подключенный к второму входу ключа 12, и формирователь 22 импульсов заданной амплитуды, включенньй между выходом амплитудного детектора 3 и одним из входов элемента И 16, подключенньш другим входом к инверсному выходу D-триггера. Выход компаратора 9 также подключен к входу элемента И 16. Выход компаратора 15 подключен к уп- 5)авляющим входам D-триггера 11 и ключа 6. Выход фильтра 4 нижних частот связан с вторым входом компаратора 9.

Временные диаграммы ( фиг.2) характёризуют:

а -напряжение запуска устройства в работу (выходное напряжение одно- вибратора) J

б - выходное напряжение датчика 1i

в - выходное напряжение блока 5 сравнения;

г - выходное напряжение интеграто- Ра 7;

д - выходное напряжение компаратора 9;

е - выходное напряжение компаратора -15;

ж - выходное напряжение формирователя 22 импульсов заданной амплитуды

3 - выходное напряжение элемента И 16j

и - выходное напряжение D-триггера 1 1 J

к - выходное напряжение интегратора 13}

л - выходное напряжение фильтра 4 нижних частот.

Устройство работает следующим образом.

В начальный момент подается сигнал Пуск от кнопки 19 на одновиб- ратор 20, который устанавливает в ноль интеграторы 7 и 13. При этом коэффициент усиления усилителя 2 минимален. По заднему фронту запускающего импульса (фиг,2а) осуществляетс однократное ударное возбуждение исследуемого образца, приводящее к возникновению его механических колебаний, которые с помощью датчика 1 преобразуются в электрический сигнал. Таким образом на выходе датчика 1 формируется электрический сигнал, соответствующий этим колебаниями и характеризующийся кривой, приведенной на фиг,26 Возрастающая часть этой кривой характеризует процесс нарастания колебаний образца от О до максимальной амплитуды /йякс После достижения максимальной амплитуды и Али «колебаний (фиг,26) начинается процесс затухания колебаний от ид/101ксДО О, который несет в себе полезную информацию о свойствах образца, таких, например, как наличие дефектов в композиционном материале.

Для получения такой информации необходимо определить логарифмический декремент затухания колебаний, который определяется вьфажением

rf i in н .

N

и,

(1)

N - количество колебаний в течение времени, за которое амплитуда колебаний изменится от Ug до , Uj - верхнее пороговое напряжение, В,

3

и„ нижнее пороговое напряжение , В,

Выходной сигнал датчика 1, усиленный усилителем 2, детектируется и поступает на формирователь 22 импульсов заданной амплитуды и ФНЧ 4 на вход блока 5 сравнения.

Формирователь 22 импульсов вы- рабатьшает импульсы (фиг.2ж), поступающие на вход элемента И 16. На второй вход блока 5 сравнения поступает сигнал с выхода интегратора 7, который в начальный момент равен нулю. Вькодной сигнал блока 5 сравнения через замкнутый ключ 6 поступает на вход интегратора 17. Ключ 6 работает таким образом, что при напряжении на его управляющем входе, соответствующем логическому О, он замкнут, а при логической 1 - разомкнут. Так как в начальньй момент времени выходной сигнал компаратора 15 соответствует логическому О, то ключ 6 замкнут и на вход интегратора 7 поступает сигнал с выхода блока 5 сравнения.

Выходной сигнал интегратора 17 (фиг.2г) начинает нарастать и с запаздыванием, которое определяется его постоянной интегрирования, поступает на второй вход блока 5 сравнения со знаком, противоположным знаку входного сигнала, поступающего с выхода ФНЧ 4. Пока сигнал на. выходе ФНЧ 4 нарастает, повторяя выходной сигнал датчика (кривая фиг.2г), выходное напряжение блока 5 сравнения повторяет полярность выходного напряжения ФНЧ 4, так как выходное напряжение интегратора 7 вычитается из напряжения блока 5 сравнения, причем последнее по амплитуде больше. Выходное напряжение блока 5 сравнения поступает на первый вход компаратора 15, второй вход которого соединен с шиной нулевого потенциала.

Поскольку напряжение, поступающее на первый вход компаратора 15, больш нуля, на выходе его имеем сигнал логического О. Так как напряжение на первом входе блока 5 сравнения нарастает, то нарастает и выходное напряжение интегратора 7 (фиг.Зг), а выходное напряжение блока 9 сравнения уменьшается (фиг.Зв). Когда сигнал на выходе ФНЧ 4 достигает максимального значения выходной

1446485

сигнал блока 5 сравнения принимает

5

нулевое значение, так как сигналы на его входах сравнялись по величине. (- При переходе выходного напряжения блока 5 сравнения через ноль (фйг.2в) срабатывает компаратор 15 и на его выходе появляется сигнал логической 1 (фиг.2д). Этот сигнал поступает 0 одновременно на ключ 6, размыкая его и на элемент И 16. Ключ 6 при этом размыкается и интегратор 17 переходит в режим хранения, поддерживая на выходе набранное напряже- 5 ние (фиг.2г), которое является верхним пороговым напряжением.

В процессе нарастания сигнала на выходе датчика 1 выходной сигнал ФНЧ 4 поступает также на вход компара- 0 тора 9.

Вследствие того, что источник 8 опорного напряжения представляет со-/ бой делитель напряжения, выходное напряжение ФНЧ 4 превьшает нижнее пороговое напряжение, поступающее на вход компаратора 9,и на выходе его присутствует сигнал логической 1 (фиг;2е), поступаюш ш на вход элемента И 16. Этот сигнал логической 1 на выходе 0 компаратора 9 держится до того момента, пока выходное напряжение ФНЧ 4 не сравнится с нижним пороговым напряжением. Нижнее пороговое напряжение определяется величиной верхнего по- 5 рогового напряжения Ug, умноженного на коэффициент деления. Для удобства отсчета делитель напряжения может быть откалиброван в логарифмах отношения верхнего порогового напряжения к нижнему.

Таким образом, в момент достижения сигналом на выходе датчика .1 значения П.ыкс (фиг.2б) на трех входах четьфехвходового элемента И 16 имеются сигналы логической 1. С приходом очередного импульса с выхода формирователя 22 импульсов заданной амплитуды импульсы передаются на счетчик 17.

При достижении выходным напряжением ФНЧ 4 значения, равного нижнему пороговому напряжению, на выходе компаратора 9 появляется сигнал логического О (фиг.Зе) и элемент И 16 прекращает передавать импульсы на счетчик 17 (фиг.Зз). Счетчик 17 подсчитывает количество импульсов, прошедших за время изменения иссле0

5

0

5

дуемого сигнала (т.е. сигнала с выхода амплитудного детектора 3) от верхнего до нижнего пороговых напряжений. Регистратор 18 фиксирует число N импульсов, сосчитанных счетчиком 17. Зная это число, вычисляют логарифмический декремент сР затухания колебаний по формуле (1). Одновременно с прекращением передачи им- пульсов на счетчик 17 сигнал логического О с выхода компаратора 9, преобразоваиньй инвертором 10 в сигнал логической 1 поступает на С-вход D-триггера 11, на D и R-входы которого поступает сигнал логической 1 с выхода компаратора 15. С приходом логической 1 на С-вход D- триггера 11 на его.прямом выходе появляется сигнал логической 1 (фиг.2и) и на вход интегратора 13 начинает поступать опорное напряжение. На инверсном выходе D-триггера 11 при этом появляется сигнал логического О, который, поступая на один из входов элемента И 16, запрещает прохождение импульсов на счетчик 17. Нарастающее напряжение на выходе интегратора 13 открывает ключ 14 (полевой транзистор), в результа- те чего сопротивление его уменьшается, увеличивая тем самым коэффициент усиления усилителя 2.

При этом выходной сигнал усилителя 2 нарастает, следовательно, нарастает сиг1{ал на первом входе блока 5 сравнения, на втором входе которой присутствует неизменный сигнал с выхода интегратора 17, так как последний находится в режиме хране- ния. Вследствие роста сигнала, поступающего с ФНЧ на вход компаратора 15, на выходе последнего внс5вь появляется сигнал логической 1, однко благодаря наличию на одном из входов элемента И 18 сигнала логического О импульсы на счетчик 17 не поступают. При достижении выходн го сигнала ФНЧ 4 значения, равного верхнему пороговому напряжению, вы- ходной сигнал блока 5 сравнения переходит через ноль и изменяет свой знак на противоположный, переводя уем самым компаратор 15 верхнего уровня в состояние логического О на его выходе. Сигнал логического О с выхода компаратора 15, поступая на D и R-входы D-триггера 11,

изменяет его состояние, т.е. на прямом выходе D-триггера появляется сигнал логического О, который переводит интегратор 13 в режим хранения (фиг.2к), вследствие чего коэффициент усиления усилителя 2 прекращает нарастать, стабилизируется его новое значение и вследствие затухания исследуемого сигнала выходной сигнал ФНЧ 4 начинает убывать (фиг.2л).

При этом на инверсном выходе D- триггера 11 появляется сигнал логической 1, разрешая тем самым прохождение импульсов на счетчик 17 при условии наличия сигналов единиц на других входах элемента И 16.

Сигнал логического О с выхода компаратора 15, поступая на ключ 6, замыкает его. Выходной сигнал блока 5 сравнения снова начинает поступать на интегратор 7, выходной сигнал которого начинает возрастать, и йосту- пает на второй вход блока 5 срав не- ния. В связи с тем, что в момент замыкания ключа 6 выходной сигнал блока 5 сравнения близок к нулю (фиг.2в), возрастание выходного сигнала интегратора 7 очень мало. Благодаря тому, что выходной сигнал ФНЧ 4 убывает (фиг,2л), а сигнал интегратора 7 слабо растет, выходной сигнал блока 5 сравнения быстро убывает и, достигнув нуля, изменяет свой знак (фиг. 2в). Вследствие этого на выходе компаратора 15 верхнего уровня появляется сигнал логической 1 (фиг.2д) и ключ 6 размыкается.

Далее процесс измерения повторяется.

Формула изобретения

Устройство для измерения логарифмического декремента затухания, содержащее последовательно соединенные датчик и усилитель, два компаратора, формирователь импульсов заданной амплитуды, два источника опорного напряжения и последовательно соединенны элемент И, счетчик и регистратор, отличающееся тем, что, с

целью повышения достоверности, оно снабжено последовательно соединенными первым ключом, первый вход которого подключен к первому источнику опорного напряжения, первым

интегратором и вторым ключом, выход которого связан с управляющим входом усилителяJ D-триггером, последовательно соединенными амплитудным детектором, вход которого подключен к выходу усилителя, фильтром нижних частот, блоком сравнения, третьим ключом и вторым интегратором, выход которого подключен к второму входу блока сравнения и входу второго источника опорного напряжения, последовательно соединенными кнопкой Пуск и одновибратором и инвертором, включенным между выходом первого компаратора и счетным входом D-триггера, второй компаратор включен между , выходом блока сравнения, управляющи

ми входами D-триггера, третьего ключа и первым входом элемента И, второй вход которого связан с выходом первого компаратора, подключенного первым входом к выходу фильтра нижних частот, а вторым входом - к выходу второго источника опорного напряжения, лрямой выход D-триггера связан с вторым входом первого ключа, а инверсный выход - с третьим входом элемента И, формирователь импульсов заданной амплитуды включен между выходом амплитудного детектора и четвертым входом элемента И, а выход одновибратора связан с входами Сброс интеграторов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный генератор | 1985 |

|

SU1327131A1 |

| Устройство имитации движения баланса электронно-механических часов | 1984 |

|

SU1249474A1 |

| Устройство для определения степени затухания измерительных магнитоэлектрических преобразователей | 1988 |

|

SU1628028A1 |

| Преобразователь частота-напряжение | 1979 |

|

SU809546A2 |

| Устройство для измерения амплитуды колебаний баланса механических часов | 1985 |

|

SU1254430A1 |

| Измеритель среднеквадратического значения напряжения одиночного импульса случайной формы и длительности | 1987 |

|

SU1429054A1 |

| Устройство автоматического управления диапроекторами | 1987 |

|

SU1453361A1 |

| Устройство для вычисления параметров нелинейных колебательных систем | 1985 |

|

SU1302243A1 |

| Способ защиты установки продольной емкостной компенсации | 1987 |

|

SU1422294A1 |

| Устройство для измерения логарифмического декремента затухания струнных преобразователей | 1990 |

|

SU1818596A1 |

Изобретение относится к неразрушающим методам контроля и может быть использовано при исследовании физических свойств изделий. Цель изобретения - повышение достоверности за счет исключения потери информации в начальный момент затухания колебаний. Сигнал с датчика 1 поступает через последовательно соединенные усилитель 2, амплитудный детектор 3 и фильтр 4 нижних частот на первый вход блока 5 сравнения, второй вход которого связан с выходом интегратора 7, подключенного через ключ 6 к выходу блока 5 сравнения. Сигнал с него поступает на компаратор 15 нижнего уровня, а сигнал с интегратора 7 поступает через источник 8 опорного напряжения на л компаратор 9 верхнего уровня. Схема устройства позволяет не учитывать момент нарастания сигнала с датчика до начала его спадания. Счетчик 17 подсчитывает количество периодов сигнала между моментами срабатывания по верхнему и нижнему уровням срабатывания компараторов 9 и 15, которое пропорционально логарифмическому декременту затухания. 2 ил. с (Л

/7

а

юншштппшяпшипияяппшппппяпдшядптдппптшшппя

Фиг.2

| Устройство для поинтервальной обработки скважин | 1972 |

|

SU464696A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для склейки фанер в стыках | 1924 |

|

SU1973A1 |

Авторы

Даты

1988-12-23—Публикация

1987-05-04—Подача