п

+

42ь 4

00

со

00

-к|

Изобретение относится к импульсной и цифровой технике и может быть испольэонано в качестве задающего генератора со стабильной частотой повторения импульсов.

Целью изобретения является повы- гаение временной стабильности.

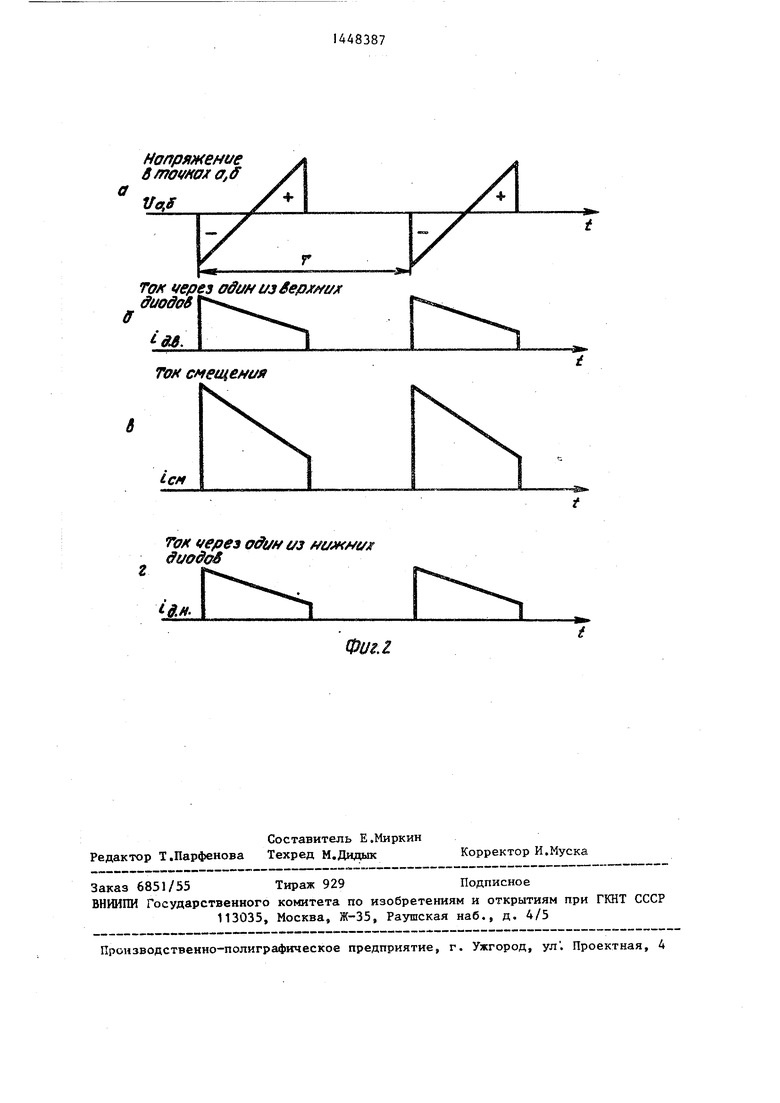

На фиг, 1 изображена принципиальная схема предлагаемого генератора импульсов; на фиг, 2 - временные диаграммы его работы.

На фиг, 2 на диаграмме а изображено времязадающее напряжение в точках а , S времязадающего конденсатора; на диаграмме & показано изменение тока через верхний диод ключа; на диаграмме & приведен ток смещения; на диаграмме -г изображен ток, протекающий через нижний диод ключа.

Генератор (фиг, 1) содержит интегральный Т-триггер 1, тактовый вход которого подсоединен к выходу логического элемента ИЛИ 2, а выходы через резисторы 3 и 4 подключены к базгчм транзисторов 5 и 6 буферных ключей. Эмиттеры транзисторов 5 и 6 подсоединены к потенциальной шине источника питания +Е, а коллекторы - к общим точкам соединений днодиых ключей 7, 8 и 9, 10, Нижние выводы диодных ключей подсоединены к корпусу генератора, а верхние (левые) - к левой общей точке соединения левой обкладки времязадающего конденсатора 11, нижнего вывода времязадающего резистора 12, неинвертирующего входа первого компаратора 3, входа правого повторителя 14 напряжения. Верхний вывод правых диодных ключей 9, 10 подсоединен к правой обкладке времязадающего конденсатора 11, нижнему выводу времязадающего резистора 15, неинвертирующему входу второго компаратора 16 и входу левого повторителя 17 напряжения, Вых,од правого повторителя 14 через резистор 18 подсоединен к общей точке соединения правой пары диодных ключей 9, 10, а выход Левого повторителя 7 через резистор 19 подключен к общей точке соединения левой пары диодных ключей 7, 8, Инвертирующие входы компараторов 13 и 16 соединены между собой и подключены к общей точке 20 соединения резисторов 21 и 22 резистивного делителя, служащего для получения плавающего опорного напряжения, Выходы компараторов 13 и 16 подсоединены к входу логического элемента ИЛИ 2. Верхние выводы времязадающих резисторов 12 и 15 подсоединены к потенциальной щине источника питания 1-Е. Потенциальная шина, источника смещения -Е через резисторы 23 и 24 соединена с общими точками каждой из пар встречно включенных диодных ключей 7, 8 и 9, 10.

Устройство работает следзпощим образом.

Пусть Т-триггер 1 находится в состоянии 1, Транзистор 5 буферного

ключа закрыт и конденсатор 11 перезаряжается по цепи: диодные ключи 7, 8, конденсатор 11, резистор 15, потенциальная шина +Е источника питания, В результате напряжение на правой обкладке конденсатора 1 увеличивается. Когда оно становится равным напряженио в точке 20 соединения резисторов 21, 22 делителя, происходит срабатывание компаратора 16, Положительный перепад напряжения с выхода компаратора 16 поступает на вход логического элемента ИЛИ 2 и затем с выхода элемента 2 на счетный вход триггера 1, Триггер переходит в

другое (дулевое) устойчивое состояние. При этом потенциал правой обкладки конденсатора 11 (T.S, фиг, 1) становится нулевым, а левой 1т,а , фиг, 1) - отрицательным. Затем конденсатор 11 начинает перезаряжаться по цепи: диодные ключи 9, 10 конденсатор , резистор 12; шина +Е источника питания. Повторяется процесс, аналогичный описанному. Временные диаграммы напряжения в точках а и & схемы (фиг. 1) показаны на фиг, 2а,

В моменты переключения триггера, когда времязадающее напряжение достигает порогового уровня, начальное

напряжение в т, О или в точке S (фиг, 1) может быть определено по формуле

50

R21

и,()и,(о) , (1)

Реверсивное переключение конденсатора 11 осуществляется при помощи встречно включенных диодных ключей 7, 8 и 9, 10 (включенных по баланс- ной схеме), которые управляются перепадами напряжения, формируемыми буферными ключами 5 и 6, которые в свою очередь управляются перепадами, поступающими с выхода триггера 1, .

Если ток, протекающий через нижние диодные ключи 8-10 (фиг. 2г), изменяется по такому же закону, по какому изменяется ток,верхних диодных ключей (фиг, 2б), то падения напряжения на диодных ключах 7, 8 и 9, 10 в момент проводящего состояния последних, равны по величине и противоположны по знаку. Следователь- ю из двух резисторов и одного конденсаФормула изобретения

Генератор импульсов, содержащий 5 Т-триггер, компаратор, два диодных ключа, выполненных на двух парах последовательно соединенных и встречно подключенных полупроводниковых диодов, и времязадающую цепь, состоящую

из двух резисторов и одного конденсаФормула изобретения

Генератор импульсов, содержащий Т-триггер, компаратор, два диодных ключа, выполненных на двух парах последовательно соединенных и встречно подключенных полупроводниковых диодов, и времязадающую цепь, состоящую

| название | год | авторы | номер документа |

|---|---|---|---|

| ПИКОВЫЙ ДЕТЕКТОР | 2009 |

|

RU2409818C1 |

| Генератор импульсов | 1987 |

|

SU1628190A1 |

| МНОГОФУНКЦИОНАЛЬНЫЙ ПИКОВЫЙ ДЕТЕКТОР | 2019 |

|

RU2708687C1 |

| Мультивибратор | 1979 |

|

SU790122A1 |

| Устройство для ускоренного заряда аккумуляторной батареи | 1988 |

|

SU1557630A2 |

| ОДНОВИБРАТОР | 1972 |

|

SU358768A1 |

| Преобразователь постоянного напряжения | 1983 |

|

SU1169108A1 |

| Формирователь импульсов | 1985 |

|

SU1325674A1 |

| Одновибратор | 1981 |

|

SU983988A1 |

| Ждущий мультивибратор | 1990 |

|

SU1739484A1 |

Изобретение относится к импульсной технике и может использоваться в автоматике и вычислительной технике. Целью изобретения является повышение временной стабильности. В устройство, содержащее Т-триггер 1, компаратор 16, два диодных ключа, выполненных на двух парах последовательно соединенных и встречно включенных полупроводниковых диодов 7-10 и времязадающую цепь, состоящую из двух резисторов 12, 15 и одного конденсатора 11, а также делителя напряжения на резисторах 21 и 22, введены второй компаратор 13, логический элемент 2, два буферных транзисторных ключа 5 и 6 и два повторителя 14 и 17 напряжения. Устройство обеспечивает высокую стабильность временных параметров при изменении температуры окружающей среды, напряжения источников питания и параметров схемы в процессе старения за счет стабилизации тока заряда конденсатора и тока смещения диодных ключей. 2 ил. Ф (Л

но, суммарное падение напряжения на диодных ключах 7, 8 и 9, О, находящихся в состоянии Включено равно нулю. Это достигается тек, что ток смещения формируется при помощи повторителей 14 и 17 напряжения и резисторов 18, 19, 23, 24, Во время перезаряда емкости ток через верхний диодный ключ 7 (или 9) не остается постоянным, а уменьщается по мере перезаряда конденсатора 11 (фиг, 2б), Напряжение в т, а (или S) через повторитель 14 (или 17) поступает на резистор 18 (или 17/ и

тора, обе обкладки которого, первая и вторая соответственно, через резисторы соединены с потенциальной щиной источника питания и через диод15 ные ключи - с общей щиной устройства, при этом общие точки соединения диодов диодных ключей через резисторы подключены к источнику смещения, неинвертирующий вход, компаратора под-

20 ключен к первой обкладке конденсатора, а его инвертирующий вход соединен с общей точкой соединения резисторов резистивного делителя напряжения.

включенного между потенциальной ши- преобразуется в ток смещения диодно- 25 ной источника питания и общей шиной го ключа 10 (или 8), Происходит син- устройства, о тличающийся хронное (согласованное) изменение то- тем, что, с целью повышения временной ка смещения (фиг, 2в) с током верх- стабильности, в него введены второй него диода. Ток смещения при помощи компаратор напряжения, логический резисторов 18, 19, 23, 24 выбирается 30 элемент ИЛИ, два буферных транзистор- по величине в два раза больше, чем ток верхнего диода, чтобы обеспечивалось равенство

(2) (3)

icM()i3.H()(b

()э.9() .

Таким образом, осуществление согласованного процесса изменения тока смещения и повьщ1ения стабильности порогового уровня за счет, непосредственного подключения времязадающего конденсатора к входам компараторов обеспечивает идеальные условия работы экспоненциального ЕС-моста, образованного резисторами 12, 15, конденсатором 11, делителем (21-22).

Длительность периода при R,,R,FR можно определить по формуле

ных ключа и два повторителя напряже- гая - первый и второй, при этом выход первого повторителя соединен через резистор с общей точкой соединения

35 диодов первого диодного ключа, а выход второго повторителя подаслючен к общей точке соединения диодов второго диодного ключа, при этом вход второго повторителя соединен с левой об40 кладкой времязадающего конденсатора, а вход первого - с второй обкладкой конденсатора, неинвертирующий вход второго компаратора соединен с вто- рой обкладкой времязадающего конден45 сатора, а инвертирующий - с общей точкой соединения резисторов резистивного делителя, причем выходы компараторов подключены через логический элемент ИЛИ к счетному входу Т-тригТ 2ЕС In , R21

(4)

где К относительное значение порогового уровня;

45 сатора, а инвертирующий - с общей точкой соединения резисторов резистивного делителя, причем выходы компараторов подключены через логически элемент ИЛИ к счетному входу Т-триг50 гера, подключенного инвертирукнцим и неинвертирующим входами через резисторы к базам двух транзисторов буферных ключей, эмиттеры которых

подключены к потенциальной щине ис- R20, R21 - значение сопротийле- 55 точника питания, а коллектор каждо- ний делителя; го из транзисторов соединен с общей С - емкость времяз адаю- точкой соединения диодов одного из щего конденсатора 11, диодных ключей.

тора, обе обкладки которого, первая и вторая соответственно, через резисторы соединены с потенциальной щиной источника питания и через диодные ключи - с общей щиной устройства, при этом общие точки соединения диодов диодных ключей через резисторы подключены к источнику смещения, неинвертирующий вход, компаратора под-

ключен к первой обкладке конденсатора, а его инвертирующий вход соединен с общей точкой соединения резисторов резистивного делителя напряжения.

включенного между потенциальной ши- 25 ной источника питания и общей шиной устройства, о тличающийся тем, что, с целью повышения временной стабильности, в него введены второй компаратор напряжения, логический 30 элемент ИЛИ, два буферных транзистор-

ных ключа и два повторителя напряже- гая - первый и второй, при этом выход первого повторителя соединен через резистор с общей точкой соединения

5 диодов первого диодного ключа, а выход второго повторителя подаслючен к общей точке соединения диодов второго диодного ключа, при этом вход второго повторителя соединен с левой об0 кладкой времязадающего конденсатора, а вход первого - с второй обкладкой конденсатора, неинвертирующий вход второго компаратора соединен с вто- рой обкладкой времязадающего конден5 сатора, а инвертирующий - с общей точкой соединения резисторов резистивного делителя, причем выходы компараторов подключены через логический элемент ИЛИ к счетному входу Т-триг0 гера, подключенного инвертирукнцим и неинвертирующим входами через резисторы к базам двух транзисторов буферных ключей, эмиттеры которых

Напря ненае . д/nowox a,ff /I

V

V

To/f vepe3 ifffi/fft/3Sepjfffi/ диодов Г

&В.

Tof смещен1/я

iCM

To/( vffflffs offe/ff t/3 диодоЗ

I d.H.

Фиг. I

A

r

-38 t

1

| ГЕНЕРАТОР ИМПУЛЬСОВ | 0 |

|

SU329660A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Генератор импульсов | 1975 |

|

SU585595A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-12-30—Публикация

1987-05-05—Подача