Изобретение относится к цифровой измерительной технике, в частности к аналого-цифровым преобразователям, и может быть использовано для построения быстродействующих преобразователей напряжения в код (ПНК) параллельного типа.

Целью изобретения является повышение точности преобразования.

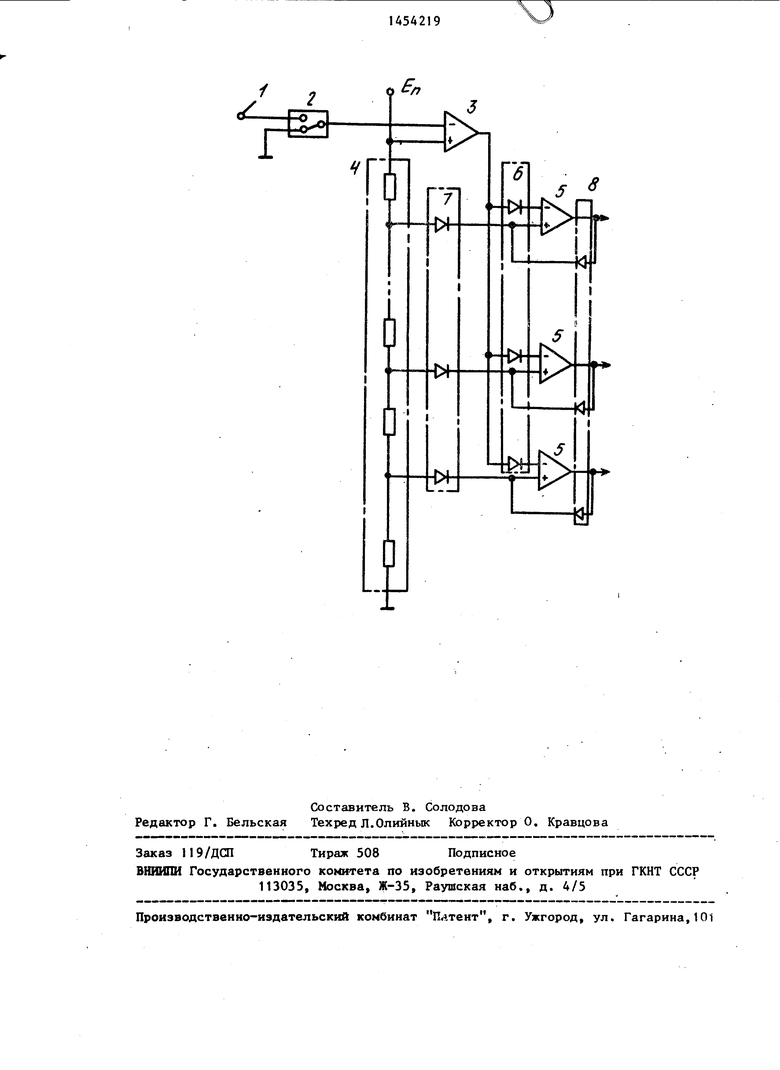

На чертеже представлена электрическая схема предлагаемого ПНК.

ПНК содержит входную шину 1, переключатель 2, блок вычитания 3, делитель напряжения 4, компараторы 5, диоды соответственно первой 6, второй 7 и третьей 8 групп.

ПНК работает следующим образом.

В подготовительном режиме переключатель 2 устанавливается в состояние, при котором его выход подключен к общей шине. На выходе блока вычитания 3 при этом устанавливается потенциал, равный потенциалу Еn шины опорного питания. Потенциалы на инвертирующих входах компараторов 5 превышают потенциалы на их неинвертирующих входах, и на выходах компараторов 5 устанавливаются низкие (неактивные) уровни сигналов. Токи неинвертирующими входами компараторов 5 от делителя напряжения 4 в этом случае не потребляются.

Уровни выходных сигналов Uк компараторов выбираются такими, чтобы в неактивном состоянии они не превышали напряжения UR на одном резисторе делителя напряжения 4, а в активном состоянии соблюдалось неравенство

En - UR < Uк < En.

В режиме преобразования переключатель 2 устанавливается в состояние, при котором его выход соединен с входной шиной 1 ПНК. На выходе блока вычитания 3 устанавливается потенциал, равный Еn - Uвх, где Uвх - входное преобразуемое напряжение, подаваемое на входную шину 1 ПНК. При этом срабатывают компараторы (начиная с верхнего по схеме), потенциал на инвертирующих входах которых становится ниже потенциалов на их неинвертирующих входах. На выходах сработанных компараторов устанавливаются высокие (активные) уровни сигналов.

В силу того, что активные уровни выходных сигналов сработанных компараторов превышают по величине уровни напряжения, снимаемые неинвертирующими входами компараторов через первые диоды с выходов делителя напряжения 4, первые диоды сработанных компараторов оказываются смещенными в обратном направлении, а токи неинвертирующими входами сработанных компараторов потребляются не с выходов делителя напряжения 4, а с активных входов сработанных компараторов.

Ток, протекающий через делитель напряжения 4, остается неизменным, и шкала уровней квантования постоянна. Точность преобразования при этом повышается по сравнению с известными ПНК.

Организация у компараторов 5 положительной обратной связи путем соединения их выводов через диоды третьей группы 8 с их неинвертирующими входами позволяет фиксировать в цифровом коде амплитудное значение входного сигнала, которое он имел в момент преобразования. Цифровой код при этом снимается с выходов компараторов, причем младший разряд кода формируется верхним по схеме компаратором 5.

Следует отметить, что в момент срабатывания i-го компаратора все же происходит некоторое шунтирование делителя напряжения. Однако такое шунтирование минимально сказывается, по сравнению с шунтированием у известных ПНК, на точности преобразования, так как, во-первых, в предлагаемом ПНК потребляемый в момент срабатывания i-м компаратором от делителя напряжения ток вдвое меньше по сравнению с током, потребляемым каждым несработанным компаратором в известных ПНК; во-вторых, один срабатываемый компаратор в предлагаемом ПНК оказывает меньшее шунтирующее воздействие на делитель, нежели, как это наблюдается в известных ПНК, все несработанные компараторы, потребляющие от делителя напряжения максимальные токи.

В то же время наблюдаемое в предлагаемом ПНК шунтирование во время срабатывания компаратора имеет и положительную сторону. Так, в известных ПНК неблагоприятными для преобразования являются случаи, когда уровень входного напряжения равен одному из квантующих уровней делителя напряжения. В несработанном состоянии i-й компаратор, потребляя ток от i-го выхода делителя напряжения, оказывает на него шунтирующее действие, поэтому i-й уровень квантования несколько занижен. При достижении входным напряжением i-го уровня квантования срабатывает i-й компаратор. При этом ток, потребляемый сработанным компаратором от i-го выхода делителя напряжения, резко уменьшается, что вызывает повышение i-го уровня квантования, который может вновь превысить уровень преобразуемого входного напряжения и заставить i-й компаратор вернуться в исходное несработанное состояние. Далее процессы могут повториться, а на выходе компаратора может наблюдаться неоднозначность считывания.

Предлагаемый ПНК свободен от этого недостатка. Во время срабатывания компаратора за счет шунтирующего воздействия несколько увеличивается падение напряжения на верхних резисторах делителя, с которым сравнивается входное напряжение. После срабатывания компаратора шунтирующее воздействие прекращается и падение напряжения на верхних резисторах восстанавливается (уменьшается, что тем более подтверждает включенное состояние компаратора и исключает его дребезг).

Перед каждым циклом преобразования необходимо с помощью переключателя 2 занулять инвертирующий вход блока вычитания 3, тем самым приводя в исходное состояние сработанные компараторы.

Диоды первой группы 6 введены в ПНК для организации искусственного смещения потенциалов неинвертирующих входов компаратора 5 на величину, равную смещению потенциалов их неинвертирующих входов первыми диодами второй группы 7. (56) Хоровиц П. и др. Искусство схемотехники. М. : Мир, 1984, с. 60, т. 2, рис. 9, 41.

Шило В. Л. Линейные интегральные схемы в радиоэлектронной аппаратуре, М. : Советское радио, 1979, с. 342-343, рис. 8.26.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В КОД ПАРАЛЛЕЛЬНОГО ТИПА | 1988 |

|

SU1635876A1 |

| Аналого-цифровой преобразователь | 1981 |

|

SU984034A1 |

| Интегрирующий аналого-цифровой преобразователь | 1987 |

|

SU1628204A1 |

| СИГНАЛИЗАТОР ОБЛЕДЕНЕНИЯ | 1994 |

|

RU2102791C1 |

| Устройство для контроля исправности релейной защиты | 1988 |

|

SU1644252A1 |

| Устройство преобразования напряжение-код | 1984 |

|

SU1339891A1 |

| Устройство для контроля исправности релейной защиты | 1989 |

|

SU1684746A1 |

| Преобразователь напряжение-код | 1981 |

|

SU1003332A1 |

| ПАРАЛЛЕЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ДИНАМИЧЕСКОГО ТИПА (ВАРИАНТЫ) | 2008 |

|

RU2389133C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ИНТЕГРИРУЮЩЕГО ТИПА ДЛЯ ИЗМЕРЕНИЯ МАЛЫХ ЭЛЕКТРИЧЕСКИХ СИГНАЛОВ | 2018 |

|

RU2693647C1 |

Изобретение относится к цифровой измерительной технике, в частности к аналого - цифровым преобразователям, и может быть использовано для построения быстродействующих преобразователей напряжения в код параллельного типа. Цель изобретения - повышение точности преобразования. Поставленная цель достигается за счет поддержания постоянным по величине уровня тока, протекающего через последовательно включенные резисторы делителя напряжения, и сохранения неизменными формируемых делителем напряжения уровня квантования. Для этого выходы делителя через диоды первой группы подключены к неинвертирующим входам компараторов, выходы которых соединены с неинвертирующими входами через диоды второй группы. Инвертирующие входы компараторов через диоды третьей группы в обратном включении соединены с выходом блока вычитания. Неинвертирующий вход блока вычитания соединен с шиной опорного напряжения, а инвертирующий вход - с выходом переключателя, первый вход которого соединен с входной шиной, а второй вход - с общей шиной. Делитель напряжения включен между шиной опорного питания и общей шиной. При нулевом уровне входного напряжения потенциалы инвертирующих входов компараторов превышают потенциалы их неинвертирующих входов. Токи с выходов делителя при этом неинвертирующими входами не потребляются. При увеличении входного напряжения срабатывают компараторы, потенциалы на инвертирующих входах которых становятся ниже потенциалов на их неинвертирующих входах. Ток неинвертирующими входами сработанных компараторов в этом случае потребляется с их выходов. Уровни квантования, формируемые делителем напряжения, остаются неизменными. 1 ил.

ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В КОД ПАРАЛЛЕЛЬНОГО ТИПА, содержащий делитель напряжения из n последовательно соединенных резисторов, первый вход которого подключен к общей шине, а второй вход является шиной опорного напряжения, и n - 1 компараторов, отличающийся тем, что, с целью повышения точности преобразования, в него введены переключатель, блок вычитания и первая, вторая и третья группы из n - 1 токоограничивающих элементов каждая, выполненных на диодах, причем первый вход переключателя является входной шиной, второй вход подключен к общей шине, а выход соединен с инвертирующим входом блока вычитания, неинвертирующий вход которого является шиной опорного напряжения, а выход соединен с анодами диодов первой группы, катоды которых подключены к инвертирующим входам соответствующих компараторов, неинвертирующие входы которых подключены к катодам соответствующих диодов второй и третьей групп, при этом аноды диодов второй группы соединены с соответствующими выходами делителя напряжения, а аноды диодов третьей группы - с выходами соответствующих компараторов, которые являются соответствующими выходными шинами.

Авторы

Даты

1994-02-28—Публикация

1987-06-16—Подача