Изобретение относится к средствам измерения электрических величин и может быть использовано, если измеряемые величины имеют малые значения.

Для измерения малых электрических величин широкое распространение имеет включение в схему измерителя нормирующего усилителя с заранее выбранным постоянным коэффициентом усиления. Нормирующий усилитель предназначен для приведения в соответствие диапазона изменения измеряемого малого электрического сигнала с диапазоном изменения входного сигнала используемого в этом случае стандартного преобразователя аналог-код. Это позволяет задействовать все разряды выходного кода преобразователя, тем самым уменьшив ту составляющую часть погрешности преобразования, которая связана с разрядностью цифрового кода.

Опыт разработки таких измерительных систем отражен в книге Нуберта Г.П. Измерительные преобразователи неэлектрических величин. - Л.: Энергия, 1970. - 105 с. Нормирующий инструментальный усилитель имеется, например, в многоканальном преобразователе сигналов тензорезистивных датчиков в патенте РФ №2424533. Однако включение в цепь измерения нормирующего усилителя приводит к увеличению аддитивных шумов, действующих на входе преобразователя, на величину шума самого усилителя, что, при измерении малых электрических сигналов увеличивает погрешность измерения.

Для уменьшения влияния аддитивных шумов на погрешность измерения электрических величин в аналого-цифровых преобразователях применяют интегрирование смеси измеряемого сигнала с шумом. (Волович Г.И. Схемотехника аналоговых и аналого-цифровых электронных устройств. - М.:»Додэка-XXI», 2005. - 446 с.).

Если для аналого-цифрового преобразования смеси электрического сигнала и аддитивного шума, возникающего из-за влияния внешних электромагнитных полей, применяют двухтактное преобразование интегрирующего типа, то уменьшить погрешность преобразования можно, если для интегрирования применяется операционный усилитель с дифференциальным входным каскадом, при этом электрические цепи, подключаемые к инвертирующему и неинвертирующему входам операционного усилителя, на котором реализуется интегратор, симметрируют (см., например, патент РФ №2097777). В этом патенте реализовано двухтактное аналого-цифровое преобразование интегрирующего типа, где интегратор построен на операционном усилителе, а симметрирование электрических цепей, по которым сигналы и шумы поступают на инвертирующий и неинвертирующий входы операционного усилителя, осуществляется с целью создания одинаковых условий для действия помех электромагнитного происхождения на обоих входах операционного усилителя, что позволяет за счет подавления в операционном усилителе синфазных помех уменьшить погрешность преобразования.

Недостатком устройства по патенту РФ №2097777 является то, что устройство может измерять только сигналы резистивных датчиков, включенных в мостовую схему, которая является симметричной схемой. В других случаях, когда источник электрического сигнала не содержит симметричные выходные электрические цепи, это устройство не сможет эффективно подавить электромагнитные помехи при измерении электрических величин

В качестве прототипа выбран двухтактный аналого-цифровой нелинейный преобразователь интегрирующего типа, описанный в патенте РФ №2564909. В этом устройстве входной зажим, через последовательно соединенные один из входов управляемого двухвходового ключевого элемента и резистор, соединен с инвертирующим входом операционного усилителя, между этим входом и выходом которого включен конденсатор, второй вход управляемого двухвходового ключевого элемента соединен с выходом источника тока разряда, неинвертирующий вход операционного усилителя соединен с шиной, имеющей нулевой потенциал, выход операционного усилителя соединен с первым входом компаратора, второй вход компаратора соединен с источником уровня сравнения, выход компаратора соединен со входом блока тактирования и управления, один выход которого соединен с управляющим входом управляемого двухвходового ключевого элемента и со входом блока включения/выключения источника тока, а второй выход соединен со входом блока кодирования, выход блока включения/выключения источника тока разряда соединен с управляющим входом источника тока разряда, а блок кодирования, который состоит из последовательно соединенных осциллятора, логической схемы «И» и счетчика, на выходе имеет выход счетчика, который и является выходом аналого-цифрового преобразователя. Резистор, включенный между входом устройства и инвертирующим входом операционного усилителя, вместе с операционным усилителем и конденсатором, включенный между его инвертирующим входом и выходом, образуют интегрирующий операционный усилитель.

Техническим результатом в устройстве по патенту РФ №2564909 является уменьшение погрешности преобразования путем формирования разряда емкости интегратора по нелинейной зависимости от времени во втором такте преобразования.

Недостатком устройства по патенту РФ №2564909 является то, что выходной код при малых значениях входной измеряемой величины принимает значения, близкие к нулю. При этом относительная погрешность, определяемая как отношение разброса выходных кодов к среднему значению выходного кода, по мере приближения среднего значения выходного ода к нулю, возрастает, хотя действие шумов, приводящее к разбросу выходных кодов, не изменяется при уменьшении измеряемой электрической величины. Это увеличение относительной погрешности измерения малых электрических величин в устройстве по патенту РФ №2564909 возникает из-за того, что неинвертирующий вход операционного усилителя подключен к нулевому потенциалу, и поэтому при малых значениях измеряемой электрической величины выходные коды принимают малые значения.

Задачей заявляемого изобретения является уменьшение относительной погрешности аналого-цифрового нелинейного преобразователя интегрирующего типа с двухтактным преобразованием в локальной окрестности нижней границы динамического диапазона измеряемой электрической величины, если преобразователь применяется для измерения малых электрических величин при аддитивных помехах, и если источник измеряемой электрической величины не содержит симметричные выходные электрические цепи.

Предлагаемый аналого-цифровой преобразователь интегрирующего типа для измерения малых электрических сигналов, содержащий операционный усилитель, инвертирующий вход которого соединен с конденсатором и входным резистором, при этом через эти входной резистор и конденсатор протекает измеряемый малый электрический ток, вход управляемого ключевого элемента соединен с входным зажимом, выход операционного усилителя соединен со вторым выводом конденсатора и первым входом компаратора, второй вход которого соединен с источником уровня сравнения, выход компаратора соединен со входом блока тактирования и управления, второй выход которого соединен со входом блока кодирования и входом блока включения/выключения источника тока разряда, выход которого соединен со входом источника тока разряда емкости интегратора, а блок кодирования, который состоит из последовательно соединенных осциллятора, логической схемы «И» и счетчика, на выходе имеет выход счетчика, который и является выходом аналого-цифрового преобразователя, отличающийся тем, что в него введены запоминающая емкость, один вывод которой соединен с нулевой шиной, второй вывод запоминающей емкости через симметрирующий резистор соединен с неинвертирующим входом операционного усилителя, выход управляемого ключевого элемента соединен с нулевой шиной, а управляющий вход ключевого элемента соединен с первым выходом блока тактирования и управления, вход блока включения/выключения источника тока разряда соединен со входом блока кодирования, входной зажим соединен с общей точкой входного резистора и входом управляемого ключевого элемента, а выход источника тока разряда соединен с одним концом того резистора, который другим концом соединен с общей точкой входного резистора, конденсатора и инвертирующего входа операционного усилителя, введена также коммутируемая диодно-резистивная схема заряда запоминающей емкости, которая содержит первый резистор, одним концом соединенный с плюсом источника напряжения со средней точкой, которая соединена с нулевой шиной, второй конец соединен с плюсом первого диода, минус которого соединен с точкой соединения запоминающей емкости и плюса второго диода, минус которого соединен со вторым резистором, второй конец которого соединен с минусом источника напряжения, а также содержит блок из двух последовательно соединенных ключевых элементов, общая точка которых соединена с нулевой шиной, второй вывод одного ключевого элемента соединен с общей точкой первого диода и первого резистора, а второй вывод другого ключевого элемента соединен с общей точкой второго диода и второго резистора, управляющий вход блока ключевых элементов соединен с третьим выходом блока тактирования и управления.

Поставленная задача решается тем, что на неинвертирующий вход операционного усилителя подается ненулевой потенциал, величина которого формируется на запоминающей емкости, включенной между неинвертирующим входом и общей шиной. Чтобы скомпенсировать изменение потенциала в связи с токами утечки через запоминающую емкость, заряд на ней подстраивается во втором такте преобразования. Для этого неинвертирующий вход операционного усилителя, вместо соединения с общей шиной, через резистор соединяют с запоминающей емкостью, процесс заряда-разряда которой синхронизируется с фазами цикла аналого-цифрового преобразования, а величина заряда запоминающей емкости определяется специальной коммутируемой диодно-резистивной схемой. Процесс изменения величины заряда на запоминающей емкости, на которой формируется напряжение, поступающее на неинвертирующий вход операционного усилителя, осуществляется во втором такте преобразования от момента срабатывания компаратора до момента начала первого такта следующего цикла преобразования, а уровень напряжения на запоминающей емкости, достигнутый к моменту начала первого такта следующего цикла преобразования, сохраняется неизменным до момента срабатывания компаратора во втором такте следующего цикла преобразования. Это позволяет обеспечить ток заряда емкости интегратора в первом такте преобразования, сформировать не нулевой цифровой код на выходе преобразователя при любом значении входного сигнала, в том числе и нулевом, а также позволяет исключить переключатель из цепи тока заряда емкости интегратора в первом такте преобразования.

Соединение неинвертирующего входа операционного усилителя с запоминающей емкостью, электрический потенциал на которой устанавливается коммутируемой диодно-резистивной схемой, позволяет подключать к неинвертирующему входу дополнительные электрические цепи без изменения режима включения операционного усилителя по постоянному току. В частности, это можно использовать с целью уменьшения погрешности преобразователя при действии электромагнитных помех путем электрического симметрирования резистивных электрических цепей, соединенных с инвертирующим и неинвертирующим входами интегрирующего операционного усилителя. Симметрирование резистивных цепей достигается попарным равенством входного резистора, через который протекает входной ток, и дополнительного резистора, подключаемого к неинвертирующему входу, а также резистора, через который протекает ток разряда интегрирующего конденсатора и симметрирующего резистора, через который на неинвертирующий вход операционного усилителя поступает напряжение от запоминающей емкости. При этом помехи, поступающие на инвертирующий вход вместе с измеряемым входным током, компенсируются операционным усилителем за счет подачи такой же помехи на неинвертирующий вход от включенной в электрическую схему симметрирующей электрической цепи, за счет чего удается уменьшить влияние аддитивных помех электромагнитной природы на выходной код преобразователя. Режим работы интегрирующего операционного усилителя обеспечивается изменением схемы его включения, для чего неинвертирующий вход отсоединен от нулевой шины и подключен через резистор к запоминающему конденсатору.

Для того, чтобы исключить влияние помех, улавливаемых антенной, на процесс заряда запоминающей емкости во втором такте преобразования, введен второй ключевой элемент, вход которого соединен с общей точкой антенны и одного вывода резистора, выход ключевого элемента соединен с нулевой шиной, а управляющий вход соединен с первым выходом блока тактирования и управления. В этом случае достигается полная симметрия электрических цепей, подключенных к инвертирующему и неинвертирующему входам операционного усилителя.

Краткое описание чертежей:

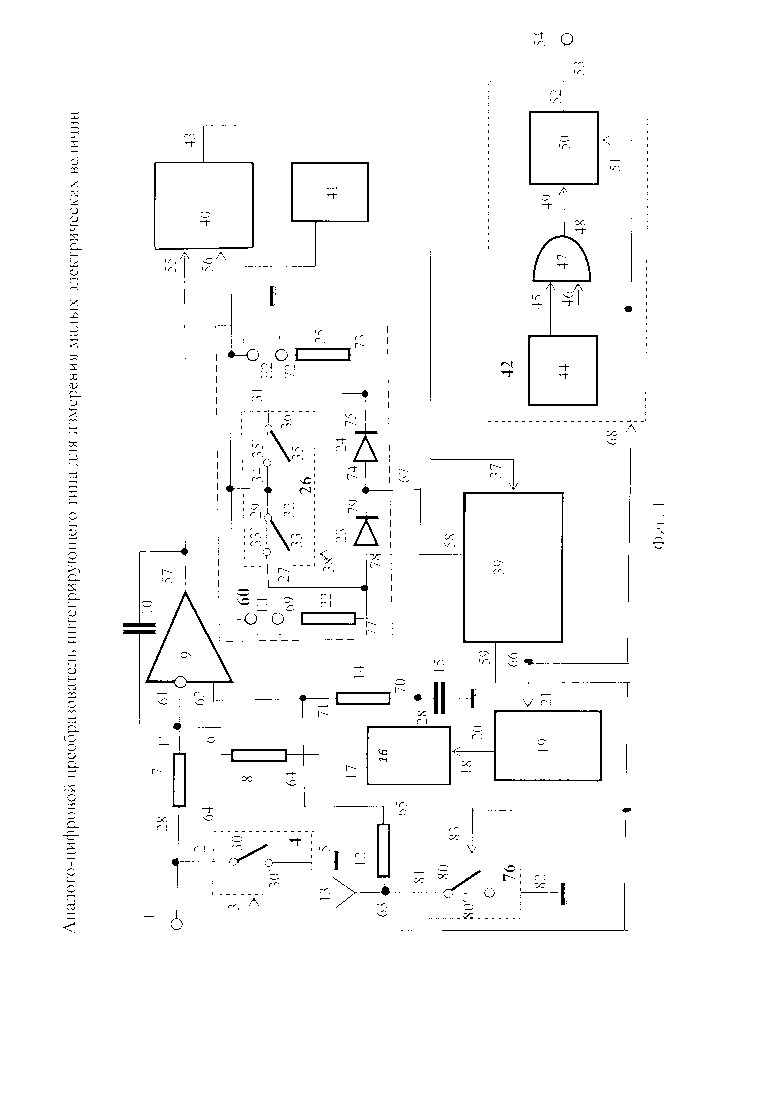

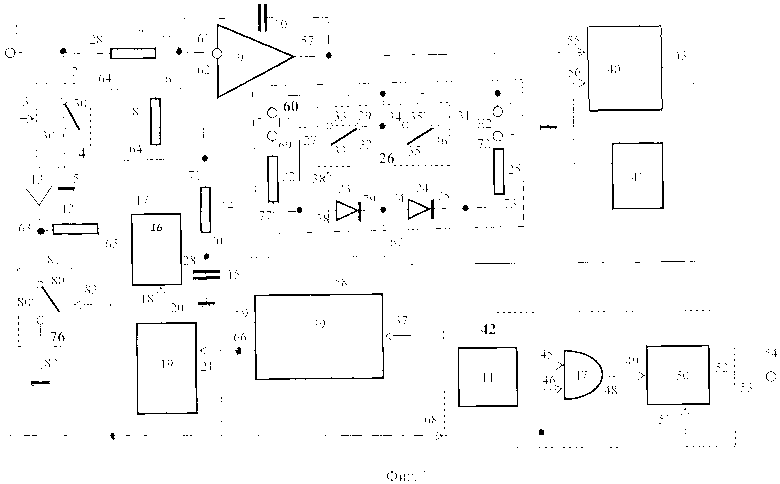

фиг. 1 - структурная схема предложенного аналого-цифрового преобразователя интегрирующего типа для измерения малых электрических сигналов;

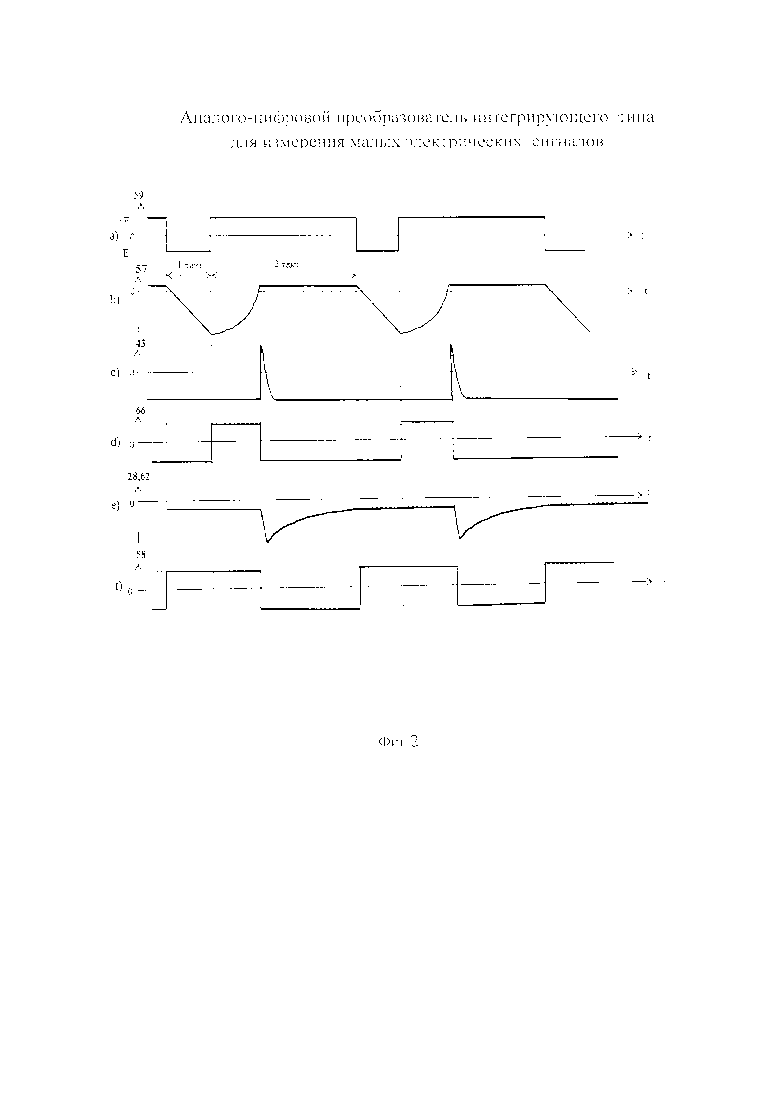

фиг. 2 - временные зависимости сигналов на выходах блоков структурной схемы предложенного аналого-цифрового преобразователя, номера выходов блоков указаны на оси ординат.

Структурная схема предложенного аналого-цифрового преобразователя интегрирующего типа с двухтактным преобразованием (фиг. 1) имеет вход 1, который соединен с выводом 2 ключевого элемента 4 и выводом 28 резистора 7, вывод 5 ключевого элемента 4 соединен с общей шиной, вывод 11 резистора 7 соединен с инвертирующим входом операционного усилителя 9, выводом 6 резистора 8 и выводом 61 конденсатора 10, вывод 57 конденсатора 10 соединен с выходом операционного усилителя 9 и входом 55 компаратора 40, выход 43 компаратора 40 соединен со входом 37 блока тактирования и управления 39, а второй вход 56 компаратора 40 соединен с источником уровня сравнения 41. Первый выход 59 блока тактирования и управления 39 соединен с управляющим входом 3 ключевого элемента 4, второй выход 66 блока тактирования и управления 39 соединен со входом 21 блока включения/выключения источника тока разряда 19, выход 20 которого соединен со входом 18 источника тока разряда емкости интегратора 16, выход 17 которого соединен со входом 64 резистора 8.

Второй выход 66 блока тактирования и управления 39 соединен также со входом 68 блока кодирования 42, который содержит осциллятор 44, выход которого соединен со входом 45 логической схемы «И» 47, вход 46 которой соединен со входом 68 блока кодирования 42, выход 48 логической схемы «И» 47 соединен со счетным входом 49 счетчика 50, управляющий вход 51 которого соединен со входом 68 блока кодирования 42, а выход 52 счетчика 50 соединен с выходом 53 блока кодирования, который является выходом 54 аналого-цифрового преобразователя.

Вывод 67 коммутируемой диодно-резистивной схемы заряда 60 соединен с выводом 28 запоминающей емкости 15 и выводом 70 симметрирующего резистора 14, второй вывод запоминающей емкости 15 соединен с общей шиной, вывод 71 симметрирующего резистора 14 соединен с неинвертирующим входом 62 операционного усилителя 9. В коммутируемой диодно-резистивной схеме заряда 60 плюс источника напряжения Е1 соединен с выводом 69 резистора 22, вывод 77 резистора 22 соединен с выводом 78 диода 23 и выводом 27 блока ключевых элементов 26, являющийся выводом ключевого элемента 32. Вывод 79 диода 23 соединен с выводом 74 диода 24 и выводом 67 коммутируемой диодно-резистивной схемы заряда 60, вывод 75 диода 24 соединен с выводом 73 резистора 25 и выводом 31 блока ключевых элементов 26, являющийся выводом ключевого элемента 36. Вывод 72 резистора 25 соединен с минусом источника напряжения Е2, плюс источника напряжения Е2 и минус источника напряжения Е1 соединены с общей шиной. В блоке ключевых элементов 26 вывод 29 ключевого элемента 32 соединен с выводом 34 ключевого элемента 36 и соединен с общей шиной. Управляющий вход 38 блока ключевых элементов 26 соединен с третьим выводом 58 блока тактирования и управления 39. Источники напряжения Е1 и Е2 образуют двухполярный источник напряжения со средней точкой.

При необходимости электрического симметрирования входных цепей, соединенных со входами 61 и 62 операционного усилителя 9, в схему вводят резистор 12, вывод 65 которого соединен с неинвертирующим входом 62 операционного усилителя 9, а вывод 63 соединяют с антенной 13. В этом случае резистор 7 должен иметь такое же сопротивление, что и резистор 12, а резистор 8 должен иметь такое же сопротивление, что и симметрирующий резистор 14. В качестве антенны 13 может быть использован отрезок монтажного провода, либо антенной 13 может быть часть монтажного провода, не защищенная экранированием, который соединяет источник слабого измеряемого электрического сигнала с входной цепью измерителя.

Если помехи электромагнитной природы оказываются настолько большими, что, попадая на неинвертирующий вход 62 операционного усилителя 9, во втором такте преобразования оказывают влияние на процесс разряда емкости 10, то для устранения этого влияния в схему вводится ключевой элемент 76, вывод 81 которого соединяют с точкой соединения выхода антенны 13 и входа 63 резистора 12,, второй вывод 82 ключевого элемента 76 соединяют с нулевой шиной, а управляющий вход 83 ключевого элемента 76 соединяют с первым выходом 59 блока тактирования и управления 39.

Предложенный двухтактный аналого-цифровой преобразователь интегрирующего типа, представленный на фиг. 1, работает следующим образом. Временные диаграммы напряжений в нескольких точках преобразователя, поясняющие его работу, представлены на фиг. 2.

Процесс преобразования входных электрических сигналов осуществляется циклами, каждый из которых состоит из двух этапов (временных тактов), которые задаются блоком тактирования и управления 39 формированием на втором выходе 59 управляющего сигнала, показанного на фиг.2 а). Первому такту преобразования соответствует отрицательный сигнал на выходе 59, второму такту - положительный.

В течение первого такта ключевой элемент 4 находится в положении 30, размыкая контакт входного зажима 1 с общей шиной, в течение второго такта ключевой элемент 4 находится в положении 30', и входной зажим 1 оказывается замкнут на общую шину, что обеспечивает практическое отсутствие входного тока в течение второго такта преобразования через резистор 7 и конденсатор 10. Это обеспечивает протекание через резистор 7 и конденсатор 10 входного тока только в течение длительности первого такта преобразования. В первом такте происходит накопление заряда конденсатором 10, при этом уровень напряжения на выходе 57 операционного усилителя 9 пропорционален интегралу от входного электрического тока (фиг. 2 b).

В течение первого такта преобразования на третьем выходе 58 блока тактирования и управления 39 формируется положительный уровень напряжения (фиг. 2 f), который поступает на управляющий вход 38 блока ключевых элементов 26 коммутируемой диодно-резистивной схемы заряда 60, приводя ключевые элементы 32 и 36 в состояние 33' и 35' соответственно. При этом выводы 27 и 31 блока ключевых элементов 26 замыкаются на общую шину, и разряд запоминающей емкости 15 возможен током, величина которого ограничена входным сопротивлением неинвертирующего входа 62 операционного усилителя 9 и сопротивлением диода 24, включенного в обратном направлении. Это обеспечивает сохранение заряда на запоминающей емкости 15 (фиг. 2 е), имеющегося на ней к моменту начала первого такта преобразования. Величина емкости 15 выбирается исходя из максимально допустимой погрешности преобразования, которая однозначно связана с величиной уменьшения заряда на ней, обусловленного утечками за время цикла преобразования. Токи от источника Е1 через резистор 22 и ключевой элемент 32, и от источника Е2 через резистор 25 и ключевой элемент 36 утекают в общую шину. В результате на емкости 15 в первом такте устанавливается напряжение, отличающееся от напряжения на нулевой шине на величину, не более напряжения, при котором откроется либо диод 23, либо диод 24.

Поскольку в течение первого такта преобразования операционный усилитель 9 находится в линейном режиме, а входной ток неинвертирующего входа 62 операционного усилителя 9 мал, то на запоминающей емкости 15, неинвертирующем входе 62 и инвертирующем входе 61 устанавливаются очень близкие постоянные потенциалы, что обеспечивает протекание входного тока через резистор 7 и соответствующее накопление заряда на конденсаторе 10. Это приводит к изменению напряжения на выходе операционного усилителя 9 (фиг. 2b).

В первом такте преобразования на втором выходе 66 блока тактирования и управления 39 формируется отрицательный уровень напряжения (фиг. 2 d), из-за чего блок включения/выключения источника тока разряда 19 и блок кодирования 42 находятся в исходном состоянии, не формируя сигнал на включение источника тока разряда емкости интегратора 16, запрещая прохождение через схему И 47 импульсов осциллятора 44 и приводя счетчик 50 в исходное состояние.

Во втором такте преобразования на первом выходе 59 блока тактирования и управления 39 (фиг. 2 а) и втором выходе 66 этого же блока 39 (фиг. 2 d) устанавливаются положительные уровни напряжения, разрешая блоку включения/выключения источника тока разряда 19 включить генератор 16 тока разряда интегрирующей емкости 10, начать счет импульсов осциллятора 44 счетчиком 50, перевести ключевой элемент 4 в положение 30' при этом входной зажим 1 замыкается на общую шину. В результате входной ток начинает течь через ключевой элемент 4, а конденсатор 10 разряжается через резистор 8 током, определяемым генератором тока разряда 16. В течение времени разряда конденсатора 10 на третьем выходе 58 блока тактирования и управления 39 сохраняется положительный потенциал (фиг. 2 f), тем самым обеспечивая сохранение потенциала на запоминающей емкости 15, который был в первом такте преобразования. При этом напряжение на выходе 57 операционного усилителя 9 зависит только от заряда, накопленного конденсатором 10 к моменту окончания первого такта преобразования, и от разрядного тока, формируемого генератором тока разряда 16 (фиг. 2 b).

В момент достижения напряжением на выходе 57 операционного усилителя 9 уровня сравнения, задаваемого источником уровня сравнения 41, на выходе 43 компаратора 40 формируется импульс (фиг. 2 с), который поступает на вход 37 блока тактирования и управления 39, при этом на втором выходе 66 и третьем выходе 58 устанавливаются отрицательные потенциалы, сохраняющиеся до окончания второго такта преобразования. При этом блок включения/выключения источника тока разряда 19 формирует сигнал на приведение источника тока разряда 16 в исходное положение, при котором его ток, разряжающий конденсатор 10, становится равным нулю. Пороговый уровень источника уровня сравнения 41 выбирается таким, чтобы сравнение с ним выходного напряжения операционного усилителя 9 наступило при нахождении операционного усилителя 9 в линейном режиме.

Амплитудный компаратор 40, после момента сравнения напряжения на выходе 57 операционного усилителя 9 и порогового уровня источника уровня сравнения 41, фиксирует на входе 55 этот уровень напряжения. В результате на выходе 57 операционного усилителя 9 устанавливается постоянный потенциал, что обеспечивает линейность режима работы операционного усилителя 9 от момента сравнения до начала следующего цикла измерения, поэтому напряжения на его неинвертирующем входе 62 и инвертирующем входе 61 до конца текущего цикла измерения оказываются практически равными.

Работа коммутируемой диодно-резистивной схемы заряда 60 во втором такте преобразования осуществляется следующим образом.

От начала второго такта преобразования до момента появления импульса на выходе 43 амплитудного компаратора 40, на третьем выходе 58 блока тактирования и управления 49 сохраняется положительный уровень напряжения

При срабатывании амплитудного компаратора 40 и, соответственно, появлении отрицательного уровня напряжения на третьем выходе 58 блока тактирования и управления 39 (фиг. 2 f), этот уровень поступает на управляющий вход 38 блока ключевых элементов 26 коммутируемой диодно-резистивной схемы заряда 60, переводя ключевые элементы 32 и 36 в состояние 33 и 35 соответственно, размыкая соединенные до этого с общей шиной вывод 77 резистора 22 и вывод 73 резистора 25 коммутируемой диодно-резистивной схемы заряда 60. При этом в цепи резистор 22, диоды 23 и 24, резистор 25 коммутируемой диодно-резистивной схемы заряда 60 устанавливаются потенциалы, определяемые параметрами элементов этой цепи, напряжением источников питания E1 и Е2, процессами заряда-разряда запоминающей емкости С15 (фиг. 2 е). Сопротивления резистора 22 и резистора 25 выбираются таким образом, чтобы потенциал вывода 67 коммутируемой диодно-резистивной схемы заряда 60 был ниже потенциала, устанавливающегося на запоминающей емкости 15 к моменту появления импульса на выходе 43 амплитудного компаратора 40. В результате этот потенциал устанавливается на неинвертирующем входе 62 операционного усилителя 9. Соответственно, на неинвертирующем 62 и инвертирующем 61 входах формируются напряжения, близкие к напряжению на запоминающей емкости 15.

Изменение потенциала на инвертирующем входе 61 операционного усилителя 9 зависит не только от изменения потенциала на запоминающей емкости 15, но и от процесса уменьшения заряда на конденсаторе 10 от момента срабатывания компаратора 40 до момента окончания текущего цикла измерения и начала следующего цикла измерения. Поскольку конденсатор 10 включен в электрические цепи, создающие гальваническую связь, то происходит саморазряд конденсатора 10, в результате, поскольку напряжение на выходе 57 операционного усилителя 9 остается неизменным, то напряжение на инвертирующем входе 61 начинает возрастать до момента начала следующего цикла преобразования (фиг. 2е). При этом уровень напряжения, до которого уменьшается потенциал выхода 67 коммутируемой диодно-резистивной схемы заряда 60 после размыкания ключей 32 и 36 (положения 33 и 35 соответственно), выбирается таким, чтобы он не только был ниже уровня напряжения на запоминающей емкости 15, но и, в результате разряда конденсатора 10, к моменту начала следующего цикла измерения он был ниже потенциала нулевой шины.

Измерение малых электрических сигналов возможно, если в операционном усилителе 9 во входных цепях используются полевые транзисторы с малыми токами утечки. Описание работы схемы приведено для случая, когда в полевых входных транзисторах операционного усилителя 9 в затворах сформирован канал n-типа, при этом измеряемый ток втекает в измерительную цепь, состоящую из резистора 7 и конденсатора 10. Если необходимо измерить вытекающий ток, то используются операционные усилители с полевыми транзисторами с каналом p-типа. В этом случае в первом такте преобразования на запоминающей емкости 15 необходимо сформировать положительный (относительно нулевой шины) уровень напряжения. Для этого необходимо в коммутируемой диодно-резистивной схеме заряда 60 поменять номиналы резистора 22 и резистора 25. В этом случае при размыкании ключей 32 и 36 в коммутируемой диодно-резистивной схеме заряда 60, на выходе 57 операционного усилителя 9 формируется отрицательный уровень напряжения, емкость 10 в момент начала первого такта преобразования оказывается максимально заряженной, и вытекающий измеряемый ток в первом такте преобразования будет разряжать емкость 10, а напряжение на выходе 57 операционного усилителя 9 в первом такте преобразования будет возрастать.

В начале следующего цикла преобразования на третьем выходе 58 блока тактирования и управления 39 появляется положительный потенциал (фиг. 2 f), что приводит в блоке ключевых элементов 26 ключевые элементы 32 и 36 в состояние 33' и 35' соответственно. В этот момент из-за соответствующего выбора параметров резистора 22, резистора 25, емкости 10 и длительности второго такта преобразования, на запоминающей емкости 15 имеется отрицательный потенциал, меньший разности потенциалов на диодах 23 или 24 в открытом состоянии. В этом случае, из-за замыкания ключевых элементов 32 и 36 на общую шину, на выводе 78 диода 23 и выводе 75 диода 24 устанавливается потенциал общей шины, и диоды 23 и 24 закрываются. На запоминающей емкости 15 сохраняется потенциал от момента окончания текущего цикла преобразования до момента срабатывания амплитудного компаратора 40 во втором такте следующего цикла преобразования.

Таким образом, коммутируемая диодно-резистивная схема заряда 60 обеспечивает удержание потенциала на запоминающей емкости 15 от начала первого такта преобразования до момента сравнения, и удержание потенциала на ней в заданном диапазоне от момента сравнения до начала следующего цикла измерения, при этом подключение запоминающей емкости 15 через симметрирующий резистор 14 к неинвертирующему входу 62 операционного усилителя 9 позволяет установить на инвертирующем входе 61 потенциал, обеспечивающий устойчивую работу преобразователя даже при нулевом входном токе, и обеспечивает на выходе преобразователя такое значение цифрового кода, которое позволяет уменьшить относительную погрешность измерения до необходимой величины.

Подключение запоминающей емкости 15 к неинвертирующему входу 62 операционного усилителя 9 может быть использовано для симметрирования электрических цепей, подключаемых к входам операционного усилителя 9 путем подачи на неинвертирующий вход 62 операционного усилителя 9 электрического сигнала от действия электромагнитной помехи, улавливаемой антенной 13.

Симметричные электрические сигналы в предлагаемом устройстве действуют следующим образом.

Флуктуации напряжения на входе 1, появляющиеся из-за влияния электромагнитных помех, действующих в тракте до входного зажима 1, поступают на инвертирующий вход 61 вместе с измеряемой входной электрической величиной. Эти же флуктуации от действия электромагнитной помехи улавливаются антенной 13 и через резистор 12, сопротивление которого равно сопротивлению резистора 7, поступают на неинвертирующий вход 62 операционного усилителя 9. Сопротивление резистора 8 и сопротивление симметрирующего резистора 14 также выбираются одинаковыми. Вследствие одинаковости электрических цепей, соединенных с инвертирующим 61 и неинвертирующим 62 входами операционного усилителя 9, а также вследствие подключения к неинвертирующему входу 62 операционного усилителя 9 через резистор 12 антенны 13, на эти входы поступает одинаковая аддитивная помеха электромагнитной природы синфазно, что обеспечивает эффективное подавление этой помехи, поскольку операционный усилитель 9 имеет встроенные средства подавления синфазных помех.

Компенсирующий эффект от включения антенны 13 и резистора 12 в цепь неинвертирующего входа 62 операционного усилителя 9 возникает в первом такте цикла преобразования. Во втором такте из-за подключения этой цепи электромагнитная помеха действует на неинвертирующий вход 62 операционного усилителя 9, и ничем не компенсируется. Чтобы электромагнитная помеха, попадая на неинвертирующий вход 62 операционного усилителя 9, во втором такте преобразования не влияла на процесс разряда емкости 10, в схему вводится ключевой элемент 76. Он обеспечивает соединение вывода 63 резистора 12 и антенны 13 с нулевым потенциалом в течение второго такта преобразования. В первом такте преобразования ключевой элемент 76 размыкает соединение вывода 63 резистора 12 и антенны 13 с нулевой шиной, что обеспечивает уменьшение влияния электромагнитных помех на заряд емкости 10, как ранее было указано.

Работа ключевого элемента 76 осуществляется следующим образом. На управляющий вход 83 ключевого элемента 76 в первом такте поступает отрицательный перепад напряжения от первого выхода 59 блока тактирования и управления 39 (фиг. 2 а). В первом такте ключевой элемент 76 находится в положении 80, и электромагнитная помеха, улавливаемая антенной 13, через резистор 12 поступает на неинвертирующий вход 62 операционного усилителя 9. Во втором такте преобразования ключевой элемент 76 переводится в положение 80', и на вывод 63 резистора 12 вместо напряжения от действия электромагнитной помехи поступает нулевой потенциал, тем самым блокируя прохождение сигнала электромагнитной помехи на неинвертирующий вход 62 операционного усилителя 9.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ДВУХТАКТНОГО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ ИНТЕГРИРУЮЩЕГО ТИПА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2014 |

|

RU2564909C1 |

| ЦИФРО-АНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2015 |

|

RU2602396C1 |

| Цифро-аналоговый преобразователь | 2017 |

|

RU2648579C1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В ИНТЕРВАЛ ВРЕМЕНИ | 1991 |

|

RU2032269C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ ИЗМЕНЕНИЯ СОПРОТИВЛЕНИЯ РЕЗИСТИВНЫХ ДАТЧИКОВ В ЭЛЕКТРИЧЕСКИЙ СИГНАЛ | 2010 |

|

RU2499237C2 |

| АНАЛОГОВЫЙ ИНТЕГРАТОР | 2015 |

|

RU2602374C1 |

| МНОГОФУНКЦИОНАЛЬНЫЙ ПИКОВЫЙ ДЕТЕКТОР | 2019 |

|

RU2708687C1 |

| Аналоговое запоминающее устройство | 1990 |

|

SU1734123A1 |

| МНОГОКАНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ ПРИРАЩЕНИЯ СОПРОТИВЛЕНИЯ РЕЗИСТИВНЫХ ДАТЧИКОВ В НАПРЯЖЕНИЕ | 2015 |

|

RU2586084C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2007 |

|

RU2359403C1 |

Изобретение относится к области измерительной техники. Технический результат заключается в уменьшении относительной погрешности аналого-цифрового нелинейного преобразователя интегрирующего типа с двухтактным преобразованием. Аналого-цифровой преобразователь интегрирующего типа для измерения малых электрических сигналов включает вход (1), ключевой элемент (4), резисторы (7, 8, 12), операционный усилитель (9), конденсатор (10), компаратор (40), блок тактирования и управления (39) источником уровня сравнения (41), блок включения/выключения источника тока разряда (19), источника тока разряда емкости интегратора (16), симметрирующий резистор (14), запоминающую емкость (15), ключевой элемент (76), диодно-резистивную схему заряда (60), которая включает источники напряжения Е1, Е2, резисторы (22), (25), диоды (23), (24), блок ключевых элементов (26). Аналого-цифровой преобразователь также включает блок кодирования (42), который содержит осциллятор (44), логическую схему «И» (47), счетчик (50), а выход (54) является выходом аналого-цифрового преобразователя. 2 з.п. ф-лы, 2 ил.

1. Аналого-цифровой преобразователь интегрирующего типа для измерения малых электрических сигналов, содержащий операционный усилитель, инвертирующий вход которого соединен с конденсатором и входным резистором, при этом через эти входной резистор и конденсатор протекает измеряемый малый электрический ток, вход управляемого ключевого элемента соединен с входным зажимом, выход операционного усилителя соединен со вторым выводом конденсатора и первым входом компаратора, второй вход которого соединен с источником уровня сравнения, выход компаратора соединен со входом блока тактирования и управления, второй выход которого соединен со входом блока кодирования и входом блока включения/выключения источника тока разряда, выход которого соединен со входом источника тока разряда емкости интегратора, блок кодирования содержит осциллятор, выход которого соединен с одним входом логической схемы «И», второй вход которой соединен со входом блока кодирования, выход логической схемы «И» соединен со счетным входом счетчика, управляющий вход которого соединен со входом блока кодирования, а выход счетчика является выходом блока кодирования и выходом аналого-цифрового преобразователя, отличающийся тем, что в него введены запоминающая емкость, один вывод которой соединен с нулевой шиной, второй вывод запоминающей емкости через симметрирующий резистор соединен с неинвертирующим входом операционного усилителя, выход управляемого ключевого элемента соединен с нулевой шиной, а управляющий вход ключевого элемента соединен с первым выходом блока тактирования и управления, вход блока включения/выключения источника тока разряда соединен со входом блока кодирования, входной зажим соединен с общей точкой входного резистора и входом управляемого ключевого элемента, а выход источника тока разряда соединен с одним концом того резистора, который другим концом соединен с общей точкой входного резистора, конденсатора и инвертирующего входа операционного усилителя, введена также коммутируемая диодно-резистивная схема заряда запоминающей емкости, которая содержит первый резистор, одним концом соединенный с плюсом источника напряжения со средней точкой, которая соединена с нулевой шиной, второй конец соединен с плюсом первого диода, минус которого соединен с точкой соединения запоминающей емкости и плюса второго диода, минус которого соединен со вторым резистором, второй конец которого соединен с минусом источника напряжения, а также содержит блок из двух последовательно соединенных ключевых элементов, общая точка которых соединена с нулевой шиной, второй вывод одного ключевого элемента соединен с общей точкой первого диода и первого резистора, а второй вывод другого ключевого элемента соединен с общей точкой второго диода и второго резистора, управляющий вход блока ключевых элементов соединен с третьим выходом блока тактирования и управления.

2. Аналого-цифровой преобразователь интегрирующего типа для измерения малых электрических сигналов по п. 1, отличающийся тем, что введены антенна и резистор, одним концом соединенный с антенной, другим концом соединенный с неинвертирующим входом операционного усилителя, сопротивление этого резистора подбирается равным входному сопротивлению, а симметрирующее сопротивление подбирается равным сопротивлению, через которое течет ток разряда емкости интегратора.

3. Аналого-цифровой преобразователь интегрирующего типа для измерения малых электрических сигналов по п. 2, отличающийся тем, что введен второй ключевой элемент, вход которого соединен с общей точкой антенны и одного вывода резистора, выход ключевого элемента соединен с нулевой шиной, а управляющий вход соединен с первым выходом блока тактирования и управления.

| СПОСОБ ДВУХТАКТНОГО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ ИНТЕГРИРУЮЩЕГО ТИПА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2014 |

|

RU2564909C1 |

| ИЗМЕРИТЕЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ БЫСТРОДЕЙСТВУЮЩЕЙ ТЕНЗОМЕТРИЧЕСКОЙ СИСТЕМЫ | 2009 |

|

RU2424533C2 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 0 |

|

SU297125A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1234972A1 |

| US 20080074167 A1, 27.03.2008. | |||

Авторы

Даты

2019-07-03—Публикация

2018-02-14—Подача