Фи«,1

Изобретение относится к системам программного управления.

Цель изобретения - повышение на дежности устройства и расширение его функциональных возможностей.

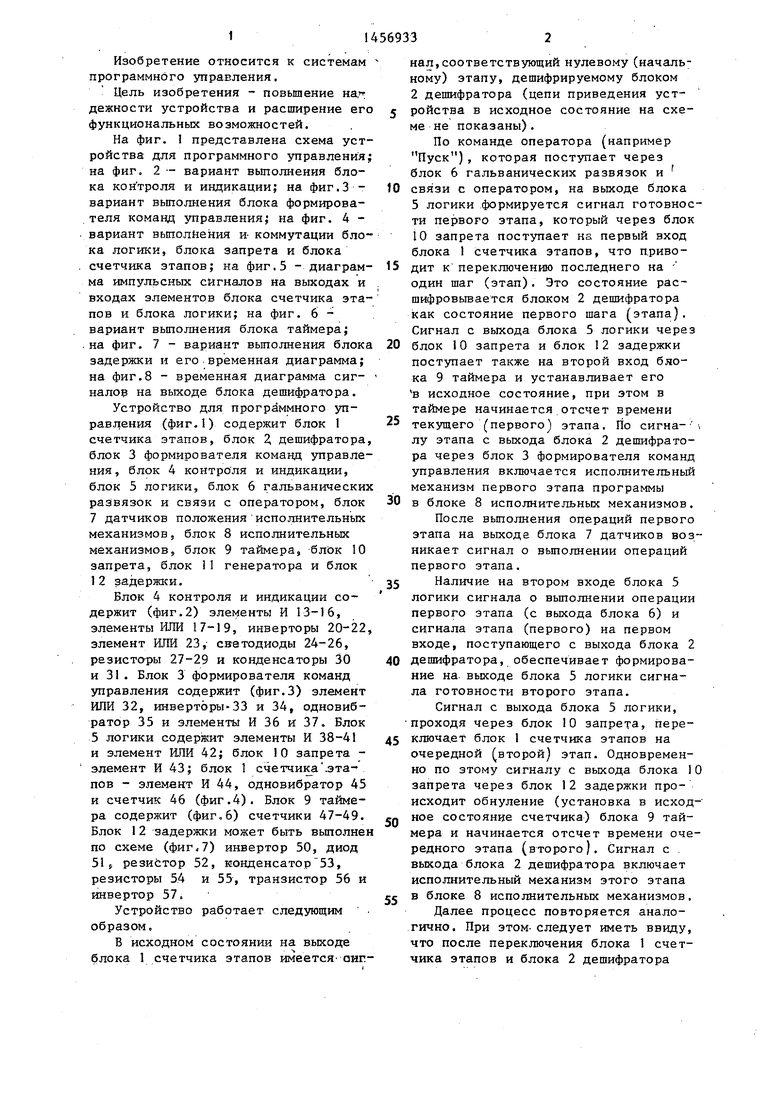

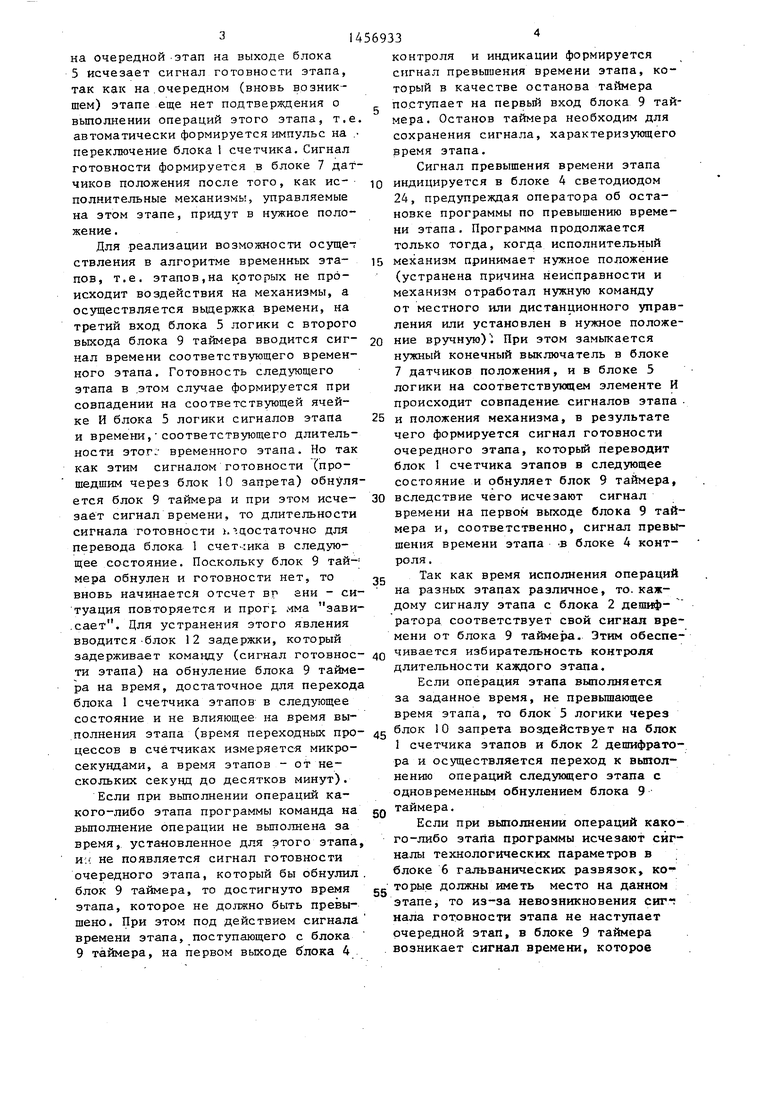

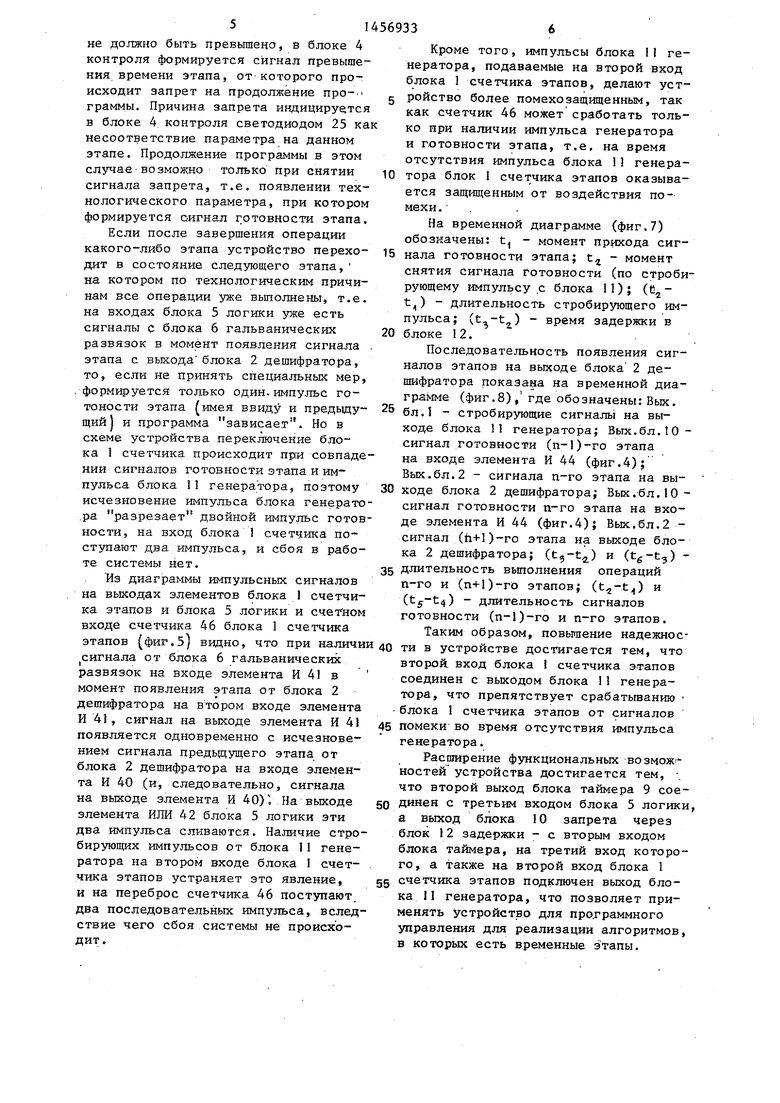

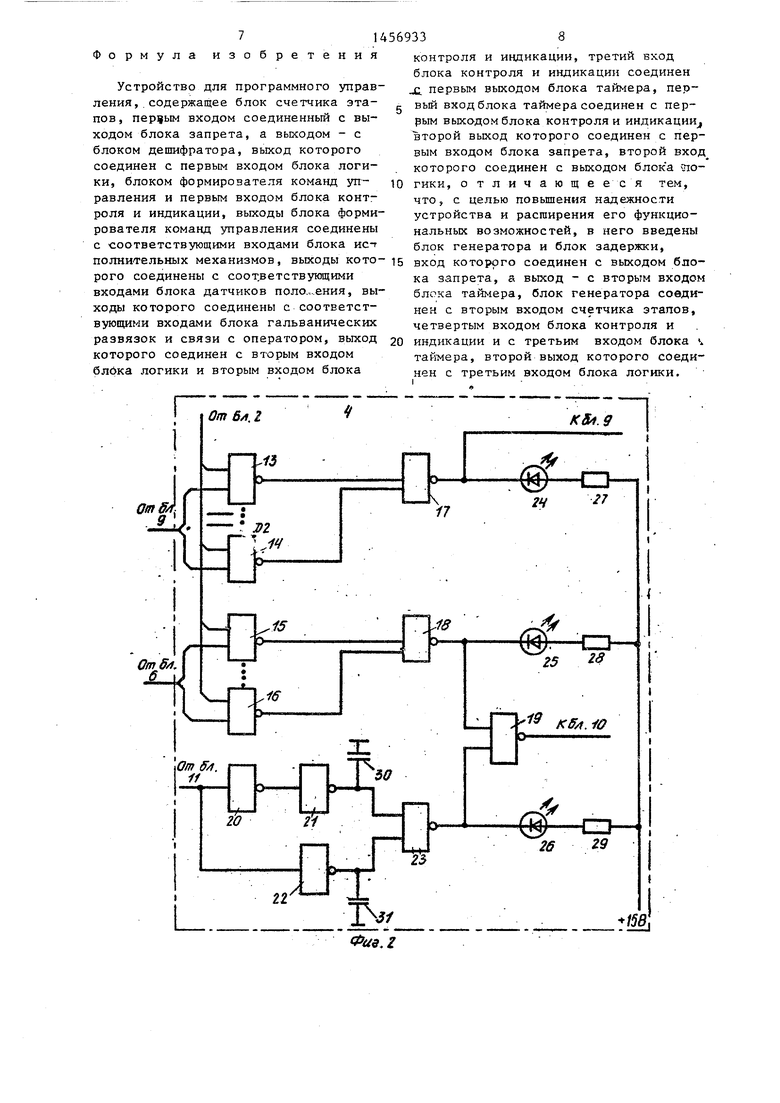

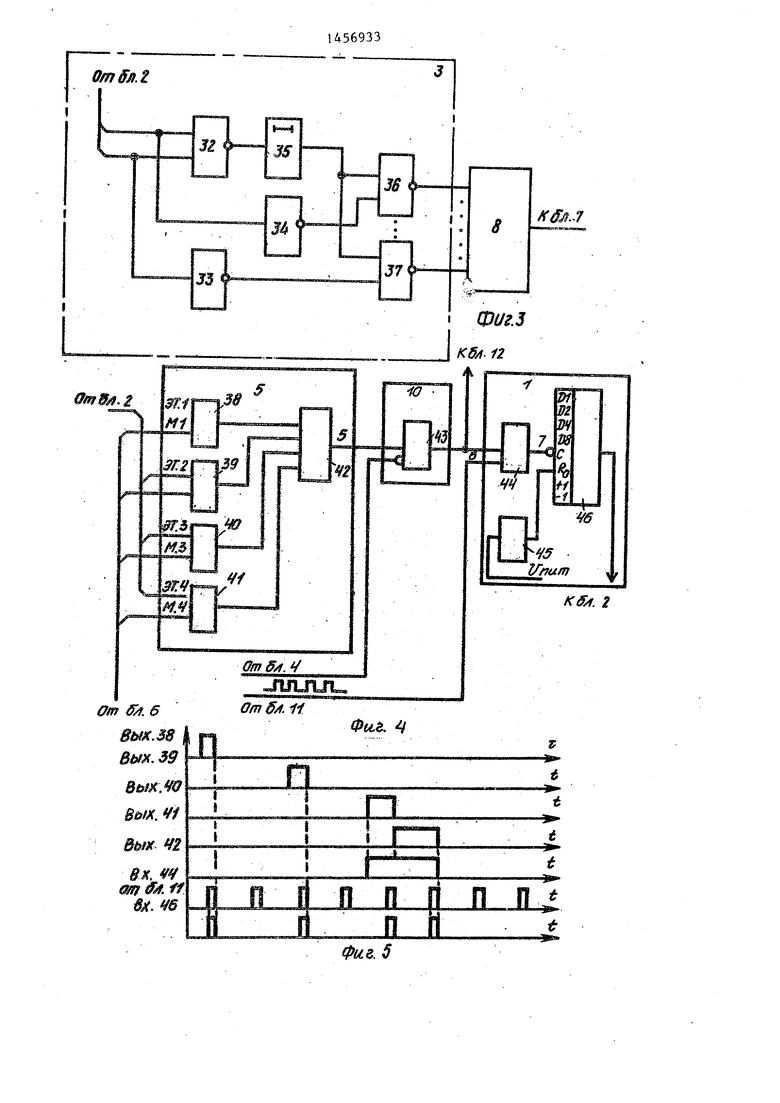

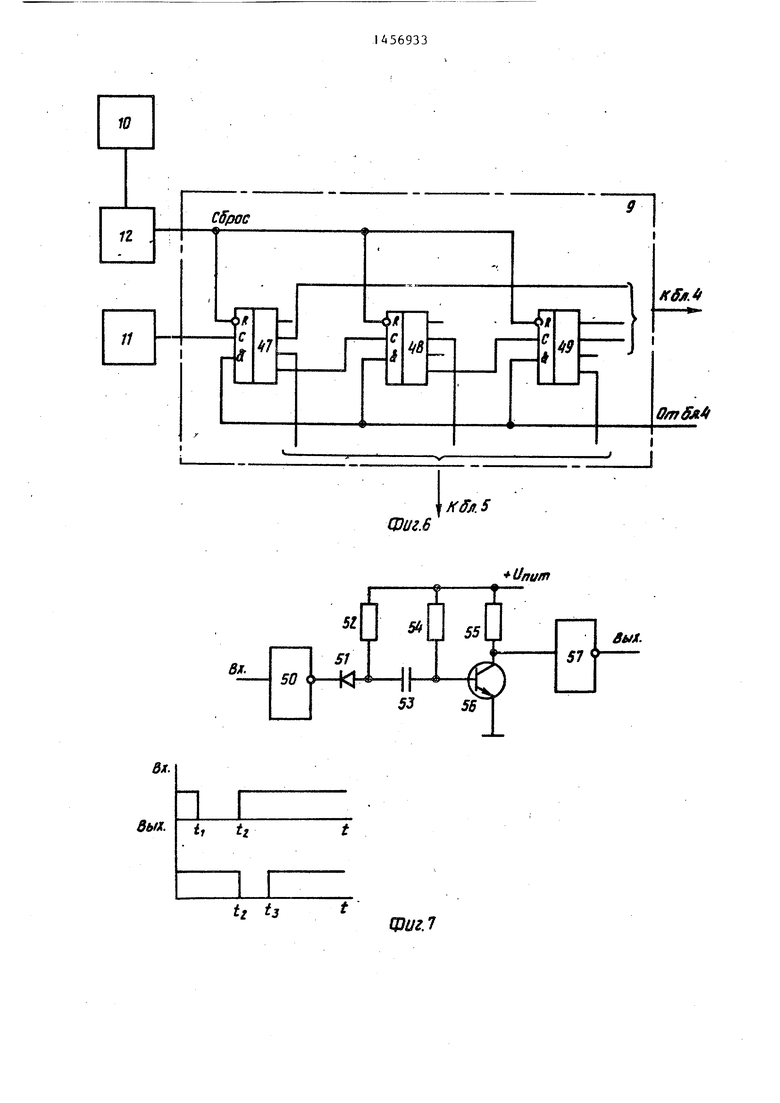

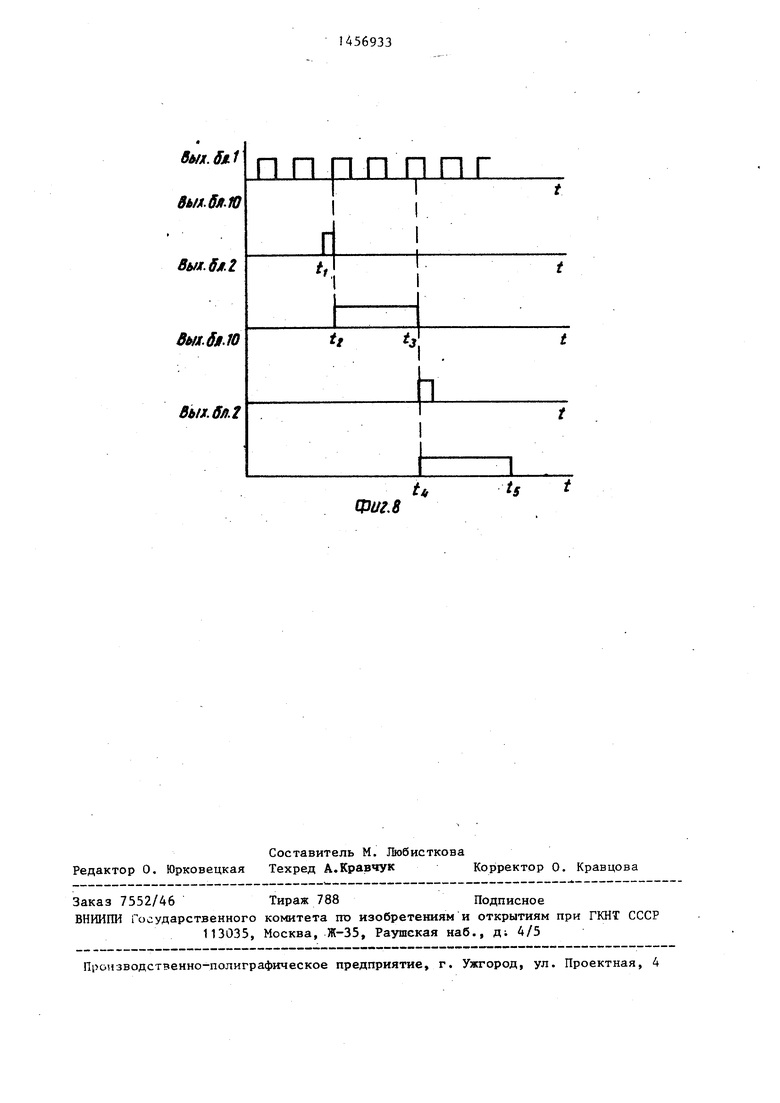

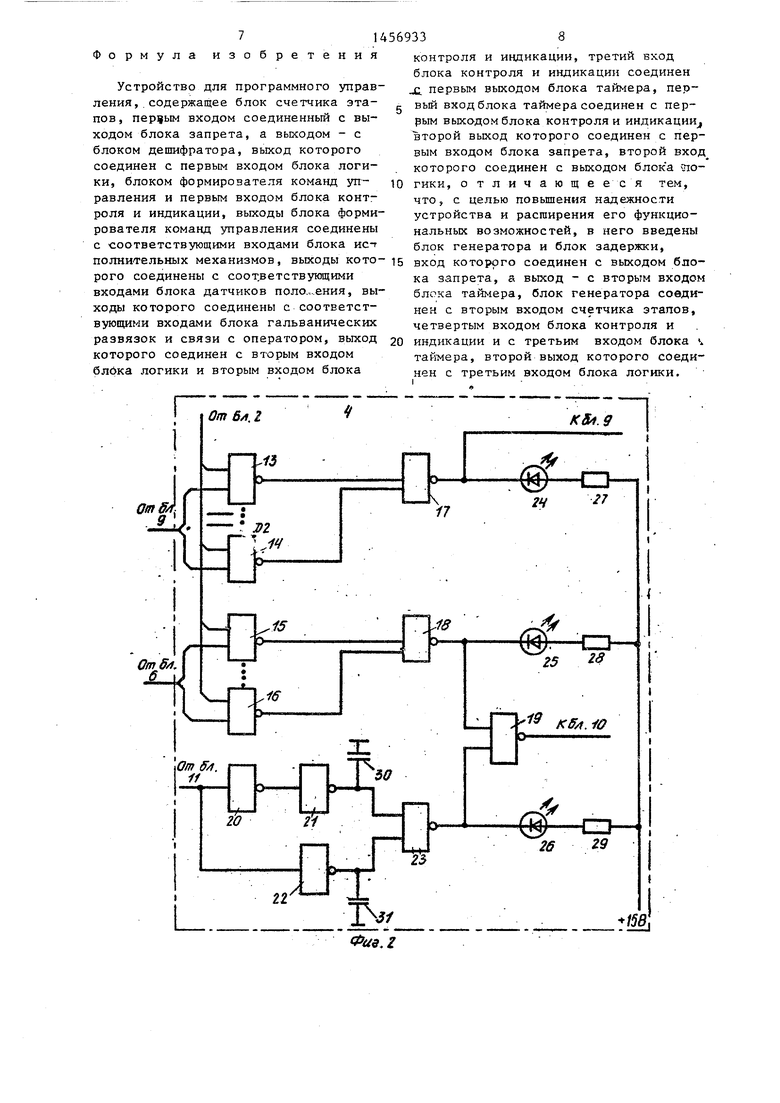

На фиг. 1 представлена схема устройства для программного управления; на фиг, 2 - вариант вьтолнения блока контроля и индикации; на фиг.З - вариант выполнения блока формирователя команд управления; на фиг. 4 - вариант выполнения и- коммутации бло ка логики, блока запрета и блока счетчика этапов; на фиг.З - диаграм- ма импульсных сигналов на выходах и входах элементов блока счетчика этапов и блока логики; на фиг. 6 - вариант выполнения блока таймера; на фиг, 7 - вариант вьтолнения блока задержки и его временная диаграмма; на фиг,8 - временная диаграмма сиг- налов на выходе блока дешифратора.

Устройство для программного управления (фиг,1) содержит блок 1 счетчика этапов, блок 2, дешифратора, блок 3 формирователя команд управления, блок 4 контроля и индикации, блок 5 логики, блок 6 гальванических развязок и связи с оператором, блок 7 датчиков положения исполнительных механизмов, блок 8 исполнительных механизмов, блок 9 таймера, блок 10 запрета, блок П генератора и блок 12 задержки,

Блок 4 контроля и индикации содержит (фиг,2) элементы И 13-16, элементы ИЛИ 17-19, инверторы 20-22, элемент ИЛИ 23, св етодиоды 24-26, резисторы 27-29 и конденсаторы 30 и 31, Блок 3 формирователя команд управления содержит (фиг.З) элемент ИЛИ 32, инверторы-33 и 34, одновиб- ратор 35 и элементы И 36 и 37, Блок 5 логики содержит элементы И 38-41 и элемент ИЛИ 42; блок 10 запрета - элемент И 43; блок 1 счетчика .этапов - элемент И 44, одновибратор 45 и счетчик 46 (фиг,4). Блок 9 таймера содержит (фиг,6) счетчики 47-49, Блок 12 задержки может быть выполнен по схеме () инвертор 50, диод 51 t резистор 52, к онденсатор 53, резисторы 54 и 55, транзистор 56 и инвертор 57.

Устройство работает следующим . образом,

Б исходном состоянии на выходе блока 1 счетчика этапов имеется оиг

0 5 0

5 0 5

0 5

5

нал,соответствующий нулевому (начальному) этапу, дешифрируемому блоком 2 дешифратора (цепи приведения устройства в исходное состояние на схеме не показаны).

По команде оператора (например Пуск), которая поступает через блок 6 гальванических развязок и связи с оператором, на выходе блока 5 логики формируется сигнал готовности первого этапа, который через блок 10 запрета поступает на первый вход блока 1 счетчика этапов, что приводит к переключению последнего на один шаг (этап). Это состояние расшифровывается блоком 2 дешифратора как состояние первого шага этапа). Сигнал с выхода блока 5 логики через блок 10 запрета и блок 12 задержки поступает также на второй вход блока 9 таймера и устанавливает его в исходное состояние, при этом в таймере начинается отсчет времени текущего (первого) этапа. По сигна- лу этапа с выхода блока 2 дешифратора через блок 3 формирователя команд управления включается исполнительньш механизм первого этапа программы в блоке 8 исполнительных механизмов.

После выполнения операций первого этапа на выходе блока 7 датчиков возникает сигнал о выполнении операций первого этапа.

Наличие на втором входе блока 5 логики сигнала о вьшолнении операции первого этапа (с выхода блока 6) и сигнала этапа (первого) на первом входе, поступающего с выхода блока 2 дешифратора, обеспечивает формирование на выходе блока 5 логики сигнала готовности второго этапа.

Сигнал с выхода блока 5 логики, проходя через блок 10 запрета, переключает блок 1 счетчика этапов на очередной второй) этап. Одновременно по этому сигналу с выхода блока 10 запрета через блок 12 задержки происходит обнуление (установка в исходное состояние счетчика) блока 9 таймера и начинается отсчет времени очередного этапа (второго). Сигнал с . выхода блока 2 дешифратора включает исполнительный механизм этого этапа в блоке 8 исполнительных механизмов.

Далее процесс повторяется аналогично. При этом- следует иметь ввиду, что после переключения блока 1 счетчика этапов и блока 2 дешифратора

на очередной -этап на выходе блока 5 исчезает сигнал готовности этапа, так как на.очередном (вновь возникшем) этапе еще нет подтверждения о выполнении операций этого этапа, т.е. автоматически формируется импульс на .- переключение блока I счетчика. Сигнал готовности формируется в блоке 7 датчиков положения после того, как исполнительные механизмы, управляемые на этом этапе, придут в нужное положение .

Для реализации возможности осуществления в алгоритме временных этапов, т.е. этапов,на к оторых не происходит воздействия на механизмы, а осуществляется вьщержка времени, на третий вход блока 5 логики с второго выхода блока 9 таймера вводится сигнал времени соответствующего временного этапа. Готовность следующего этапа в .этом случае формируется при совпадении на соответствующей ячейке И блока 5 логики сигналов этапа и времени, соответствующего длительности этог. временного этапа. Но так как этим сигналом готовности (прошедшим через блок 10 запрета) обнуля10

56933

контроля и индикации формируется сигнал превьппения времени этапа, который в качестве останова таймера (. поступает на первый вход блока 9 таймера. Останов таймера необходим для сохранения сигнала, характеризующего время этапа.

Сигнал превышения времени этапа индицируется в блоке 4 светодиодом 24, предупреждая оператора об остановке программы по превышению времени этапа. Программа продолжается только тогда, когда исполнительный механизм принимает нужное положение (устранена причина неисправности и механизм отработал нужную команду от местного или дистанционного управления или установлен в нужное положение вручную). При этом замыкается нужный конечный выключатель в блоке 7 датчиков положения, и в блоке 5 логики на соответствующем элементе И происходит совпадение сигналов этапа и положения механизма, в результате чего формируется сигнал готовности очередного этапа, который переводит блок 1 счетчика этапов в следующее состояние и обнуляет блок 9 таймера.

15

20

25

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для программного управления | 1984 |

|

SU1238034A1 |

| Устройство для программного управления | 1979 |

|

SU877475A1 |

| Устройство для ввода информации | 1983 |

|

SU1092485A1 |

| Устройство для ввода информации | 1983 |

|

SU1160386A1 |

| УСТРОЙСТВО ДЛЯ РЕГУЛИРОВАНИЯ РЕАКТИВНОЙ МОЩНОСТИ | 1991 |

|

RU2007814C1 |

| Устройство для ввода информации | 1982 |

|

SU1084771A1 |

| Устройство для контроля | 1986 |

|

SU1363169A1 |

| ЭЛЕКТРОННЫЙ ТАЙМЕР-ЗАДАТЧИК РИТМА | 1992 |

|

RU2012028C1 |

| Устройство для индикации | 1983 |

|

SU1161936A1 |

| СИСТЕМА КОНТРОЛЯ И УПРАВЛЕНИЯ ДЛИТЕЛЬНОСТЬЮ ТЕХНОЛОГИЧЕСКИХ ОПЕРАЦИЙ НА ЛИНИИ СТАЦИОНАРНЫХ ГАЛЬВАНИЧЕСКИХ ВАНН | 1987 |

|

RU1491053C |

Изобретене относится к системам программного управления. Цель изобретения - повышение надежно-.ти устройства и расширение его / жциональ ных возможностей. Устройство для про граммногр управления содержит блок 1 счетчика этапов, блок 2 дешифратора, блок 3 формирователя команд управления, блок 4 контроля и индикации, блок 5 логики, блок 6 гальванических развязок и связи с оператором, блок 7 датчиков положения исполнительных механизмов,блок 8 исполнительных механизмов, блок 9 таймера, блок 10 запрета, блок 11 генератора и блок 12 задержки. Повышение надежности в устройстве достигается тем. Что BTO.-I рой вход блока 1 счетчика этапов соединен с выходом блока 11 генератора, что препятствует срабатыванию блока 1 от сигналов помехи во время отсутствия импульса генератора. Расширение функциональных возможностей устройства достигается тем, что второй выход блока 9 таймера соединен с третьим входом блока 5 логики, а выход блока 10 запрета через блок 12 задержки - с вторым входом блока 5, на третий вход которого, а также на второй вход блока 1 подключен выход блока 1I, что позволяет примекять устройство для программного управления для реализации алгоритмов, в которых есть временные этапы. 8 ил. (Л с: ел со САЭ

ется блок 9 таймера и при этом исче- 30 вследствие чего исчезают сигнал

времени на первом выходе блока 9 мера и, соответственно, сигнал пр шения времени этапа .в блоке 4 ко роля .

зает сигнал времени, то длительности сигнала готовности ь .достаточно для перевода блока 1 счет-шка в следующее состояние. Поскольку блок 9 тай- мера обнулен и готовности нет, то вновь начинается отсчет вр гни - ситуация повторяется и nporj. мма зави- .сает. Для устранения этого явления

Так как время исполнения операций на разных этапах различное, то. каждому сигналу этапа с блока 2 дешифратора соответствует свой сигнал времени от блока 9 таймера. Этим обеспевводится-блок 12 задержки, который

задерживает команду (сигнал готовнос- 40 чивается избирательность контроля

ти этапа) на обнуление блока 9 тайме- длительности каждого этапа.

ра на время, достаточное для перехода

блока 1 счетчика этапов в следующее

состояние и не влияющее на время выЕсли операция этапа выполняется за заданное время, не превьшающее время этапа, то блок 5 логики через

полнения этапа (время переходных про- 45 ° ° запрета воздействует на блок

1 счетчика этапов и блок 2 дешифратоцессов в счётчиках измеряется микросекундами, а время этапов - от нескольких секунд до десятков минут). Если при вьшолнении операций какого-либо этапа программы команда на выполнение операции не выполнена за время, установленное для этого этапа, и;( не появляется сигнал готовности очередного этапа, который бы обнулил . блок 9 таймера, то достигнуто время этапа, которое не должно быть превышено. При этом под действием сигнала времени этапа, поступающего с блока 9 таймера, на первом выходе блока 4

50

55

ра и осуществляется переход к выполнению операций следукщего этапа с одновременным обнулением блока 9 таймера.

Если при выполнении операций какого-либо этапа программы исчезают сигналы технологических параметров в блоке 6 гальванических развязок, которые должны иметь место на данном этапе, то из-за невозникновения сигг нала готовности этапа не наступает очередной этап, в блоке 9 таймера возникает сигнал времени, которое

вследствие чего исчезают сигнал

времени на первом выходе блока 9 таймера и, соответственно, сигнал превышения времени этапа .в блоке 4 контроля .

Так как время исполнения операций на разных этапах различное, то. каждому сигналу этапа с блока 2 дешифратора соответствует свой сигнал времени от блока 9 таймера. Этим обеспе0

5

ра и осуществляется переход к выполнению операций следукщего этапа с одновременным обнулением блока 9 таймера.

Если при выполнении операций какого-либо этапа программы исчезают сигналы технологических параметров в блоке 6 гальванических развязок, которые должны иметь место на данном этапе, то из-за невозникновения сигг нала готовности этапа не наступает очередной этап, в блоке 9 таймера возникает сигнал времени, которое

51456933

не должно быть превышено, в блоке 4 контроля формируется сигнал превышения времени этапа, от которого происходит запрет на продолжение про-. граммы. Причина запрета индицируется в блоке 4 контроля светодиодом 25 как несоответствие параметра на данном этапе. Продолжение программы в этом случае-возможно только при снятии сигнала запрета, т.е. появлении, технологического параметра, при котором формируется сигнал готовности этапа. Если после завершения операции

10

Кроме того, импульсы блока 1I ге нератора, подаваемые на второй вход блока 1 счетчика этапов, делают уст 5 ройство более помехозащищенным, так как счетчик 46 может сработать только при наличии импульса генератора и готовности этапа, т.е. на время отсутствия импульса блока 1} генератора блок 1 счетчика этапов оказывается защищенным от воздействия помехи.

На временной диаграмме (фиг.7) обозначены: t - момент прихода ,.-ninDi. ,. - миминч прихода СИ какого-либо этапа устройство перехо- 15 нала готовности этапа; t/- момент

лит R Р.ПГ ТПЯ мгтр г ттргт г1лт( отйгта

дит В состояние следующего этапа, на котором по технологическим причинам все операции уже выполнены, т.е. на входах блока 5 логики уже есть сигналы с блока 6 гальванических развязок в момент появления сигнала этапа с выхода блока 2 дешифратора, то, если не принять специальных мер, сформируется только один, импульс го- тоности этапа (имея ввиду и предыду- 25 щий} и программа зависает. Но в схеме устройства переключение блока 1 счетчика происходит при совпадении сигналов готовности этапа и импульса блока iI генератора, поэтому исчезновение импульса блока генерато- .ра разрезает двойной импульс готовности, на вход блока 1 счетчика поступают два импульса, и сбоя в работе системы нет.

Из диаграммы импульсных сигналов . на выходах элементов блока 1 счетчика этапов и блока 5 логики и счетйом входе счетчика 46 блока 1 счетчика

снятия сигнала готовности (по строби рующему импульсу с блока II); ( ty,) - длительность стробирующего импульса; (t-j-t) - время задержки в

20 блоке 12.

Последовательность появления сигналов этапов на выходе блока 2 дешифратора показана на временной диаграмме (фиг.8), где обозначены: Вых. бл.1 - стробирующие сигналы на выходе блока П генератора; Вых.бл.Ю сигнал готовности (n-l)-ro этапа на входе элемента И 44 (фиг.4); Вых.бл.2 - сигнала п-го этапа на вы30 ходе блока 2 дешифратора; Вых.бл.Ю сигнал готовности п-го этапа на входе элемента И 44 (фиг.4); Вых.бл.2 - сигнал (ti+I)-го этапа на выходе блока 2 дешифратора; () и (tg-t,)

35 длительность выполнения операций п-го и (п+1)-го этапов; () и () - длительность сигналов готовности (n-l)-ro и п-го этапов. Таким образом, повьрление надежнос

/., ..лхаким ооразом, повьрление надежное

этапов (фиг 5 видно, что при наличии 40 ти в устройстве достигается тем, что

Г ТЛТ J-Ii3 ГТЯ 1 Т Т TTrtiy ГЗ f Г f ТГ Г: п f rrrrff f

сигнала от блока 6 гальванических развязок на входе элемента И 41 в момент появления этапа от блока 2 дешифратора на втором входе элемента И 4}, сигнал на выходе элемента И 41 появляется одновременно с исчезновением сигнала предьдущего этапа от блока 2 дешифратора на входе элемента И 40 (и, следовательно, сигнала на выходе элемента И 40); На выходе элемента ИЛИ 42 блока 5 логики эти два импульса сливаются. Наличие стро- бирующих импульсов от блока I1 генератора на втором входе блока 1 счетчика этапов устраняет это явление, и на переброс счетчика 46 поступают два последовательных импульса, вследствие чего сбоя системы не происходит.

второй, вход блока 1 счетчика этапов соединен с выходом блока 11 генератора, что препятствует срабатьшанию блока 1 счетчика этапов от сигналов 45 помехи во время отсутствия импульса генератора.

Расширение функциональных возмож ностей устройства достигается тем, - что второй выход блока таймера 9 сое50 динен с третьим входом блока 5 логики а выход блока 10 запрета через блок 12 задержки - с вторым входом блока таймера, на третий вход которого, а также на второй вход блока 1

55 счетчика этапов подключен выход блока П генератора, что позволяет применять устройство для программного управления для реализации алгоритмов, в которых есть временные этапы.

0

Кроме того, импульсы блока 1I генератора, подаваемые на второй вход блока 1 счетчика этапов, делают уст- 5 ройство более помехозащищенным, так как счетчик 46 может сработать только при наличии импульса генератора и готовности этапа, т.е. на время отсутствия импульса блока 1} генератора блок 1 счетчика этапов оказывается защищенным от воздействия помехи.

На временной диаграмме (фиг.7) обозначены: t - момент прихода ,.-ninDi. ,. - миминч прихода СИ 5 нала готовности этапа; t/- момент

j4-x,.-ninDi. ,. - миминч прихода СИ нала готовности этапа; t/- момент

снятия сигнала готовности (по строби- рующему импульсу с блока II); ( ty,) - длительность стробирующего импульса; (t-j-t) - время задержки в

блоке 12.

Последовательность появления сигналов этапов на выходе блока 2 дешифратора показана на временной диаграмме (фиг.8), где обозначены: Вых. бл.1 - стробирующие сигналы на выходе блока П генератора; Вых.бл.Ю- сигнал готовности (n-l)-ro этапа на входе элемента И 44 (фиг.4); Вых.бл.2 - сигнала п-го этапа на выходе блока 2 дешифратора; Вых.бл.Ю- сигнал готовности п-го этапа на входе элемента И 44 (фиг.4); Вых.бл.2 - сигнал (ti+I)-го этапа на выходе блока 2 дешифратора; () и (tg-t,) длительность выполнения операций п-го и (п+1)-го этапов; () и () - длительность сигналов готовности (n-l)-ro и п-го этапов. Таким образом, повьрление надежносхаким ооразом, повьрление надежное

ти в устройстве достигается тем, что

ти в устройстве достигается тем, что

второй, вход блока 1 счетчика этапов соединен с выходом блока 11 генератора, что препятствует срабатьшанию блока 1 счетчика этапов от сигналов помехи во время отсутствия импульса генератора.

Расширение функциональных возмож ностей устройства достигается тем, - что второй выход блока таймера 9 соединен с третьим входом блока 5 логики, а выход блока 10 запрета через блок 12 задержки - с вторым входом блока таймера, на третий вход которого, а также на второй вход блока 1

счетчика этапов подключен выход блока П генератора, что позволяет приенять устройство для программного управления для реализации алгоритмов, которых есть временные этапы.

71

Формула изобретения

Устройство для программного управ ления, содержащее блок счетчика этапов, первым входом соединенный с выходом блока запрета, а выходом - с блоком дешифратора, выход которого соединен с первьсм входом блока логики, блоком формирователя команд управления и первым входом блока контроля и индикации, выходы блока форми рователя команд управления соединены с соответствующими входами блока ис-т полнительных механизмов, выходы кото рого соединены с соот.ветствующими входами блока датчиков поло.,..ения, вы ходы которого соединены с соответствующими входами блока гальванических развязок и связи с оператором, выход которого соединен с вторым входом блбка логики и вторым входом блока

569338

контроля и индикации, третий вход блока контроля и индикации соединен -С. первым выходом блока таймера, пер- g вый вход блока таймера соединен с пер- рым выходом блока контроля и индикации второй выход которого соединен с первым входом блока запрета, второй вход которого соединен с выходом блок а 7IO- 10 гики, отличающе ее я тем, что, с целью повышения надежности устройства и расширения его функциональных возможностей, в него введены блок генератора и блок задержки,

15 вход которого соединен с вькодом блока запрета, а выход - с вторым входом блока таймера, блок генератора соединен с вторым входом счетчика этапов, четвертым входом блока контроля и 20 индикации и с третьим входом блока таймера, второй выход которого соединен с третьим входом блока логики.

.Z

т ff/f. 6

8ЫХ.38 i .

0ЫХ.4 B&ix. VI

&Ш if I

8x, 4f

e.s

Отб/1.И

фиг. S

7

Фиг.З

ti t3

Щи г. 7

с(зиг,в

| Устройство для программного управления | 1979 |

|

SU877475A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство для программного управления | 1984 |

|

SU1238034A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1989-02-07—Публикация

1987-02-02—Подача