(54) УСТРОЙСТВО ДЛЯ .ИРОГРАММНОГО УПРАВЛЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для программного управления | 1984 |

|

SU1238034A1 |

| Устройство для программного управления | 1987 |

|

SU1456933A1 |

| Устройство для програмнного управления технологическим процессом | 1979 |

|

SU866540A1 |

| СИСТЕМА ТРЕВОЖНОЙ СИГНАЛИЗАЦИИ | 1994 |

|

RU2103744C1 |

| Устройство для контроля правильности включения канала управления технологическим оборудованием | 1981 |

|

SU1107108A1 |

| Система автоматического управления процессом крашения | 1987 |

|

SU1527344A1 |

| Устройство для ввода-вывода информации | 1983 |

|

SU1118995A1 |

| Устройство для программного управления намоточным станком | 1987 |

|

SU1451648A1 |

| Процессор программируемого контроллера | 1988 |

|

SU1550515A2 |

| УСТРОЙСТВО ДЛЯ АВАРИЙНОЙ И ПРЕДУПРЕДИТЕЛЬНОЙ СИГНАЛИЗАЦИИ | 1967 |

|

SU225035A1 |

Изобретение относится к системам программного управления, например, пуском турбин. Известно устройство для програм- . много управления, содержащее генератор импульсов, счетчик импульсов, дешифратор, блок задания программы, блок контроля и индикации, формирователь команд, блок памяти, коммутатор, блок совпадения, таймер, сумматор и схему сравнения flQ. Недостатками этого устройства являются низкая надежность и ограниченные функциональные возможности. Низкая надежность известного устройства обусловлена тем, что для осуществления кон.троля за ходом выполнения программы в нем используются отдельный блок памяти, хранящий начало текущего времен этапа, блок коммутатора, хранящий пост янную времени ме ханизма, бл оки совпадения черезкоторые посигналу блока задания про граммы проходят сигналы таймера,блок тай мера ({юрмируюший текущее время программы, в котором суммируются снгвалы блоков памяти и коммутатора, и блок сравнения сигналов сумматора и текущего времени. Болыиое количество разнообразных блоков снижает суммарную надежность устройства в целом. Ограничение функциональных возможностей устройства обусловлено тем, что в нем применен принцип синхронной обработки информации. В этом случае одвн этап программы обрабатывается всегда за одно и то же время, определяемое параметрами генератора, счетчика и дещифратрра. необходимости настройки счетчика, генератора и деши(})ратора на этапы гфограммы, имеющие наибольщую длительность, время выполнения всей программы завышается.Поэтому для объектов, в которых быстродействие упраалпюшего программного устройства нмеет решающее значение, это устройство не лрнгодно.

Наиболее близким к предлагаемому по технической сущности является устроство для программного управления, в котором на каждом этапе с помощью блока контроля осуществляется контроль работы устройства. Принцип работы устройства асинкронный, - каждый следующий этап обработки программы начинается после окончания предьщущего 2.

Недостатком известного устройства является понижение надежности из-за большого количества оборудования, которое пропорционально увеличивается с ростом- числа этапов. Так, например,к ждому этапу программы необходим свой элемент памяти. Для триддатидвух этапов программы требуется тридцать два элемента памяти, а для 2 этапов- 2 элементовпамяти. Кроме того, над ежкость устройства снижается из-за отсутствия обратной связи Между блоком логики и блоком памяти. При отсутствии такой связи, если происходит произвольное переключение исполнительных органо не соотв етствующих выполняемому этапу прозграммы, то возбужденная память переключается до окончания этапа программы и, следовательно, нарушается последовательность выполнения программы, что приводит к низкой надежности устройства.

Недостатком известного устройства является таюке его ограниченная функциональная возможность из-за ограниченности применения только для таких объектов, у которых на каждом этапе имеется одинаковое количество датчиков Входной информации.

Цель изобретения - повьшение надежности и расщирение функциональных воз можностей устройства.

Поставленная цель достигается тем, что в устройство для программного управления содержащее последовательно соединенные первый блок датчиков положения и блок логики . вторым входом соединенный с выходом второго блока датчиков положения, третьим входом- с первыми входами блока команд и блока контроля и индикации, введены последовательно соединенные блок счетчиков и дешифратор и последовательно соединенные таймер и блок запрета, выходом подключенный ко второму входу блока команд, вторым входом через блок контроля и индикации- к выходу таймера, входом соединенного с выходом блока логики и входом блока счетчиков, а вы ход дешифратора соединен с первыми

Входами блока контроля и индикации и блока команд.

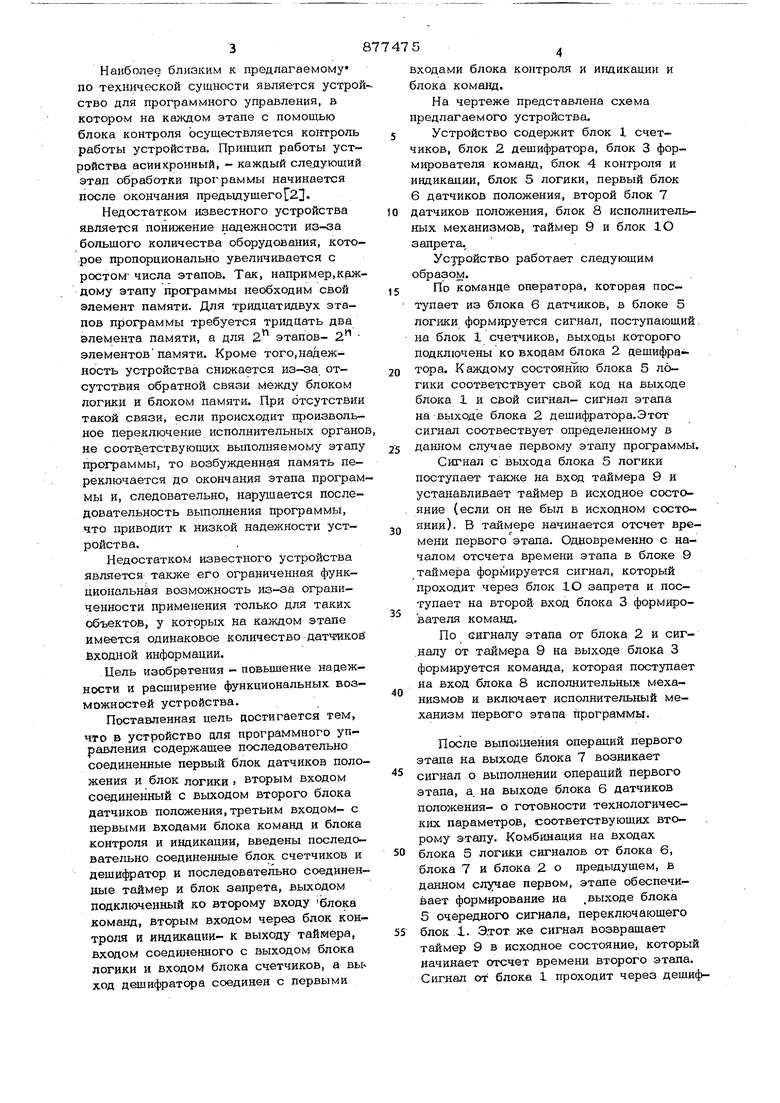

На чертеже представлена схема предлагаемого устройства.

Устройство содержит блок 1 счетчиков, блок 2 дешифратора, блок 3 формирователя команд, блок 4 контроля и индикации, блок 5 логики, первый блок 6 датчиков положения, второй блок 7 датчиков положения, блок 8 исполнительных механизмов, таймер 9 и блок Ю запрета.

Устройство работает следующим образом.

По команде оператора, которая поступает из блока 6 датчиков, в блоке 5 лопжи форгмируется сигнал, поступающий. на блок 1 счетчиков, выходы которого подключены ко входам блока 2 дешифра тора. Каждому состоянйю блока 5 логики соответствует свой код на выходе блока 1 и свой сигнал- сигнал этапа на выходе блока 2 дешифратор а. Этот сигнал соотвествует определенному в данном случае первому этапу программы.

Сигнал с выхода блока 5 логики поступает таклсе на вход таймера 9 и устанавливает таймер в исходное состо. яние (если он не был в исходном состоянии). В таймере начинается отсчет времени первого этапа. Одновременно с началом отсчета времени этапа в блоке 9 таймера формируется сигнал, который проходит через блок Ю запрета и поступает на второй- вход блока 3 формирователя команд.

По сигналу этапа от блока 2 и сигналу от таймера 9 на выходе блока 3 формируется команда, которая поступает на вход блока 8 исполнительны механизмов и включает исполнительный механизм первого этапа программы.

После выполнения операций первого этапа на выходе блока 7 возникает сигнал о выполнении операций первого этапа, а. на выходе блока 6 датчиков положения- о готовности технологических параметров, соответствующих второму этапу. Комбинация на входах блока 5 логики сигналов от блока 6, блока 7 и блока 2 о предьодущем, в данном случае первом, этапе обеспечивает формирование на .выходе блока 5 очередного сигнала, переключающего блок 1. Этот же сигнал возвращает таймер 9 в исходное состояние, которы начинает отсчет времени второго этапа Сигнал от блока 1 проходит через деши5ратор на выходе которого появляется сигнал второго этапа. В блоке 3 формируется команда на выполнение операций Второго этапа. Далее процесс повторяется аналогично. Если при выполнении операций какого либо этапа программы эти операции не будут выполнены за-время, определяемое комбинациями сигналов от таймера 9 и дешифратора (это сигнал этапа), то на выходе блока 4 формируется сигнал запрета, поступающий на блок 1О запрета продолжения программы.Этот сигнал не разрешает пройти сигналу с . таймера на блок 3. Однов|зе.мейно в блоке 4 индицируется причина приостановки программы. Так как время исполнения разных этапов различное, то каждому сигналу времени этапа, поступающему из таймер 9 в блок 4 контроля, соответствует свой сигнал этапа из дешефратора. Этим обеспечивается избирательность контрол длительности каждого этапа. ЕСЛИ операция этапа выполняется за заданное время, не превышающее время настройки таймера для данного этапа, то блок 5 логики осуществляет переход к вьшолнению операций следующего этап с регенерацией таймера, как это было описано выше. Наличие в блоке 1 счетчика п разрядов памяти позволяет реализовать в предлагаемом устройстве программу, состоящую из 2 этапов. Таким образом, повышение надежности в устройстве достигается за счет введения в устройство блока счетчика и блока дешифратора, а также тем, что выход дешифратора подключен ко входу блока логики, и блоку команд, а это препятствует са иопроизвольному переключению программы до окончания вьшол емого очередного этапа программы. 1 Расширение функциональных возмокностей устройства достигается тем, что соединение блоков не ограничивает количество датчиков входной информации на любом этапе выполнения программы и за счет введения в устройство блока Ю запрета продолжения программы, соединенного с таймером 9 блоком 4 контроля и индикации и блоком 3 команд, облегчается поиск неисправности при остановке программы в результате неисправности. Формула взобретения Устройство для программного управления, содержащее последовательно соединенные первый блок датчиков положения и блок логики, вторым входом соединенный с выходом блока датчиков положения, третьим вхсдаомс первыми входами блока команд и блока контроля и индикации, отличающееся тем,что, с целью повышения надежности и расширения функциональных возможностей устройства, в него введены последовательно соединенные блок счетчиков, и дешефратор и последовательТю соединенные таймер и блок запрета, выходом подключенный ко второму входу блока команд, вторым входом через блок контроля и индикации к выходу таймера, входом соединенного с выходом блока логики и входом блока счетчиков а выход дешефратора соединен с первыми входами блока контроля и. Е1ндикации и блока команд. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР N 594483, кл. Q О5 В 19/О8, 1975. 2.Авторское свидетельство СССР №557190, кл. F О1 D 19/ОО,1974. ( прототип);

Авторы

Даты

1981-10-30—Публикация

1979-08-09—Подача