1

Изобретение относится к преобразовательной технике и может найти применение в системах электропитания аппаратуры средств связи, измерительной и вычислительной техники.

Целью изобретения является повышение коэффи11иента полезного действия за счет уменьшения динамических, потерь в ключах демодулятора.

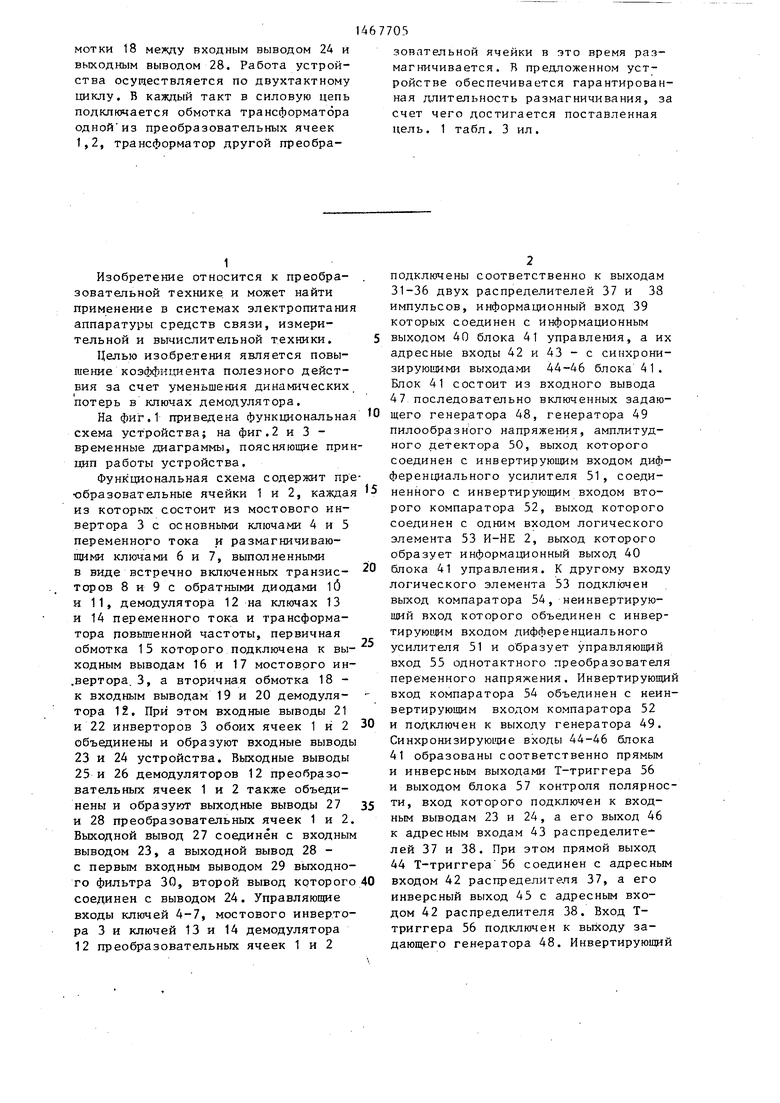

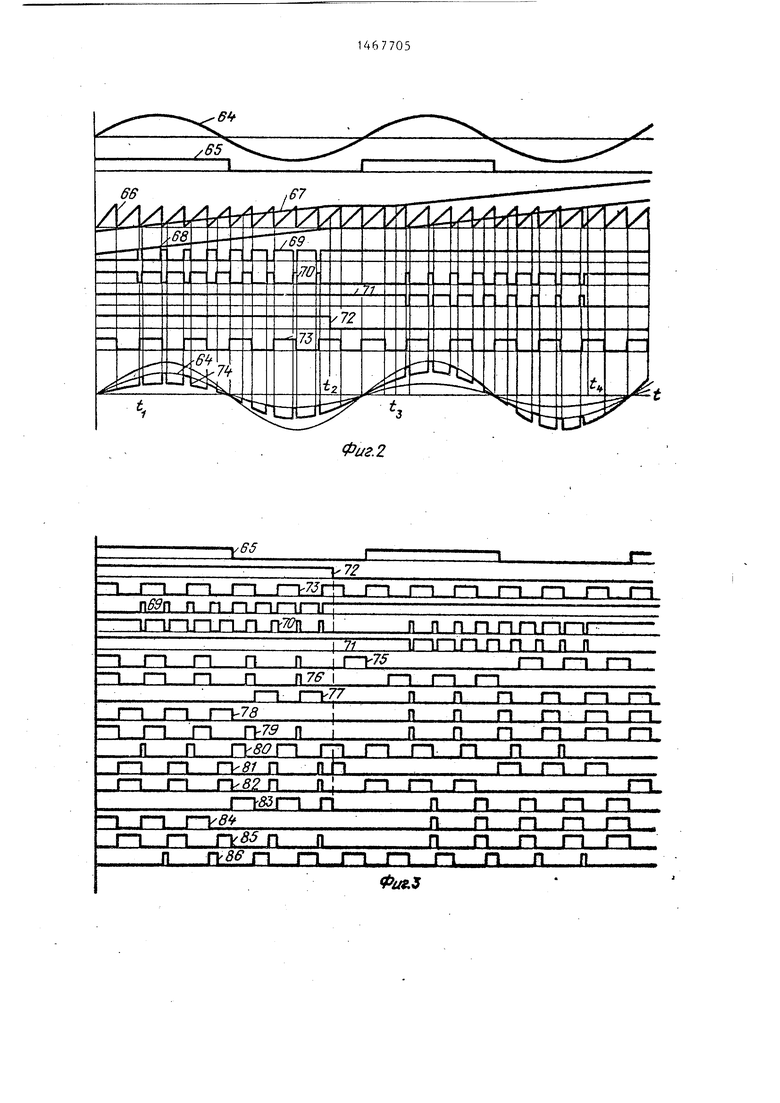

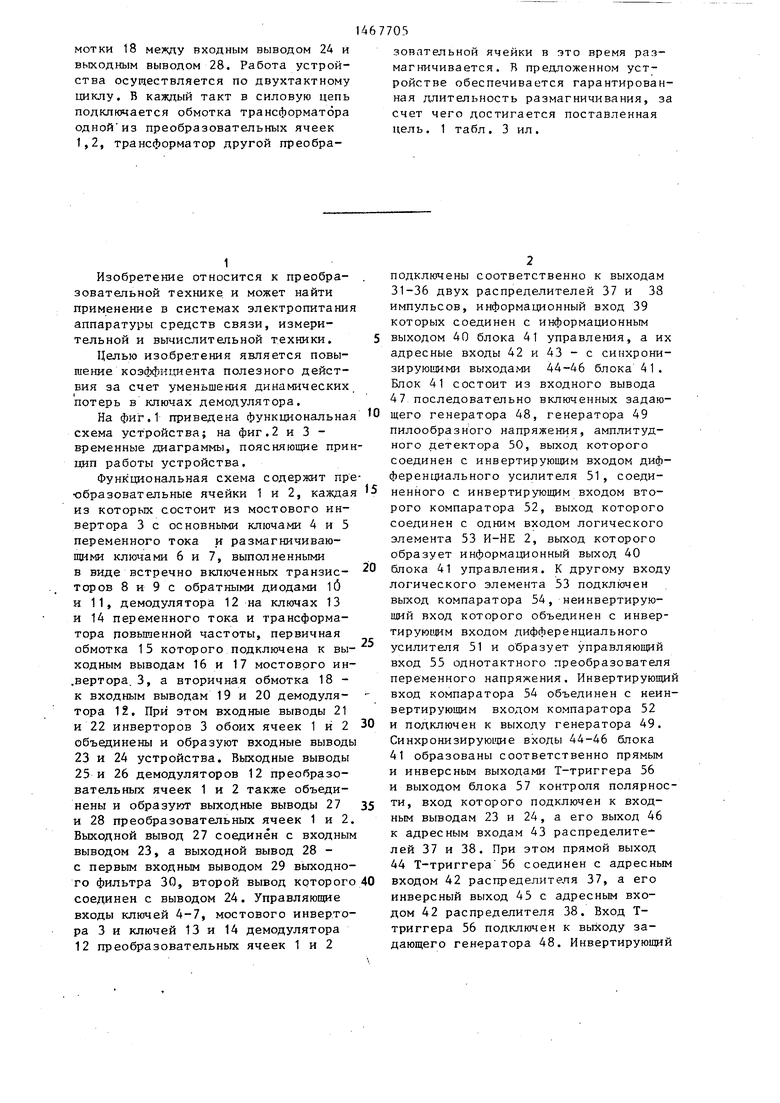

На фиг,1 приведена функциональная схема устройства; на фиг.2 и 3 - временные диаграммы, поясняющие прин цип работы устройства.

Функциональная схема содержит пре образовательные ячейки 1 и 2, каждая из которых состоит из мостового инвертора 3 с основными ключами 4 и 5 переменного тока и размагничивающими ключами 6 и 7, выполненными в виде встречно включенных транзисторов 8 и 9 с обратными диодами 16 и 11, демодулятора 12 на ключах 13 и 14 переменного тока и трансформатора повышенной частоты, первичная обмотка 15 которого подключена к выходным выводам 16 и 17 мостового ин- .вертора, 3, а вторичная обмотка 18 - к входным выводам 19 и 20 демодулятора 12. При этом входные выводы 21 и 22 инверторов 3 обоих ячеек 1 и 2 объединены и образуют входные выводы 23 и 24 устройства. Выходные выводы 25 и 26 демодуляторов 12 преобразовательных ячеек 1 и 2 также объединены и образуют выходные выводы 27 и 28 преобразовательных ячеек 1 и 2. Выходной вывод 27 соединен с входным выводом 23, а выходной вывод 28 - с первым входным выводом 29 выходного фильтра 30, второй вывод которого соединен с выводом 24. Управляющие входы ключей 4-7, мостового инвертора 3 и ключей 13 и 14 демодулятора 12 преобразовательных ячеек 1 и 2

10

5

0

5

0

5

0

подключены соответственно к выходам 31-36 двух распределителей 37 и 38 импульсов, информационный вход 39 которых соединен с информационным выходом 40 блока 41 управления, а их адресные входы 42 и 43 - с синхронизирующими выходами 44-46 блока 41. Блок 41 состоит из входного вывода 47 последовательно включенных задающего генератора 48, генератора 49 пилообразного напряжения, амплитудного детектора 50, выход которого соединен с инвертирующим входом диф- ферен1ф1ального усилителя 51 , соединенного с инвертирующим входом второго компаратора 52, выход которого соединен с одним входом логического элемента 53 И-НЕ 2, выход которого образует информационный выход 40 блока 41 управле дая. К другому входу логического элемента 53 подключен выход компаратора 54, неинвертирующий вход которого объединен с инвертирующим входом дифференциального усилителя 51 и образует управляющий вход 55 однотактного преобразователя переменного напряжения. Инвертирующий вход компаратора 54 объединен с неинвертирующим входом компаратора 52 и подключен к выходу генератора 49. Синхронизируюище входы 44-46 блока 41 образованы соответственно прямым и инверсным выходами Т-триггера 56 и выходом блока 57 контроля полярности, вход которого подключен к входным выводам 23 и 24, а его выход 46 к адресным входам 43 распределите лей 37 и 38. При этом прямой выход 44 Т-триггера 56 соединен с адресным входом 42 распределителя 37, а его инверсный выход 45 с адресным входом 42 распределителя 38. Вход Т- триггера 56 подключен к выходу задающего генератора 48. Инвертирующий

вход компаратора 58 подключен к выходу амплитудного детектора 50, не- инвертируюгаий - к управляющему входу 55, а его выход подключен к дополнительному адресному входу 59 распределителей 37 и 38. Каждый из основных ключей 4 и 5 инверторов 3 выполнен в виде встречно включенных транзисторов 60 и 61 с обратными диодами 62 и 63, выходные выводы 25 и 26 каждого из демодуляторов 12 образованы клеммами одного из ключей 14, при этом выходы 31 и 32 казвдого из распределителей 37 и 38 импульсов соединены с управляющими входами транзисторов 60 и 61 основных ключей 5 и 4, проводящих ток положительного и отрицательного направлений соответственно выходы 33 и 34 - с управляющими входами транзисторов 8 и 9 размагничивающих ключей 6 и 7 проводящих ток положительного и отрицательного направлений соответственно выход 35 - с управляющим входом ключа 13, включенного последовательно с вторичной обмоткой 18, а ; выход 36 - с управляюп1Им входом ключа 14, образующего выходные выводы 26 и 25 демодулятора 12. Кажды из распределителей 37 и 38 выполнен в виде логического блока, реализующего следующую таблицу истинности.

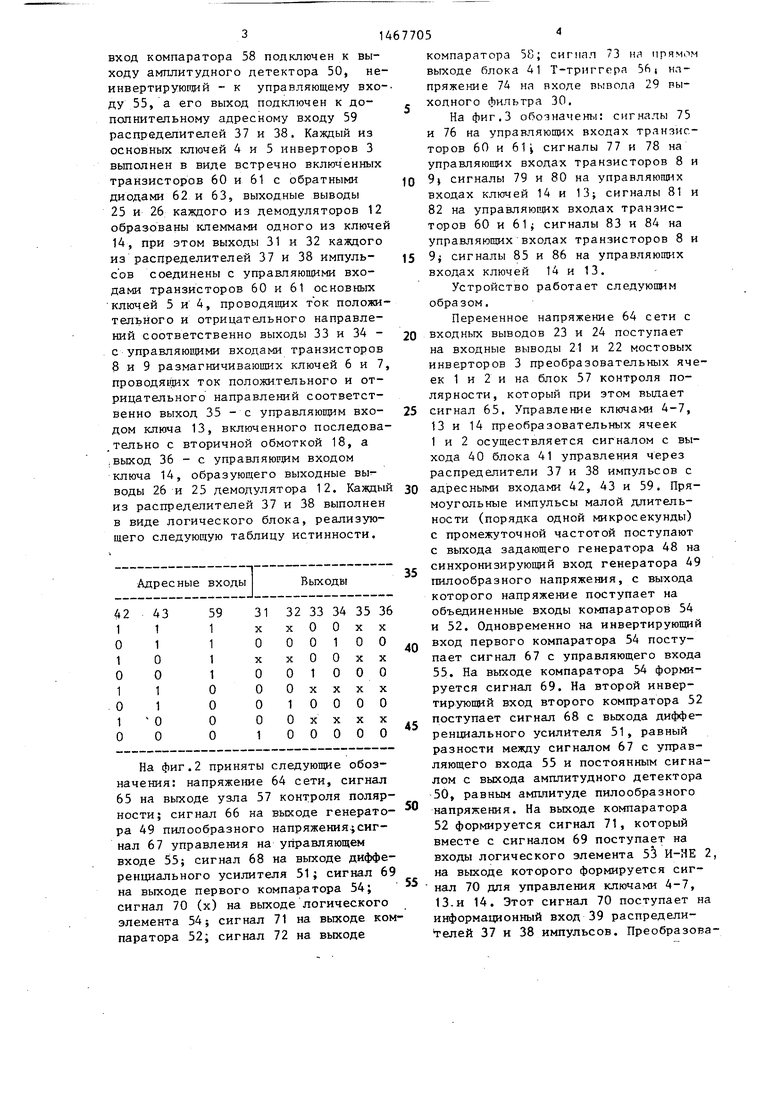

На фиг.2 приняты следующие обозначения: напряжение 64 сети, сигнал 65 на выходе узла 57 контроля полярности; сигнал 66 на выходе генератора 49 пилообразного напряжения}сигнал 67 управления на управляющем входе 55; сигнал 68 на выходе дифференциального усилителя 51; сигнал 69 на выходе первого компаратора 54; сигнал 70 (х) на выходе логического элемента 54; сигнал 71 на выходе компаратора 52; сигнал 72 на выходе

0

5

0

5

0

5

0

5

компаратора 58; сигнал 73 ня прямом выходе блока 41 Т-триггера 5fii ил- пряжение 74 на входе вывода 29 выходного фильтра 30.

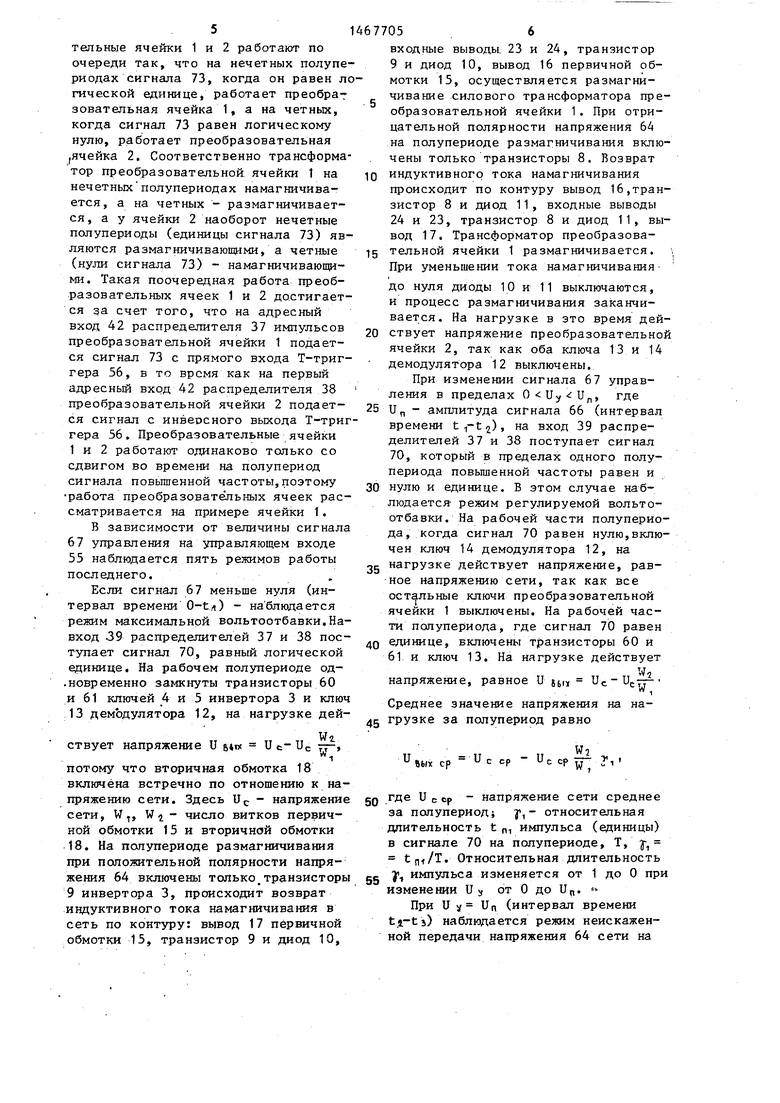

На фиг.З обозначены: сигналы 75 и 76 на управляющих входах транзисторов 60 и 61i сигналы 77 и 78 на управляющих входах транзисторов 8 и 9 сигналы 79 и 80 на управляющих входах ключей 14 и 13; сигналы 81 и 82 на управляющих входах транзисторов 60 и 61; сигналы 83 и 84 на управляющих входах транзисторов 8 и 9; сигналы 85 и 86 на управляющих входах ключей 14 и 13.

Устройство работает следующим образом.

Переменное напряжение 64 сети с входных выводов 23 и 24 поступает на входные выводы 21 и 22 мостовых инверторов 3 преобразовательных ячеек 1 и 2 и на блок 57 контроля полярности, который при этом вьщает сигнал 65. Управление ключами 4-7, 13 и 14 преобразовательных ячеек 1 и 2 осуществляется сигналом с выхода 40 блока 41 управления через распределители 37 и 38 импульсов с адресными входами 42, 43 и 59. Прямоугольные импульсы малой длительности (порядка одной микросекунды) с промежуточной частотой поступают с выхода задающего генератора 48 на синхронизирующий вход генератора 49 пилообразного напряжения, с выхода которого напряжение поступает на объединенные входы компараторов 54 и 52. Одновременно на инвертирующий вход первого компаратора 54 поступает сигнал 67 с управляющего входа 55. На выходе компаратора 54 формируется сигнал 69. На второй инвертирующий вход второго компратора 52 поступает сигнал 6В с выхода дифференциального усилителя 51, равный разности между сигналом 67 с управляющего входа 55 и постоянным сигналом с выхода амплитудного детектора 50, равным амплитуде пилообразного напряжения. На выходе компаратора 52 формируется сигнал 71, который вместе с сигналом 69 поступает на входы логического элемента 53 И-ИЕ 2, на выходе которого формируется сиг- нал 70 для управления ключами 4-7, 13. и 14. Этот сигнал 70 поступает на информационный вход 39 распредели- телей 37 и 38 импульсов. Преобразовательные ячейки 1 и 2 работают по очереди так, что на нечетных полупериодах сигнала 73, когда он равен лгической единице, работает преобразовательная ячейка 1, а на четньк, когда сигнал 73 равен логическому нулю, работает преобразовательная ячейка 2. Соответственно трансформатор преобразовательной ячейки 1 на нечетных полупериодах намагничивается, а на четных - размагничивается, а у ячейки 2 наоборот нечетные полупериоды (единицы сигнала 73) являются размагничивающими, а четные (нули сигнала 73) - намагничиваю1щ- ми. Такая поочередная работа преобразовательных ячеек 1 и 2 достигается за счет того, что на адресный вход 42 распределителя 37 импульсов преобразовательной ячейки 1 подается сигнал 73 с прямого входа Т-триг- гера 56, в то время как на первый адресный вход 42 распределителя 38 преобразовательной ячейки 2 подается сигнал с инверсного выхода Т-триг гера 56, Преобразовательные ячейки 1 и 2 работают одинаково только со сдвигом во времени на полупериод сигнала повьшенной частоты,поэтому работа преобразовательных ячеек рассматривается на примере ячейки 1.

В зависимости от величины сигнала 67 управления на управляющем входе 55 наблюдается пять режимов работы последнего.

Если сигнал 67 меньше нуля (интервал времени 0-tл) - на блюдается режим максимальной вольтоотбавки.На- вход 39 распределителей 37 и 38 поступает сигнал 70, равный логической единице. На рабочем полупериоде од- .повременно замкнуты транзисторы 60 и 61 ключей 4 и 5 инвертора 3 и ключ 13 демодулятора 12, на нагрузке дей

4677056

входные выводы. 23 и 24, транзистор 9 и диод 10, вывод 16 первичной обмотки 15, осуществляется размагничивание силового трансформатора преобразовательной ячейки 1. При отрицательной полярности напряжения 64 на полупериоде размагничивания включены только транзисторы 8. Возврат 10 индуктивного тока намагничивания

происходит по контуру вывод 16,транзистор 8 и диод 11, входные выводы 24 и 23, транзистор 8 и диод 11, вывод 17, Трансформатор преобразова- 15 тельной ячейки 1 размагничивается. При уменьшении тока намагничивания-

до нуля диоды 10 и 11 выключаются, и процесс размагничивания заканчивается. На нагрузке в это время дей20 ствует напряжение преобразовательной ячейки 2, так как оба ключа 13 и 14 демодулятора 12 выключены.

При изменении сигнала 67 управления в пределах , где

25 ип - амплитуда сигнала 66 (интервал времени ), на вход 39 распределителей 37 и 38 поступает сигнал 70, который в пределах одного полупериода повышенной частоты равен и

30 нулю и единице, В этом случае наблюдается режим регулируемой вольто- отбавки. На рабочей части полупериода, когда сигнал 70 равен нулю,включен ключ 14 демодулятора 12, на

25 нагрузке действует напряжение, равное напряжению сети, так как все остальные ключи преобразовательной

ячейки 1 выключены. На рабочей части полупериода, где сигнал 70 равен 40 единице, включены транзисторы 60 и 61 и ключ 13, На нагрузке действует

напряжение, равное U jf,,

1 Среднее значение напряжения на на45 грузке за попупериод равно

| название | год | авторы | номер документа |

|---|---|---|---|

| Регулируемый преобразователь переменного напряжения в переменное | 1986 |

|

SU1410234A2 |

| Устройство для регулирования напряжения | 1987 |

|

SU1443096A1 |

| Регулируемый преобразователь переменного напряжения в переменное | 1986 |

|

SU1372539A1 |

| Преобразователь напряжения с многозонной модуляцией | 1982 |

|

SU1086525A1 |

| Преобразователь @ -фазного напряжения с промежуточным ВЧ-преобразователем | 1985 |

|

SU1394370A1 |

| ПРОГРАММИРУЕМЫЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ | 1992 |

|

RU2020709C1 |

| Способ преобразования постоянного напряжения в переменное с регулированием его величины и устройство для преобразования постоянного напряжения в регулируемое переменное | 1979 |

|

SU959239A1 |

| Регулируемый преобразователь постоянного напряжения | 1985 |

|

SU1396216A1 |

| Стабилизированный источник вторичного электропитания | 1982 |

|

SU1049876A1 |

| Многоканальный стабилизированный источник вторичного электропитания | 1984 |

|

SU1166085A1 |

Изобретение относится к преобразовательной технике. Цель изобретения - повышение коэффициента полезного действия за счет уменыиеш-1я динамических потерь в ключах демодулятора. Устройство содержз1т преобразовательные ячейки 1, 2, каждая из которых содержит мостовой инвертор 3, с первичной обмоткой 15 трансформатора, включенной в его диагональ. Вторичная обмотка 18 трансформатора подключена к демодулятору 12. Регулирование напряжения осупествляется изменением относительного времени и направления включения вторичной об5 сл

и -и Hi

и с УС 77,

ствует напряжение U

потому что вторичная обмотка 18 включена встречно по отношению к напряжению сети. Здесь - напряжение сети, W:,, W - число витков первичной обмотки 15 и вторичной обмотки 18, На полупериоде размагничивания при положительной полярности напряжения 64 включены только транзисторы 9 инвертора 3, происходит возврат индуктивного тока намагничивания в сеть по контуру: вывод 17 первичной обмотки 15, транзистор 9 и диод 10,

ср

и

с ср

- и

W2 Р W ,

где и с ср - напряжение сети среднее за попупериод; у,- относительная длительность t импульса (единицы) в сигнале 70 на полупериоде. Т, , Относительная длительность у импульса изменяется от 1 до О при изменении UN, от О до U,,,

При и Un (интервал времени tj-ts) наблкщается режим неискаженной передачи напряжения 64 сети на

нагрузку, ji, О и напряжение на нагрузке, равное ивыгср Ucср На входе 39 распределителей 37 и 38 действует сигнал 70, равный логическому нулю. На рабочем полупериоде все время замкнут ключ 14 демодулятора 12, преобразовательные ячейки 1 и 2 все время отключены от сети. На полупериоде размагничивания все происходит так же как и ранее. При дальнейшем увеличении сигнала 67 и его изменении в пределах U (интервал времени tj-t) на входе 39 распределителей 37 и 38 действует сигнал .70, принимающий значение и 1, и О на каждом полупериоде сигнала повышенной частоты. При этом на части рабочего полупериода, где сигнал 70 принимает значение 1 замкнуты транзисторы 8 и 9 и ключ 13 демодулятора 12. На нагрузке действует напряжение равное сумме напряжения 64 сети и напряжения на вторичной обмотке 18 трансформатора преобразовательной ячейки 1, т.е.

и (,1х и .

потому что напряжение вторичной обмотки 18 включено согласно с напряжением сети. На части полупериода, где сигнал 70 равен нулю, включен ключ 14 демодулятора 12, на нагрузке действует напряжение сети, так как все ключи преобразовательной ячейки 1 выключены. Среднее значение напряжения на нагрузке равно

и с ср

+ и

с ср

Wi Wi

f.,

где

- относительная длительность

t (единицы) в сигнале 70 на полу- периоде Т, ti tna/T. Относительная длительность у импульса изменяется от О до 1 при изменении U у от U п до 2Un. При наблюдается режим максимальной вольтодобавки. На

рабочем полупериоде замкнуты постоян- Q инвертора, а вторичная - к входу де- но транзисторы 8 и 9 ключей 6 и 7 и ключ 13 демодулятора 12. На полупе- рирде размагничивания при положительной полярности напряжения 64 вклкг чены транзисторы 61 ключей 4 и 5,а 55 при отрицательной - транзисторы 60.

Реверс вольтодобавочного напряжения относительно нагфяжения 64 сети однозначно определяется Bej4H4HHoA

модулятора, при этом входы инверторо соединены с входными выводами, выходы демодуляторов объединены и образуют выходные выводы преобразователь ных ячеек, причем их первый выходной вывод соединен с первым входным выводом, а второй - с первым входным выводом выходного фильтра, второй входной вывод которого соединен с

0

0

5

сигнала 67 управления и режимом работы распределителей 37 и 38 импульсов. Так при сигнале на адресном входе 59 (режим вольтодобавки) сигнал 70 проходит на выход 31 и 32 и на выход 35. Сигнал размагничивания (это сигнал инверсный сигналу 73) поступает при положительной полярности напряжения 64 на выход 34, а при отрицательной полярности на выход 33. Сигнал 70 на рабочих полупериодах поступает на выход 36.

Режим неискаженной передачи дос- 5 тигается включением ключа 14, демодулятора 12, при этом ключ 13 разомкнут и таким образом предотвращается разряд собственной емкости обмотки через закороченный трансформатор,чем исключаются динамические потери и повышается коэффициент полезного действия.

Дополнительным положительным свойством предлагаемого однотактного преобразователя переменного напряжения является повышение эксплуатационной надежности работы из-за гарантированной длительности размагничивания, что позволяет изменять управляющий сигнал практически с неограниченной скоростью. Это приводит к увеличению быстродействия регулирования и стабилизации.

I 5 Формула изобретения

0

5

Однотактный преобразователь переменного напряжения, содержащий две преобразовательные ячейки, каждая из которых состоит из мостового инвертора с двумя основными ключами и двумя размагничивающими ключами, выполненными в виде встречно включенных транзисторов с обратныьш диодами демодулятора на ключах, причем все ключи выполнены двунаправленными пол ностью управляемыми, и трансформатора повышенной частоты, первичная обмотка которого подключена к выходу

0

инвертора, а вторичная - к входу де-

модулятора, при этом входы инверторов соединены с входными выводами, выходы демодуляторов объединены и образуют выходные выводы преобразовательных ячеек, причем их первый выходной вывод соединен с первым входным выводом, а второй - с первым входным выводом выходного фильтра, второй входной вывод которого соединен с

вторым входным выводом, управляющие входы ключей инвертора и демодулятора каждой из ячеек подклгочены соответственно к выходам двух распределителей импульсов, информационные входы которых соединены с информационным выходом блока управления, а их адресные входы - с синхронизирующими выходами блока управления, который состоит из последовательно включенных задающего генератора, генератора пилообразного напряжения, амплитудного детектора, выход которого соединен с инвертирующим входом диффе- ренциального усилителя, выходом соединенного с инвертирующим входом второго компаратора, выход которого соединен с одним входом логического элемента 2И-НЕ, выход которого образует информационный выход блока управления, а к его другому входу подключен выход.первого компаратора, неинвер- тируюпщй вход которого объединен с неинвертирующим входом дифференциаль- ного усилителя и образует управляющий вход, причем инвертирующий вход первого компаратора объединен с неин- вертируюшдм входом второго компаратора и подключен к выходу генератора пилообразного напряжения, при этом синхронизирующие выходы блока управления образованы соответственно прямым и инверсным выходами Т-триггера и выходом узла контроля полярности, вход которого подключен к входным выводам, а его вькод - к вторым адресным входам распределителей импульсов обоих преобразовательных ячеек, при этом прямой выход Т-триггера соеди- нен с первым адресным входом распре

5 0 5 О

5

делителя импульсов первой преобразовательной ячейки, его инверсный выход - с первым адресным входом распределителя импульсов второй преобразовательной ячейки, его вход подключен к выходу задающего генератора, отличающийся тем, что, с целью повышения коэффициента полезного действия за счет уменьшения динамических потерь в ключах демодулятора, введены третий компаратор, инвертирующий вход которого подключен к выходу амплитудного детектора,не- инвертируюший - к управляющему входу, а его выход подключен к введенному дополнительному адресному входу первого и второго распределителей импульсов, причем каждый из ключей инверторов выполнен в виде двух встречно включенных транзисторов с обратными диодами, выходные выводы каждого из демодуляторов образованы выводами одного из его ключей, при этом первый и второй выходы каждого из распределителей импульсов соединены соответственно казкдый с управляющими входами пары транзисторов одного направления основных ключей, третий и четвертый выходы соответственно каждый с управляющими входами пары транзисторов одного направления размагничивающих ключей, пятый выход - с управляющим входом ключа демодулятора, включенного последовательно с вторичной обмоткой трансформатора повышенной частоты, а шестой выход соединен с управляющим входом ключа, образующего выходные выводы демодулятора.

Фиг.2

| Регулятор напряжения | 1977 |

|

SU942237A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Регулируемый преобразователь переменного напряжения в переменное | 1986 |

|

SU1410234A2 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1989-03-23—Публикация

1987-08-31—Подача