Изобретение относится к электротехнике и может быть использовано в силовой преобразовательной технике для управления электроприводами, для обеспечения пониженной скорости движения их исполнительных органов.

Целью изобретения является повы- ,шение надежности работы при формировании квазисинусоидального напряжения пониженной в два раза частоты.

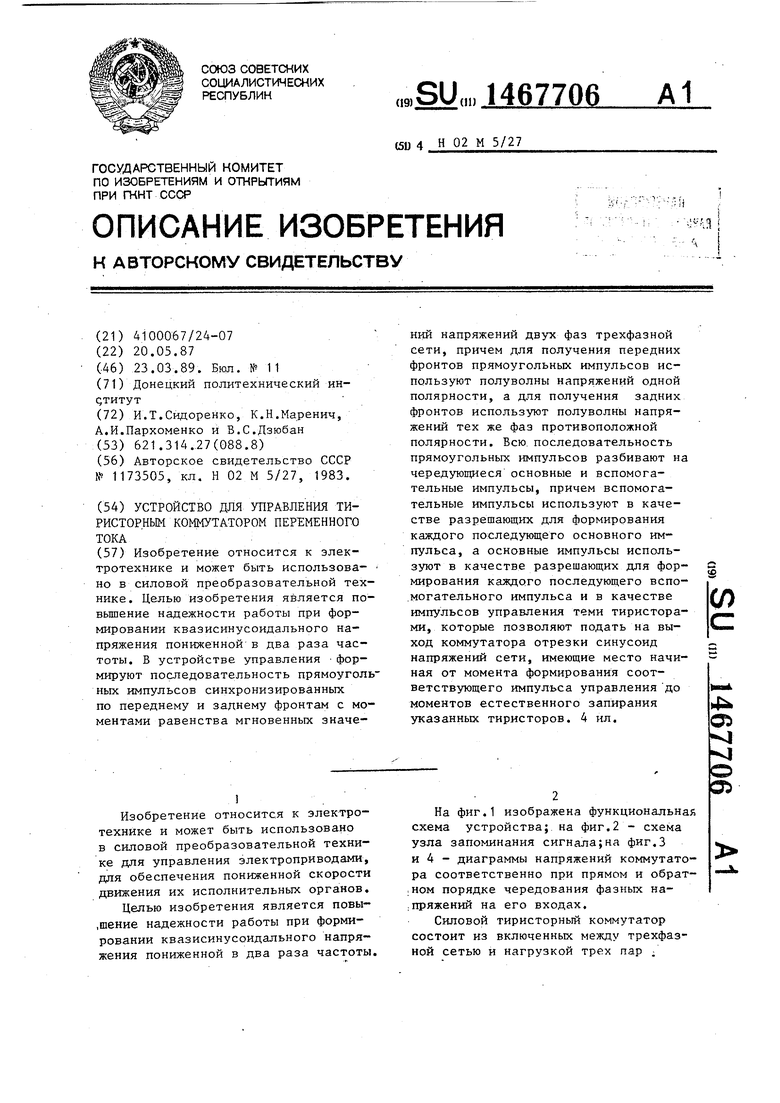

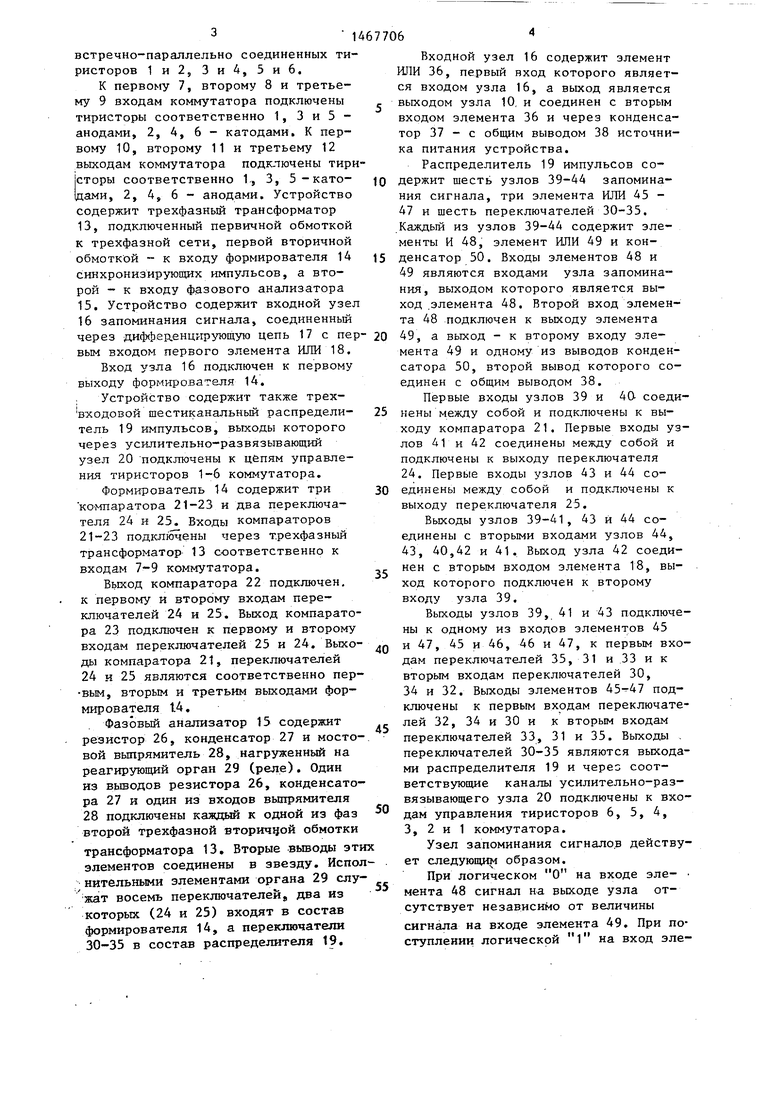

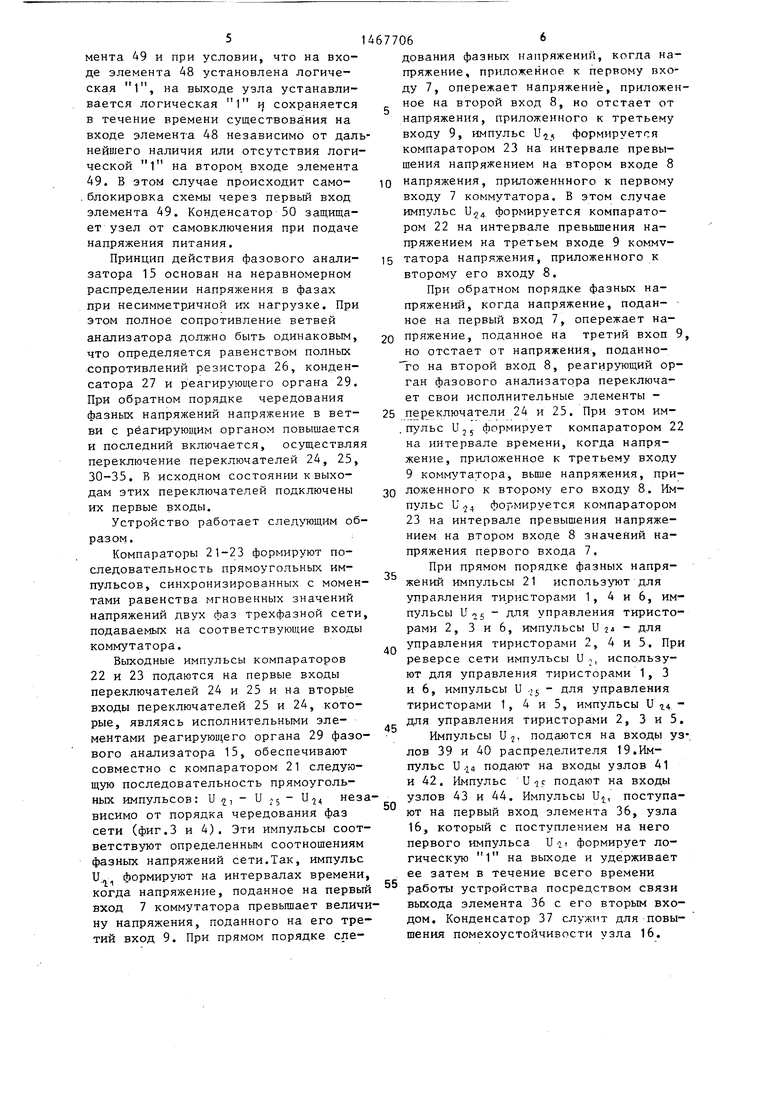

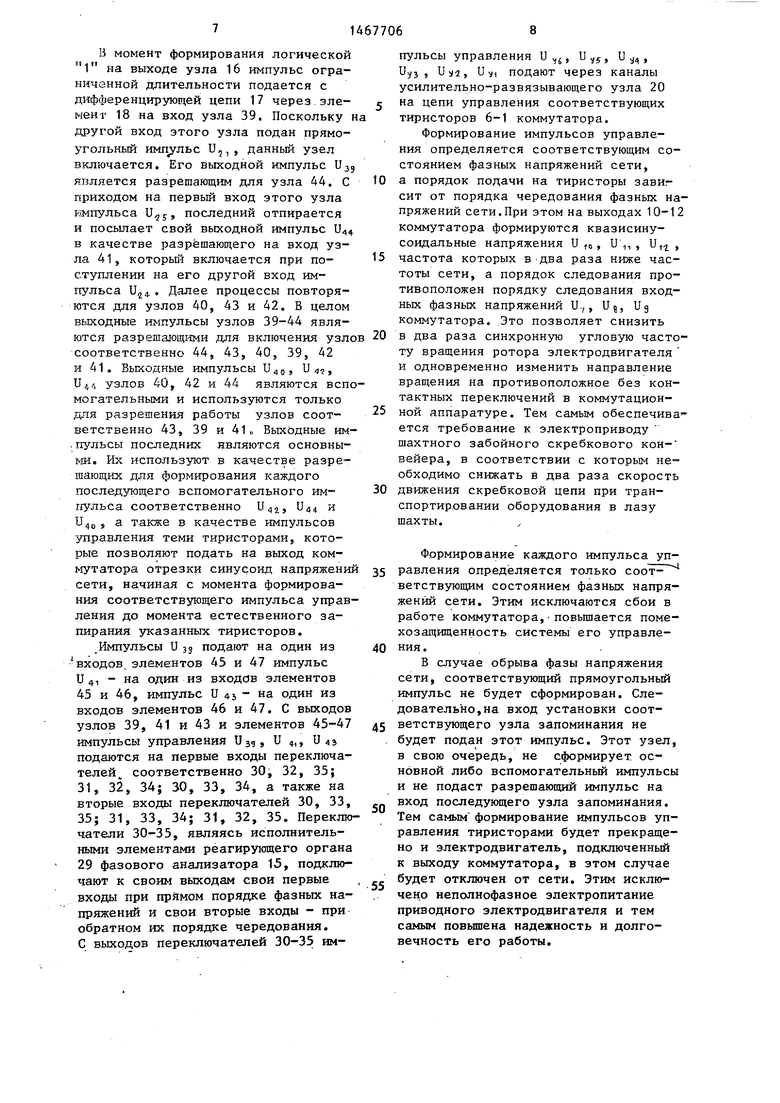

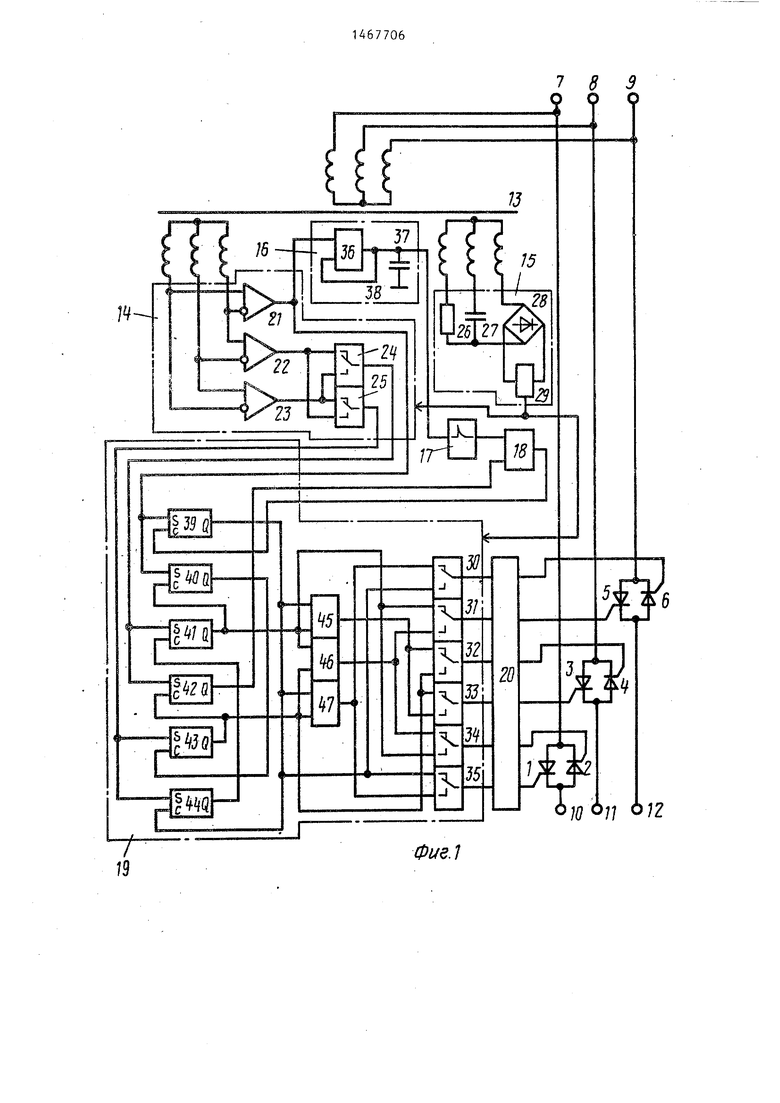

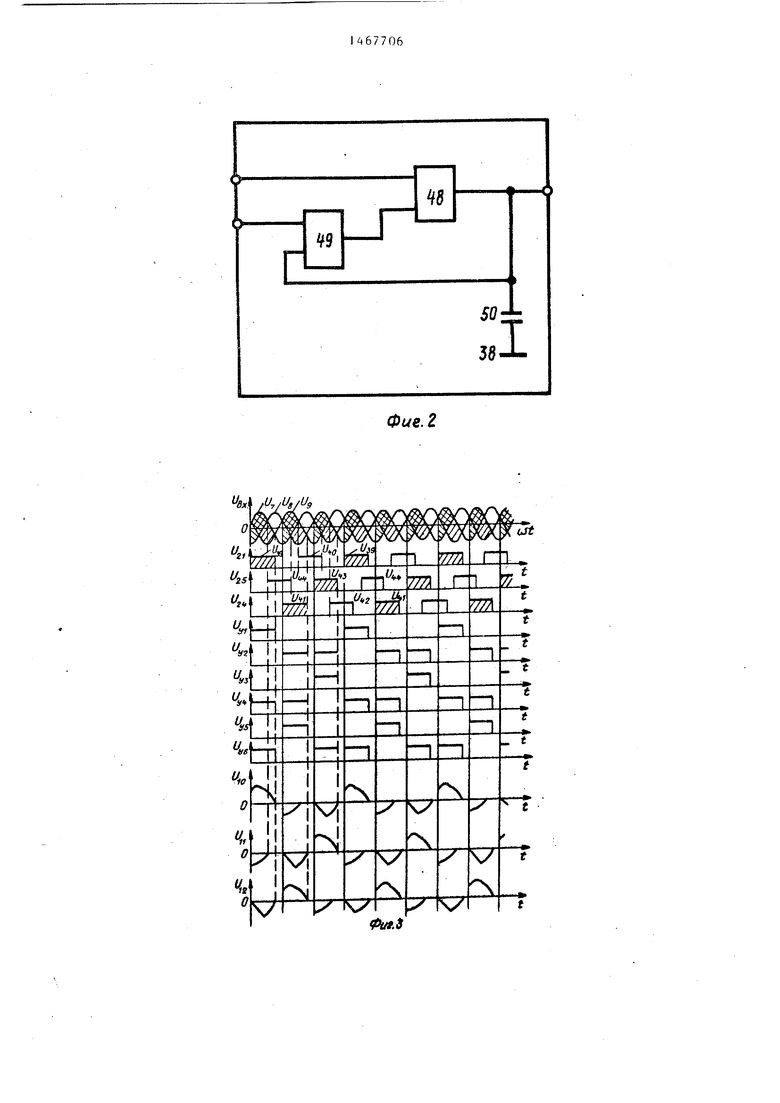

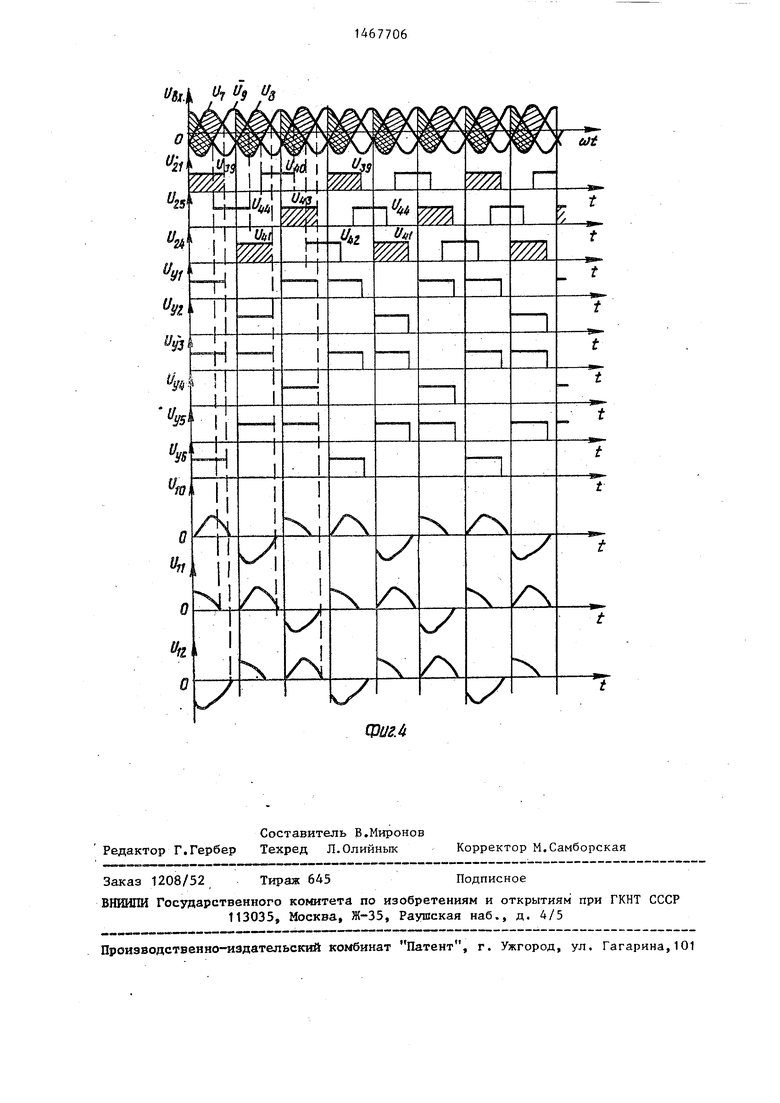

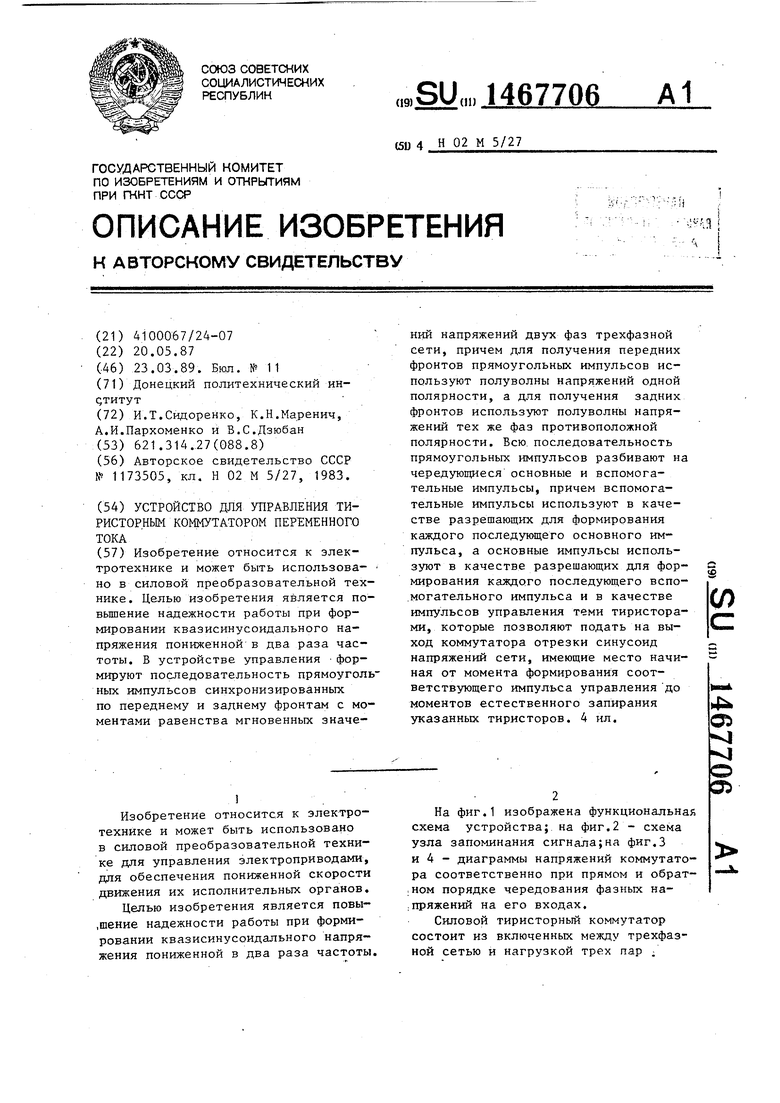

На фиг.1 изображена функциональная схема устройства; на фиг.2 - схема узла запоминания сигнала;на фиг.З и 4 - диаграммы напряжений коммутатора соответственно при прямом и обрат- ,ном порядке чередования фазных на- ;пряжений на его входах.

Силовой тиристорный коммутатор состоит из включенных между трехфазной сетью и нагрузкой трех пар ;

встречно-параллельно соединенных тиристоров 1и25 ЗиА, 5и6,

К nepBONry 7, второму 8 и третье- му 9 входам коммутатора подключены тиристоры соответственно 1, 3 и 5 - анодами, 2, А, 6 - катодами. К первому 10, второму 11 и третьему 12 выходам коммутатора подключены тири |сторы соответственно 1-, 3, 5 - катодами, 2, 4, 6 - анодами. Устройство содержит трехфазный трансформатор 13, подключенный первичной обмоткой к трехфазной сети, первой вторичной обмоткой - к входу формирователя 14 синхронизирующих импульсов, а второй - к входу фазового анализатора 15. Устройство содержит входной узел 16 запоминания сигнала, соединенный через диф(ЬeReнциpy oщyю цепь 17 с первым входом первого элемента ИЛИ 18. Вход узла 16 подключен к первому выходу формирователя 14.

Устройство содержит также трех- входовой шестиканальньм распределитель 19 импульсов, выходы которого через усилительно-развязывающий узел 20 подключены к ЦЕПЯМ управления тиристоров 1-6 коммутатора.

Формирователь 14 содержит три ко-мпаратора 21-23 и два переключателя 24 и 25. Входы компараторов 21-23 подключены через трехфазный трансформатор 13 соответственно к входам 7-9 коммутатора.

Вькод компаратора 22 подключен, к первому и второму входам переключателей 24 и 25. Выход компаратора 23 подключен к первому и второму входам переключателей 25 и 24. Выходы компаратора 21, переключателей 24 и 25 являются соответственно пер- вьм, вторым и третьим выходами формирователя 14,

Фазовый анализатор 15 содержит резистор 26, конденсатор 27 и мостовой выпрямитель 28, нагруженный на реагирующий орган 29 (реле). Один из вьшодов резистора 26, конденсатора 27 и один из входов выпрямителя 28 подключены каждый к одной из фаз второй трехфазной вторичцой обмотки трансформатора 13, Вторые выводы эт элементов соединены в звезду. Испонительными элементами органа 29 слу жат восемь переключателейj два из которых (24 и 25) входят в состав формирователя 14, а переключатели 30-35 в состав распределителя 19,

0

5

0

5

0

5

0

Входной узел 16 содержит злемент ИЛИ 36, первый вход которого является входом узла 16, а выход является выходом узла 10, и соединен с вторым входом элемента 36 и через конденсатор 37 - с общим выводом 38 источника питания устройства.

Распределитель 19 импульсов содержит шесть узлов 39-44 запоминания сигнала, три элемента ИЛИ 45 - 47 и шесть переключателей 30-35. Каждый из узлов 39-44 содержит элементы И 48, элемент ИЛИ 49 и конденсатор 50. Входы элементов 48 и 49 являются входами узла запоминания, выходом которого является выход .элемента 48. Второй вход элемента 48 подключен к выходу элемента 49, а выход - к второму входу элемента 49 и одному из выводов конденсатора 50, второй вывод которого соединен с общим выводом 38.

Первые входы узлов 39 и 40- соединены между собой и подключены к выходу компаратора 21. Первые входы узлов 41 и 42 соединены между собой и подключены к выходу переключателя 24. nepBbfe входы узлов 43 и 44 соединены между собой и подключены к выходу переключателя 25.

Выходы узлов 39-41, 43 и 44 соединены с вторыми входами узлов 44, 43, 40,42 и 41. Выход узла 42 соединен с вторым входом элемента 18, выход которого подключен к второму входу узла 39.

Выходы узлов 39, 41 и 43 подключены к одному из входов элементов 45 и 47, 45 и 46, 46 и 47, к первым входам переключателей 35, 31 и 33 и к вторым входам переключателей 30, 34 и 32. Выходы элементов 45-47 подключены к первым входам переключателей 32, 34 и 30 и к вторым входам переключателей 33, 31 и 35. Выходы переключателей 30-35 являются выходами распределителя 19 и через соответствующие каналы усилительно-развязывающего узла 20 подключены к входам управления тиристоров 6, 5, 4, 3, 2 и 1 коммутатора.

Узел запоминания сигналов действует следующим образом.

При логическом О на входе эле- мента 48 сигнал на выходе узла отсутствует независимо от величины сигнала на входе элемента 49. При поступлении логической 1 на вход эле51

мента 49 и при условии, что на входе элемента 48 установлена логическая 1, на выходе узла устанавливается логическая 1 fj сохраняется в течение времени существова ния на входе элемента 48 независимо от дальнейшего наличия или отсутствия логической 1 на втором, входе элемента 49. В этом случае происходит само- .блокировка схемы через первый вход элемента 49. Конденсатор 50 защищает узел от самовключения при подаче напряжения питания.

Принцип действия фазового анализатора 15 основан на неравномерном распределении напряжения в фазах при несимметричной ргх нагрузке. При этом полное сопротивление ветвей анализатора должно быть одинаковьм, что определяется равенством полных сопротивлений резистора 26, конденсатора 27 и реагирующего органа 29. При обратном порядке чередования фазных напряжений напряжение в ветви с реагирующим органом повышается и последний включается, осуществляя переключение переключателей 24, 25, 30-35. В исходном состоянии к выходам этих переключателей подключены их первые входы.

Устройство работает следующим образом.

Компараторы 21-23 формируют последовательность прямоугольных импульсов, синхронизированных с моментами равенства мгновенных значений напряжений двух фаз трехфазной сети подаваемых на соответствующие входы коммутатора.

Выходные импульсы компараторов 22 и 23 подаются на первые входы переключателей 24 и 25 и на вторые входы переключателей 25 и 24, которые, являясь исполнительными элементами реагирующего органа 29 фазового анализатора 15, обеспечивают совместно с компаратором 21 следующую последовательность прямоугольных импульсов: U ., - U ;; - 74 незвисимо от порядка чередования фаз сети (фиг.З и 4). Эти импульсы соответствуют определенным соотношениям фазных напряжений сети.Так, импульс и.„ формируют на интервалах времени когда напряжение, поданное на первы вход 7 коммутатора превьшает величну напряжения, поданного на его третий вход 9. При прямом порядке сле77066

дования фазных напряжений, когда напряжение, приложенное к первому входу 7, опережает напряжение, приложенное на второй вход 8, но отстает от напряжения, приложенного к третьему входу 9, импульс и, формируется компаратором 23 на интервале превышения напряжением на втором входе 8

Q напряжения, приложеннного к первому входу 7 коммутатора. В этом случае импульс U24 формируется компаратором 22 на интервале превышения напряжением на третьем входе 9 KOMMV5 татора напряжения, приложенного к второму его входу 8.

При обратном порядке фазных напряжений, когда напряжение, подан- ное на первый вход 7, опережает на0 пряжение, поданное на третий вход 9, но отстает от напряжения, поданно- го на второй вход 8, реагирующий орган фазового анализатора переключает свои исполнительные элементы 25 переключатели 24 и 25, При этом им- .пульс Ujj формирует компаратором 22 на интервале времени, когда напряжение, приложенное к третьему входу 9 коммутатора, выше напряжения, при30 ложенного к второму его входу 8. Импульс формируется компаратором 23 на интервале превышения напряжением на втором входе 8 значений напряжения первого входа 7,

При прямом порядке фазных напряжений импульсы 21 используют для управления тиристорами 1, 4 и 6, импульсы ил5 для управления тиристорами 2, 3 и 6, импульсы и 2i - для управления тиристорами 2, 4 и 5. При реверсе сети импульсы Uo, используют для управления тиристорами 1, 3 и 6, импульсы и -25 - для управления тиристорами 1, 4 и 5, импульсы U 4 - для управления тиристорами 2, 3 и 5. Импульсы и 21 подаются на входы узлов 39 и 40 распределителя 19.Импульс и,14 подают на входы узлов 41 и 42. Импульс и тс подают на входы узлов 43 и 44. Импульсы Uj, поступают на первый вход элемента 36, узла 16, который с поступлением на него первого импульса Uai формирует логическую 1 на выходе и удерживает ее затем в течение всего времени

35

40

45

50

55

работы устройства посредством связи выхода элемента 36 с его вторым входом. Конденсатор 37 служит для повышения помехоустойчивости узла 16.

В момент формирования логической 1 на выходе узла 16 импульс ограниченной длительности подается с дифференцирующей цепи 17 через.эле- мент 18 на вход узла 39. Поскольку н другой вход этого узла подан прямоугольный и шульс данный узел включается. Его выходной импульс Оз является разрешающим для узла 44, С приходом на первый вход этого узла кмпульса , последний отпирается и посьшает свой выходной импульс 1)44 в качестве разрешающего на вход узла 41, которьш включается при по- ступлении на его другой вход импульса Далее процессы повторяются для узлов 40, 43 и 42. В целом выходные импульсы узлов 39-44 являются разрешшощими для включения узло соответственно 44, 43, 40, 39, 42 и 41. Выходные импульсы U4 узлов 40, 42 и 44 являются вспомогательными и используются только для разрешения работы узлов соот- вететвенно 43, 39 и 41„ Выхйдные им- .пульсы последних нвляются основными. Их используют в качестве разрешающих для формирования каждого последующего вспомогательного им- пульса соответственно и,г, 1/44 и J S также в качестве импульсов управления теми тиристорами, которые позволяют подать на выход коммутатора отрезки синусоид напряжений сети, начиная с момента формирования соответствующего импульса управления до момента естественного запирания з азанных тиристоров.

,Импульсы и 33 подают на один из входов, элементов 45 и 47 импульс и 41 - на один из входов элементов 45 и 46, импульс U 4i - на один из входов элементов 46 и 47. С выходов узлов 39, 41 и 43 и элементов 45-47 импульсы управления U ,, подаются на первые входы переключателей соответственно 30, 32, 35; 31, 32, 34; 30, 33, 34, а также на вторые входы переключателей 30, 33, 35; 31, 33, 34; 31, 32, 35. Переключатели 30-35, являясь исполнительными элементами реагирующего органа 29 фазового анализатора 15, подключают к своим выходам свои первые входы при прямом порядке фазных напряжений и свои вторые входы - при обратном их порядке чередования. С выходов переключателей 30-35 импульсы управления Uv,j, U „5 , U , Uyj , Ui/2, и VI подают через каналы усилительно-развязывающего узла 20 на депи управления соответствующих тиристоров 6-1 коммутатора,

Формирование импульсов управления определяется соответствующим состоянием фазных напряжений сети, а порядок подачи на тиристоры завиг сит от порядка чередования фазных напряжений сети.При этом на выходах 10-1 коммутатора формируются квазисинусоидальные напряжения U о, U , , U, частота которых в-два раза ниже частоты сети, а порядок следования противоположен порядку следования входных фазных напряжений U-,, Uj, Ug коммутатора. Это позволяет снизить в два раза синхронную угловую частоту вращения ротора электродвигателя и одновременно изменить направление вращения на противоположное без контактных переключений в коммутационной аппаратуре. Тем самым обеспечива ется требование к электроприводу шахтного забойного скребкового кон- вейера, в соответствии с которым необходимо снижать в два раза скорость движения скребковой цепи при транспортировании оборудования в лазу шахты,

Формирование каждого импульса управления определяется только ветствующим состоянием фазных напряжений сети. Этим исключаются сбои в работе коммутатора,повьш1ается помехозащищенность систе « 1 его управления ,

В случае обрыва фазы напряжения сети, соответствующий прямоугольный импульс не будет сформирован. Следовательно, на вход установки соответствующего узла запоминания не будет подан этот импульс. Этот узел, в свою очередь, не сформирует основной либо вспомогательный импульсы и не подаст разрешающий импульс на вход последующего узла запоминания, Тем самым формирование импульсов управления тиристорами будет прекращено и электродвигатель, подключенный к выходу коммутатора, в этом случае будет отключен от сети. Этим исключено неполнофазное электропитание приводного электродвигателя и тем самым повышена надежность и долговечность его работы.

5 1467706

Формула изобретения

Устройство для управления тири- сторным ком гутатором переменного тока, содержащее источник питания, шестиканальный распределитель импульсов, выходы которого подключены к входам усилительно-развязьшающего узла, выходы которого являются выходами устройства, трехфазный транс--;- форматор, первичная обмотка которого предназначена для подключения к . питающей сети, первая вторичная обмотка подключена к входу формирователя синхрони зирующих импульсов,вторая вторичная обмотка - к входу фазового анализатора, отличающееся тем, что, с целью повьшения надежности работы при формировании квазисинусоидального напряжения пониженной в два раза частоты, устройство снабжено входным узлом запоминания сигнала, содержащим элемент ИЛИ и конденсатор, первым элементом ИЛИ и дифференцирующш. узлом, шестиканальный распределитель импульсов снабжен шестью узлами запоминания сигнала, шестью переключателями, вторым, третьим и четвертым элементами ИЛИ, формирователь синхронизирующих импульсов снабжен тремя компараторами, седьмым и восьмым переключателями, каждый узел запоминания сигнала в шестиканальном распределителе импульсов содержит элемент И, элемент ИЛИ и конденсатор, причем первый вход элемента И является первым входом узла запоминания сигнала, выход этого элемента является выходом указанного узла и соединен с первым входом элемента ИЛИ и через конденсатор - с общим выводом источника питания, второй вход элемента ИЛИ является вторым входом узла запоминания сигнала, выход элемента ИЛИ соединен с вторым входом элемента И первый вход элемента ИЛИ входного узла запоминания сигнала является входом указанного узла, выходом которого является выход Элемента ИЛИ, который соединен с вторьм входом .того же элемента ИЛИ и через конденсатор - с общим выводом источника питания, входами формирователя синхронизирующих импульсов являются входы компараторов, неинвертирующие входы первого, второго и третьего коммутатора соединены соответствен-

10

0

5

0

5

0

5

0

5

0

5

но с инвертирующими входами, третьего, первого и второго компараторов, вькод второго компаратора подключен к первому и второму входам соответственно седьмого и восьмого переключателей, вькод третьего компаратора подключен к первому и второму входам соответственно восьмого и седьмого переключателей, выходы первого компаратора, седьмого и вось мого .переключателей являются соответственно первым, вторым и третьим выходами формирователя синхронизирующих импульсов, первый выход которого подключен через последовательно соединенные входной узел запоми- I нания сигнала и дифференцирующий узел к первому входу первого элемента ИЛИ, первые входы первого и второго, третьего и четвертого, пятого и шестого узлов запоминания шести- канального распределителя импульсов подключены соответственно к первому, второму и третьему выходам формирователя синхронизирующих импульсов, выходы первого, второго, третьего, пятого и. шестого узлов запоминания сигналов соединены с вторым входом соответственно шестого, пятого,второго, четвертого и третьего узлов запоминания, выход четвертого узла запоминания соединен с вторым входом первого элемента ИЛИ, выход которого соединен с вторым входом первого узла запоминания сигнала, входы второго, третьего и четвертого элементов ИЛИ подключены соответственно к выходам первого и третьего, третьего и пятого, первого и пятого узлов запоминания сигналов, выходы перво- JY), третьего и пятого узлов запоминания сигналов подключены также к первому входу соответственно шестого,второго и четвертого переключателей и к второму входу соответственно первого, пятого и третьего переключат.елей, выходы второго, третьего и четвертого элементов ИЛИ подключены к первым входам соответственно третьего, пятого и первого и также к вторым входам соответственно четвертого, второго и шестого переключателей, выходы первого, второго, третьего, четвертого, пятого и шестого пере- кдючателей являются выходами распределителя импульсов, а управляющие входы всех переключателей соединены с выходом фазового анализатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ управления трехфазным силовым полупроводниковым коммутатором и устройство для его осуществления | 1983 |

|

SU1173505A1 |

| Способ ступенчатого регулирования частоты вращения асинхронного электродвигателя с тиристорным коммутатором | 1986 |

|

SU1517107A1 |

| Способ регулирования частоты вращения трехфазного асинхронного электродвигателя | 1985 |

|

SU1376209A1 |

| Способ пуска конвейера | 1984 |

|

SU1221094A1 |

| Устройство для управления тиристорным преобразователем | 1986 |

|

SU1413694A1 |

| Способ формирования управляющих импульсов в одноканальных системах фазового управления вентильным преобразователем | 1988 |

|

SU1624631A1 |

| Устройство для импульсно-фазового управления тиристорным преобразователем | 1986 |

|

SU1432695A1 |

| СПОСОБ ПЕРЕДАЧИ И ПРИЕМА КОМАНД УПРАВЛЕНИЯ ПО ПРОВОДАМ ТРЕХФАЗНОЙ СЕТИ | 1991 |

|

RU2017224C1 |

| Устройство для управления @ -фазным тиристорным преобразователем | 1988 |

|

SU1739453A1 |

| Система управления и контроля трехфазных сетей наружного освещения с каскадным включением | 1983 |

|

SU1136256A1 |

Изобретение относится к электротехнике и может быть использова- но в силовой преобразовательной технике. Целью изобретения является повышение надежности работы при формировании квазисинусоидального напряжения пониженной в два раза частоты. В устройстве управления формируют последовательность прямоуголь ных импульсов синхронизированных по переднему и заднему фронтам с моментами равенства мгновенных значеНИИ напряжений двух фаз трехфазной сети, причем для получения передних фронтов прямоугольных импульсов используют полуволны напряжений одной полярности, а для получения задних фронтов используют полуволны напряжений тех же фаз противоположной полярности. Всю, последовательность прямоугольных импульсов разбивают на чередующиеся основные и вспомогательные импульсы, причем вспомогательные импульсы используют в качестве разрешающих для формирования каждого последующего основного импульса, а основные импульсы используют в качестве разрешающих для формирования каждого последующего вспомогательного импульса и в качестве импульсов управления теми тиристорами, которые позволяют подать на выход коммутатора отрезки синусоид напряжений сети, имеющие место начиная от момента формирования соответствующего импульса управления до моментов естественного запирания указанных тиристоров. 4 ил. S (Л С 4 О5

Фие.2

Ф1а.З

%i Л 4s ,

ФигЛ

| Способ управления трехфазным силовым полупроводниковым коммутатором и устройство для его осуществления | 1983 |

|

SU1173505A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1989-03-23—Публикация

1986-05-20—Подача