11473033

Изобретение относится к электротехнике, в частности преобразовательной технике, а именно к устройствам синхронизации синхронных систем им- пульсно-фазового управления вентильными преобразователями с естественной коммутацией уиристоров. Преимущественно устройство предназначено

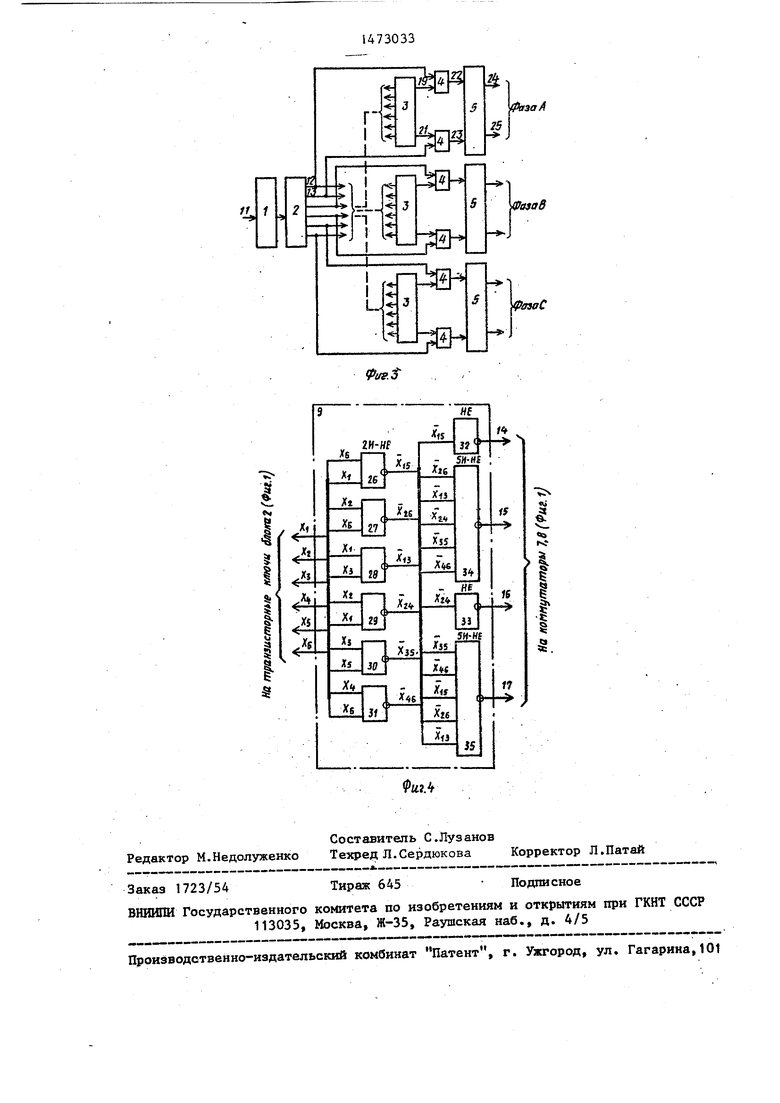

Логичесгий блок (фиг.4) содержит шесть элементов 2И-НЕ 26-3 , входы которых подключены к нуль-органам 2,, два элемента НЕ 32, 33 и два элемента 5И-НЕ 34, 35, выходы которых соединены с управляющими входами коммутаторов 7 и 8.

Устройство работает следующим

для работы от источника энергии огра- Q образом.

: ничейной.мощности, характеризующегося существенной нестабильностью параметров выходного напряжения, и может быть использовано для управления ти

Искаженное коммутационными провалами силовое трехфазное напряжение 11 (фиг.1 и 2) подается на первичную обмотку трансформаторов 1 (фиг.1).

быть использовано MJJ- .- --- -- - --чристорными преобразователями мобиль- ,5 двух трехфазных противофазно вклю...«««-ж лTtrttrtTr.T-v rsm/ T TjrTTTJt.i v Г МЧТТЛТГ ИЯ TTD ЯЖ&НМ &

ных сельскохозяйственных агрегатов с автономным источником энергии.

Цель изобретения - повышение помехоустойчивости системы импульсно-фа- зового управления от коммутационных провалов.

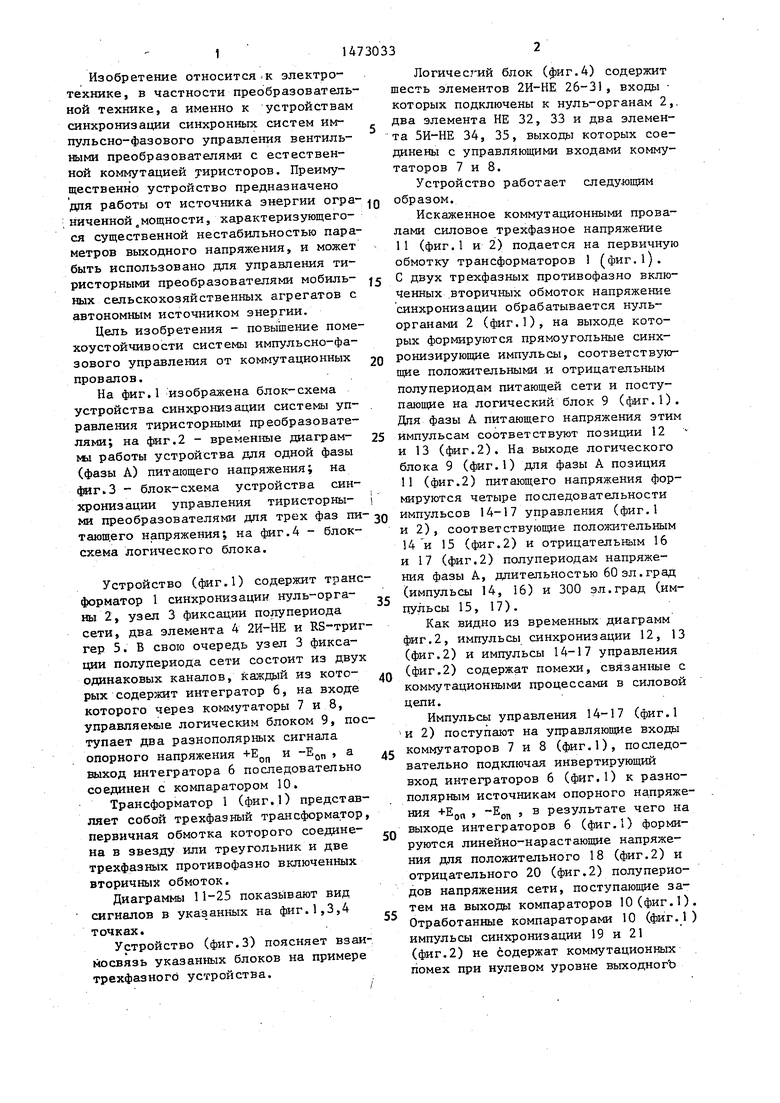

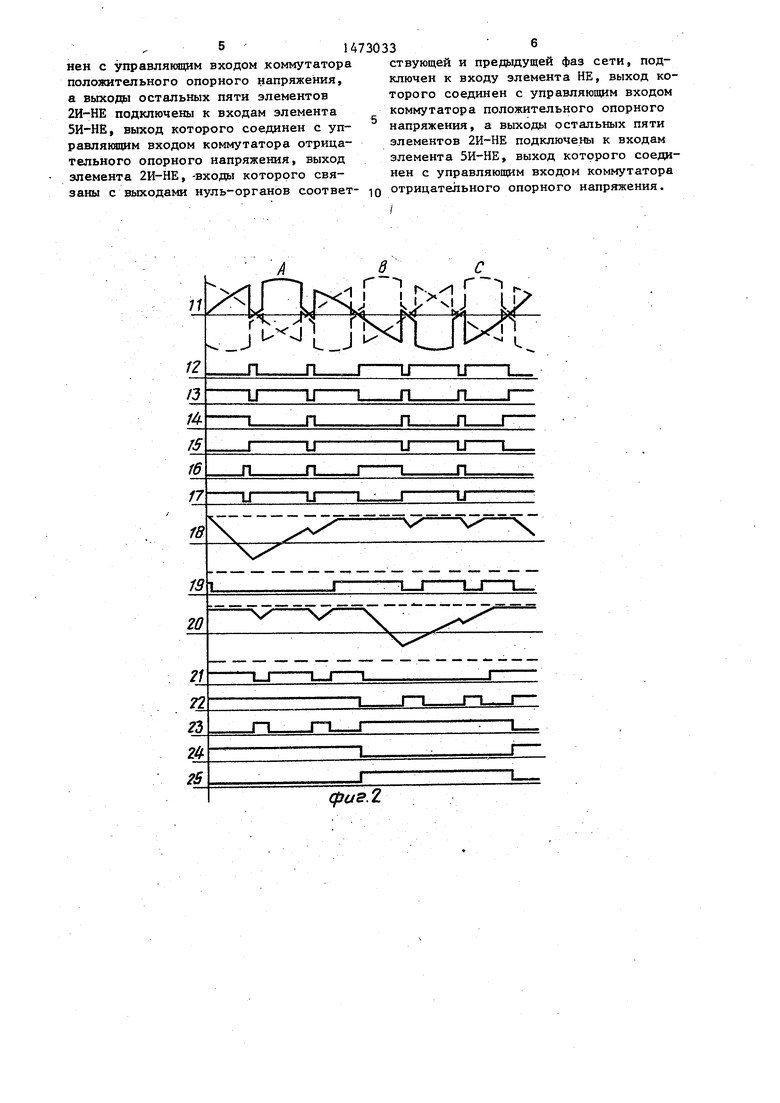

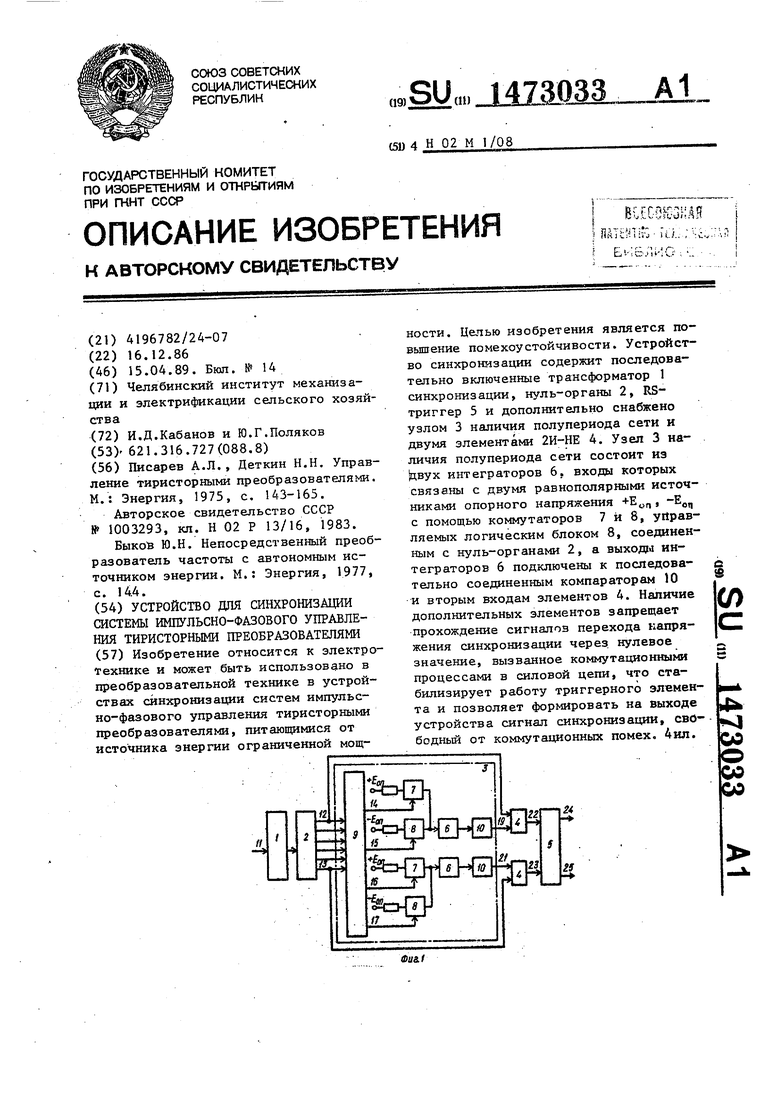

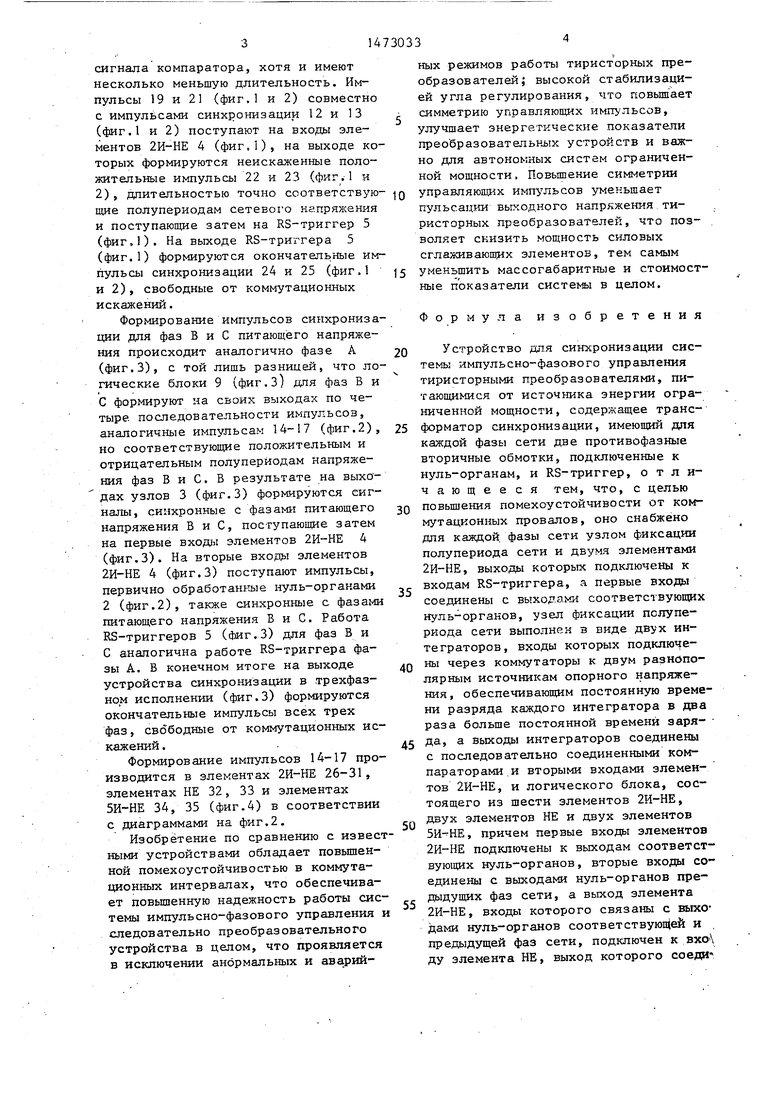

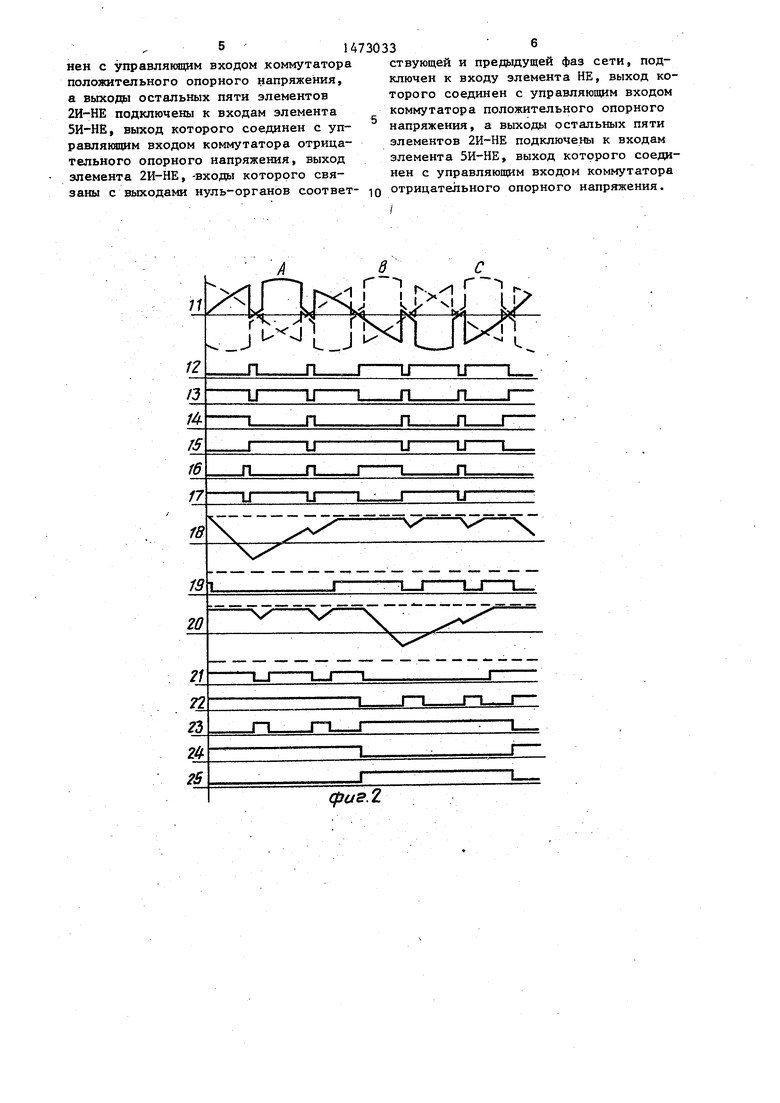

На фиг.1 изображена блок-схема устройства синхронизации системы управления тиристорными преобразователями; на фиг.2 - временные диаграм- №1 работы устройства для одной фазы (фазы А) питающего напряжения; на 4мг.3 - блок-схема устройства синхронизации управления тиристорны20

25

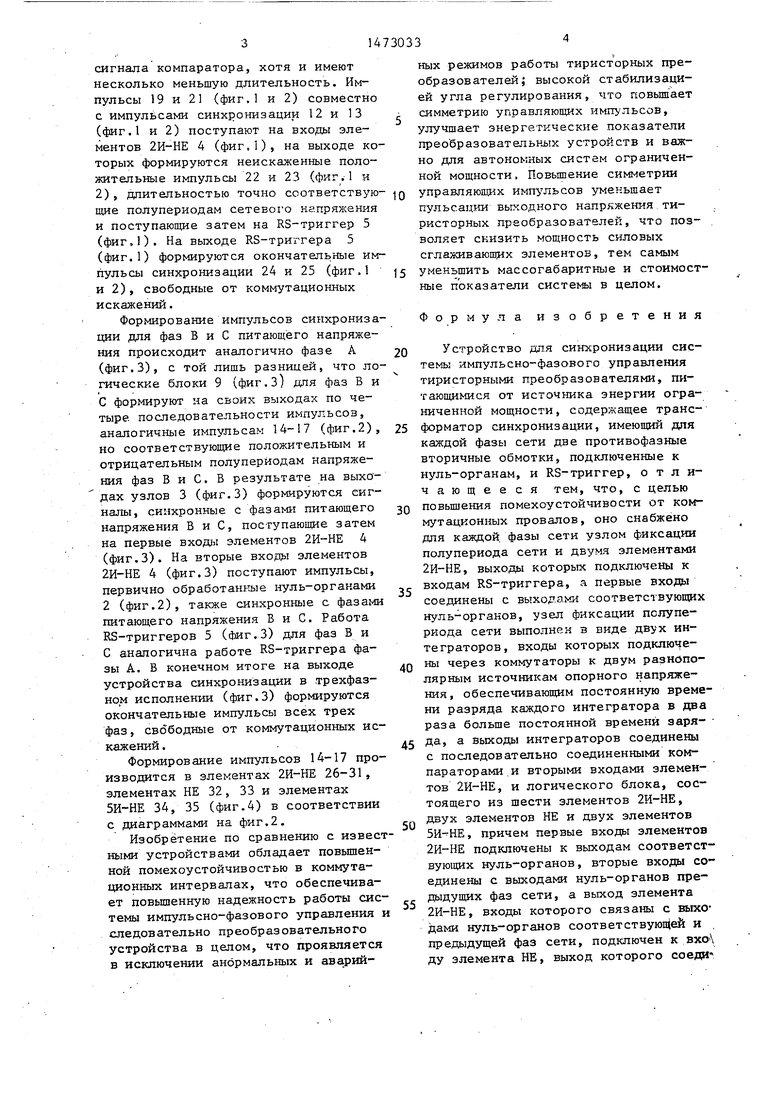

ченных вторичных обмоток напряжение синхронизации обрабатывается нуль- органами 2 (фиг.1), на выходе которых формируются прямоугольные синхронизирующие импульсы, соответствующие положительнь:ми и отрицательным полупериодам питающей сети и поступающие на логический блок 9 (фиг.1). Для фазы А питающего напряжения этим импульсам соответствуют позиции 12 и 13 (фиг.2). На выходе логического блока 9 (фиг.1) для фазы А позиция 11 (фиг.2) питающего напряжения формируются четыре последовательности

Г еоГазоГ Г;,, ™;к Газ пи-30 -пульсов U-,7 управления (4.Г.,

, Л 9 r-nnTRpTfTRvronrae полояситель

тающего напряжения; на фиг.4 схема логического блока.

блоки 2) , соответствующие полоясительным 14 и 15 (фиг.2) и отрицательным 16 и 17 (фиг.2) полупериодам напряжения фазы А, длительностью 60 эл.град (импульсы 14, 16) и 300 эл.град (импульсы 15, 17).

40

Устройство (фиг.1) содержит трансорматор 1 синхронизации нуль-орга- ы 2, узел 3 фиксации полупериода сети, два элемента 4 2И-НЕ и RS-триг- гер 5. В свою очередь узел 3 фиксации полупериода сети состоит из двух одинаковых каналов, каждай из которых содержит интегратор 6, на входе которого через коммутаторы 7 и 8, управляемые логическим блоком 9, поступает два разнополярных сигнала опорного напряжения + Е и -Е , а выход интегратора 6 последовательно соединен с компаратором 10.

Трансформатор 1 (фнг.О представляет собой трехфазный трансформатор, первичная обмотка которого соединена в звезду или треугольник и две трехфазных противофазно включенных вторичных обмоток.

Диаграммы 11-25 показывают вид сигналов в указанных на фиг.1,3,4

точках.

Устройство (фиг.З) поясняет взаимосвязь указанных блоков на примере трехфазного устройства.

Логичесгий блок (фиг.4) содержит шесть элементов 2И-НЕ 26-3 , входы которых подключены к нуль-органам 2,, два элемента НЕ 32, 33 и два элемента 5И-НЕ 34, 35, выходы которых соединены с управляющими входами коммутаторов 7 и 8.

Устройство работает следующим

образом.

Искаженное коммутационными провалами силовое трехфазное напряжение 11 (фиг.1 и 2) подается на первичную обмотку трансформаторов 1 (фиг.1).

-- - --ч двух трехфазных противофазно вклю двух трехфазных противофазно вклюTtrttrtTr.T-v rsm/ T TjrTTTJt.i v Г МЧТТЛТГ ИЯ TTD ЯЖ&НМ &

ченных вторичных обмоток напряжение синхронизации обрабатывается нуль- органами 2 (фиг.1), на выходе которых формируются прямоугольные синхронизирующие импульсы, соответствующие положительнь:ми и отрицательным полупериодам питающей сети и поступающие на логический блок 9 (фиг.1). Для фазы А питающего напряжения этим импульсам соответствуют позиции 12 и 13 (фиг.2). На выходе логического блока 9 (фиг.1) для фазы А позиция 11 (фиг.2) питающего напряжения формируются четыре последовательности

-пульсов U-,7 управления (4.Г.,

-пульсов U-,7 управления (4.Г.,

Tjr 9 r-nnTRpTfTRvronrae полояситель

0

и 2) , соответствующие полоясительным 14 и 15 (фиг.2) и отрицательным 16 и 17 (фиг.2) полупериодам напряжения фазы А, длительностью 60 эл.град (импульсы 14, 16) и 300 эл.град (импульсы 15, 17).

Как видно из временных диаграмм фиг.2, импульсы синхронизации 12, 13 (фиг.2) и импульсы 14-17 управления (фиг.2) содержат помехи, связанные с коммутационными процессами в силовой

цепи.

Импульсы управления 14-17 (фиг.1 и 2) поступают на управляющие входы коммутаторов 7 и 8 (фиг.1), последовательно подключая инвертирующий вход интеграторов 6 (фиг.1) к разно- полярным источникам опорного на пряже- ния +ЕО„ , -ЕОП , в результате чего на выходе интеграторов 6 (фиг.1) формируются линейно-нарастающие напряжения для положительного 18 (фиг.2) и отрицательного 20 (фиг.2) полуперйодов напряжения сети, поступающие затем на выходы компараторов 10 (фиг.1). Отработанные компараторами 10 (фиг.1) импульсы синхронизации 19 и 21 (фиг,2) не бодержат коммутационных помех при нулевом уровне выходногЪ

0

5

сигнала компаратора, хотя и имеют есколько меньшую длительность. Имульсы 19 и 21 (фиг.1 и 2) совместно с импульсами синхронизации 12 и 13 (фиг.1 и 2) поступают на входы элементов 2И-НЕ 4 (фиг.), на выходе которых формируются неискаженные положительные импульсы 22 и 23 (фиг.1 и 2) , длительностью точно соответствующие полупериодам сетевого напряжения и поступающие затем на RS-триггер 5 (фиг.1). На выходе RS-триггера 5 (фиг.1) формируются окончательные импульсы синхронизации 24 и 25 (фиг.1 и 2), свободные от коммутационных искажений.

Формирование импульсов синхронизации для фаз В и С питающего напряжения происходит аналогично фазе А (фиг.З), с той лишь разницей, что логические блоки 9 (фиг.З) для фаз В и С формируют на своих выходах по четыре последовательности импульсов, аналогичные импульсам 14-17 (фиг.2), но соответствующие положительным и отрицательным полуперйодам напряжения фаз В и С. В результате на выхо- дах узлов 3 (фиг.З) формируются сигналы, синхронные с фазами питающего напряжения В и С, поступающие затем на первые входы элементов 2И-НЕ 4 (фиг.З). На вторые входы элементов 2И-НЕ 4 (фиг.З) поступают импульсы, первично обработанные нуль-органами 2 (фиг.2), также синхронные с фазами питающего напряжения В и С. Работа RS-триггеров 5 (фиг.З) для фаз В и С аналогична работе RS-триггера фазы А. В конечном итоге на выходе устройства синхронизации в трехфазном исполнении (фиг.З) формируются окончательные импульсы всех трех фаз, свободные от коммутационных искажений.

Формирование импульсов 14-17 производится в элементах 2И-НЕ 26-31, элементах НЕ 32, 33 и элементах 5И-НЕ 34, 35 (фиг.4) в соответствии с диаграммами на фиг.2.

Изобретение по сравнению с известными устройствами обладает повьшен- ной помехоустойчивостью в коммутационных интервалах, что обеспечивает повышенную надежность работы системы импульсно-фазового управления и следовательно преобразовательного устройства в целом, что проявляется в исключении анормальных и аварийных режимов работы тиристорных преобразователей; высокой стабилизацией угла регулирования, что повьш1ает симметрию управляющих импульсов, улучшает энергетические показатели преобразовательных устройств и важно для автономных систем ограниченной мощности. Повышение симметрии

управляющих импульсов уменьшает пульсац ш выходного напряжения,тиристорных преобразователей, что поз- , воляет снизить мощность силовых сглаживающих элементов, тем самым

5 уменьшить массогабаритные и стоимостные показатели системы в целом.

Формула изобретения

0Устройство для синхронизации системы импульсно-фазового управления тиристорными преобразователями, питающимися от источника энергии ограниченной мощности, содержащее транс- 5 форматор синхронизации, имеющий для каждой фазы сети две противофазные вторичные обмотки, подключенные к нуль-органам, и RS-триггер, отличающееся тем, что, с целью Q повьш1ения помехоустойчивости от коммутационных провалов, оно снабжено для каждой фазы сети узлом фиксации полупериода сети и двумя элементами 2И-НЕ, выходы которых подключены к входам RS-триггера, а первые входы соединены с выходами соответствующих нуль-органов, узел фиксации полупериода сети выполнен в виде двух интеграторов, входы которых подключе- XQ ны через коммутаторы к двум разнбпо- лярным источникам опорного напряжения, обеспечивающим постоянную времени разряда каждого интегратора в два раза больше постоянной времени эаря- Д5 да, а выходы интеграторов соединены с последовательно соединенными компараторами, и вторыми входами элементов 2И-НЕ, и логического блока, состоящего из шести элементов 2И-НЕ, - двух элементов НЕ и двух элементов 5И-НЕ, причем первые входы элементов 2И-НЕ подключены к выходам соответст- нуль-органов, вторые входа соединены с выходами нуль-органов предыдущих фаз сети, а выход элемента 2И-НЕ, входы которого связаны с выходами нуль-органов соответствуюп ей и , предыдущей фаз сети, подключен к вхо ду элемента НЕ, выход которого соедИ

5

55

1473033

нен с управпякяцим входом коммутатора положительного опорного напряжения, а выходы остальных пяти элементов 2И-НЕ подключены к входам элемента 5И-НЕ, выход которого соединен с уп- равляняцим входом коммутатора отрицательного опорного напряжения, выход элемента 2И-НЕ, -входы которого связаны с выходами нуль-органов соответ

0

ствующей и предадущей фаз сети, подключен к входу элемента НЕ, выход которого соединен с управляющим входом коммутатора положительного опорного напряжения, а выходы остальных пяти элементов 2И-НЕ подключены к входам элемента 5И-НЕ, выход которого соединен с управляющим входом коммутатора отрицательного опорного напряжения.

/

| название | год | авторы | номер документа |

|---|---|---|---|

| Электропривод переменного тока | 1988 |

|

SU1610590A1 |

| Устройство для стабилизации вакуума | 1983 |

|

SU1149060A1 |

| Электропривод переменного тока | 1986 |

|

SU1522372A1 |

| Преобразователь частоты | 1983 |

|

SU1173501A1 |

| Устройство управления тиристором | 1986 |

|

SU1330746A1 |

| УСТРОЙСТВО БЕЗУДАРНОГО ПУСКА | 2017 |

|

RU2654544C1 |

| Устройство для импульсно-фазового управления тиристорным преобразователем | 1986 |

|

SU1432695A1 |

| Устройство для импульсного регулирования частоты вращения асинхронного электродвигателя | 1985 |

|

SU1288884A1 |

| УСИЛИТЕЛЬ МОЩНОСТИ ДЛЯ УПРАВЛЕНИЯ ИСПОЛНИТЕЛЬНЫМ ДВИГАТЕЛЕМ ПЕРЕМЕННОГО ТОКА | 1995 |

|

RU2103804C1 |

| Устройство для управления вентильным преобразователем | 1980 |

|

SU1146781A1 |

Изобретение относится к электротехнике и может быть использовано в преобразовательной технике в устройствах синхронизации систем импульсно-фазового управления тиристорными преобразователями, питающимися от источника энергии ограниченной мощности. Целью изобретения является повышение помехоустойчивости. Устройство синхронизации содержит последовательно включенные трансформатор 1 синхронизации, нульорганы 2, RS-триггер 5 и дополнительно снабжено узлом 3 наличия полупериода сети и двумя элементами 2И-НЕ 4. Узел 3 наличия полупериода сети состоит из двух интеграторов 6, входы которых связаны с двумя равнополярными источниками опорного напряжения +Еоп, -Еоп с помощью коммутаторов 7 и 8, управляемых логическим блоком 8, соединенным с нуль-органами 2, а выходы интеграторов 6 подключены к последовательно соединенным компараторам 10 и вторым входам элементов 4. Наличие дополнительных элементов запрещает прохождение сигналов перехода напряжения синхронизации через нулевое значение, вызванное коммутационными процессами в силовой цепи, что стабилизирует работу триггерного элемента и позволяет формировать на выходе устройства сигнал синхронизации, свободный от коммутационных помех. 4 ил.

- Г6

LJ

Л.

17и

х::

20

JTL

(fuS.2

ЛГ

П

:

11

а

заА

UTWC j

| Писарев А.Л., Деткин Н.Н | |||

| Управление тиристорными преобразователями | |||

| М.: Энергия, 1975, с | |||

| Крутильная машина для веревок и проч. | 1922 |

|

SU143A1 |

| Устройство для управления мостовым преобразователем | 1981 |

|

SU1003293A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Быков Ю.Н | |||

| Непосредственный преобразователь частоты с автономным источником энергии | |||

| М.: Энергия, 1977, с | |||

| Аппарат для электрической передачи изображений без проводов | 1920 |

|

SU144A1 |

Авторы

Даты

1989-04-15—Публикация

1986-12-16—Подача