Изобретение относится к технике связи и может быть использовано для контроля каналов тональной частоты.

Цель изобретения - повышение точности контроля.

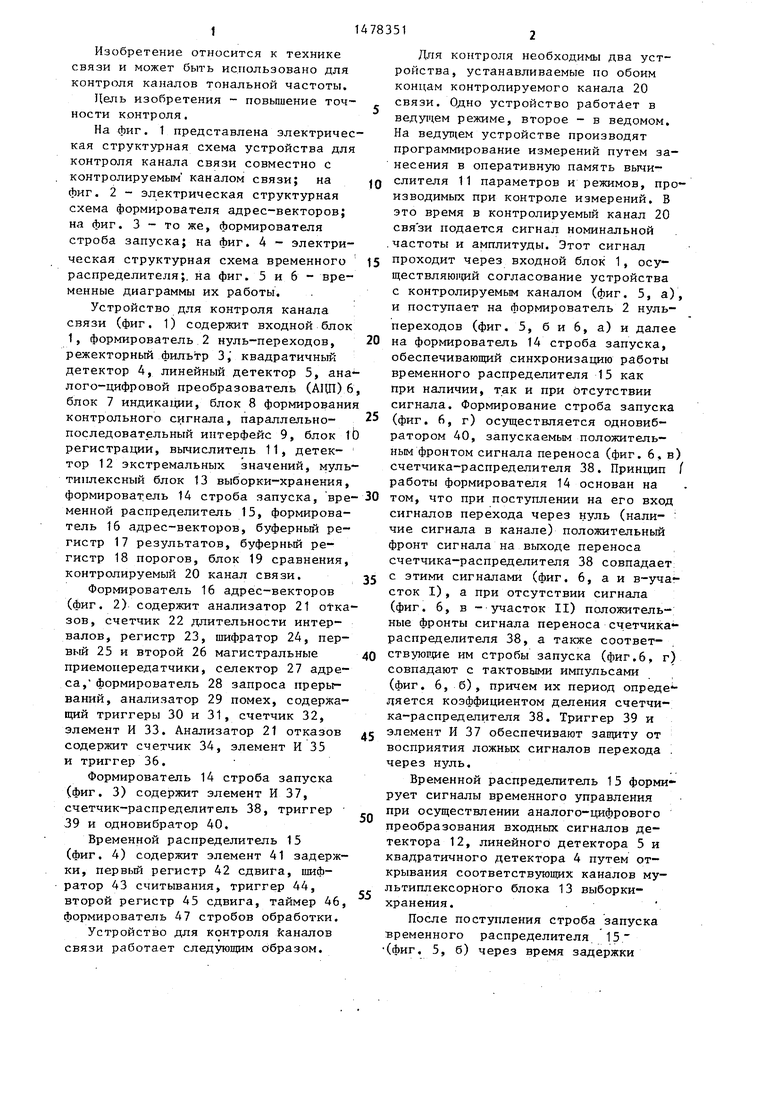

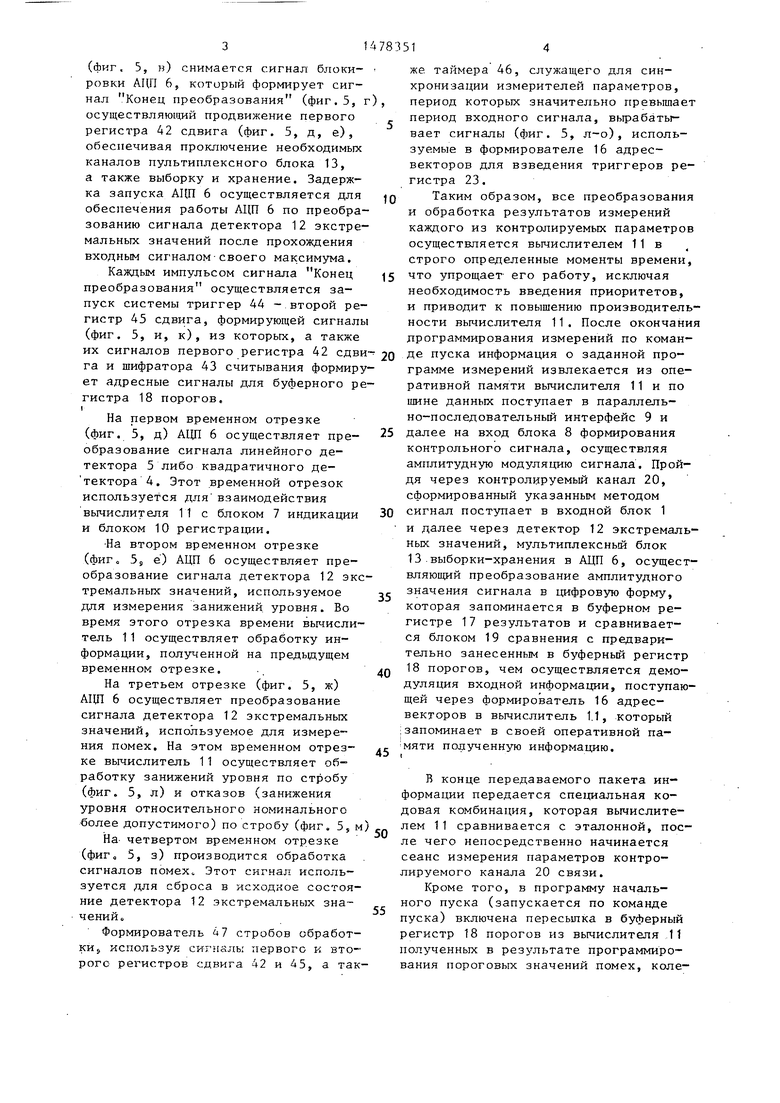

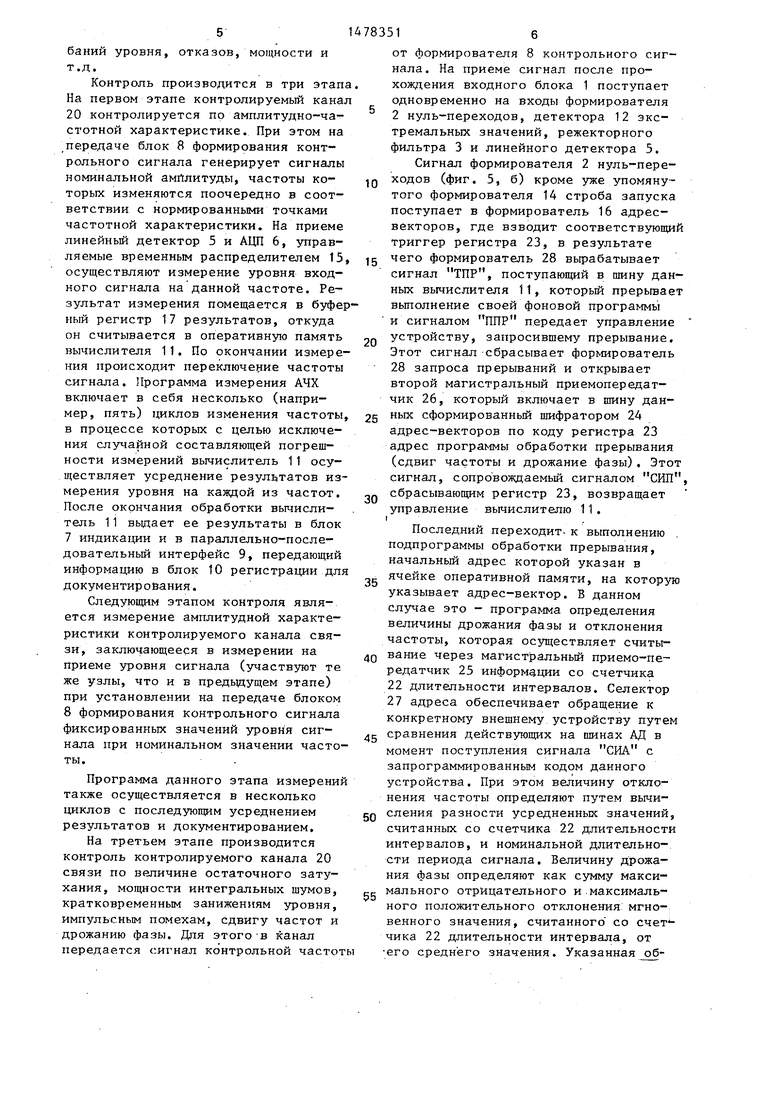

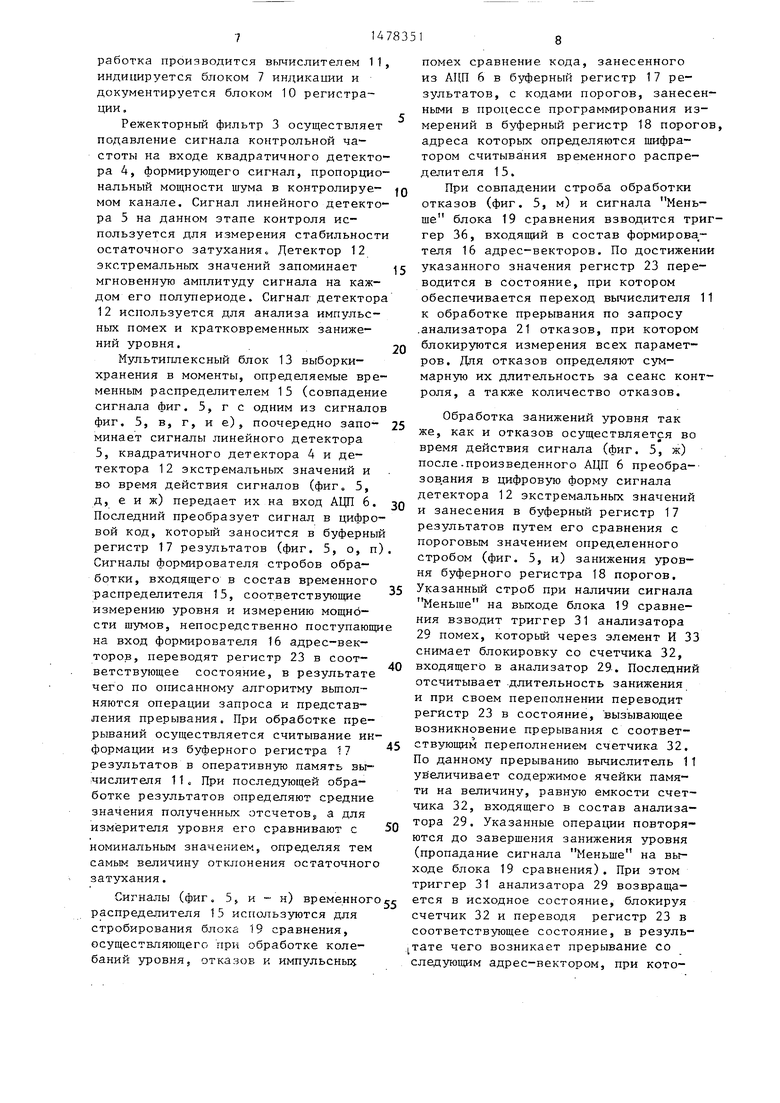

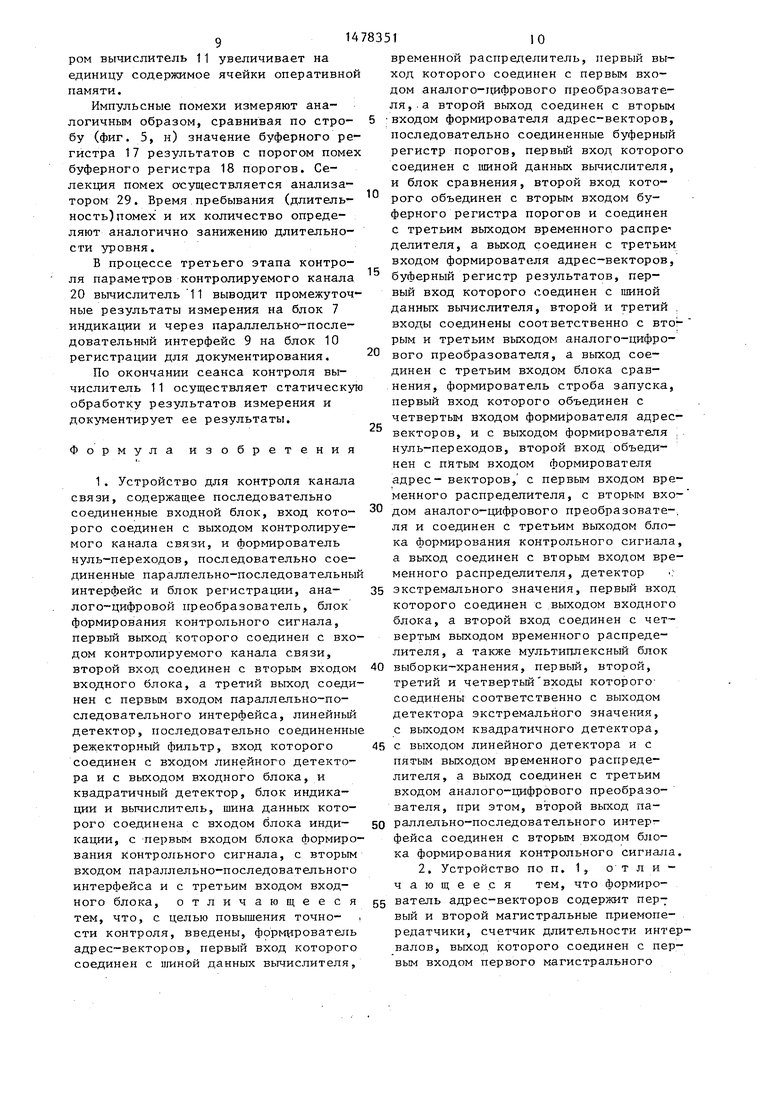

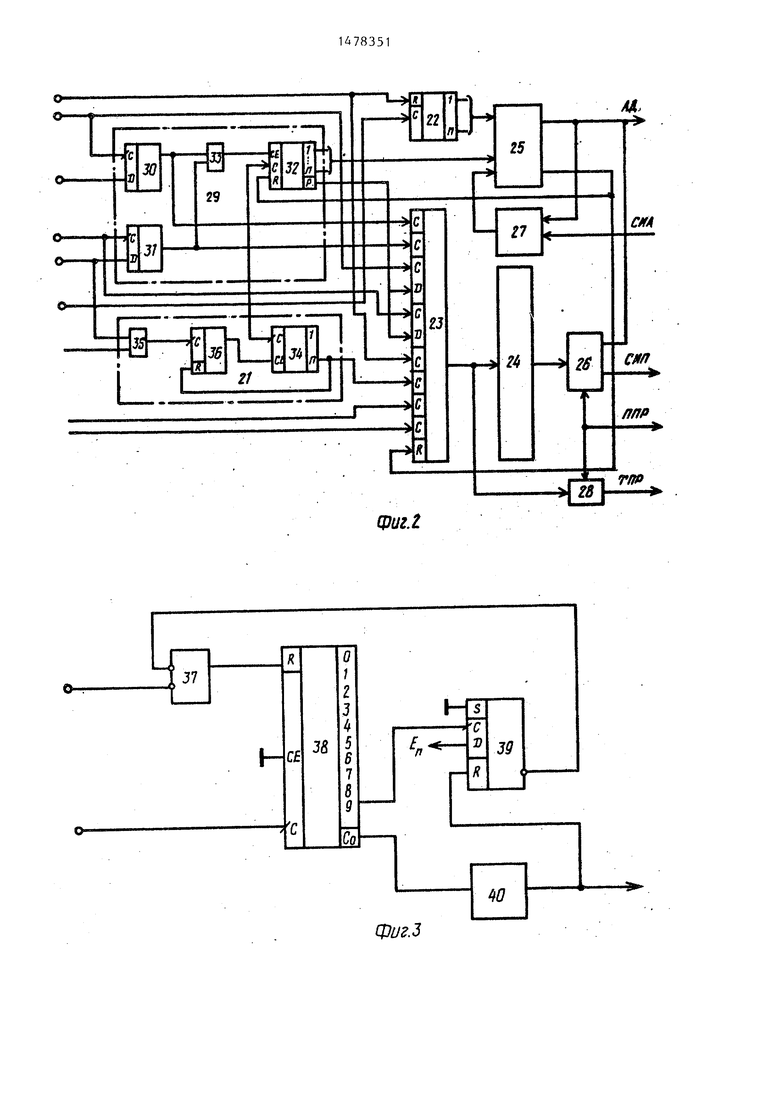

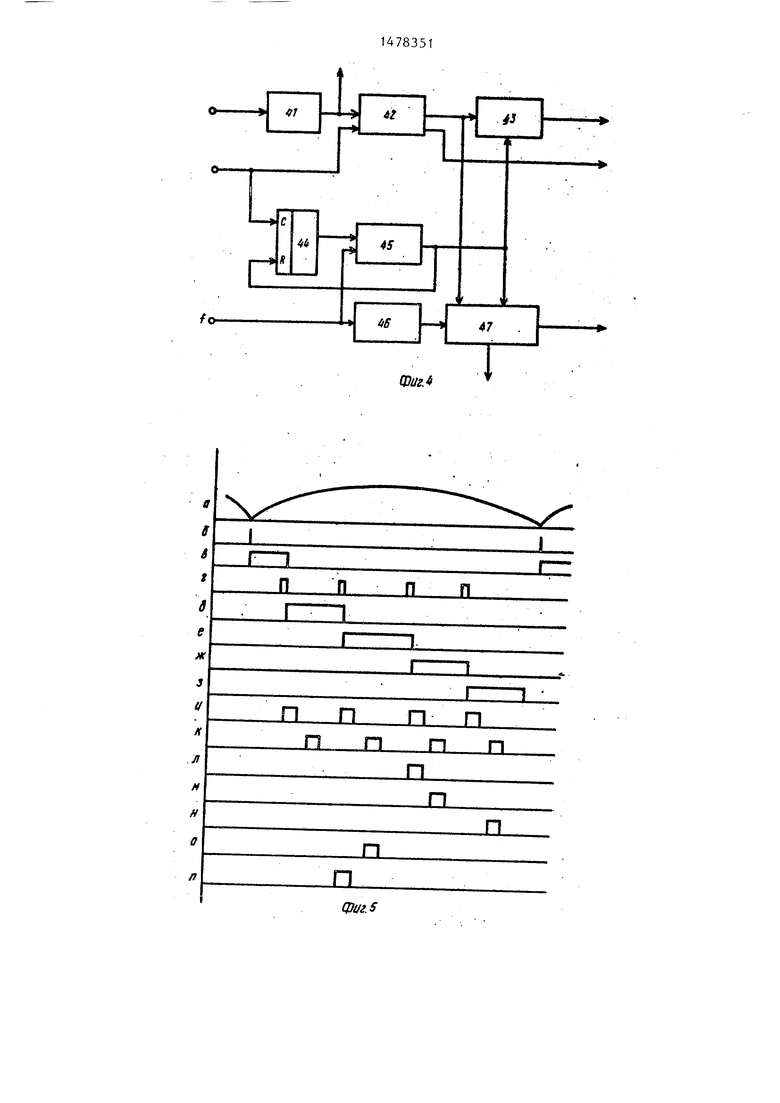

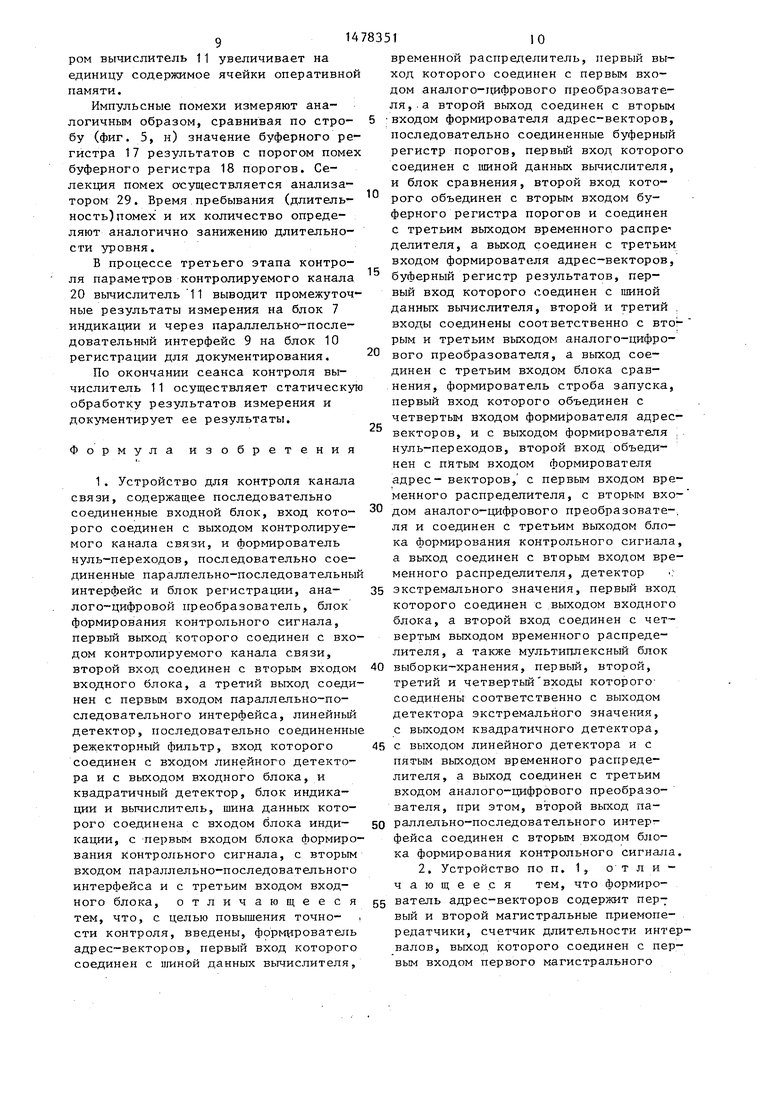

На фиг. 1 представлена электрическая структурная схема устройства для контроля канала связи совместно с контролируемым каналом связи; на фиг. 2 - электрическая структурная схема формирователя адрес-векторов; на фиг. 3 - то же, формирователя строба запуска; на фиг. 4 - электрическая структурная схема временного распределителя; на фиг. 5 и 6 - временные диаграммы их работы.

Устройство для контроля канала связи (фиг. 1) содержит входной блок 1, формирователь 2 нуль-переходов, режекторный фильтр 3, квадратичный детектор 4, линейный детектор 5, аналого-цифровой преобразователь (А1Щ)6 блок 7 индикации, блок 8 формировани контрольного сигнала, параллельно- последовательный интерфейс 9, блок 1 регистрации, вычислитель 11, детектор 12 экстремальных значений, мультиплексный блок 13 выборки-хранения, формирователь 14 строба запуска, временной распределитель 15, формирователь 16 адрес-векторов, буферный регистр 17 результатов, буферный регистр 18 порогов, блок 19 сравнения, контролируемый 20 канал связи.

Формирователь 16 адрес-векторов (фиг. 2) содержит анализатор 21 отказов, счетчик 22 длительности интервалов, регистр 23, шифратор 24, первый 25 и второй 26 магистральные приемопередатчики, селектор 27 адреса,1 формирователь 28 запроса прерываний, анализатор 29 помех, содержащий триггеры 30 и 31, счетчик 32, элемент И 33. Анализатор 21 отказов содержит счетчик 34, элемент И 35 и триггер 36.

Формирователь 14 строба запуска (фиг. 3) содержит элемент И 37, счетчик-распределитель 38, триггер 39 и одновибратор 40,

Временной распределитель 15 (фиг. 4) содержит элемент 41 задержки, первый регистр 42 сдвига, шифратор 43 считывания, триггер 44, второй регистр 45 сдвига, таймер 46, формирователь 47 стробов обработки.

Устройство для контроля каналов связи работает следующим образом.

0

5

0

5

0

5

0

5

0

Для контроля необходимы два устройства, устанавливаемые по обоим концам контролируемого канала 20 связи. Одно устройство работает в ведущем режиме, второе - в ведомом. На ведущем устройстве производят программирование измерений путем занесения в оперативную память вычислителя 11 параметров и режимов, производимых при контроле измерений. В это время в контролируемый канал 20 свя зи подается сигнал номинальной частоты и амплитуды. Этот сигнал проходит через входной блок 1, осуществляющий согласование устройства с контролируемым каналом (фиг. 5, а), и поступает на формирователь 2 нуль- переходов (фиг. 5, б и 6, а) и далее на формирователь 14 строба запуска, обеспечивающий синхронизацию работы временного распределителя 15 как при наличии, так и при отсутствии сигнала. Формирование строба запуска (фиг. 6, г) осуществляется одновиб- ратором 40, запускаемым положительным фронтом сигнала переноса (фиг. 6, в) счетчика-распределителя 38. Принцип ( работы формирователя 14 основан на том, что при поступлении на его вход сигналов перехода через нуль (наличие сигнала в канале) положительный фронт сигнала на выходе переноса счетчика-распределителя 38 совпадает с этими сигналами (фиг. 6, аи в-уча - сток I), а при отсутствии сигнала (фиг. 6, в - участок II) положительные фронты сигнала переноса счетчика - распределителя 38, а также соответствующие им стробы запуска (фиг.6, г) совпадают с тактовыми импульсами (фиг. 6, б), причем их период опреде - дяется коэффициентом деления счетчика-распределителя 38. Триггер 39 и элемент И 37 обеспечивают защиту от восприятия ложных сигналов перехода через нуль.

Временной распределитель 15 формирует сигналы временного управления при осуществлении аналого-цифрового преобразования входных сигналов детектора 12, линейного детектора 5 и квадратичного детектора 4 путем открывания соответствующих каналов му- льтиплексорного блока 13 выборки- хранения.

После поступления строба запуска временного распределителя 15 (фиг. 5, б) через время задержки

3К

(Лиг« 5, в) снимается сигнал блокировки АЦП 6, который формирует сигнал Конец преобразования (фиг. 5, г осуществляющий продвижение первого регистра 42 сдвига (фиг. 5, д, е), обеспечивая проключение необходимых каналов пультиплексного блока 13, а также выборку и хранение. Задержка запуска АЦП 6 осуществляется для обеспечения работы АЦП 6 по преобразованию сигнала детектора 12 экстремальных значений после прохождения входным сигналом своего максимума. Каждым импульсом сигнала Конец преобразования осуществляется запуск системы триггер 44 - второй регистр 45 сдвига, формирующей сигналы (фиг. 5, и, к), из которых, а также

0

5

же таймера 46, служащего для синхронизации измерителей параметров, период которых значительно превышает период входного сигнала, вырабатывает сигналы (фиг. 5, л-о), используемые в формирователе 16 адрес- векторов для взведения триггеров регистра 23.

Таким образом, все преобразования и обработка результатов измерений каждого из контролируемых параметров осуществляется вычислителем 11 в строго определенные моменты времени, что упрощает его работу, исключая необходимость введения приоритетов, и приводит к повышению производительности вычислителя 11. После окончания дрограммирования измерений по коман

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля канала связи | 1985 |

|

SU1249711A1 |

| Электронные вторичные часы с цифровой индикацией | 1983 |

|

SU1170417A1 |

| Способ контроля канала связи и устройство для его осуществления | 1989 |

|

SU1700756A1 |

| Устройство для контроля телеграфного тракта | 1978 |

|

SU720771A1 |

| Устройство для измерения отношения сигнала к помехе в телевизионном канале | 1985 |

|

SU1292206A1 |

| Преобразователь угла поворота вала в код | 1987 |

|

SU1525916A1 |

| Информационно-измерительное устройство | 1985 |

|

SU1256074A1 |

| Устройство для сопряжения масс-спектрометра с ЭВМ | 1988 |

|

SU1580379A1 |

| Устройство кодирования и декодирования факсимильных сигналов | 1980 |

|

SU1043834A1 |

| Информационно-управляющая система центрального теплового пункта жилых общественных и промышленных зданий | 1987 |

|

SU1511751A1 |

Изобретение относится к технике связи. Цель изобретения - повышение точности контроля. Устройство содержит входной блок 1, формирователь 2 нуль-переходов, режекторный фильтр 3, квадратичный детектор 4, линейный детектор 5, АЦП 6, блок 7 индикации, блок 8 формирования контрольного сигнала, параллельно-последовательный интерфейс 9, блок 10 регистрации, вычислитель 11, детектор 12 экстремальных значений, мультиплексный блок 13 выборки-хранения, формирователь 14 строба запуска, временной распределитель 15, формирователь 16 адрес-векторов, буферный регистр 17 результатов, буферный регистр 18 порогов, блок 19 сравнения и контролируемый канал 20 связи. Контроль производится в три этапа. На первом этапе канал 20 контролируется по амплитудно-частотной х-ке, программа измерения которой включает пять циклов измерения частоты. На втором этапе измеряется амплитудная х-ка канала 20, программа измерения которой также осуществляется в несколько циклов с последующим усреднением результатов и документированием. На третьем этапе контролируется канал 20 по величине остаточного затухания, мощности интегральных шумов, кратковременным занижениям уровня, импульсным помехам, сдвигу частот и дрожанию фазы. Устройство по пп. 2, 3 ф-лы отличается выполнением формирователей 16 и 14. 2 з.п. ф-лы, 6 ил.

их сигналов первого регистра 42 сдви- 20 Де пуска информация о заданной про- га и шифратора 43 считывания формирует адресные сигналы для буферного регистра 18 порогов, i

На первом временном отрезке (фиг. 5, д) АЦП 6 осуществляет пре- 5 образование сигнала линейного детектора 5 либо квадратичного де- тектора 4. Этот временной отрезок используется для взаимодействия вычислителя 11 с блоком 7 индикации 30 и блоком 10 регистрации.

На втором временном отрезке (фиг„ 59 е) АЦП 6 осуществляет преобразование сигнала детектора 12 экстремальных значений, используемое 5 для измерения занижений уровня. Во время этого отрезка времени вычислитель 11 осуществляет обработку информации, полученной на предыдущем временном отрезке.40

На третьем отрезке (фиг. 5, ж) АЦП 6 осуществляет преобразование сигнала детектора 12 экстремальных значений, используемое для измерения помех. На этом временном отрезке вычислитель 11 осуществляет обработку занижений уровня по стробу (фиг. 5, л) и отказов (занижения уровня относительного номинального более допустимого) по стробу (фиг. 5, м)

На четвертом временном отрезке (фиг„ 5, з) производится обработка сигналов помехь Этот сигнал используется для сброса в исходное состояние детектора 12 экстремальных значений

Формирователь 7 стробов обработки,, используя сигналы первого к второго регистров сдвига -+2 и 45, а так45

50

55

грамме измерении извлекается из оперативной памяти вычислителя 11 и по шине данных поступает в параллельно-последовательный интерфейс 9 и далее на вход блока 8 формирования контрольного сигнала, осуществляя амплитудную модуляцию сигнала. Пройдя через контролируемый канал 20, сформированный указанным методом сигнал поступает в входной блок 1 и далее через детектор 12 экстремаль ных значений, мультиплексный блок 13 выборки-хранения в АЦП 6, осущест вляющий преобразование амплитудного значения сигнала в цифровую форму, которая запоминается в буферном регистре 17 результатов и сравнивается блоком 19 сравнения с предварительно занесенным в буферный регистр 18 порогов, чем осуществляется демодуляция входной информации, поступаю щей через формирователь 16 адрес- векторов в вычислитель 11, который запоминает в своей оперативной памяти полученную информацию, i

В конце передаваемого пакета информации передается специальная кодовая комбинация, которая вычислителем 11 сравнивается с эталонной, после чего непосредственно начинается сеанс измерения параметров контролируемого канала 20 связи.

Кроме того, в программу начального пуска (запускается по команде пуска) включена пересылка в буферный регистр 18 порогов из вычислителя 11 полученных в результате программирования пороговых значений помех, коле-

0 Де пуска информация о заданной про-

5 0

5 0

5

0

5

грамме измерении извлекается из оперативной памяти вычислителя 11 и по шине данных поступает в параллельно-последовательный интерфейс 9 и далее на вход блока 8 формирования контрольного сигнала, осуществляя амплитудную модуляцию сигнала. Пройдя через контролируемый канал 20, сформированный указанным методом сигнал поступает в входной блок 1 и далее через детектор 12 экстремальных значений, мультиплексный блок 13 выборки-хранения в АЦП 6, осуществляющий преобразование амплитудного значения сигнала в цифровую форму, которая запоминается в буферном регистре 17 результатов и сравнивается блоком 19 сравнения с предварительно занесенным в буферный регистр 18 порогов, чем осуществляется демодуляция входной информации, поступающей через формирователь 16 адрес- векторов в вычислитель 11, который запоминает в своей оперативной памяти полученную информацию, i

В конце передаваемого пакета информации передается специальная кодовая комбинация, которая вычислителем 11 сравнивается с эталонной, после чего непосредственно начинается сеанс измерения параметров контролируемого канала 20 связи.

Кроме того, в программу начального пуска (запускается по команде пуска) включена пересылка в буферный регистр 18 порогов из вычислителя 11 полученных в результате программирования пороговых значений помех, коле-

баний уровня, отказов, мощности и т.д.

Контроль производится в три этапа На первом этапе контролируемый канал 20 контролируется по амплитудно-частотной характеристике. При этом на передаче блок 8 формирования контрольного сигнала генерирует сигналы номинальной амплитуды, частоты которых изменяются поочередно в соответствии с нормированными точками частотной характеристики. На приеме линейный детектор 5 и АЦП 6, управляемые временным распределителем 15, осуществляют измерение уровня входного сигнала на данной частоте. Результат измерения помещается в буферный регистр 17 результатов, откуда он считывается в оперативную память вычислителя 11. По окончании измерения происходит переключение частоты сигнала. Программа измерения АЧХ включает в себя несколько (например, пять) циклов изменения частоты, в процессе которых с целью исключения случайной составляющей погрешности измерений вычислитель 11 осуществляет усреднение результатов измерения уровня на каждой из частот. После окончания обработки вычислитель 11 выдает ее результаты в блок

7индикации и в параллельно-последовательный интерфейс 9, передающий информацию в блок 10 регистрации для документирования.

Следующим этапом контроля является измерение амплитудной характеристики контролируемого канала связи, заключающееся в измерении на приеме уровня сигнала (участвуют те же узлы, что и в предыдущем этапе) при установлении на передаче блоком

8формирования контрольного сигнала фиксированных значений уровня сигнала при номинальном значении частоты.

Программа данного этапа измерений также осуществляется в несколько циклов с последующим усреднением результатов и документированием.

На третьем этапе производится контроль контролируемого канала 20 связи по величине остаточного затухания, мощности интегральных шумов, кратковременным занижениям уровня, импульсным помехам, сдвигу частот и дрожанию фазы. Для этого в канал передается сигнал контрольной частот

.

10

15

20

78351б

от формирователя 8 ког трольного сигнала. На приеме сигнал после прохождения входного блока 1 поступает одновременно на входы формирователя 2 нуль-переходов, детектора 12 экстремальных значений, режекторного фильтра 3 и линейного детектора 5.

Сигнал формирователя 2 нуль-переходов (фиг. 5, б) кроме уже упомянутого формирователя 14 строба запуска поступает в формирователь 16 адрес- векторов, где взводит соответствующий триггер регистра 23, в результате чего формирователь 28 вырабатывает сигнал ТПР, поступающий в шину данных вычислителя 11, который прерывает выполнение своей фоновой программы и сигналом ППР передает управление устройству, запросившему прерывание. Этот сигнал сбрасывает формирователь 28 запроса прерываний и открывает второй магистральный приемопередатчик 26, который включает в шину дан- 2д ных сформированный шифратором 24 адрес-векторов по коду регистра 23 адрес программы обработки прерывания (сдвиг частоты и дрожание фазы). Этот сигнал, сопровождаемый сигналом СИП, сбрасывающим регистр 23, возвращает

управление вычислителю 11. i

Последний переходит- к выполнению подпрограммы обработки прерывания, начальный адрес которой указан в

„ ячейке оперативной памяти, на которую указывает адрес-вектор. В данном случае это - программа определения величины дрожания фазы и отклонения частоты, которая осуществляет считывание через магистральный приемо-пе- редатчик 25 информации со счетчика 22 длительности интервалов. Селектор 27 адреса обеспечивает обращение к конкретному внешнему устройству путем

45 сравнения действующих на шинах АД в

30

40

50

55

момент поступления сигнала СИА с запрограммированным кодом данного устройства. При этом величину отклонения частоты определяют путем вычисления разности усредненных значений, считанных со счетчика 22 длительности интервалов, и номинальной длительности периода сигнала. Величину дрожания фазы определяют как сумму максимального отрицательного и максимального положительного отклонения мгновенного значения, считанного со чика 22 длительности интервала, от его среднего значения. Указанная обработка производится вычислителем 11, индицируется блоком 7 индикации и документируется блоком 10 регистрации.

Режекторный фильтр 3 осуществляет подавление сигнала контрольной частоты на входе квадратичного детектора 4, формирующего сигнал, пропорциональный мощности шума в контролируе- мом канале. Сигнал линейного детектора 5 на данном этапе контроля используется для измерения стабильности остаточного затухания0 Детектор 12 экстремальных значений запоминает мгновенную амплитуду сигнала на каждом его полупериоде. Сигнал детектора 12 используется для анализа импульсных помех и кратковременных занижений уровня.

Мультиплексный блок 13 выборки- хранения в моменты, определяемые временным распределителем 15 (совпадение сигнала фиг. 5, г с одним из сигналов фиг. 5, в, г, и е) , поочередно запо- минает сигналы линейного детектора 5, квадратичного детектора 4 и детектора 12 экстремальных значений и во время действия сигналов (фиг„ 5, д, е и ж) передает их на вход АЦП 6. Последний преобразует сигнал в цифровой код, который заносится в буферный регистр 17 результатов (фиг. 5, о, п) Сигналы формирователя стробов обработки, входящего в состав временного распределителя 15, соответствующие измерению уровня и измерению мощности шумов, непосредственно поступающи на вход формирователя 16 адрес-векторов, переводят регистр 23 в соответствующее состояние, в результате чего по описанному алгоритму выполняются операции запроса и представления прерывания. При обработке прерываний осуществляется считывание информации из буферного регистра 17 результатов в оперативную память вычислителя 11. При последующей обработке результатов определяют средние значения полученных отсчетов, а для измерителя уровня его сравнивают с номинальным значением, определяя тем самым величину отклонения остаточного затухания.

Сигналы (фиг. 5, и - н) временного распределителя 15 используются для стробирования блока т9 сравнения, осуществляющего при обработке колебаний уровня, отказов к импульсных

JQ 5 0

5 о 0

5

0

5

помех сравнение кода, занесенного из АЦП ft в буферный регистр 17 результатов, с кодами порогов, занесенными в процессе программирования измерений в буферный регистр 18 порогов, адреса которых определяются шифратором считывания временного распределителя 15.

При совпадении строба обработки отказов (фиг. 5, м) и сигнала Меньше блока 19 сравнения взводится триггер 36, входящий в состав формирова - теля 16 адрес-векторов. По достижении указанного значения регистр 23 переводится в состояние, при котором обеспечивается переход вычислителя 11 к обработке прерывания по запросу анализатора 21 отказов, при котором блокируются измерения всех параметров. Для отказов определяют суммарную их длительность за сеанс контроля, а также количество отказов.

Обработка занижений уровня так же, как и отказов осуществляется во время действия сигнала (фиг. 5, ж) после.произведенного АЦП 6 преобра- в цифровую форму сигнала детектора 12 экстремальных значений и занесения в буферный регистр 17 результатов путем его сравнения с пороговым значением определенного стробом (фиг. 5, и) занижения уровня буферного регистра 18 порогов. Указанный строб при наличии сигнала Меньше на выходе блока 19 сравнения взводит триггер 31 анализатора 29 помех, который через элемент И 33 снимает блокировку со счетчика 32, входящего в анализатор 29. Последний отсчитывает длительность занижения и при своем переполнении переводит регистр 23 в состояние, вызывающее возникновение прерывания с соответствующим переполнением счетчика 32. По данному прерыванию вычислитель 11 увеличивает содержимое ячейки памяти на величину, равную емкости счетчика 32, входящего в состав анализатора 29. Указанные операции повторяются до завершения занижения уровня (пропадание сигнала Меньше на выходе блока 19 сравнения). При этом триггер 31 анализатора 29 возвращается в исходное состояние, блокируя счетчик 32 и переводя регистр 23 в соответствующее состояние, в резуль- LT3Te чего возникает прерывание со следующим адрес-вектором, при кото

914

ром вычислитель 11 увеличивает на единицу содержимое ячейки оперативно памяти.

Импульсные помехи измеряют аналогичным образом, сравнивая по стробу (фиг. 5, н) значение буферного регистра 17 результатов с порогом поме буферного регистра 18 порогов. Селекция помех осуществляется анализатором 29. Время пребывания (длительность) помех и их количество определяют аналогично занижению длительности уровня.

В процессе третьего этапа контроля параметров контролируемого канала 20 вычислитель 11 выводит промежуточные результаты измерения на блок 7 индикации и через параллельно-последовательный интерфейс 9 на блок 10 регистрации для документирования.

По окончании сеанса контроля вычислитель 11 осуществляет статическу обработку результатов измерения и документирует ее результаты.

Формула изобретения

0

8351

10

временной распределитель, первый выход которого соединен с первым входом аналого-цифрового преобразователя, а второй выход соединен с вторым входом формирователя адрес-векторов, последовательно соединенные буферный регистр порогов, первый вход которого соединен с шиной данных вычислителя, и блок сравнения, второй вход которого объединен с вторым входом буферного регистра порогов и соединен с третьим выходом временного распре делителя, а выход соединен с третьим входом формирователя адрес-векторов, буферный регистр результатов, первый вход которого соединен с шиной данных вычислителя, второй и третий входы соединены соответственно с вторым и третьим выходом аналого-цифрового преобразователя, а выход соединен с третьим входом блока сравнения, формирователь строба запуска, первый вход которого объединен с четвертым входом формирователя адрес-

0

25

векторов, и с выходом формирователя

0

5

нуль-переходов, второй вход объединен с пятым входом формирователя адрес- векторов, с первым входом временного распределителя, с вторым вхо- дом аналого-цифрового преобразовать-, ля и соединен с третьим выходом блока формирования контрольного сигнала, а выход соединен с вторым входом временного распределителя, детектор экстремального значения, первый вход которого соединен с выходом входного блока, а второй вход соединен с четвертым выходом временного распределителя, а также мультиплексный блок 0 выборки-хранения, первый, второй, третий и четвертый входы которого соединены соответственно с выходом детектора экстремального значения, с выходом квадратичного детектора, с выходом линейного детектора и с пятым выходом временного распределителя, а выход соединен с третьим входом аналого-цифрового преобразователя, при этом, второй выход параллельно-последовательного интерфейса соединен с вторым входом блока формирования контрольного сигнала. 2. Устройство по п. 1, отличающееся тем, что формирователь адрес-векторов содержит пер-; вый и второй магистральные приемопередатчики, счетчик длительности интервалов, выход которого соединен с первым входом первого магистрального

5

0

5

10

приемопередатчика, последовательно соединенные регистр и нтфратор, выход которого соединен с первым входом второго магистрального приемопередатчика, формирователь запроса прерывания, первый вход которого соединен с выходом регистра, а второй вход объединен с вторым входом второго магистрального приемопередатчика, анализатор помех, первый вход которого объединен с первым С-входом регистра, второй вход объединен с вторым С-входом регистра, первый выход соединен с вторым входом 15 первого магистрального приемопередатчика, второй выход соединен с первым и вторым D-входами регистра, третий вход соединен с первым выходом первого магистрального приемопередатчика и с R-входом регистра, а третий и четвертый выходы соединены соответственно с третьим и четвертым С-входами регистра, пятый С-вход которого объединен с R-входом счетчика длительности интервалов, анализатор отказов, первый вход которого объединен с четвертым входом анализатора помех, второй вход объединен с пятым

при этом R-вход счетчика длительнос интервалов является четвертым входом формирователя адрес-векторов, первый и второй входы анализатора помех,, в рой вход анализатора отказов и седьмой и восьмой С-входы регистра являются вторым входом формирователя адрес-векторов, второй вход анализатор отказов является пятым входом формирователя адрес-векторов, четвертый и шестой входы анализатора помех являются третьим входом формирователя адрес-векторов, а второй выход первого магистрального приемопередатчика, второй вход селектора адреса, выход второго магистрального, приемопередатчика, выход формирователя запроса прерываний и второй вход второго магистрального приемопередатчика являются вторым входом формирователя адрес-векторов.

20

25

входом анализатора помех и с С-входом 30 a также элемент И, пятый вход которого является первым входом формирователя строба запуска, второй вход соединен с инверсным выходом триггера, а выход соединен с R-входом счет чика-распределителя, С-вход которого 35 является вторым входом формирователя строба запуска, а первый и второй вы ходы соединены.соответственно с входом одновибратора и С-входом триггер

счетчика длительности интервалов, а выход соединен с шестым С-входом регистра, а также селектор адреса, первый вход которого соединен с третьим входом второго магистрального приемопередатчика и объединен с вторым выходом первого магистрального -приемопередатчика, третий вход которого соединен с выходом селектора адреса,

10

15

7835112

при этом R-вход счетчика длительности интервалов является четвертым входом формирователя адрес-векторов, первый и второй входы анализатора помех,, второй вход анализатора отказов и седьмой и восьмой С-входы регистра являются вторым входом формирователя адрес-векторов, второй вход анализатора отказов является пятым входом формирователя адрес-векторов, четвертый и шестой входы анализатора помех являются третьим входом формирователя адрес-векторов, а второй выход пер вого магистрального приемопередатчика, второй вход селектора адреса, выход второго магистрального, приемопередатчика, выход формирователя запроса прерываний и второй вход второго магистрального приемопередатчика являются вторым входом формирователя адрес-векторов.

20

25

a также элемент И, пятый вход которого является первым входом формирователя строба запуска, второй вход соединен с инверсным выходом триггера, а выход соединен с R-входом счетчика-распределителя, С-вход которого является вторым входом формирователя строба запуска, а первый и второй выходы соединены.соответственно с входом одновибратора и С-входом триггера.

Фиг.З

п.

ж

3

ц к л м н о

пп

ФигЛ

п

ПП

П П

П

п

П

п

п

П

П.

ГЗ

Фиг. 5

IiI

a JLI

5II f i I I I I I I M I I I I I I t I I M I I

6II till

ппПQ.

Фиг. 6

| Устройство для контроля канала связи | 1985 |

|

SU1249711A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1989-05-07—Публикация

1987-05-14—Подача