Ј

00

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь частотно-модулированных сигналов | 1989 |

|

SU1702515A1 |

| Формирователь повторяющихся частотно-модулированных сигналов | 1988 |

|

SU1555806A1 |

| Формирователь линейно-частотно-модулированных сигналов | 1987 |

|

SU1494203A1 |

| Формирователь частотно-модулированных сигналов | 1990 |

|

SU1732420A1 |

| Синтезатор частот | 1987 |

|

SU1501246A1 |

| ИМИТАТОР ПАССИВНОГО РАДИОЛОКАТОРА | 1988 |

|

SU1841093A2 |

| Синхронный режекторный фильтр | 1986 |

|

SU1413699A1 |

| ЧАСТОТНО-МОДУЛИРОВАННЫЙ РАДИОВЫСОТОМЕР | 2003 |

|

RU2263330C2 |

| СЧЕТЧИК АКТИВНОЙ ЭНЕРГИИ С ЧАСТОТНЫМ ВЫХОДОМ | 1992 |

|

RU2037830C1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ЗАПИСИ И ВОСПРОИЗВЕДЕНИЯ ЭЛЕКТРОННЫХ СИГНАЛОВ ЦВЕТНОГО ИЗОБРАЖЕНИЯ ОБЪЕКТОВ (ВАРИАНТЫ) | 2003 |

|

RU2258319C2 |

Изобретение относится к радиотехнике. Цель изобретения - повышение линейности модуляционной х-ки при использовании цифрового модулирующего сигнала. Формирователь содержит опорный г-р 1, управляемый г-р 2, сумматор 3, ЦАП 4 и 5, суммирующий интегрирующий эл-т 6, вычитатель 7, частотный дискриминатор 8 и преобразователь 9 частота-код. При использовании цифрового модулирующего сигнала он преобразуется в ЦАП 4 в аналоговый сигнал и через сумматор 3 поступает на управляющий вход г-ра 2, меняя его выходную частоту на заданную величину. Далее преобразователь 9 преобразует эту величину в частоту, а затем в код, который вычитается из цифрового сигнала в вычитателе 7. Остаток через ЦАП 5 поступает на вход эл-та 6 до тех пор, пока полученный код не будет равен цифровому сигналу. Цель достигается введением сумматора 3, ЦАП 4 и 5, вычитателя 7 и преобразователя 9. 1 ил.

О

оо

00

Изобретение относится к радиотехнике и может использоваться в системах передачи и приема информации.

Цель изобретения - повышение линейности модуляционной характеристики при использовании цифрового модулирующего сигнала.

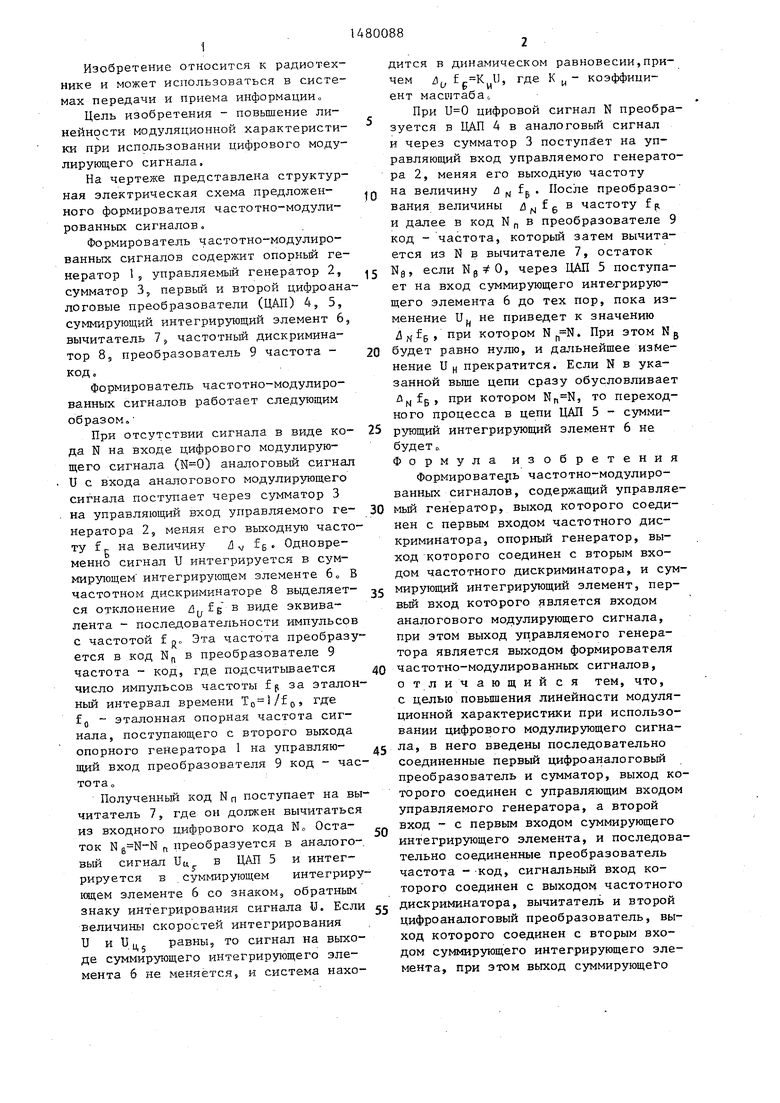

На чертеже представлена структурная электрическая схема предложенного формирователя частотно-модулированных сигналов,

Формирователь частотно-модулированных сигналов содержит опорный генератор ls управляемый генератор 2, сумматор 35 первьй и второй цифроана- логовые преобразователи (ЦАП) 4, 5, суммирующий интегрирующий элемент 6, вычитатель 7, частотный дискриминатор 8Э преобразователь 9 частота - код о

Формирователь частотно-модулированных сигналов работает следующим образом.

При отсутствии сигнала в виде кода N на входе цифрового модулирующего сигнала () аналоговый сигнал U с входа аналогового модулирующего сигнала поступает через сумматор 3 на управляющий вход управляемого ге нератора 2, меняя его выходную частоту fp на величину 4V f6. Одновременно сигнал U интегрируется в суммирующем интегрирующем элементе 6„ В частотном дискриминаторе 8 выделяется отклонение д f g в виде эквивалента - последовательности импульсов с частотой f о- Эта частота преобразуется в код Nn в преобразователе 9 частота - код, где подсчитывается число импульсов частоты fp за эталонный интервал времени , где f0 - эталонная опорная частота сигнала, поступающего с второго выхода опорного генератора 1 на управляющий вход преобразователя 9 код - частота

Полученный код N п поступает на вычитатель 7, где он должен вычитаться из входного цифрового кода Ш„ Остаток N n преобразуется в аналоговый сигнал 11Ц в ЦАП 5 и интегрируется в суммирующем интегрирующем элементе 6 со знаком, обратным знаку интегрирования сигнала U. Если величины скоростей интегрирования U и Uц равны5 то сигнал на выходе суммирующего интегрирующего элемента 6 не меняется, и система находится в динамическом равновесии,причем ди f K U, где К и- коэффициент масштаба.

При цифровой сигнал N преобразуется в ЦАП 4 в аналоговый сигнал и через сумматор 3 поступает на управляющий вход управляемого генератора 2, меняя его выходную частоту

д на величину и N fБ . После преобразования величины 4Nf6 в частоту fp и далее в код N п в преобразователе 9 код - частота, который затем вычитается из N в вычитателе 7, остаток

5 Nfl, если , через ЦАП 5 поступает на вход суммирующего интегрирующего элемента 6 до тех пор, пока изменение U не приведет к значению 4Nf6, при котором . При этом NB

0 будет равно нулю, и дальнейшее изменение U H прекратится. Если N в указанной выше цепи сразу обусловливает aNfB, при котором , то переходного процесса в цепи ЦАП 5 - сумми5 рующий интегрирующий элемент 6 не будет „ Формула изобретения

Формирователь частотно-модулированных сигналов, содержащий управляе0 мый генератор, выход которого соединен с первым входом частотного дискриминатора, опорный генератор, выход которого соединен с вторым входом частотного дискриминатора, и сум5 мирующий интегрирующий элемент, первый вход которого является входом аналогового модулирующего сигнала, при этом выход управляемого генератора является выходом формирователя

0 частотно-модулированных сигналов, отличающийся тем, что, с целью повышения линейности модуляционной характеристики при использовании цифрового модулирующего сигна5 ла, в него введены последовательно соединенные первый цифроаналоговый преобразователь и сумматор, выход которого соединен с управляющим входом управляемого генератора, а второй

вход - с первым входом суммирующего интегрирующего элемента, и последовательно соединенные преобразователь частота - код, сигнальный вход которого соединен с выходом частотного

5 дискриминатора, вычитатель и второй цифроаналоговый преобразователь, выход которого соединен с вторым входом суммирующего интегрирующего элемента, при этом выход суммирующего

314800884

интегрирующего элемента соединен саналогового преобразователя и второй третьим входом сумматора, второй вы-вход вычитателя соединены между со- ход опорного генератора соединен сбой и точка их соединения является управляющим входом преобразователя входом цифрового модулирующего сиг- частота - код, вход первого цифро-нала.

| Электросвязь, 1984, № 6, с.53 | |||

| I |

Авторы

Даты

1989-05-15—Публикация

1986-12-18—Подача