Изобретение относится к электронной технике, в частности к способу изоляции активных областей монолитной интегральной схемы (МИС) с помощью протонной бомбардировки.

Целью изобретения является повышение процента выхода годных изделий путем улучшения электрических параметров транзисторов.

Согласно изобретению канал транзистора формируют с помощью анодного окисления арсенида галлия. Выращенный анодный окисел не удаляют, а на него наносят фоторезист. После формирования фоторезистивной маски производят протонную бомбардировку, превращая незащищенные фоторезистом участки арсенида галлия в изолятор, затем задубленный фоторезист удаляется с помощью плазмохимического травления. Анодный окисел при этом защищает поверхность арсенида галлия от отрицательного воздействия плазмы. В дальнейшем окисел легко удаляется в растворе плавиковой кислоты.

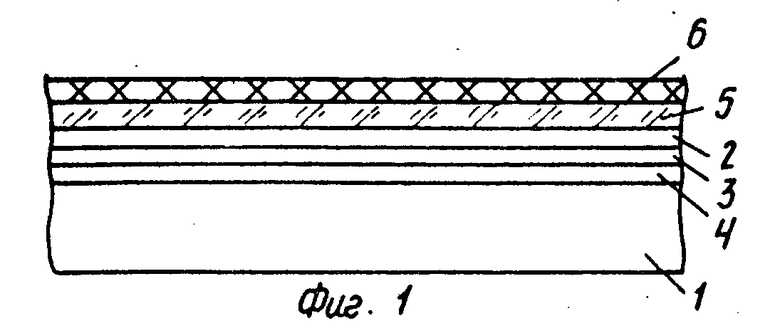

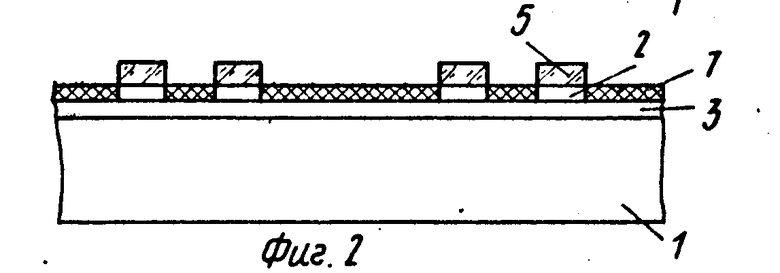

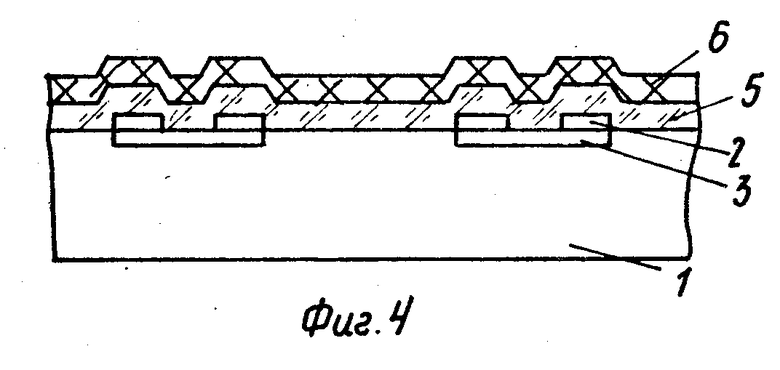

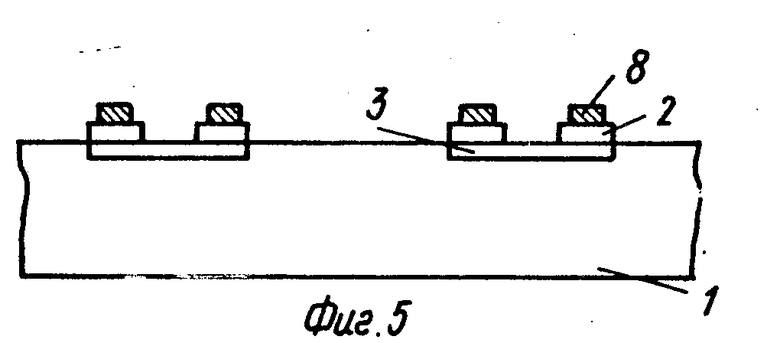

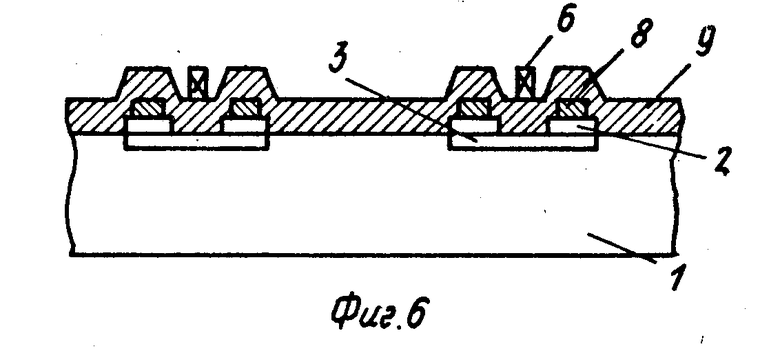

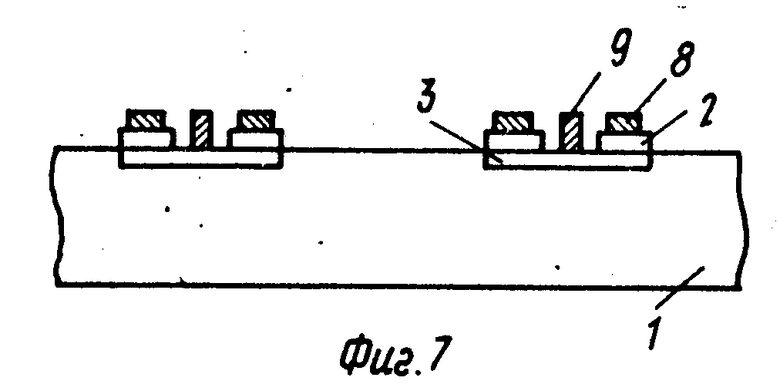

На фиг. 1-7 изображена последовательность технологических операций при изготовлении МИС на GaAs, где приняты следующие обозначения: полуизолирующая подложка 1, эпитаксиальный слой 2 n-типа, эпитаксиальный слой 3 n-типа, буферный слой 4 i-типа, слой 5 двуокиси кремния, фоторезист 6, анодный окисел 7, система металлизации омических контактов 8 на основе AuGe, алюминиевая пленка 9.

Согласно изобретению арсенид галлиевая МИС изготавливается на полуизолирующей подложке 1 (фиг.1) со структурой эпитаксиальных слоев 2-n+-, 3-n-, 4-i-типа.

Способ изготовления МИС включает следующие технологические этапы: отмывки GaAs пластин и осаждение слоя 5 двуокиси кремния. Нанесение фоторезиста 6 и фотолитография для создания маски активных каналов полевых транзисторов. Ионно-химическое травление двуокиси кремния и удаление фоторезистивной маски. Создание анодного окисла 7 GaAs (фиг.2) путем анодного окисления в электролите в потенциостатическом режиме на толщину n+-слоя. Нанесение фоторезиста и формирование маски фоторезиста 6 (фиг.3) для защиты активных областей. При проявлении фоторезиста в щелочном растворе анодный окисел GaAs удаляют на незащищенных фоторезистором участках поверхности пластины. Протонную бомбардировку проводят в двух режимах: сначала с энергией 50 кэВ и дозой 50 мкКл·см-2, а потом с энергией 100 кэВ и дозой мкКл·см-2. Затем удаляют фоторезистивную маску с помощью плазмохимического травления и одновременно удаляют анодный окисел GaAs и двуокиси кремния в растворе плавиковой кислоты. Нанесение слоя 5 двуокиси кремния (фиг.4) и нанесение фоторезиста 6. Формирование окон истоков и стоков транзисторов в фоторезисте, ионно-химическое травление двуокиси кремния, удаление фоторезиста. Напыление контактного сплава AuGe Ni Au (фиг.5) и "взрыв" контактного сплава, лежащего на слое 5 двуокиси кремния. Вжигание контактного сплава при 420-450оС в течение 2 с. Напыление алюминиевой пленки 9 металлизации затворов (фиг.6), нанесение фоторезиста 6 и формирование в нем рисунка затворов. Травление затворной металлизации (фиг.7), удаление фоторезиста.

Преимущество данного способа изготовления МИС заключается в отсутствии технологических операций, связанных с нанесением и травлением сложных систем для защиты в процессе протонной бомбардировки.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛУПРОВОДНИКОВЫХ ПРИБОРОВ | 1992 |

|

RU2029413C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛУПРОВОДНИКОВОГО ПРИБОРА С УПРАВЛЯЮЩИМ ЭЛЕКТРОДОМ СУБМИКРОННОЙ ДЛИНЫ | 1991 |

|

RU2031481C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛЕВЫХ ТРАНЗИСТОРОВ С САМОСОВМЕЩЕННЫМ ЗАТВОРОМ СУБМИКРОННОЙ ДЛИНЫ | 2010 |

|

RU2436186C2 |

| Способ изготовления полевых транзисторов на арсениде галлия | 1990 |

|

SU1831731A3 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛУПРОВОДНИКОВЫХ ПРИБОРОВ | 1990 |

|

SU1823715A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛУПРОВОДНИКОВЫХ ПРИБОРОВ | 1992 |

|

RU2031479C1 |

| СПОСОБ СОЗДАНИЯ ПОЛУПРОВОДНИКОВЫХ ПРИБОРОВ | 1979 |

|

SU807915A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛУПРОВОДНИКОВЫХ ПРИБОРОВ | 1991 |

|

SU1811330A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛЕВОГО ТРАНЗИСТОРА С БАРЬЕРОМ ШОТТКИ | 2007 |

|

RU2349987C1 |

| Способ изготовления СВЧ полевого мощного псевдоморфного транзистора | 2016 |

|

RU2633724C1 |

Изобретение относится к электронной технике, в частности, к способу изоляции монолитных интегральных схем путем протонной бомбаридовки. Цель изобретения - повышение выхода годных изделий путем улучшения электрических параметров транзисторов. Это достигается тем, что в способе изготовления арсенид-галлиевой монолитной интегральной схемы, включающем создание изоляции активных областей протонной бомбардировкой, фоторезистивную маску наносят на предварительно созданный в процессе формирования активного канала транзистора анодный окисел арсенида галлия и при протонной бомбаридовке фоторезистивную маску используют в качестве защитного покрытия активных областей. 7 ил.

СПОСОБ ИЗГОТОВЛЕНИЯ АРСЕНИД-ГАЛЛИЕВОЙ ИНТЕГРАЛЬНОЙ СХЕМЫ на структурах n+ - n - i - типа, включающий анодное окисление n+ - слоя по всей поверхности пластины за исключением областей истока и стока полевых транзисторов путем маскирования этих областей слоем двуокиси кремния, создание омических контактов на основе металлизации AuGe, формирование изоляции активных областей транзисторов протонной бомбардировкой с использованием в качестве защитного покрытия над активными областями полевых транзисторов фоторезистивной маски, формирование алюминиевых затворов, отличающийся тем, что, с целью повышения выхода годных изделий путем улучшения электрических параметров транзисторов, после проведения анодного окисления n+ - слоя по всей поверхности пластины за исключением исток-стоковых областей полевых транзисторов, активные области полевых транзисторов покрывают фоторезистивной маской, удаляют анодный окисел с пассивных областей интегральных микросхем, производят формирование изоляции активных областей полевых транзисторов путем протонной бомбардировки, используя в качестве защитного покрытия над исток-стоковыми областями двухслойной системы фоторезист - двуокись кремния, а в качестве защитного покрытия над областями каналов двухслойной системы фоторезист - анодный окисел арсенида галлия.

| В.Е.Дединец и др | |||

| СВЧ монолитная интегральная каскадная схема на арсениде галлия | |||

| - Электронная техника, сер.2 | |||

| Полупроводниковые приборы, вып.7(150), 1981, с.47 | |||

| D.C | |||

| D A vanzo Proton Isolation for Ga As Integrated circuits IEEE Trans an Electron Devices, vol.29, N 7, 1982, p.1051-1058. |

Авторы

Даты

1996-01-10—Публикация

1987-05-27—Подача