i

(Л С

AIM « WiPpUi.

3149

плтель 4 сигнала оценки, блоки 5 и 9 задержки, коммутатор 6, ана.читатор 7 ви;1еоси1 нала, обнаружитель 8 н формирователь 17 порогов. Цель достигается пведенисм (тзмсрителя 10 игума, блока 11 выбора максимл ма, блоков 12 и 13 интеграторов областей кадра, блока 14 памяти, блока 15 обработки и запоминающего блока 16. В устр-ве производится селекция движущихся объектов, которые перемещаются от кадра к кадру на величину, превышающую их линейные размеры, и предотвращается их об)1ар жение как дефек-

74

тов кинопленки, В устр-ве также ис- пол1)3уется а;1аптивная регулировка прога обнаружения в зависимости от уровня шума в кадрах кинофильма и адаптив)1ое формирование сигнала замещения дефектных эл-тов изображения. Возможность оперативной регулировки размеров областей анализа позволяет установить их оптимальные размеры в зависимости от формата кинопленки и содержания изображейия и запрограммировать эти размеры при предварительном просмотре кинофильма. 7 з.п. ф-лы, 14 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство компенсации сигнала царапин кинопленки | 1986 |

|

SU1392635A1 |

| Устройство компенсации сигнала царапин кинопленки | 1988 |

|

SU1536521A2 |

| Формирователь сигнала оценки дефектных элементов изображения в телекинопроекционной системе | 1984 |

|

SU1233300A1 |

| Устройство для бинарного квантования телевизионного видеосигнала | 1983 |

|

SU1129745A1 |

| ТЕЛЕВИЗИОННЫЙ КООРДИНАТНЫЙ ДИСКРИМИНАТОР | 1996 |

|

RU2139640C1 |

| Система передачи телевизионногоСигНАлА | 1979 |

|

SU794774A1 |

| Устройство для автоматического фазирования кадра телекинопроекционной системы | 1985 |

|

SU1244805A2 |

| Устройство для контроля видеосигнала | 1982 |

|

SU1069190A1 |

| Устройство компенсации сигнала дефектов киноленты | 1984 |

|

SU1202074A1 |

| Устройство компенсации сигнала дефектов киноленты | 1985 |

|

SU1322503A2 |

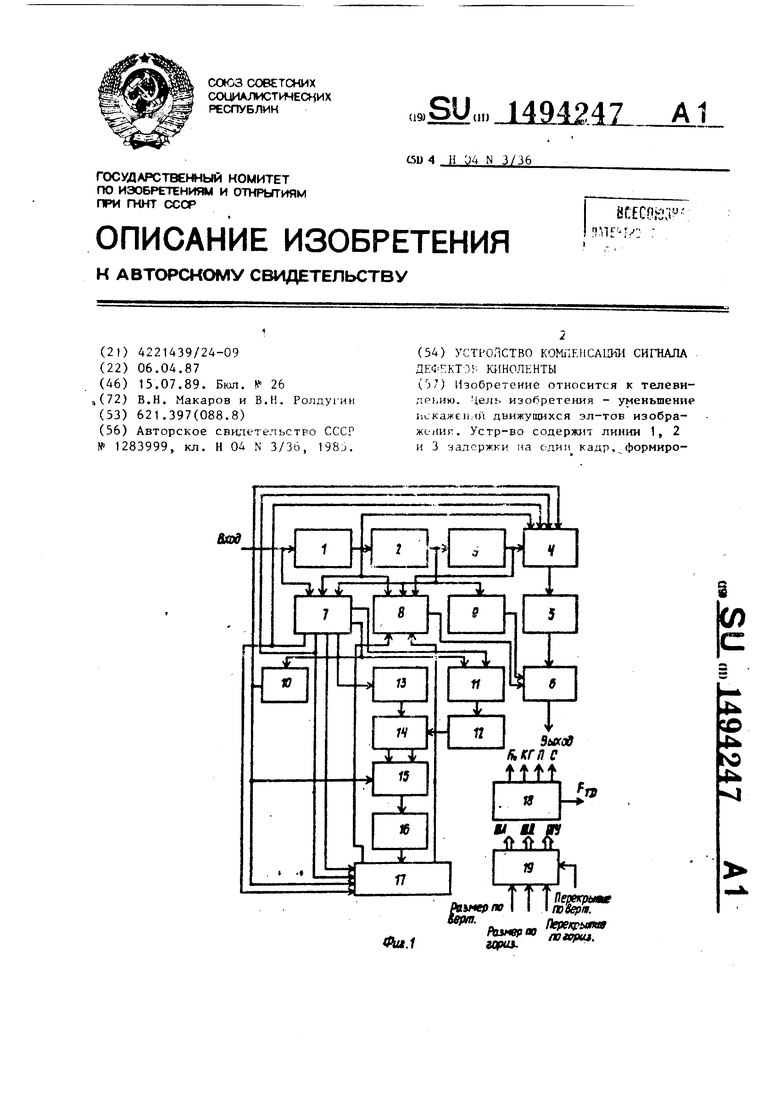

Изобретение относится к телевидению. Цель изобретения - уменьшение искажений движущихся эл-тов изображения. Устройство содержит линии 1, 2 и 3 задержки на один кадр, формирователь 4 сигнала оценки, блоки 5 и 9 задержки, коммутатор 6, анализатор 7 видеосигнала, обнаружитель 8 и формирователь 17 порогов. Цель достигается введением измерителя 10 шума, блока 11 выбора максимума, блоков интеграторов 12 и 13 областей кадра, блока 14 памяти, блока 15 обработки и запоминающего блока 16. В устройстве производится селекция движущихся объектов, которые перемещаются от кадра к кадру на величину, превышающую их линейные размеры, и предотвращается их обнаружение как дефектов кинопленки. В устройстве также используется адаптивная регулировка порога обнаружения в зависимости от уровня шума в кадрах кинофильма и адаптивное формирование сигнала замещения дефектных эл-тов изображения. Возможность оперативной регулировки размеров областей анализа позволяет установить их оптимальные размеры в зависимости от формата кинопленки и содержания изображения и запрограммировать эти размеры при предварительном просмотре кинофильма. 7 з.п. ф-лы, 14 ил.

Изобретение относится к телекино и может быть использовано при построении устройств компенсации сигналов дефекгов киноленты в телевизионной аппаратуре для передачи ки- иофильмов.

Цель изобретения - уменьшение ис- кажеииГ движущухся элементов изображения .

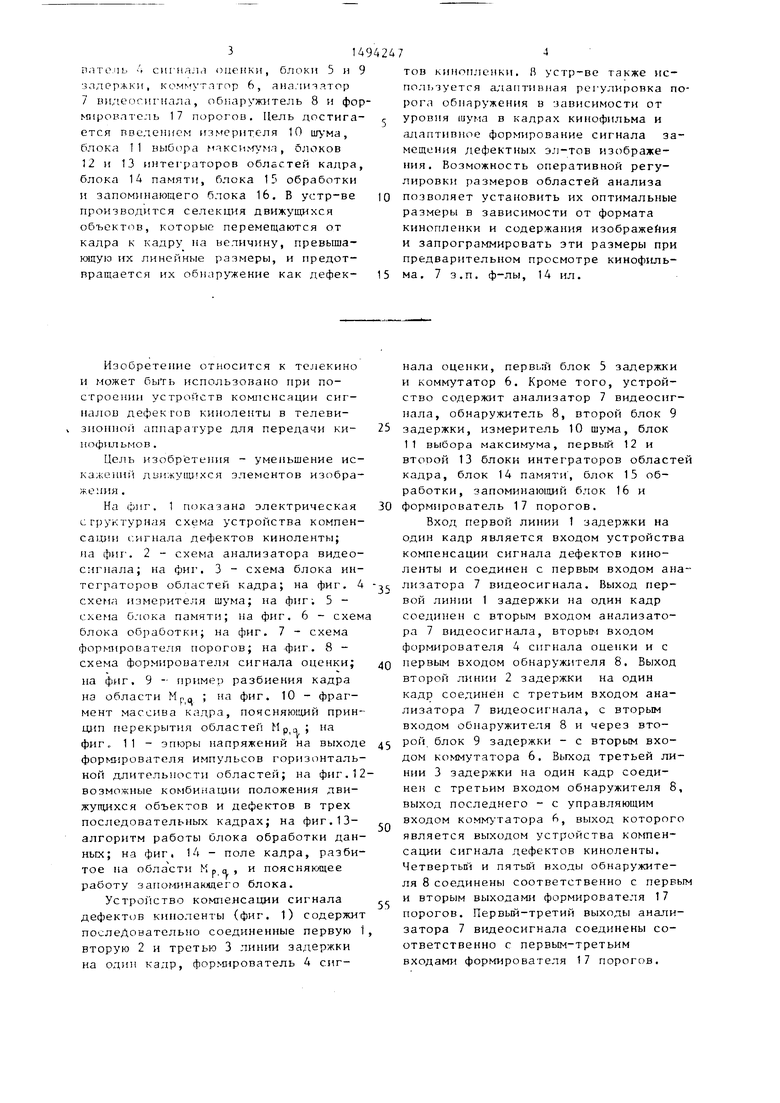

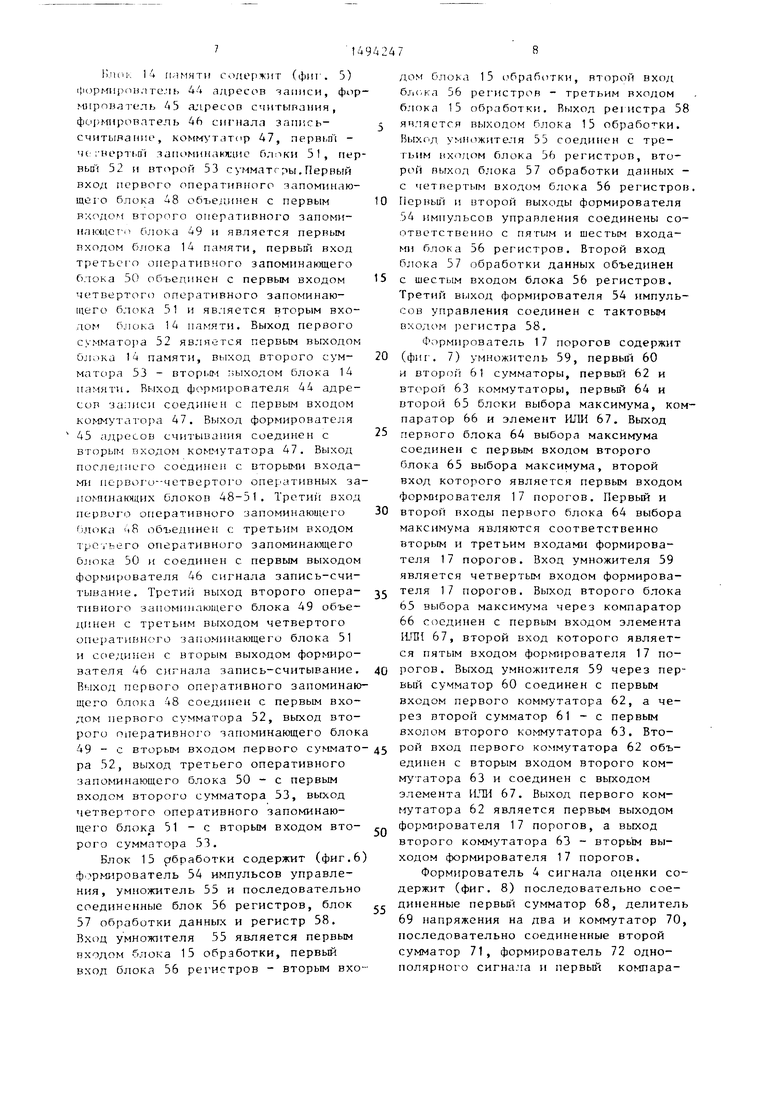

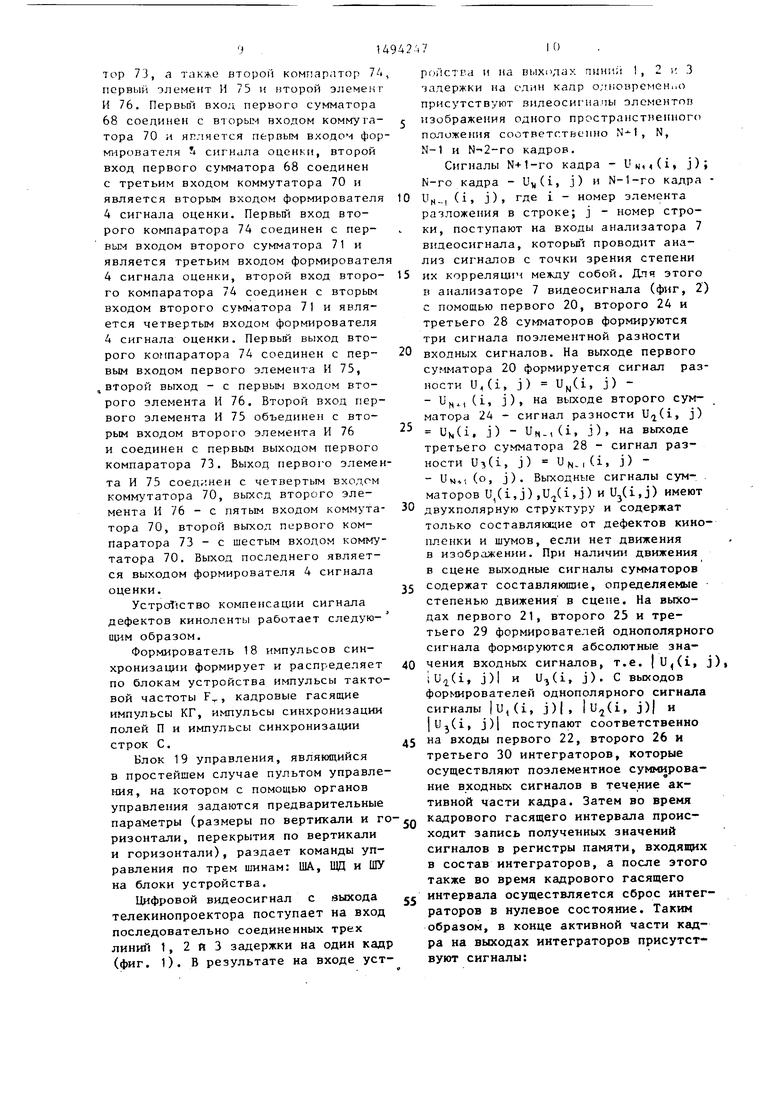

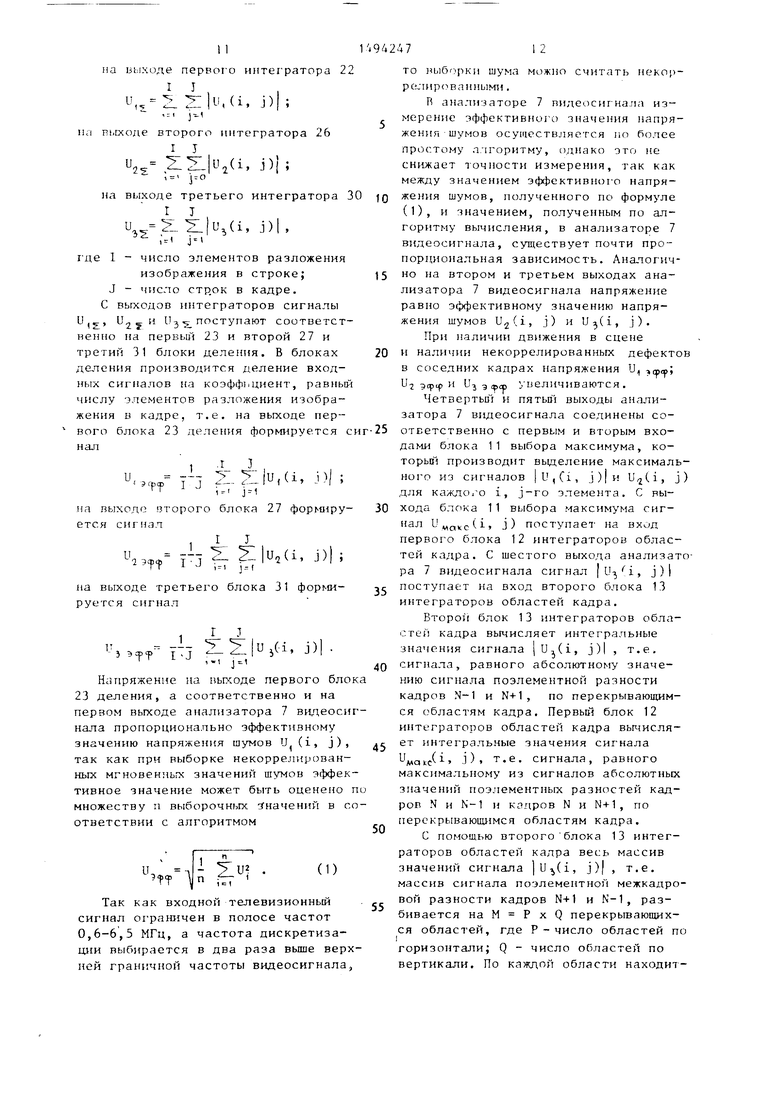

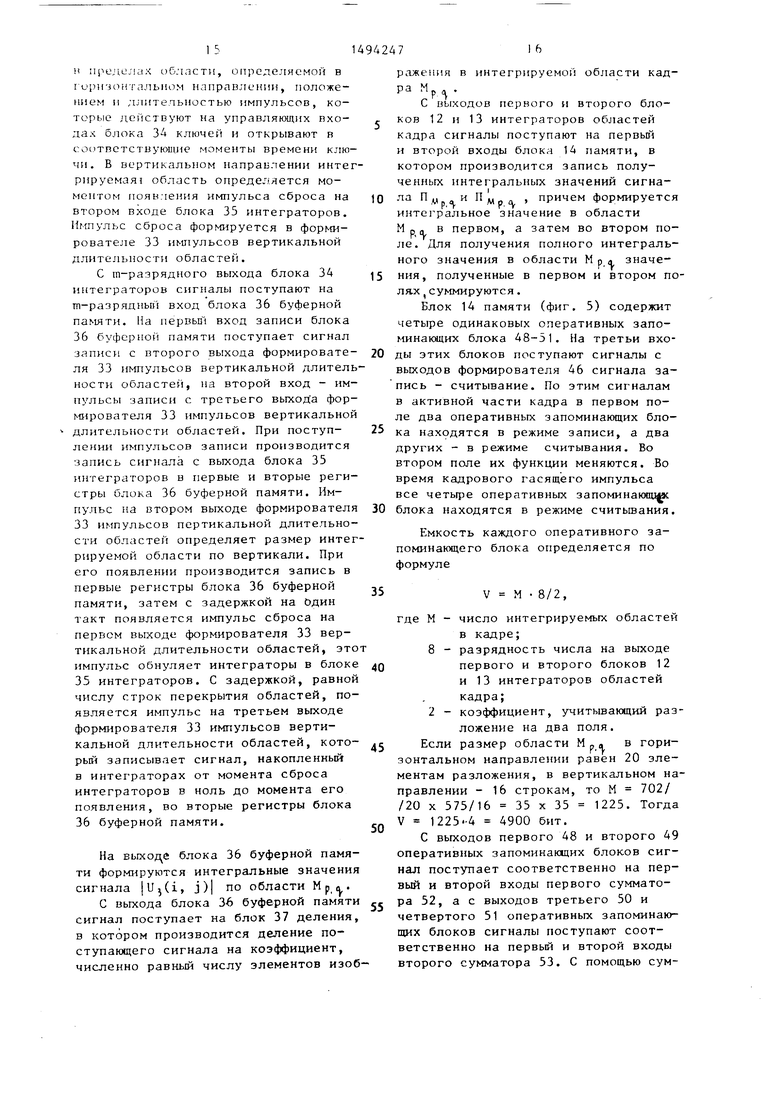

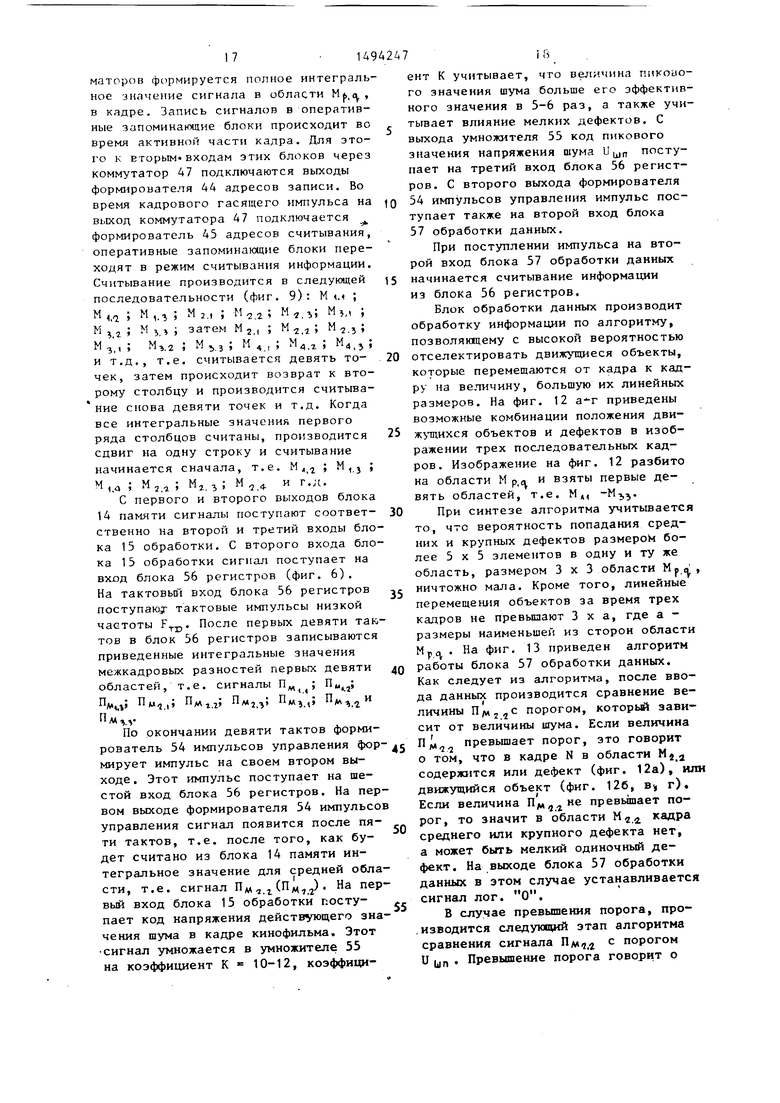

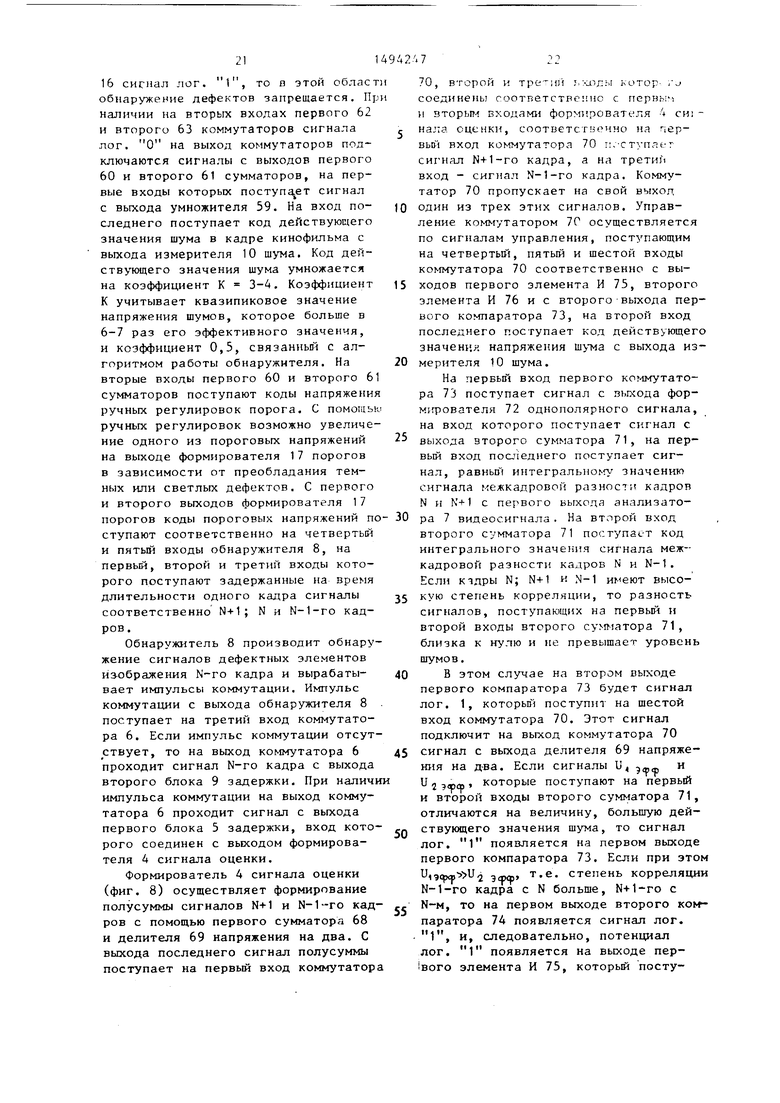

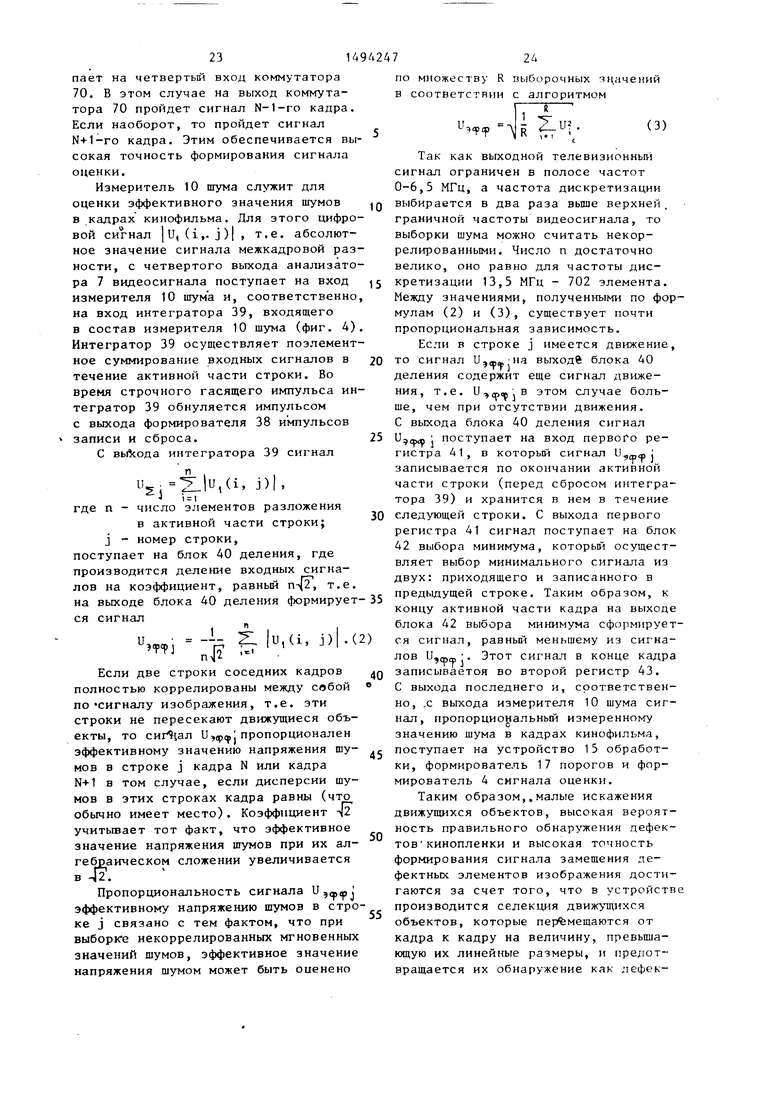

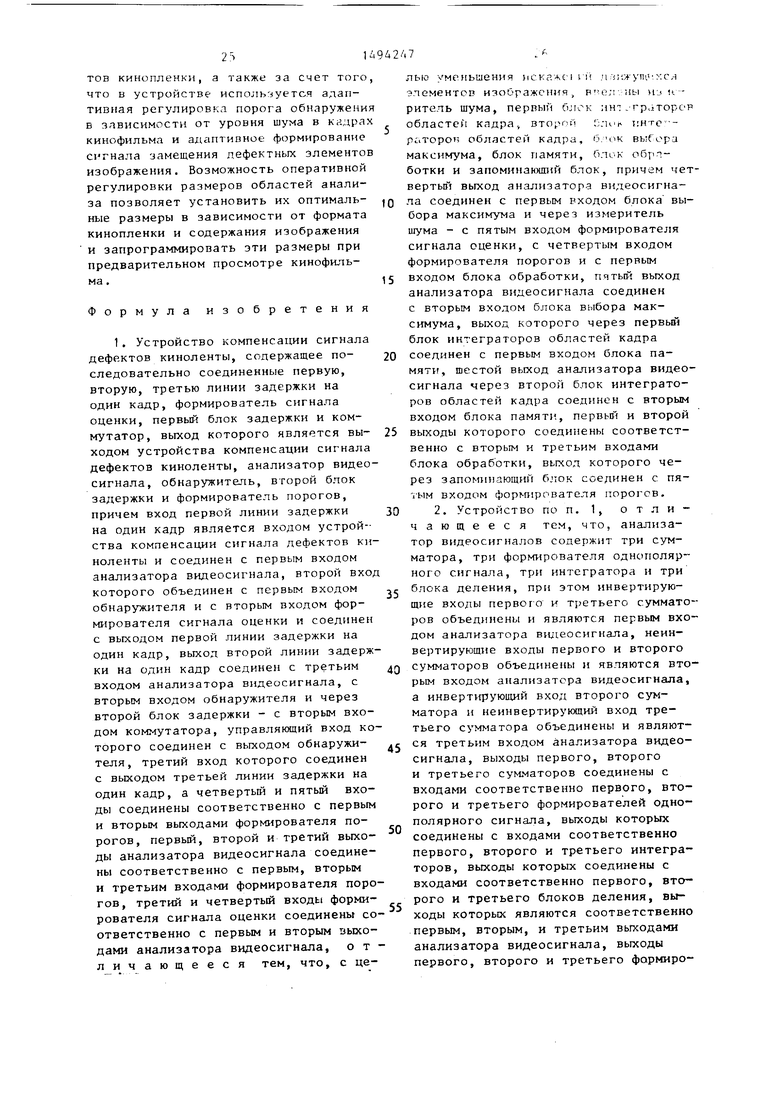

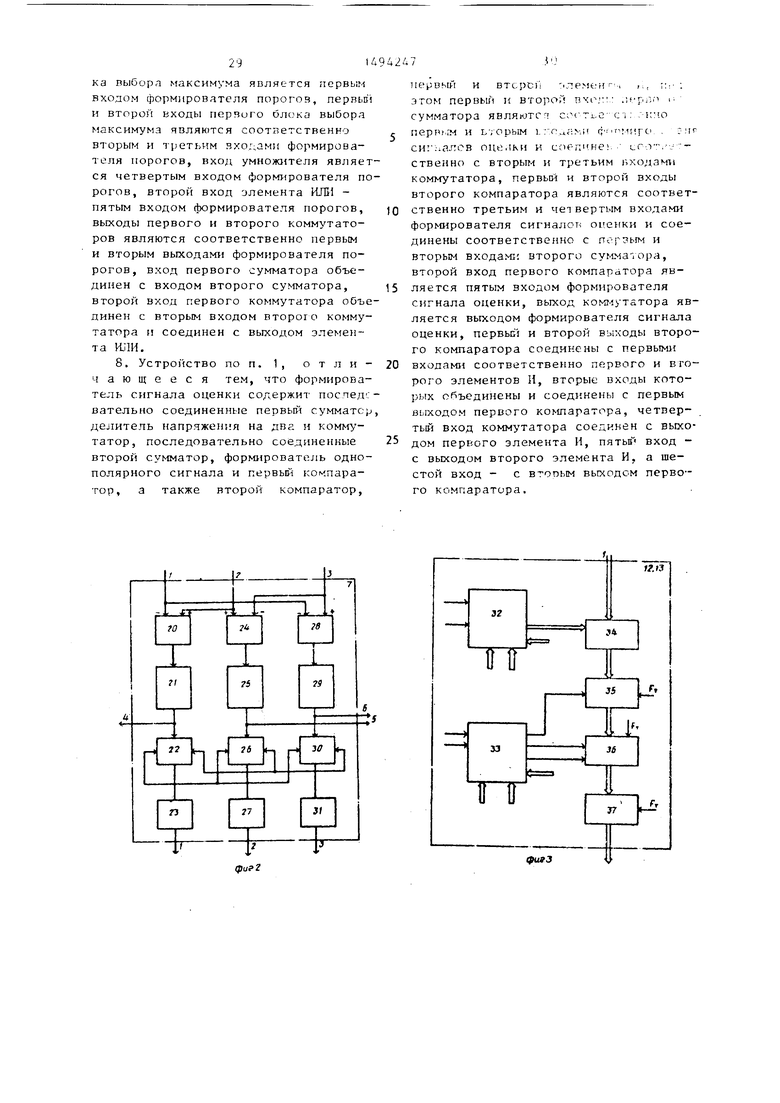

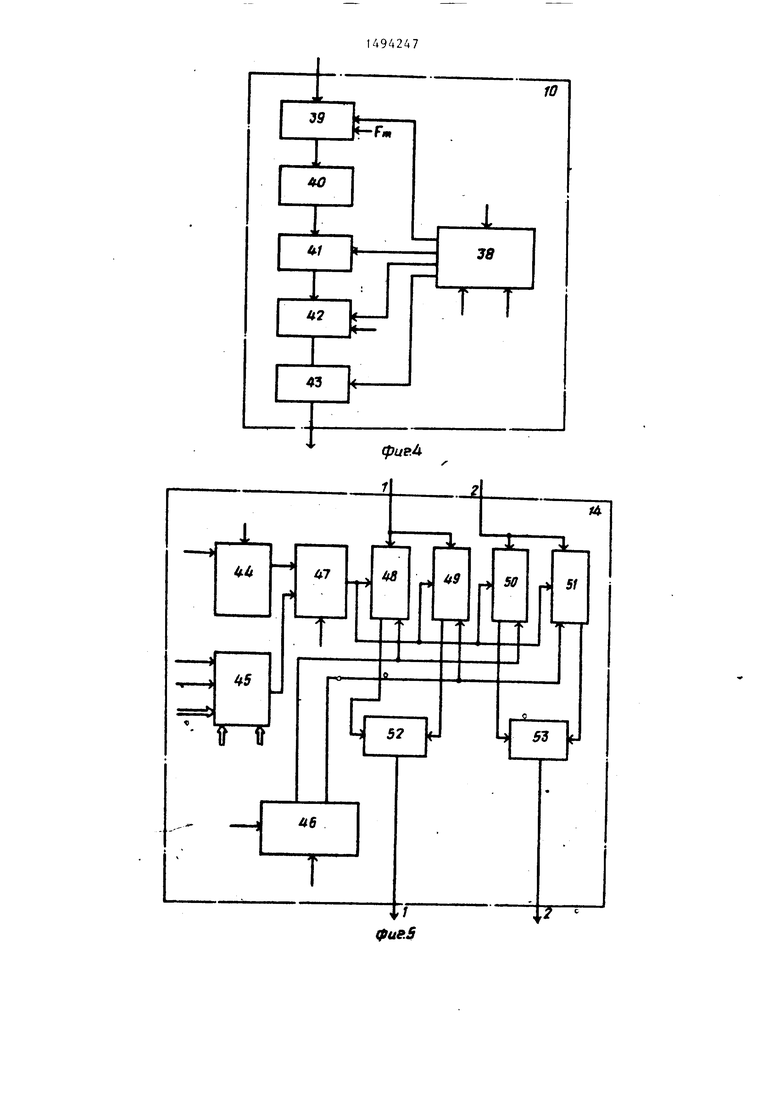

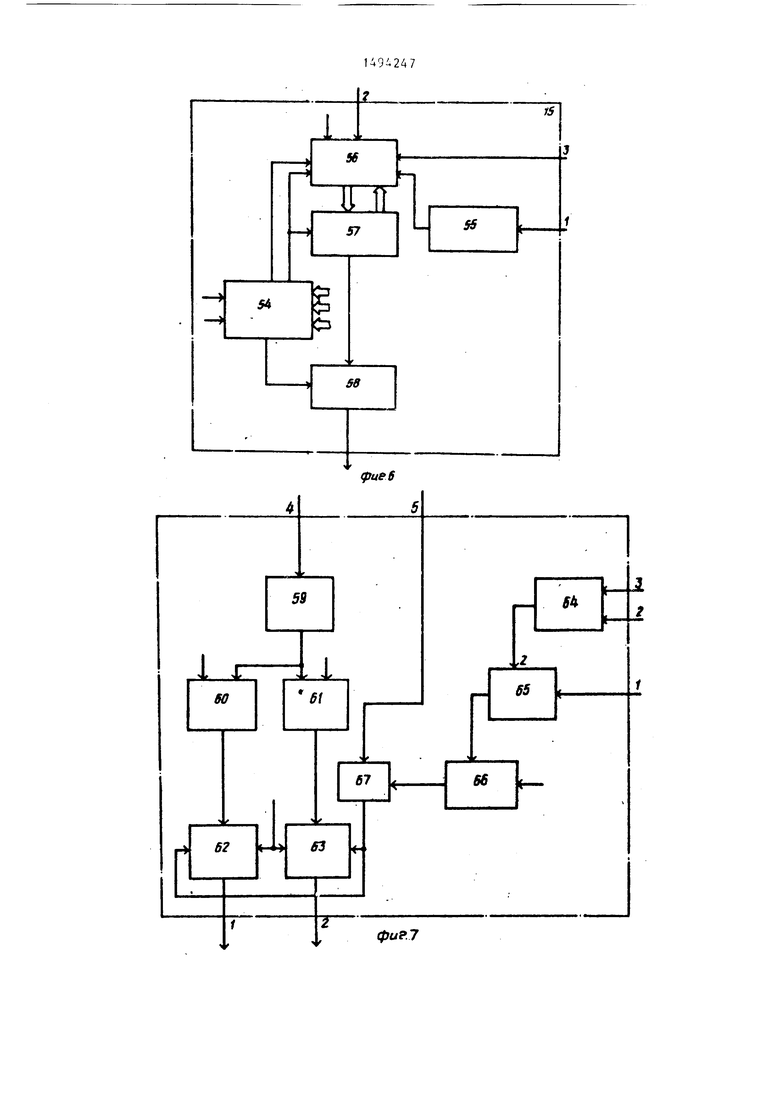

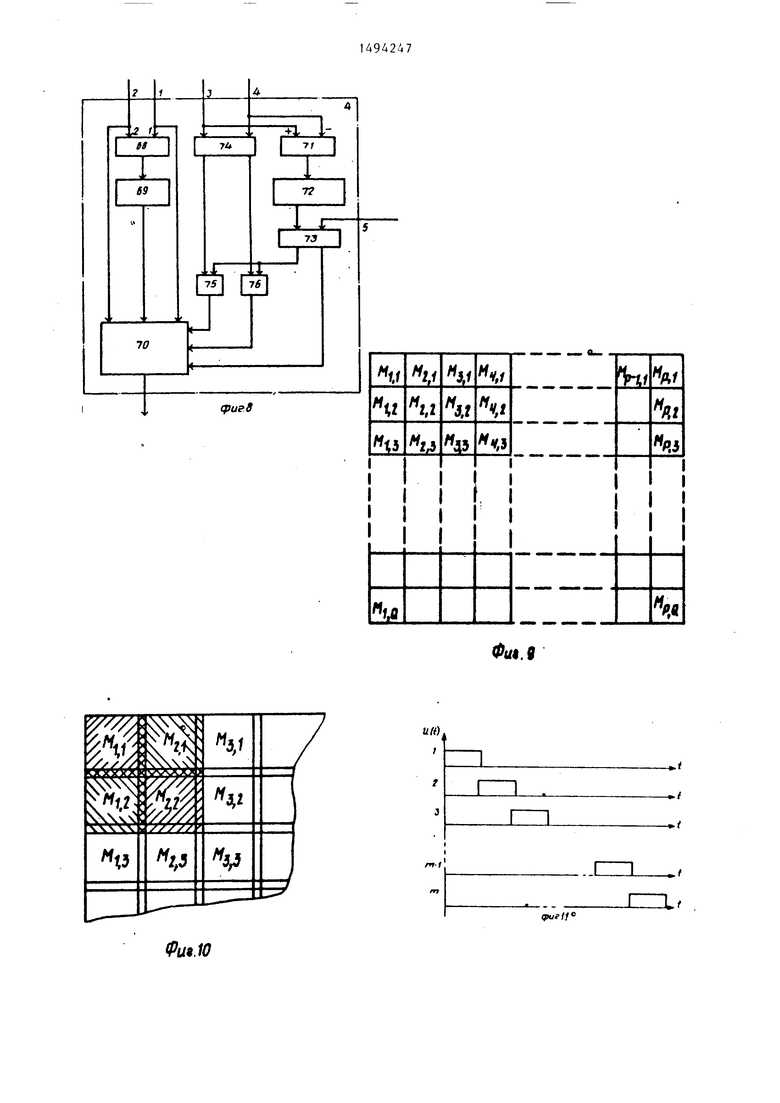

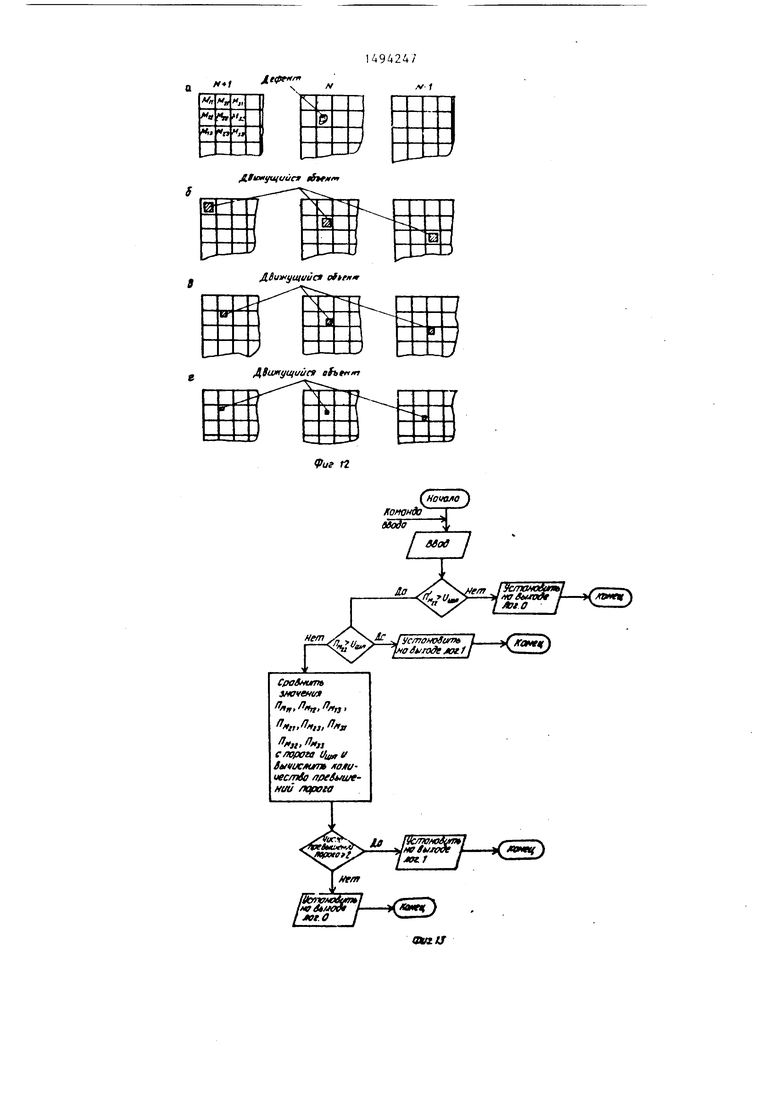

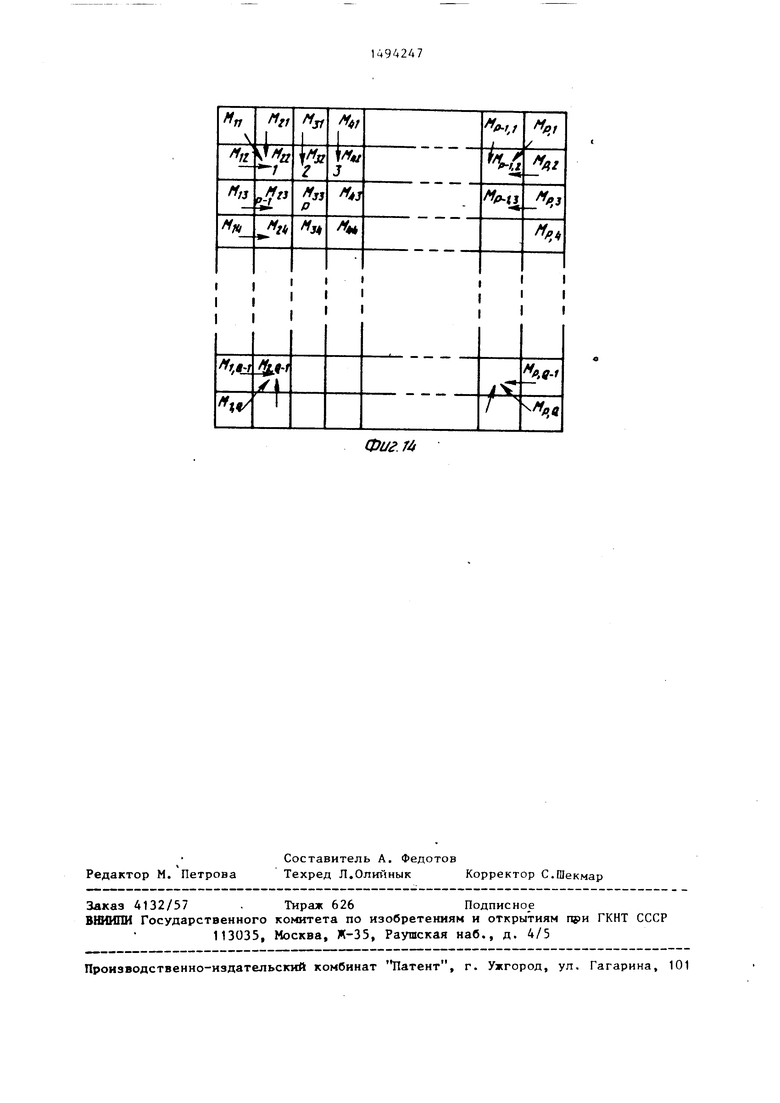

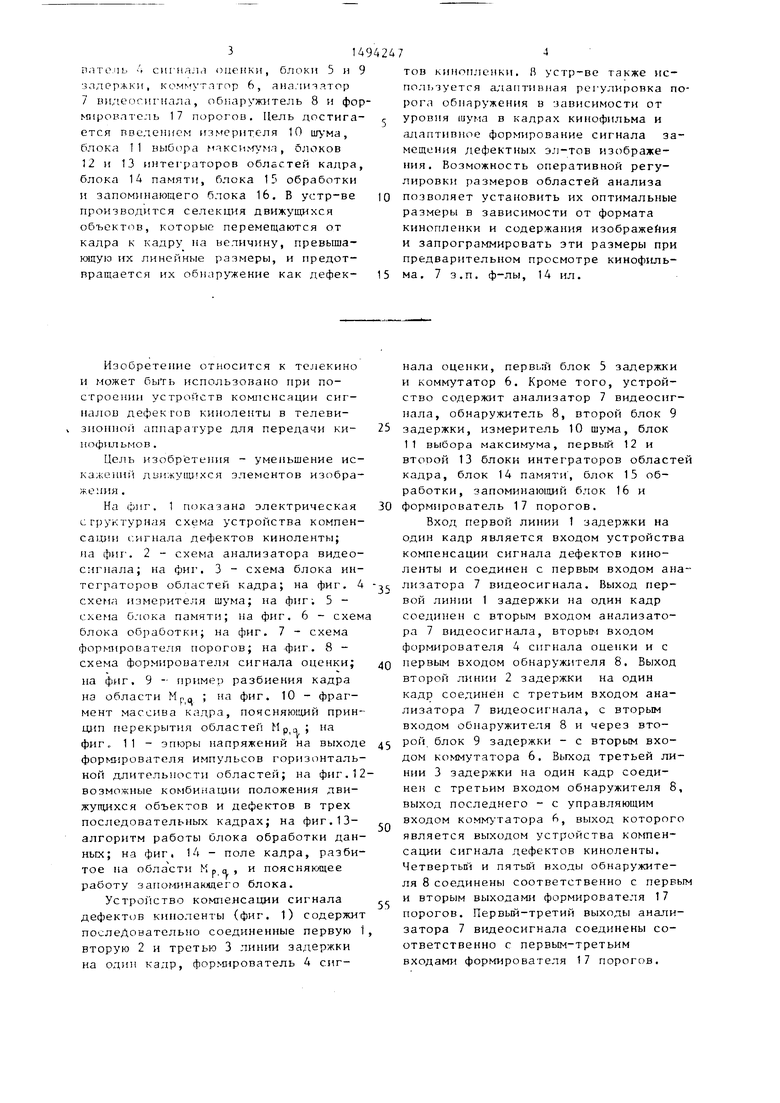

На фиг. 1 показана электрическая структурная схема устройства компен- сащп с:игнала дефектов киноленты; на фиг . 2 - схема анализатора видеосигнала; на фиг, 3 - схема блока интеграторов областей кадра; на фиг. 4 схема измерителя шума; на фиг; 5 - схема блока памяти; на фиг. 6 - схем блока обработки; на фиг. 7 - схема формирователя порогов; на фиг. 8 - схема формирователя сигнала оценки; на фиг. 9 - пример разбиения кадра на области Мр ; на фиг. 10 - фрагмент массива кадра, поясняющий принцип перекрытия областей j на фиг„ 11 - эпюры напряжений на выходе формирователя импульсов горизонтальной длительности областей; на фиг.12 возможные комбинации положения движущихся объектов и дефекгтов в трех последовательных кадрах; на фиг. 13- алгоритм работы блока обработки данных; на фиг. 14 - поле кадра, разбитое на обла сти Кра , и поясняющее работу запоминающего блока.

Устройство компенсации сигнала дефектив киноленты (фиг. 1) содержит послеДователыю соединенные первую 1 вторую 2 и третью 3 линии задержки на один кадр, фop D poвaтeль 4 сигнала оценки, первый блок 5 задержки и коммутатор 6. Кроме того, устройство содержит анализатор 7 видеосигнала, обнаружитель 8, второй блок 9 задержки, измеритель 10 шума, блок 11 выбора максим ма, первый 12 и второй 13 блоки интеграторов областе кадра, блок 14 памяти , блок 15 обработки, запоминающий блок 16 и формирователь 17 порогов.

Вход первой линии 1 задержки на один кадр является входом устройства компенсации сигнала дефектов киноленты и соединен с первым входом анализатора 7 видеосигнала. Выход первой линии 1 задержки на один кадр соединен с вторым входом анализатора 7 В1адеосигнала, вторьм входом форм {рователя 4 сигнала оценки и с первым входом обнаружителя 8, Выход второй линии 2 задержки на один кадр соединён с третьим входом анализатора 7 видеосигнала, с вторым входом обнаружителя В и через второй блок 9 задержки - с вторым входом коммутатора 6, Выход третьей линии 3 задержки на один кадр соединен с третьим входом обнаружителя В, выход последнего - с управляющим входом коммутатора 6, выход которого является выходом устройства коьтен- сации сигнала дефектов киноленты. Четвертьп и пятый входы обнаружителя 8 соединены соответственно с первы и вторым выходами формирователя 17 порогов. Первый-третий выходы анализатора 7 видеосигнала соединены соответственно с первым-третьим входами формирователя 17 порогов.

14

Кроме того, первыГ) и пторой выходы аналитатора 7 видеосигнала .соединены также с третьим и четвертым входами формирователя 4 сигнала оценки, четвсртьп выход - с первым входом блока 1I зибора максимума и через измеритель 10 шума - с пятым входом формирователя 4 сигнала оценки, с первым входом блока 15 обработки и с четвертым входом формирователя 17 порогов, Пятът выход анализатора 7 видеосигнала соединен с вторым входом блока 11 выбора максимума, выход которого через первый блок 12 интег- раторов областей кадра соединен с первым входом блока 14 памяти. Шестой выход анализатора 7 видеосигнала через второй блок 13 интеграторов областей кадра соединен с вторым входом блока 14 памяти. Первый и второй выходы блока 14 памяти соединены соответственно с вторым и третьим входами блока 15 обработки, выход которого через запоминающий блок 16 соединен с пятым входом формирователя 17 порогов.

Для формирования и распределения синхроимпульсов и команд управления устройство компенсации сигнала дефек- тов киноленты содержат также формирователь 18 импульсов синхронизации и блок 19 управления.

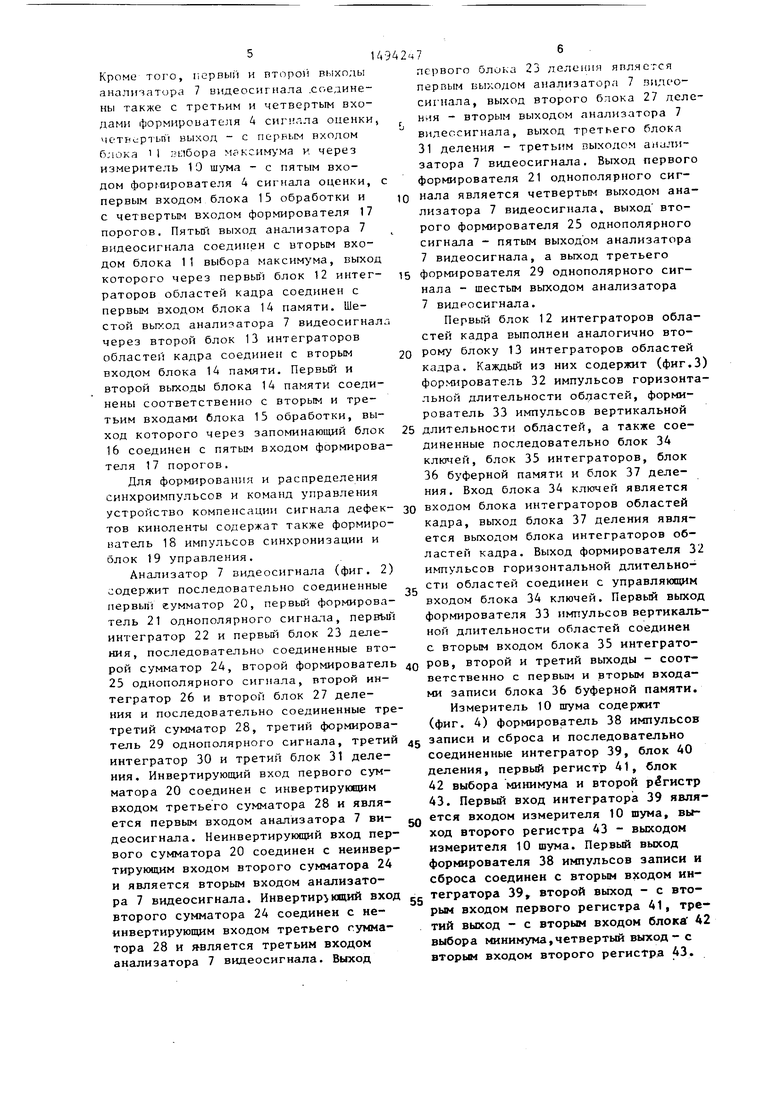

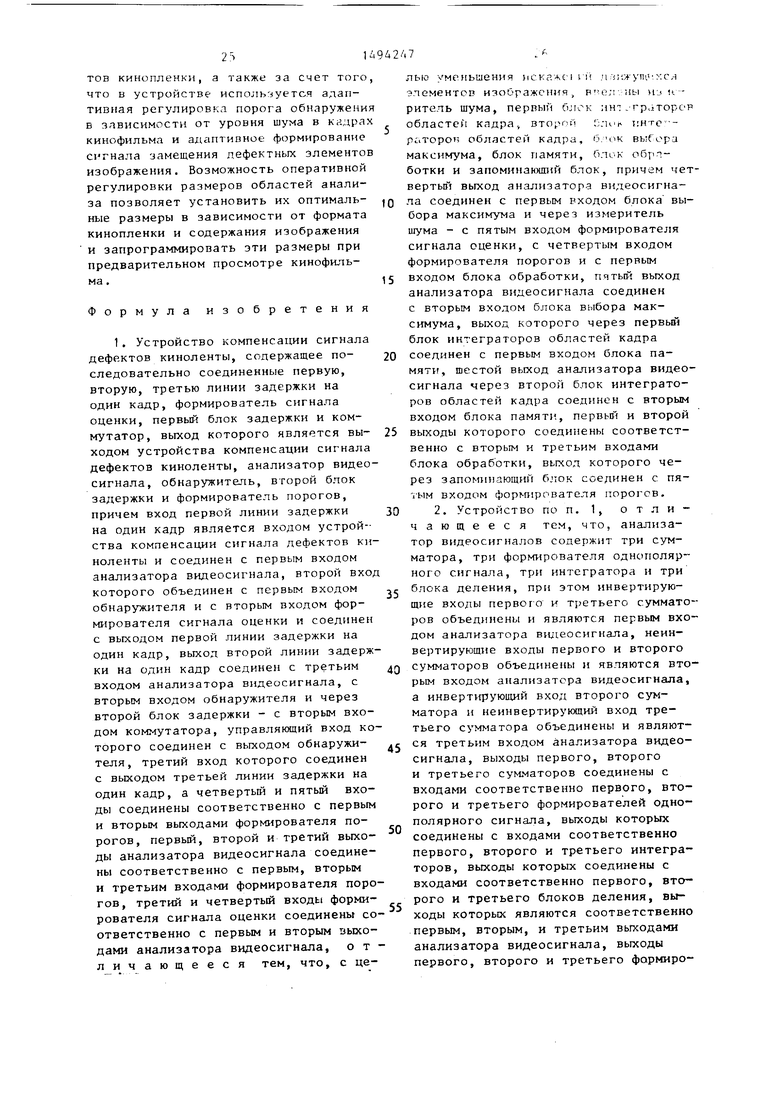

Анализатор 7 видеосигнала (фиг. 2) содержит последовательно соединенные первьп еумматор 20, первьй формирователь 21 однополярного сигнала, первьй интегратор 22 и первьй блок 23 деления, последовательно соединенные второй сумматор 24, второй формирователь 25 однополярного сигнала, второй интегратор 26 и второй блок 27 деления и последовательно соединенные тре третий сумматор 28, третий формирователь 29 однополярного сигнала, третий интегратор 30 и третий блок 31 деления. Инвертирующий вход первого сумматора 20 соединен с инвертирующим входом третьего сумматора 28 и является первым входом анализатора 7 ви- деосигнала. Неинвертирующий вход первого сумматора 20 соединен с неинвертирующим входом второго сумматора 24 и является вторым входом анализатора 7 видеосигнала. Инвертирующий вход второго сумматора 24 соединен с неинвертирующим входом третьего сумматора 28 и я вляется третьим входом анализатора 7 видеосигнала. Выход

Q 5 0 5

о

Q Q с

5

первого блока 23 деления является первым выходом анализатора 7 вилс О- сигнала, выход второго блока 27 деления - вторым выходом анализатора 7 видеосигнала, выход третьего блока 31 деления - третьим выходом анализатора 7 видеосигнала. Выход первого формирователя 21 однополярного сигнала является четвертым выходом анализатора 7 видеосигнала, выход второго формирователя 25 однополярного сигнала - пятым выходом анализатора 7 видеосигнала, а выход третьего формирователя 29 однополярного сигнала - шестым выходом анализатора 7 видеосигнала.

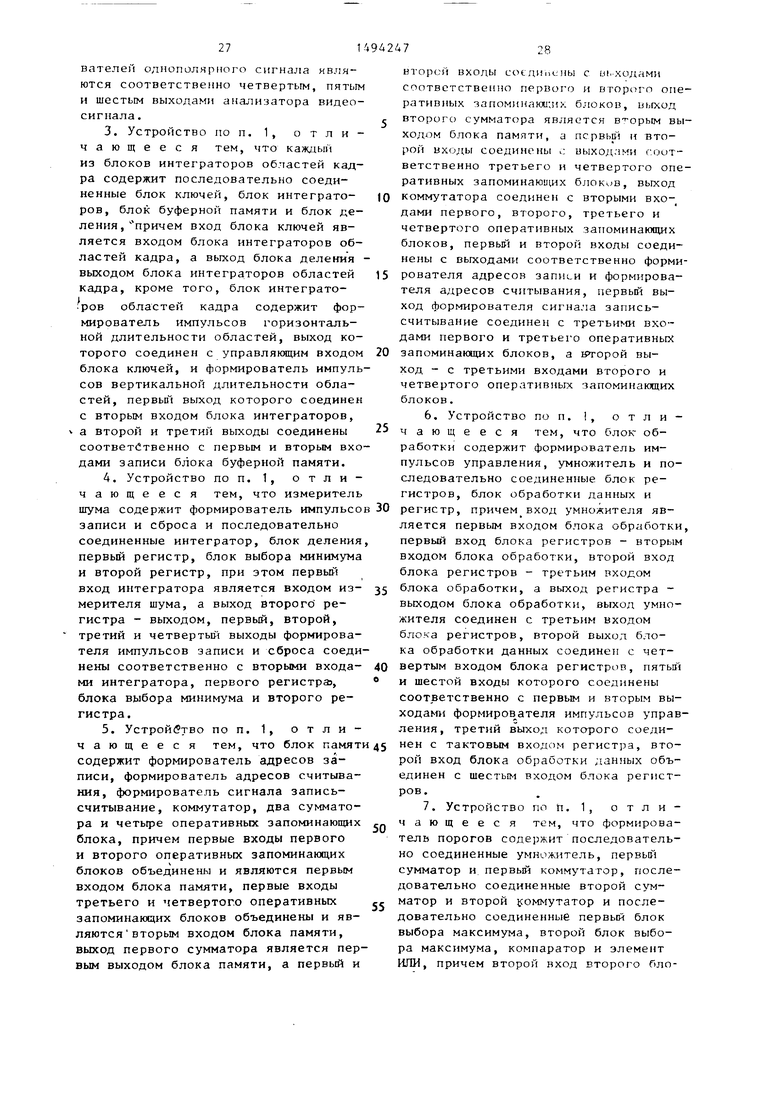

Первый блок 12 интеграторов областей кадра выполнен аналогично второму блоку 13 интеграторов областей кадра. Каждый из них содержит (фиг.З) формирователь 32 импульсов горизонтальной длительности областей, формирователь 33 импульсов вертикальной длительности областей, а также соединенные последовательно блок 34 ключей, блок 35 интеграторов, блок 36 буферной памяти и блок 37 деления. Вход блока 34 ключей является входом блока интеграторов областей кадра, выход блока 37 деления является выходом блока интеграторов областей кадра. Выход формирователя 32 импульсов горизонтальной длительности областей соединен с управляющим входом блока 34 ключей. Первый выход формирователя 33 импульсов вертикальной длительности областей соединен с вторым входом блока 35 интеграторов, второй и третий выходы - соответственно с первым и вторым входами записи блока 36 буферной памяти.

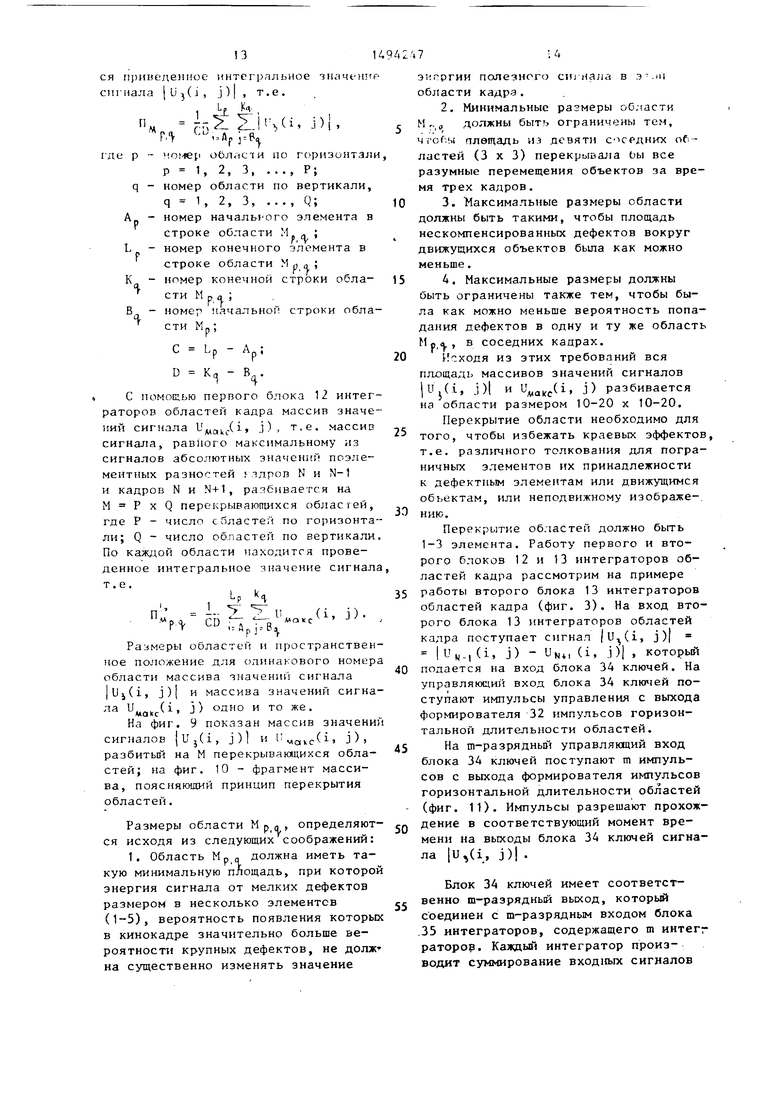

Измеритель 10 шума содержит (фиг. 4) формирователь 38 импульсов записи и сброса и последовательно соединенные интегратор 39, блок 40 деления, первый регистр 41, блок 42 выбора минимума и второй регистр 43. Первый вход интегратор а 39 является входом измерителя 10 шума, выход второго регистра 43 - выходом измерителя 10 шума. Первый выход формирователя 38 импульсов записи и сброса соединен с вторым входом интегратора 39, второй выход - с вторым входом первого регистра 41, третий выход - с вторьм входом блока 42 выбора минимума,четвертый выход- с вторым входом второго регистра 43.

Hjuii-, 14 ri iMHTi) соцержит (фиг. 5) (юрмиронлтель 44 адрес ов записи, формирователь 45 a,4pecoD считыпания, фс рмировптель 46 сиг-нала запг.сь- считывание, комм т;ат(ф 47, первьй - 4t ; нерт(. запоминлкл;1ис блпки 51, ritep вьп 52 и второй 53 сумматгры. Первый вход первого оперативного запоминающего блока 48 объединен с первым входом второго оперативного запоми- HaiouiCT блока 49 и является первым входом блока 14 памяти, первый вход третьег о оперативного запоминающего Олока 50 объединен с первым входом четвертого оперативного запоминающего блока 51 и является вторым входом блока 14 naNWTH. Выход первого cyMMaTojia 52 является первым выходом Олгжа 14 памяти, выход второго сум- матора 53 - BTOpi.ff-i выходом блока 14 памяти. Выход формирователя 44 адресов записи соединен с первьм входом KOMMyTaTojia 47. Выход формирователя 45 адресов считывания соединен с вторым входом коммутатора 47. Выход последнего соединен с вторыми входа- t-ni первог о--четвертого опе1: ативных за ио.- жнающих блоков 48-51. Трети вход первого оперативного запоминаюи;его fijTOKa -(8 объединен с третьим входом 1ро/ьего оперативного запоминающего блока 50 и соединен с первым выходом фop u poвaтeля 46 сигнала запись-считывание. Третий выход второго опера- тивного запоминающего блока 49 объединен с третьим выходом четвертого оперативного запоминающего блока 51 и сс едииен с вторым выходом формирователя 46 сигнала запись-считывание, Выход первого опе1 ативного запоминающего блока 48 соединен с первым входом первого сумматора 52, выход второго оперативного запоминающего блок 49 - с вторым входом первого суммато ра 52, выход третьего оперативного запоминающего блока 50 - с первым входом BTOpoi o сумматора 53, выход четвертого оперативного запоминающего блока 51 - с вторым входом вто- рого сумматора 53.

Блок 15 обработки содержит (фиг.6 ф.:фмирователь 54 импульсов управления, умножитель 55 и последовательно соединенные блок 56 регистров, блок 57 обработки данных и регистр 58. Вход умножителя 55 является первым входом блока 15 обработки, первый вход блока 56 регистров - вторым входом блока 15 (i6pa6t)TKH, второй вход б.ги.рса 56 регистров - третьим входом блока 15 обработки. Выход регистра 5 является выходом блока 15 обрабо ки. Выход умножителя 55 соединен с тре- гьим иходом блока 56 регистров, второй выход блока 57 обработки данных с четвертым входом б;1ока 56 регистро Перньи и второй выходы формирователя 54 имттульсов управления соединены соответственно с пятым и шестым входами блока 56 регистров. Второй вход блока 57 обработки данных объединен с шестым входом блока 56 регистров. Третий выход формирователя 54 импульсов управления соединен с тактовым входс м регистра 58.

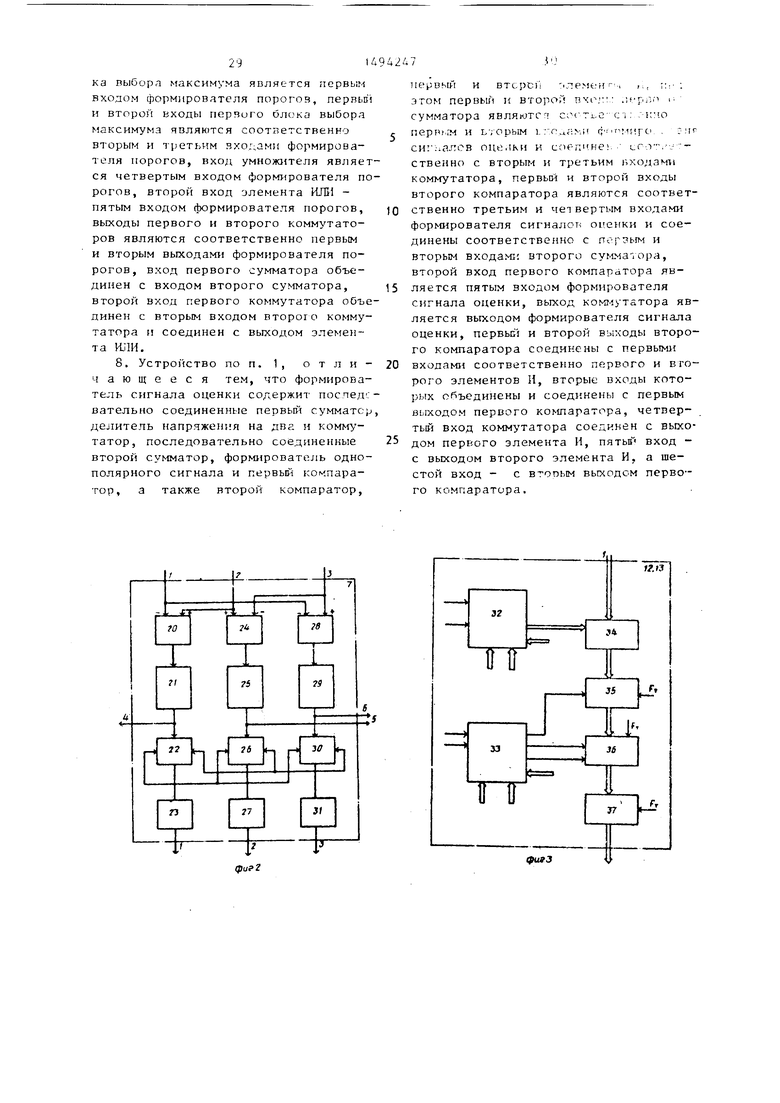

Формирователь 17 порогов содержит (фиг. 7) умножитель 59, первьв1 60 и второй 61 сумматоры, первый 62 и второй 63 коммутаторы, первый 64 и второй 65 блоки выбора максимума, копаратор 66 и элемент ИЛИ 67. Выход первого блока 64 выбора максимума соединен с первым входом второго блока 65 выбора максимума, второй вход которого является первым входом формирователя 17 порогов. Первый и второй входы первого блока 64 выбора максимума являются соответственно вторьм и третьим входами формирователя 17 порогов. Вход умножителя 59 является четвертым входом формирователя 17 порогов. Выход второго блока

65выбора максимума через компаратор

66соединен с первым входом элемента Iirni 67, второй вход которого является пятым входом формирователя 17 порогов. Выход умножителя 59 через пер вьщ сумматор 60 соединен с первым входом первого коммутатора 62, а через второй сумматор 61 - с первым входом второго коммутатора 63. Второй вход первого коммутатора 62 объединен с вторым входом второго коммутатора 63 и соединен с вьрсодом элемента ИЛИ 67. Выход первого коммутатора 62 является первым выходом формирователя 17 порогов, а выход второго коммутатора 63 - вторьЫ выходом формирователя 17 порогов.

Формирователь 4 сигнала оценки содержит (фиг. 8) последовательно соединенные первый сумматор 68, делител 69 напряжения на два и коммутатор 70 последовательно соединенные второй сумматор 71, формирователь 72 одно- полярного сигнала и nepabrfi компаратор 73, а также второй компаратор 7А, первый элемент И 75 и второй элемент И 76. Первьй вход первого сумматора 68 соединен с вторьм входом коммута- тора 70 и япляется первым входом формирователя сигнала оценки, второй вход первого сумматора 68 соединен с третьим входом коммутатора 70 и является вторым входом формирователя 10 4 сигнала оценки. Первый вход второго компаратора 74 соединен с пер- BbEvi входом второго сумматора 71 и является третьим входом формирователя 4 сигнала оценки, второй вход второ- 15 го компаратора 74 соединен с вторым входом второго сумматора 71 и является четвертым входом формирователя 4 сигнала оценки. Первый выход второго компаратора 74 соединен с пер- 20 вым входом первого элемента И 75, второй выход - с первым входом второго элемента И 76. Второй вход первого элемента И 75 объединен с вторым входом второго элемента И 76 5 и соединен с первым выходом первого компаратора 73. Выход первого элемента И 75 с четвертым входом комм татора 70, выход второго элемента И 76 - с пятым входом коммута- 30 тора 70, второй выход первого компаратора 73 - с шестым входом коммутатора 70. Выход последнего является выходом формирователя 4 сигнала оценки.35

УстроТ Ство компенсации сигнала дефектов киноленты работает следую- щим образом.

Формирователь 18 импульсов синхронизации формирует и распределяет 40 по блокам устройства импульсы тактовой частоты F, кадровые гасящие импульсы КГ, импульсы синхронизации полей П и импульсы синхронизации строк С.45

Блок 19 управления, являющийся в простейшем случае пультом управления, на котором с помощью органов управления задаются предварительные параметры (размеры по вертикали и ризонтали, перекрытия по вертикали и горизонтали), раздает команды управления по трем шинам: ША, ЩД и ШУ на блоки устройства.

Цифровой видеосигнал с выхода jj телекинопроектора поступает на вход последовательно соединенных трех линий 1, 2 и 3 задержки на один кадр (фиг. 1). В результате на входе устройства и на выходах пнимй 1 , 2 i; 3 задержки на един кадр олноврсмснмо присутствуют видеосиг напы эломентоп изображения одного пространстнеиного положения соответственно , N, N-1 и N- 2-ro кадров.

Сигналы N-t-1-го кадра - Uw,,(i, j) N-го кадра - U,j(i, j) и N-1-го кадра UH-I (i j) Д i номер элемента разложения в строке; j - номер строки, поступают на входы анализатора 7 видеосигнала, которьй проводит анализ сигналов с точки зрения степени их корреляцим между собой. Для этого в анализаторе 7 видеосигнала (фиг, 2 с помощью первого 20, второго 24 и третьего 28 сумматоров формируются три сигнала поэлементной разности входных сигналов. На выходе первого сумматора 20 формируется сигнал разности U,(i, j) U,(i, j) - -U,, (i, j), на выходе второго сумматора 24 - сигнал разности U(i, j) U|s(i. j) UN.,(i, j), на выходе третьего сумматора 28 - сигнал разности U,(i, j) j) - UN+I (o, j). Выходные сигналы сум- маторов U,(i,j) ,U(i,j) и ,:) имеют двухполярную структуру и содержат только составляющие от дефектов кинопленки и щумов, если нет движения в изображении. При наличии движения в сцене выходные сигналы сумматоров содержат составляющие, определяемые степенью движения в сцене. На выходах первого 21, второго 25 и третьего 29 формирователей однополярног сигнала формируются абсолютные значения входных сигналов, т.е. |u(i, iU(i, j)i и U(i, j). С выходов формирователей однополярного сигнала сигналы |u,(i, j)|, , j)| и ju(i, j)| поступают соответственно на входы первого 22, второго 26 и третьего 30 интеграторов, которые осуществляют поэлементное суммирование входных сигналов в течение активной части кадра. Затем во время кадрового гасящего интервала происходит запись полученных значений сигналов в регистры памяти, входящих в состав интеграторов, а после этого также во время кадрового гасящего интервала осуществляется сброс интеграторов в нулевое состояние. Таким образом, в конце активной части кадра на выходах интеграторов присутствуют сигналы:

на выходе первого интегратора 22 I J

и,(i, J)

и,. 2.

Е1,ходе второго интегратора 26 I I

и

1-г.

ZZLUj i

J

выходе третьего интегратора 30 Г Т

U(i, j)| ,

и

Ъ .-

, гг де 1 - число элементов разложения

изображения в строке; J - число стр.ок в кадре. С выходов интеграторов сигналы

и

(

Из.

поступают соответственно на первьй 23 и второй 27 и третий 31 блоки деления. В блоках деления производится деление входных сигналов на коэффициент, равный числу элементов разложения изображения Б кадре, т.е. на выходе первого блока 23 деления формируется с нал

1

.1

-1- V

I J г-- f-

1- J-1

u,(i, ;

выходе второго блока 27 формируя сигнал

Г J

и

1 эч

1 I-J

, j)| ;

- - ,., , , выходе третьего блока 31 формируется сигнал

- з эор р- I -J

1

и j( i, J)l

Напряжение яа выходе первого блока 23 деления, а соответственно и на первом выходе анализатора 7 видеосигнала пропорционально эффективному значению напряжения шумов U (i, j), так как при выборке некоррелированных мгновен}1ьгх значений шумов эффективное значение может быть оценено по множеству п выборочных З начений в соответствии с алгоритмом

- Уш

п :t7

(О

Так как входной телевизионньш сигнал ограничен в полосе частот 0,6-6,5 МГц, а частота дискретизации выбирается в два раза вьппе верхней граничной частоты видеосигнала,

0

5

0

5

0

5

0

5

0

5

то ныб трки шума можно считать некор- релирован ыми,

R анализаторе 7 видеосигнала измерение эффективного значения напряжения шумов осуществляется rio более простому л.чгоритму, однако это не снижает точности измерения, так как между значением эффективного напряжения шумов, полученного по формуле (1), и значением, полученным по алгоритму вычисления, в анализаторе 7 видеосигнала, существует почти пропорциональная зависимость. Аналогично на втором и третьем выходах анализатора 7 видеосигнала напряжение равно эффективному значению напряжения шумов UjCi, j) и U(i, j).

При наличии движения в сцене и наличии некоррелированных дефектов в соседних кадрах напряжения U;, , 2 99f и и э а) увеличиваются.

Четвертьп и пятьш выходы анализатора 7 видеосигнала соединены соответственно с первым и вторым входами блока 11 выбора максимума, ко- Topbtfi прО1гзводит выделение максимального из сигналов |U , (i, )|и U(i, j) для каждо/ о i, j-ro элемента. С выхода блока 11 выбора максимума сигнал ,(1, j) поступает на вход первого блока 12 интеграторов областей кадра. С шестого выхода анализатора 7 видеосигнала сигнал и-, , j)| поступает на вход второго блока 13 интеграторов областей кадра.

Второй блок 13 интеграторов областей кадра вычисляет интегральные значения сигнала jUi(i, j)| , т.е. сигнала, равного абсолютному значению сигнала поэлементной разности кадров N-1 и N+1, по перекрывающимся областям кадра. Первьв блок 12 интеграторов областей кадра вычисляет интегральные значения сигнала , j), т.е. сигнала, равного максимальному из сигналов абсолютных значений поэлементных разностей кадров N и N-1 и кадров N и N+1, по терскрывающимся областям кадра.

С помощью второго блока 13 интеграторов областей кадра весь массив значений сигнала |u(i, j)| , т.е. массив сигнала поэлементной межкадровой разности кадров N-i-1 и N-1, разбивается на М Р X Q перекрьгоающих- ся областей, где Р - число областей по горизонтали; Q - число областей по вертикали. По каждой области находится приведенное интегральное значение сигнала jU(i, j)|, т.е.

П

U Кч.

,

где р

.р J

4ot-iei области по горизонтали,

1, 2, 3,

Р;

q - номер области по вертикали, q 1, 2, 3, ..., Q; номер началы ого элемента в строке области М ;, ; номер конечного элемента в строке области М р о ; номер конечной строки области М

А„ L К В, номер начальной

сти Мр-, С LP - Ар; D К. - В.

строки обла 1

с первого блока 12 интеграторов областей кадра массив значений сигнала ,,.(1, j), т.е. массив сигнала, равного максимальному из сигналов абсолютных значений поэлементных разностей гялров N и N-1 и кадров N и N+1, разбивается на М Р X Q перекрываюпщхся областей, где Р - число сбластеЛ по горизонтали; Q - число областей по вертикали По каждой области находится проведенное интегральное значение сигнал т.е.

П.

LP k,

р, CD

l ,,,(i, j).

.Apj-B

Размеры ооластей и пространственное положение для одинакового номера области массива значений сигнала lUj(i, j)l и массива значений сигнала , j) одно и то же.

На фиг. 9 показан массив значений сигналов lu,(i, j)l и U.

ма J ) разбитьп на М перекрываюцихся областей; на фиг. 10 - фрагмент массива, поясняющий принцип перекрытия областей.

Размеры области Мрл, определяют- ся исходя из следующих соображений:

1, Область Mpq должна иметь такую минимальную площадь, при которой энергия сигнала от мелких дефектов размером в несколько элементов (1-5), вероятность появления которых в кинокадре значительно больше вероятности крупных дефектов, не долж на существенно изменять значение

энгргии полезного си)нала в э .ш области кадра.

2, Минимальные размеры области

,.

, о

должны быть ограничены тем.

0

5

0

5

0

5

0

5

п

е

4i-of bi алвщадь ид девяти с- седних областей (3 X 3) перекрывала бы все разумные перемещения объектов за время трех кадров.

Исходя из этих требований вся площадь массивов значений сигналов jUj(i, j)| и (.(i. j) разбивается на области размером 10-20 х 10-20.

Перекрытие области необходимо для того, чтобы избежать краевых эффектов, т.е. разл1гчного толкования для пограничных элементов их принадлежности к дефектным элементам или движущимся объектам, или неподвижному изображению.

Перекрытие областей должно быть 1-3 элемента. Работу первого и второго блоков 12 и 13 интеграторов областей кадра рассмотрим на примере работы второго блока 13 интеграторов областей кадра (фиг. 3). На вход второго блока 13 интеграторов областей кадра поступает сигнал |u(i, j)|

и

W-|(i J JM который

подается на вход блока 34 ключей. На управляющий вход блока 34 ключей поступают импульсы управления с выхода формирователя 32 импульсов горизонтальной длительности областей.

На т-разрядный управляющий вход блока 34 ключей поступают m импульсов с выхода формирователя импульсов горизонтальной длительности областей (фиг. 11). Импульсы разрешают прохождение в соответствующий момент времени на выходы блока 34 ключей сигна- ла |U,(i, j)| .

Блок 34 ключей имеет соответственно т-разрядный выход, который соединен с т-разрядным входом блока .35 интеграторов, содержащего m интегг раторов. Каждый интегратор производит суммирование входных сигналов

и пределах t)6. inCTH, определяемой в горизонтальном направлении, положением II длительностью импульсов, которые действуют на управляющих входах блока ЗА ключей и открывают в соответствуют) моменты времени ключи. В вертикальном направлении интегрируемая область определяется моментом появления импульса сброса на втором входе блока 35 интеграторов. Импульс сброса формируется в формирователе 33 импульсов вертикальной длительности областей.

С т-раэрядного выхода блока 34 интеграторов сигналы поступают на тп-разрядньй вход блока 36 буферной памяти. На первьш вход записи блока 36 буферной памяти поступает сигнал записи с второго выхода формирователя 33 импульсов вертикальной длительности областей, на второй вход - импульсы записи с третьего выход а формирователя 33 импульсов вертикальной длительности областей. При поступлении импульсов записи производится запись сигнала с выхода блока 35 интеграторов в первые и вторые регистры блока 36 буферной памяти. Импульс на втором выходе формирователя 33 импульсов пертикальной длительности областей определяет размер интегрируемой области по вертикали. При его появлении производится запись в первые регистры блока 36 буферной памяти, затем с задержкой на Один такт появляется импульс сброса на первом выходе формирователя 33 вертикальной длительности областей, это импульс обнуляет интеграторы в блоке

35интеграторов. С задержкой, равной числу строк перекрытия областей, появляется импульс на третьем выходе формирователя 33 импульсов вертикальной длительности областей, который записывает сигнал, накопленный

в интеграторах от момента сброса интеграторов в ноль до момента его появления, во вторые регистры блока

36буферной памяти.

На выходе блока 36 буферной памяти формируются интегральные значения сигнала |U(i, j)| по области Мр.

С выхода блока 36 буферной памяти сигнал поступает на блок 37 деления, в котором производится деление поступающего сигнала на коэффициент, численно равный числу элементов изображения в интегрируемой области кад- РаМр,.

t выходов первого и второго блоков 12 и 13 интеграторов областей кадра сигналы поступают на первый и второй входы блока 14 памяти, в котором производится запись полу- ченньгх интегральных значений сигна0

5

0

5

0

5

0

5

0

Wp.cyf Wp, причем формируется интегральное значение в области М р п в первом, а затем во втором поле. Для получения полного интегрального значения в области М р л значения, полученные в первом и втором полях суммируются.

Блок 14 памяти (фиг. 5) содержит четыре одинаковых оперативных запоминающих блока 48-51. На третьи входы этих блоков поступают сигналы с выходов формирователя 46 сигнала запись - считывание. По этим сигналам в активной части кадра в первом поле два оперативных запоминающих блока находятся в режиме записи, а два других - в режиме считывания. Во втором поле их функции меняются. Во время кадрового гасящего импульса все четьфе оперативных запоминающ блока находятся в режиме считьшания.

Емкость каждого оперативного запоминающего блока определяется по формуле

V М 8/2,

где М - число интегрируемых областей

в кадре;

8 - разрядность числа на выходе первого и второго блоков 12 и 13 интеграторов областей кадра;

2 - коэффициент, учитьшающий разложение на два поля. Если размер области М . , в горизонтальном направлении равен 20 элементам разложения, в вертикальном направлении - 16 строкам, то М 702/ /20 X 575/16 35 X 35 1225. Тогда V 1225-4 4900 бит.

С выходов первого 48 и второго 49 оперативных запоминающих блоков сигнал поступает соответственно на первый и второй входы первого сумматора 52, ас выходов третьего 50 и четвертого 51 оперативных запоминающих блоков сигналы поступают соответственно на первый и второй входы второго сумматора 53. С помощью сумматоров формируется полное интеграл.ь- ное значение сигнала в области Мла , в кадре. Запись сигналов в оперативные запоминающие блоки происходит во время активной части кадра. Для этого к вторым входам этих блоков через коммутатор 47 подключаются выходы формирователя 44 адресов записи. Во время кадрового гасящего импульса на выход коммутатора 47 подключается формирователь 45 адресов считывания, оперативные запоминающие блоки переходят в режим считывания информации. Считывание производится в следующей последовательности (фиг. 9): М .i ;

М

1Л

М

М

.г

м-2.2; М,,, ;

М

м.г;

M.i;

М.

Mi,, М

М,

М 5, ; затем

М 3, J.2 М ,3 4,1 4,г 4,5

И т.д., т.е. считывается девять точек, затем происходит возврат к второму столбцу и производится считывание снова девяти точек и т.д. Когда все интегральные значения первого ряда столбцов считаны, производится сдвиг на одну строку и считывание начинается сначала, т.е. М, ; M,j ;

М

М о ; Mj ,, ; М ,, 4-

1,4 2.-г С первого

и второго выходов блока 14 памяти сигналы поступают соответственно на второй и третий входы блока 15 обработки. С второго входа блока 15 обработки сигнал поступает на вход блока 56 регистров (фиг. 6). На тактовьо вход блока 56 регистров лоступакуг тактовые импульсы низкой частоты F.,p. После первых девяти тактов в блок 56 регистров записываются приведенные интегральные значения межкадровых разностей первых девяти

бластей, т.е. сигналы П,,

П

П

П

П/

п.

..7

Л««.г w,.,i i Mt.ii « г V

Пм,.гИ

По окончании девяти тактов формирователь 54 импульсов управления формирует импульс на своем втором выходе. Этот импульс поступает на шестой вход блока 56 регистров. На первом выходе формирователя 54 импульсов управления сигнал появится после пяти тактов, т.е. после того, как будет считано из блока 14 памяти интегральное значение для средней обла М7

I

сти, т.е. сигнал Пм-г.. (Пц,,). На первый вход блока 15 обработки поступает код напряжения действующего значения шума в кадре кинофильма. Этот сигнал умножается в умножителе 55 на коэффициент К 10-12, коэффици

-

10

15

20

25

30

с

40

д П в50

$5

ент К учитывает, что величина пикового значения шума больше его эффективного значения в 5-6 раз, а также учитывает влияние мелких дефектов. С выхода умножителя 55 код пикового значения напряжения шума поступает на третий вход блока 56 регистров. С второго выхода формирователя 54 импульсов управления импульс поступает также на второй вход блока 57 обработки данных.

При поступлении импульса на второй вход блока 57 обработки данных начинается считывание информации из блока 56 регистров.

Блок обработки данных производит обработку информации по алгоритму, позволяющему с высокой вероятностью отселектировать движущиеся объекты, которые перемешаются от кадра к кадру на величину, большую их линейных размеров. На фиг. 12 приведены возможные комбинации положения движущихся объектов и дефектов в изображении трех последовательных кадров. Изображение на фиг. 12 разбито на области М р« и взяты первые девять областей, т.е. М,, -Мт,..

При синтезе алгоритма учитывается то, что вероятность попадания средних и крупных дефектов размером более 5x5 элементов в одну и ту же область, размером 3 х 3 области Мра|, ничтожно мала. Кроме того, линейные перемещения объектов за время трех кадров не превышают 3 х а, где а - размеры наименьшей из сторон области Мрс. На фиг. 13 приведен алгоритм работы блока 57 обработки данных. Как следует из алгоритма, после ввода данных производится сравнение ве- с порогом, который зави- от величины шума. Если величина

превышает порог, это говорит о том, что в кадре N в области Mj содержится или дефект (фиг. 12а), или движущийся объект (фиг. 126, в г),

превьоаает по-

личины П,, ,,

сит

t

Если величина П((

рог, то значит в области М. кадра

среднего или крупного дефекта нет, а может быть мелкий одиночный дефект. На выходе блока 57 обработки данных в этом случае устанавливается сигнал лог. О.

В случае превышения порога, производится следующий этап алгоритма сравнения сигнала .j с порогом и ijn . Превьппение порога говорит о

li M, что в ка;фах N + 1 ; N и N-1 имеется движущнГюя объект, который имеет 1 еболыяук) скорость перемещения и которьп попадает в кадрах N+1 ; N, N-1 в одну и ту же обдлсть М,, ( ;)иг.12 Г ) iciH только в двух кадрах попадает в одну и ту же область М 2 -2 В этом случае на выходе блока 57 обработки данных устанавливается сиг над лог. 1. Если же сигнал П не превышает порог, то это соответ-- ствует двум возможным ситуациям (фиг. 12, а, б): или в кадре N дефект (фиг. 12 а) или в кадре N объ- ект (фиг. 12, б),. чтобы это установить производится сравнение сигнадов

,,; ,, П„,,; д ; Пд,2 ,; П,

П

.j

П.

ч,г

с порогом Uj nЕс|ЛН число превышений порога больше 1цвух, то делается вывод о том, что в кадре N имеется движущийся объект и на выходе устанавливается сигнал лог. 1. Если было только одно пре

вышение порога или ни одного, то на выходе устанавливается сигнал лог. О. Так как области Мр.су имеют ма- дые размеры (10 - 20 х 10 - 20), то MCj iKHe движущиеся объекты будут также с высокой вероятностью селектиро- ваться как и крупные.

С выхода блока 57 обработки данных сигнал поступает на вход регистра 58, на TaKTOBbDl вход которого поступают импульсы с выхода формирова- теля 54 импульсов управления. Сигнал ЛО.Г. О или 1 поступает с выхода устройства 15 обработки на запоминающий блок 16.

Емкость запоминающего блока 16 оп ределяется числом областей М р „ , т.е. если М 1225, то емкость равна 1225 бит.

Фс.рмирование адресов считывания в запоминающем блоке 16 производится таким образом, чтобы для каждого элемента KcVipa бы1 считан соответствующий сигнал лог. 1 или О.

На фиг. 14 изображено поле кадра, разбитое на области Мра . Сигнал селекции движущихся объектов, которы записывается- в запоминающий блок 16, формируется начиная с области М , т.е. следующий сигнал селекции формируется для области ,, далее для области М и т.д. В запоминающем блоке 16 сигнал селекции для области М,, запишется в ячейку с адресом 1, сигнал селекции для области

г 5

0

5

0

5

О

5

- j

М- - н ячейку с адресом 2. В про- uet:ce считывания из запоминающего блока 16 сигнал селекции для областей ,(; .z aj берется таким же, как для области М, сигнал селекции для области М ,, , берется таким же, как для области М , т.д. Таким образом, при считывании для всех элементов кадра, которые попадают в области М,,, ; М,,, ; М,,, Iv.i, код адреса считывания должен быть равным 1. Для элементов, попадающих в области М, и Мз. 2. адреса равен 2 и т.д. На фиг. 14 цифрами 1, 2 и 3 показаны номера ячеек запоминающего блока 16, в которые записан сигнал селекции для данной области. Стрелками показано то, что для данной области сигнал селекции берется из другой области.

Сигнал с выхода запоминающего блока 16 поступает на пятьв) вход формирователя 17 порогов. Пятый вход формирователя 17 порогов (фиг. 7) является соответственно первым входом элемента 1ШИ 67 , на второй вход элемента ИЛИ 67 поступает сигнал с выхода компаратора 66, на второй вход которого поступает код порога. Код порога определяется исходя из интегрального значения сигнала межкадровой разности, когда имеют место значительные изменения сюжетов от кадра к кадру. На первый вход компаратора 66 поступает сигнал, равный максимальному из трех интегральных значений сигналов межкадровых разностей кадров N; N+1; N-1. Если имеет место изменение сюжета от кадра к кад- ру, то сигнал на первом входе превышает порог и на выходе компаратора 66 появляется сигнал лог. 1, который через элемент ИЛИ 67 поступает на вторые входы первого 62 и второго 63 коммутаторов и подключает на выход коммутаторов код порога, подаваемьй на третьи входы коммутаторов. Этот код запрещает обнаружение дефектов в кадре N. Если в трех последовательных кадрах N; ; N-1 нет изменения скзжета, то на выходе компаратора 66 сигнал лог. О.В этом случае управление коммутаторами осуществляется сигналом, поступающим с выхода запоминающего блока 16. Если для данной области Мрл , в которой производится обнаружение сигнала дефектов, на вькоде запоминающего блока

16 сигнал лог. 1, то л этой област обнаружение дефектов запрещается. Пр наличии на вторых входах первого 62 и второго 63 коммутаторов сигнала лог. О на выход коммутаторов подключаются сигналы с выходов первого 60 и второго 61 сумматоров, на первые входы которых поступа ет сигнал с выхода умножителя 59. На вход по- следнего поступает код действующего значения шума в кадре кинофильма с выхода измерителя 10 шума. Код действующего значения шума умножается на коэффициент К 3-4. Коэффициент К учитывает квазипиковое значение напряжения шумов, которое больше в 6-7 раз его эффективного значения, и коэффициент 0,5, связанньй с алгоритмом работы обнаружителя. На вторые Бходы первого 60 и второго 6 сумматоров поступают коды напряжения ручных регулировок порога. С помощью ручных регулировок возможно увеличение одного из пороговых напряжений на выходе формирователя 17 порогов в зависимости от преобладания темных или светлых дефектов. С первого и второго выходов формирователя 17 порогов коды пороговых напряжений по ступают соответственно на четвертый и пятый входы обнаружителя 8, на первый, второй и третий входы которого поступают задержанные на время длительности одного кадра сигналы соответственно N-t-1; N и N-1-го кадров .

Обнаружитель 8 производит обнаружение сигналов дефектных элементов йаображения N-ro кадра и вырабаты- вает импульсы коммутации. Импульс коммутации с выхода обнаружителя 8 поступает на третий вход коммутатора 6. Если импульс коммутации отсутствует, то на выход коммутатора 6 проходит сигнал N-ro кадра с выхода второго блока 9 задержки. При наличи импульса коммутации на выход коммутатора 6 проходит сигнал с выхода первого блока 5 задержки, вход кото- рого соединен с выходом формирователя 4 сигнала оценки.

Формирователь 4 сигнала оценки (фиг. 8) осуществляет формирование полусуммы сигналов N-t-1 и N-1-го кад- ров с помощью первого сумматора 68 и делителя 69 напряжения на два. С выхода последнего сигнал полусуммы поступает на первый вход коммутатора

70, второй и ) ;. котор г соединены соответственно с перны и вторым входами формирователя 4 си1 нала оценки, соответстБечно на первый вход коммутатора 70 i:,-cTynat-r сиг нал N-t-1-го кадра, а на третип вход - сигнал N-1-го кадра. Коммутатор 70 пропускает на свой выход один из трех этих сигналов. Управление коммутатором 70 осуществляется по сигналам управления, поступающим на четвертый, пятый и щестой входы коммутатора 70 соответственно с выходов первого элемента И 75, второго элемента И 76 и с второго выхода первого компаратора 73, на второй вход последнего поступает код действующег значения напряжения с выхода измерителя 10 шума.

На первый вход первого ко -1мутато- ра 73 поступает сигнал с выхода фор- М1фователя 72 однополярного сигнала, на вход которого поступает сигнал с выхода второго сумматора 71, на первый вход последнего поступает сигнал, равньБ интегралыюьгу значению сигнала межкадровой разности кадров N и с первого выхода анализатора 7 видеосигнала . На второй вход второго сумматора 71 поступает код интегрального значе1;ия сигнала межкадровой разности кадров N и N-1. Если кэдры N; N-t-1 и N-1 имеют высокую степень корреляции, то разность сигналов, поступающих на первьй и второй входы второго сумматора 71, близка к нулю и не превышает уровень пгумов.

В этом случае на втором выходе первого компаратора 73 будет сигнал лог. 1, который поступит на шестой вход коммутатора 70. Этот сигнал подключит на выход коммутатора 70 сигнал с выхода делителя 69 напряжения на д-ва. Если сигналы U, и , которые поступают на первый и второй входы второго сумматора 71, отличаются на величину, большую действующего значения шума, то сигнал лог. 1 появляется на первом выходе первого компаратора 73. Если при это i9ср в и2 эФФ степень корреляци N-1-го кадра с N больше, N-t-1-го с N-M, то на первом выходе второго компаратора 7Д появляется сигнал лог. 1, и, следовательно, потенциал лог. 1 появляется на выходе пер- вого элемента И 75, который поступает на четвертый вход коммутатора 70. В этом случае на выход коммутатора 70 пройдет сигнал N-1-го кадра. Если наоборот, то пройдет сигнал N+1-го кадра. Этим обеспечивается высокая точность формирования сигнала оценки.

Измеритель 10 шума служит для оценки эффективного значения шумов в кадрах кинофильма. Для этого цифровой сигнал ID, (i,. j)|, т.е. абсолютное значение сигнала межкадровой разности, с четвертого выхода анализатопо множеству R выборочных значений в соответствии с алгоритмом

и

opip

.11 .

(3)

Так как выходной телевизионньм сигнал ограничен в полосе частот 0-6,5 МГц, а частота дискретизации (Q выбирается в два раза выше верхней, граничной частоты видеосигнала, то выборки шума можно считать некоррелированными. Число п достаточно велико, оно равно для частоты дисра 7 видеосигнала поступает на вход 5 кретизации 13,5 МГц - 702 элемента.

измерителя 10 шума и, соответственно. Между значениями, полученными по форма вход интегратора 39, входящего в состав измерителя 10 шума (фиг. 4). Интегратор 39 осуществляет поэлементное суммирование входных сигналов в 20 течение активной части строки. Во время строчного гасящего импульса интегратор 39 обнуляется импульсом с выхода формирователя 38 импульсов записи и сброса.

С вывода интегратора 39 сигнал

W; Z-|u,(i. J)l. j i i

где n - число элементов разложения в активной части строки;

мулам (2) и (3), существует почти пропорциональная зависимость.

Если в строке j имеется движение, то сигнал и,,; на вьгходв блока 40

деления содержит еще сигнал движения, т.е. и,,- в этом случае больше, чем при отсутствии движения. С выхода блока 40 деления сигнал 25 и, поступает на вход первого регистра 41, в который сигнал U,T, j записывается по окончании активной части строки (перед сбросом интегратора 39) и хранится в нем в течение следующей строки. С выхода первого регистра 41 сигнал поступает на блок 42 выбора минимума, который осуществляет выбор минимального сигнала из двух: приходящего и записанного в

30

деления содержит еще сигнал движения, т.е. и,,- в этом случае больше, чем при отсутствии движения. С выхода блока 40 деления сигнал 25 и, поступает на вход первого регистра 41, в который сигнал U,T, j записывается по окончании активной части строки (перед сбросом интегра тора 39) и хранится в нем в течение следующей строки. С выхода первого регистра 41 сигнал поступает на бло 42 выбора минимума, который осущест вляет выбор минимального сигнала из двух: приходящего и записанного в

J - номер строки,

поступает на блок 40 деления, где производится деление входных сигналов на коэффициент, равный п-(2, т.е.

,„ . эс предыдущей строке. Таким образом, к на выходе блока 40 деления формирует- 35

ся сигнал

1

и

эщ

п|

|u,(i, j) .(2)

концу активной части кадра на выход блока 42 выбора минимума сформируе ся сигнал, равный меньшему из сигна лов ) :. Этот сигнал в конце кадр записываетоя во второй регистр 43. С выхода последнего и, соответствен но, .с выхода измерителя 10 шума сиг нал, пропорциональный измеренному значению шума в кадрах кинофильма, поступает на устройство 15 обработки, формирователь 17 порогов и формирователь 4 сигнала оценки.

40

Если две строки соседних кадров полностью коррелированы между собой по«сигналу изображения, т.е. эти строки не пересекают движущиеся объекты, то U,jpq,: пропорционален эффективному значению напряжения шу- .с мов в строке j кадра N или кадра N+1 в том случае, если дисперсии шумов в этих строках кадра равны (что обычно имеет место). Коэффициент 42 учитьшает тот факт, что эффективное значение напряжения шумов при их ал- гебр аическом сложении увеличивается в -Л.

Пропорциональность сигнала U,j эффективному напряжению шумов в стро- производится селекция движутцихся

50

концу активной части кадра на вы блока 42 выбора минимума сформи ся сигнал, равный меньшему из си лов ) :. Этот сигнал в конце к записываетоя во второй регистр 4 С выхода последнего и, соответст но, .с выхода измерителя 10 шума нал, пропорциональный измеренном значению шума в кадрах кинофильм поступает на устройство 15 обраб ки, формирователь 17 порогов и ф мирователь 4 сигнала оценки.

Таким образом,,малые искажени движущихся объектов, высокая вер ность правильного обнар ткения де тов кинопленки и высокая точност формирования сигнала замещения д фектных элементов изображения до гаются за счет того, что в устро

ке J связано с тем фактом, что при выборк е некоррелированных мгновенных значений шумов, эффективное значение напряжения шумом может быть оценено

объектов, которые перемещаются о кадра к кадру на величину, превьш ющую их линейные размеры, п пред вращается их обнаружение как деф

по множеству R выборочных значений в соответствии с алгоритмом

и

opip

.11 .

(3)

0

мулам (2) и (3), существует почти пропорциональная зависимость.

Если в строке j имеется движение, то сигнал и,,; на вьгходв блока 40

деления содержит еще сигнал движения, т.е. и,,- в этом случае больше, чем при отсутствии движения. С выхода блока 40 деления сигнал 5 и, поступает на вход первого регистра 41, в который сигнал U,T, j записывается по окончании активной части строки (перед сбросом интегратора 39) и хранится в нем в течение следующей строки. С выхода первого регистра 41 сигнал поступает на блок 42 выбора минимума, который осуществляет выбор минимального сигнала из двух: приходящего и записанного в

0

предыдущей строке. Таким образом, к

производится селекция движутцихся

концу активной части кадра на выходе блока 42 выбора минимума сформируется сигнал, равный меньшему из сигналов ) :. Этот сигнал в конце кадра записываетоя во второй регистр 43. С выхода последнего и, соответственно, .с выхода измерителя 10 шума сигнал, пропорциональный измеренному значению шума в кадрах кинофильма, поступает на устройство 15 обработки, формирователь 17 порогов и формирователь 4 сигнала оценки.

Таким образом,,малые искажения движущихся объектов, высокая вероятность правильного обнар ткения дефектов кинопленки и высокая точность формирования сигнала замещения дефектных элементов изображения достигаются за счет того, что в устройстве

объектов, которые перемещаются от кадра к кадру на величину, превьш1а- ющую их линейные размеры, п предотвращается их обнаружение как дефектов кинопленки, а также за счет того что в устройстве используется адаптивная регулировка порога обнаружени Б зависимости от уровня шума в кадра кинофильма и адаптивное формирование сигнала замещения дефектных элементо изображения. Возможность оперативной регулировки размеров областей анализа позволяет установить их оптималь- ные размеры в зависимости от формата кинопленки и содержания изображения и запрограммировать эти размеры при предварительном просмотре кинофильма.

Формула изобретения

из блоков интеграторов областей кадра содержит последовательно соединенные блок ключей, блок интеграто- ров, блок буферной памяти и блок деления, причем вход блока ключей является входом блока интеграторов областей кадра, а выход блока делегшя выходом блока интеграторов областей кадра, кроме того, блок интеграто.ров областей кадра содержит формирователь импульсов горизонтальной длительности областей, выход которого соединен с управляющим входом блока ключей, и формирователь импульсов вертикальной длительности областей, nepBbDi выход которого соединен с вторым входом блока интеграторов, а второй и третий выходы соединены соответственно с первым и вторым входами записи блока буферной памяти.

и второй регистр, при этом первый вход интегратора является входом из- мерителя шума, а выход второго регистра - выходом, первый, второй, третий и четвертый выходы формирователя импульсов записи и сброса соединены соответственно с вторыми входа- ми интегратора, первого регистраэ, блока выбора минимума и второго регистра.

и второго оперативных запоминаюощх блоков объединены и являются первым входом блока памяти, первые входы третьего и четвертого оперативных запоминающих блоков объединены и являются вторым входом блока памяти, выход первого сумматора является первым выходом блока памяти, а первый и

второй входы соедип(.:иы с (Л.ходами соответственно первого и второго оперативных запоминакж лх блоков, выход второго сумматора является в -орым выходом блока памяти, а псрвьй и второй входы соединены : иыходлми г -оот- ветственно третьего и четвертого оперативных запоминающих , выход коммутатора соединен с вторыми входами первого, второго, третьего и четвертого оперативных запоминаюпщх блоков, первый и второй входы соединены с выходами соответственно формирователя адресов записи и формирователя адресов считывания, первьв1 выход формирователя сигна.ча запись- считывание соединен с третьими входами первого и третьего оперативных запоминающих блоков, а 15торой выход - с третьими входами второго и четвертого оперативных запоминающих блоков.

ка выбсфа максимума является первым входом формирователя порогов, первьп и второй входы первого блока выбора максимума являются соответственно вторым и третьим вхо:;ами формирователя порогов, вход умножителя является четвертым входом формирователя порогов, второй вход элемента ИЛИ - пятым входом формирователя порогов, выходы первого и второго коммутаторов являются соответственно первым и вторым выходами формирователя порогов, вход первого сумматора объединен с входом второго cyNrMaTOpa, второй вход первого коммутатора объединен с вторым входом второго коммутатора и соединен с выходом элемента ИЛИ.

/

{

первый и BTcpCi i f.iPMt Hr -, ,., ;: i этом псрвьш и BTOiw; пхо. .ivpr;ii сумматора являютс состьс ci: :i;:io

ПерВьМ и Ь ;ОрЫМ 1, ; Г, . . 1

сипчалев О1имки и соеп не. сгл-.-г :- ствеино с вторым и третьим входами коммутатора, первый и второй входы второго компаратора являются соответственно третьим и четвертым входами форт1рователя сигналот опенки и соединены соответственно с перзым и вторым входам : второго cyr-iMa. ора, второй вход первого компаратора является пятым входом формирователя сигнала оценки, выход ком1-5утатора является выходом формирователя сигнала оценки, первьы и второй выходы второго компаратора соединены с первыми входами соответственно первого и второго элементов И, вторые входы которых объединены и соединены с первым вь1ходом первого компаратора, четвертый вход коммутатора соединен с выходом первого элемента И, пятьи вход - с выходом второго элемента И. а шестой вход - с втопым выходом первого компаратора.

If.13

Fr

фиаз

39

4/

U2

44i

47

ТПГ

1494247

fO

«-Fm

J8

(риеЛ

«Л

«

5

5/

ц 52

53

,-/

фи&

.7

62

63

(pueS

6k

1н-Ц

t

65

67

66

фыР.7

Af

ЗЛ

ffff , , ,,

vSNvi X ШШ

id

M.

V

PU9.10

Фм.9

U(f) I

т-1

(

Сравмлт змгчения

„...ffft,,, fffij,

, строга UunrV tb/vixMrr лам- uec/nto apeSMue- ний /vpota

jV-1

лгЛлпя /н .

ЛаО I

Фиг.г

| Авторское свидетельство СССР № 1283999, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1989-07-15—Публикация

1987-04-06—Подача