К)

Изобретение относится к измерительной технике, может быть использовано для измерения параметров импульсов в автомат;ике, вычислитель- -ной и контрольно-измерительной технике и является усовершенствованием устройства по авт.св. № 1422189.

Целью изобретения является расширение функциональных возможностей измерителя за счет одновременного автоматического измерения длительностей фронтов импульсов и их оснований и вершин.

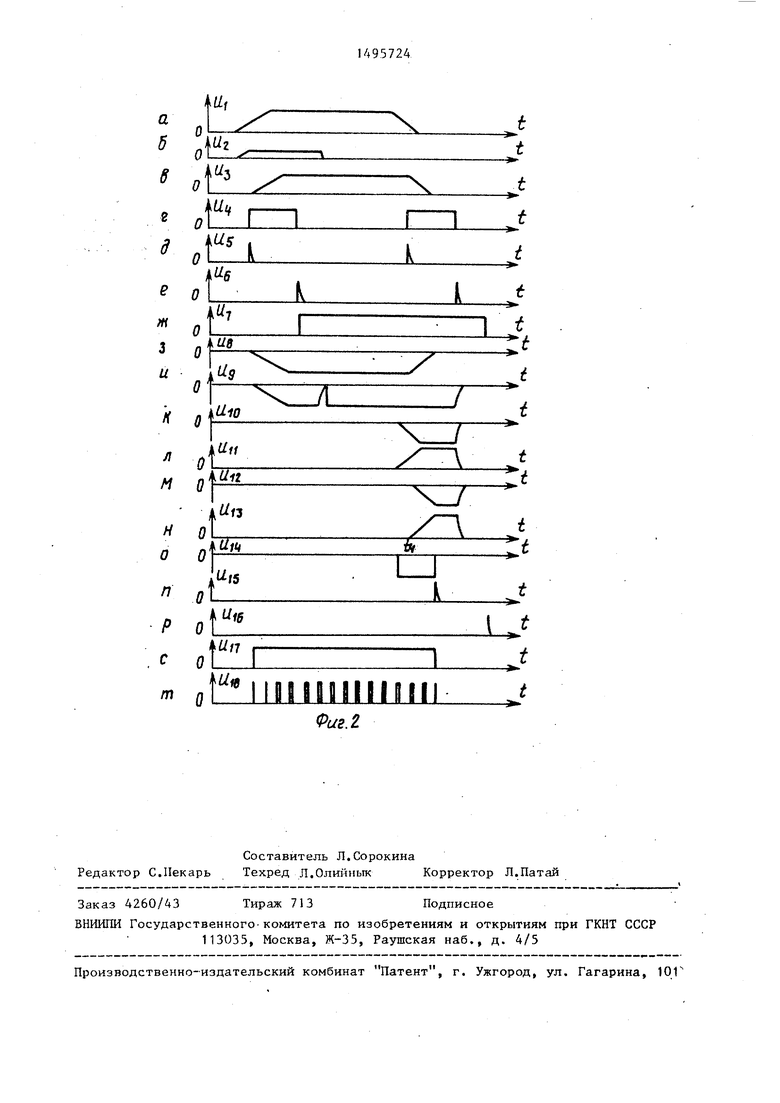

На фиг.1 представлена структур- ная схема измерителя; на фиг.2 - эпюры напряжений, поясняющие его. работу

Измеритель длительности фронтов импульсов содержит нормализатор 1 импульсов, с первого по четвертый элементы 2-5 задержки, первый 6,второй 7 и третий 8 инверторы, первый 9 и второй 10 пиковые детекторы со сбросом, первый 11 и второй 12 сумма торы, с первого по четвертый элек- тррнные ключи 13 - 16, выполненные, например, в виде высокочастотных реле, первый 17, второй 18 и третий 19 элементы ИЛИ, первый 20, второй 21 и третий 22 преобразователи напряжение частота, первый 23, второй 24 и третий 25 счетчики, выполненные, например, на микросхемах типа 133ИЕ5, первый 26, второй 27 и третий 28 RS- триггеры, первый 29 и второй 30 блоки дифференцирования, компаратор 31, выполненный, например, в виде триггера иЫйтта, регистратор 32, выполненный, например, в виде цифропеча- тающего устройства типа МПУ 6-3, первьй 33 и второй 37 цифровые умножители и цифровой делитель 35, выполненные, например, на микросхеме типа 145Ш116,.блок 36 памяти, выпол- ненный, например, на микросхеме типа К155РЕ23, и видеоусилитель 37..При этом последовательно соединены нормализатор .1 импульсов, выход которого также подключен к входу первого элемента 2 задержки и первому входу компаратора 31, первый сумматор 11, первый инвертор 6, первый электронный ключ 13, первый элемент ИЛИ 17, второй вход которого соединен с вько дом нормализатора 1 импульсов, второй з/тектронный ключ 14, первьй пиковый детектор 9, первый преобразователь 20 напряжение - частота, первый

o

5

0

5 О , 0 с

0

5

счетчик 23, цифровой делитель 35, первый цифровой умножитель 33, второй информационный вход которого соединен с выходом блока 36 памяти, и регистратор 32, последовательно соединенные второй инвертор 7, вход ко- торого подключен к выходу первого элемента 2 задержки и второму входу компаратора 31, второй пиковый детектор 10, выход которого также соединен с вторым входом первого сумматора 11, второй сумматор 12, второй вход которого подключен к выходу первого элемента 2 задержки , третий инвертор 8, третий электронный ключ 15, второй элемент ИЛИ 18, второй вход которого соединен с выходом первого элемента 2 задержки, второй преобразователь 21 напряжение - частота, первый RS-триггер 26, прямой выход которого также подключен к управляемому входу второго электронного ключа 14, первый блок 29 дифференцирования и второй элемент 3 задержки, первый выход которого соединен с управляющим входом цифрового делителя 35, последовательно соединены третий преобразователь 22 напряжение - частота и второй счетчик 24, выход которого соединен с вторым информационным входом цифрового делителя 35, последовательно соединены второй блок 30 дифференцирования, вход которого соединен с выходом компаратора 31, третий элемент 4 задержки и второй RS-триггер 27, выход которого подключен к управляющим входам первого 13 и третьего 15 электронных ключей, выход второго элемента 3 задержки соединен с управляющими кходами первого и второго пиковых детекторов 9 и 10, первого и второго счетчиков 23 и 24, первого цифрового умножителя 33, регистратора 32, R- входом первого RS-триггера 26 и S- . входом второго RS-триггера 27, последовательно соединены третий RS-триггер 28, S и R-входы которого подключены соответственно к выходам первог го блока 29 дифференцирования и третьего элемента 4 задержки, четвертый ключ 16, третий счетчик 25, установочный вход которого соединен с выходом третьего элемента 4 задержки, и второй цифровой умножитель 34, второй информационный и управляющий входы которого подключены соотретстг венно к вторым разрядным выходам бло5

ка 36 памяти и второму выходу второго элемента 3 задержки, а выход соединен с вторыми информационными разрядными входами регистратора 32, последовательно соединены четвертый элемент 5 задержки, вход которого подключен к выходу первого блока 29 дифференцирования, и третий элемент ИЛИ 19, выход которого соединен с ин формационным входом четвертого ключа 16, видеоусилитель 37, вход и выход которого соответственно подключены к выходу четвертого ключа 16 и второму входу третьего элемента ИЛИ 19.

Устройство работает следующим образом.

Исследуемый импульсный сигнал поступает на вход нормализатора 1 импульсов. На его выходе вырабатываются постоянные по амплитуде импульсы и (фиг,2а), которые поступают на второй вход компаратора 31, вход первого элемента 2 задержки и второй вход первого элемента ИЛИ 17, с выхода которого первый исследуемый импульс подается на вход третьего преобразователя 22 напряжение - частота, который вырабатывает счетные импульсы, количество которых пропорционально амплитуде U импульса и под- считьшается вторым счетчиком 24, с выхода которого их числовое значение

в двоичном коде поступает на первый вход цифрового делителя 35, а через

второй электронный ключ 14 подается на первьй пиковьй детектор 9,. который запоминает изменение текущего напряжения Пдп, (фиг о 26) переднего фронта исследуемого импульса U, за время 1(5 выхода первого элемента 2 задержанный на время импульс (фиг.2в) поступает на второй вход компаратора 3 и через второй элемент ИЛИ 18 на вход второго преобразователя 21 напряжение - частота. В момент формирования начала переднего фронта задержанного импульса Uj (фиго2в, t tj) на выходе первого преобразователя 20 напряжение - частота вырабатывается первый счетный импульс, который поступает на S-вход первого RS-триггера 26 и переводит его в положение логического 1 (фиг.2г, ). На прямом выходе первого RS-триггера 26 образуется напряжение логической 1, которое подается на вход первого блока 29 дифференцирования и запирает второй злектрон95724

ный ключ 14, оставляя напряжение на первом детекторе 9 на уровне (фиг,26, t t), С выхода первого , пикового детектора 9 напряжение поступает на вход первого преобразователя 20 напряжение - частота, который вырабатывает счётные импульсы, количество которых пропорционально 10 напряжению и подсчитывается первым счетчиком 23, с выхода которого значение счетных импульсов в двоичном коде поступает на первый вход цифрового делителя 35.

15 Передний фронт импульса U первого RS-триггера 26 дифференцируется первым блоком 29 дифференцирования, образуя положительный импульс Uj. (фиг.2д), который поступает на вход

20 четвертого элемента 5 задержки, S- вход третьего RS-триггера 28, переводя его в положение логической 1, и после задержки на время С , вторым элементом 3 задержки результаты сче25 та передает в цифровой делитель 35, где вычисляется отношение амплитуды Uy импульса к уровню изменения переднего фронта импульса а время С (фиго2е). Результат деления

30 ии/ид-jn передается вторично задержанным на время « (фиг.2е) вторым элементом 3 задержки импульсов в первый цифровой умножитель 33, на который с блока 36 памяти поступает

35 значение задержки и э регистратор 32. На выходе первого цифрового умножителя 33 определяется длительность с ,,, и дз/и переднего фронта исследуемого импульса U, ко40 торая фиксируется регистратором 32.

При этом первый пиковый детектор 9, первый 23 и второй 27 счетчики и, первый RS-триггер 26 возвращаются в

д5 исходное состояние, а второй RS-триг- гер 27 принимает значение логической 1 (фиг„2ж) и первый и третий электронные ключи 13 и 14 открываются Одновременно на выходе третье50 го RS-триггера 28 вырабатывается напряжение и,7 (фиго2-с), которое поступает на управляющий вход четвертого электронного ключа 16, а задержанный четвертым элементом 5 задержки

ее импульсов импульс иу через третий элемент ИЛИ 19 и открытый напряжением и,7 четвертый электронный ключ 16 подается на счетньш вход третьего счетчика 25, ос1 щестБЛЯющего подсчет

поступающих на его вход импульсов, и видеоусилитель 37. Усиленный усилителем до величины срабатывания двоичного счетч1-жа 25 (не менее 2,4 В),

второго преобразователя 21 напряжение - частота.

В момент формирования начала заднего фронта задержанного импульса

| название | год | авторы | номер документа |

|---|---|---|---|

| Измеритель длительности фронтов импульсов | 1987 |

|

SU1422189A1 |

| Устройство для контроля восприимчивости радиоприемников по побочным каналам приема | 1987 |

|

SU1411986A2 |

| Устройство для измерения коэффициента затухания между антеннами | 1985 |

|

SU1490652A1 |

| Устройство для контроля восприимчивости радиоприемников по побочным каналам приема | 1986 |

|

SU1383511A1 |

| Устройство для контроля чувствительности побочных каналов в радиоприемнике | 1986 |

|

SU1378073A1 |

| Измеритель длительности фронтов импульсов | 1988 |

|

SU1557535A1 |

| Устройство для контроля чувствительности побочных каналов в радиоприемниках | 1985 |

|

SU1264357A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ОТНОСИТЕЛЬНЫХ УРОВНЕЙ ПОБОЧНЫХ КОЛЕБАНИЙ РАДИОПЕРЕДАТЧИКОВ | 1990 |

|

RU2033618C1 |

| Устройство для допускового контроля амплитудно-частотной характеристики четырехполюсников | 1986 |

|

SU1348748A2 |

| Устройство для измерения коэффициента рассеяния антенны | 1985 |

|

SU1357879A1 |

Изобретение относится к измерительной технике и может быть использовано для измерения параметров импульсов в автоматике, вычислительной и контрольно-измерительной технике. Цель изобретения - расширение функциональных возможностей измерителя - достигается в результате одновременного автоматического измерения длительностей фронтов импульсов и их оснований и вершин. Измеритель содержит нормализатор 1 импульсов, элементы 2-5 задержки, инверторы 6-8, пиковые детекторы 9 и 10 со сбросом, сумматоры 11 и 12, электронные ключи 13-16, выполненные в виде реле, элементы ИЛИ 17-19, преобразователи 20-22 напряжение-частота, счетчики 23-25, RS-триггеры 26-28, блоки 29 и 30 дифференцирования, компаратор 31, регистратор 32, цифровые умножители 33 и 34, цифровой делитель 35, блок 36 памяти, видео-усилитель 37. Для определения длительности вершины исследуемого импульса вычисляется разность между длительностями основания исследуемого импульса и суммой длительностей переднего и заднего фронтов. 2 ил.

но задержанный на Г, импульс U че- U, (фиг„2н, t t) на выходе перворез третий элемент ИЛИ 19 опять поступает через открытый четвертый электронный ключ 16 на счетный вход третьего счетчика 25 и вход видеоуси- ю лителя 37. На выходе видеоусилителя 37 опять вырабатьшается усиленный до напряжения срабатьшания счетчика 25, но задержанный импульс Uj,. который вновь через третий элемент 19 по- 15 дается через открытый четвертый электронный ключ 16 на счетный вход счетчика 25, т.е. наступает формирование последовательности коротких высокочастотных импульсов (фиг. 2т) с -20 периодом следования Т С течение действия напряжения U;, на управляющем входе электронного ключа 16,

При этом с выхода первого элемента 2 задержки напряжение U, инвертируясь вторым инвертором 7, в виде напряжения Ug (фиг.2з) подается на вход второго пикового детектора 10, которьш запоминает амплитуду U исследуемого импульса, поступающую в виде напряжения U (фиг.2и) на втого преобразователя 20 напряжение - частота вновь вырабатывается первый счетный импульс, который поступает на S-вход первого RS-триггера 26 и переводит его в положение логической 1 (фиг.2г, ). На прямом выходе первого RS-триггера 26 опять образуется положительное напряжение и, которое подается на вход первого блока 29 дифференцирования и опять запирает второй электронный ключ 14, оставляя напряжение на первом пиковом детекторе 9 на уровне При этом первый 20 и третий 22 преобразователи вырабатывают счетные импуль25

рой вход первого сумматора II, на первый вход которого с выхода нормализатора 1 импульсов подается напря - жение и.

.,35

но напряжениям U,. и UM соответственно и подсчитывается первым и вторым счетчиками 23 и 24, с выходов которых результаты счета в двоичном коде поступают на цифровой делитель 35о

Опять дифференцируется первым бло30 ком 29 дифференцирования передний фронт импульса U4 первого RS-триггера 26 (фиго2г, ), которым после задержки на время о вторым элементом 3 задержки результаты счета первого 23 и второго 24 счетчиков передаются в цифровой делитель 35, где вычисляется отношение амплитуды импульса Uj к уровню изменения напряжения ид заднего фронта исследуеНа выходе первого сумматора 11 образуется отрицательное напряжение V д (фиг.2к), которое, инвертируясь первым инвертором 6 (фиг„2л), в виде напряжения U, через первый электронный ключ 13, первый элемент ИЛИ 17 и второй электронный ключ 14 поступает на первый пиковый детектор 9, на выходе которого осуществляется формирование изменения напряжения

и

ог

заднего

фронта течение

исследуемого времени л

импульса в поступающего на вход первого преобразователя 20 напряжение - частота. При этом на .первом и втором входах второго сумматора 12 формируются напряжения Vcf- (фиг.2и) и Из (фиг.2в), которые на его выходе образуют отрицательное напряжение U, (фиго2м), которое, инвертируясь третьим инвертором 8 (фиг.2н), через третий электронньй ключ 15 и втрой элемент ШТО 18 подается на вход

го преобразователя 20 напряжение - частота вновь вырабатывается первый счетный импульс, который поступает на S-вход первого RS-триггера 26 и переводит его в положение логической 1 (фиг.2г, ). На прямом выходе первого RS-триггера 26 опять образуется положительное напряжение и, которое подается на вход первого блока 29 дифференцирования и опять запирает второй электронный ключ 14, оставляя напряжение на первом пиковом детекторе 9 на уровне При этом первый 20 и третий 22 преобразователи вырабатывают счетные импуль5 0

5

5

но напряжениям U,. и UM соответственно и подсчитывается первым и вторым счетчиками 23 и 24, с выходов которых результаты счета в двоичном коде поступают на цифровой делитель 35о

Опять дифференцируется первым бло0 ком 29 дифференцирования передний фронт импульса U4 первого RS-триггера 26 (фиго2г, ), которым после задержки на время о вторым элементом 3 задержки результаты счета первого 23 и второго 24 счетчиков передаются в цифровой делитель 35, где вычисляется отношение амплитуды импульса Uj к уровню изменения напряжения ид заднего фронта исследуе0 МО го импульса за время .

В момент формирования заднего фронта исследуемого импульса U, в результате превышения напряжением и напряжения U на выходе компарато45 ра 31 вырабатывается импуйьс

(фиго2о), задний фронт которого, дифференцируясь вторым блоком 30 дифференцирования (фиг.2п), подается на R-вход третьего КЗ-триггера 28, пе50 реводя его в положени.е логического О. На выходе третьего RS-тригг ра формируется напряжение логического

О, четвертый электронный ключ закрывается и подсчет счетчиком 25 по- gg следовательности импульсов U(g прекращается. Результат деления и подсчета счетчиком количества импульсов передается вторично за- держанным на время t элементом 3 задержки импульсов в первый и второй цифровые умножители 33 и 34 соответственно, на которые с первого и вторю го выходов блока 36 памяти поступают значения о и , и на регистратор 32 о На выходах первого и второго цифровых умножителей 33 и ЗА вырабатываются значения длительностей заднего фронта иГоп п. Ci основания исследуемого импульса и,, которые фиксируются регистратором 32. При этом задержанный третьим элементом 3 задержки импульс (фиго2п) в виде импульса и(фиг.2р) поступает на S-вход второго RS-триг- гера 27 и установочный вход третьего счетчика 24, второй RS-триггер 27 и третий счетчик 25 возвращаются в исходное состояние и процесс измерения длительностей фронтов и основания исследуемого импульса прекращается .

В случае необходимости для определения длительности вершины исследуемого импульса осуществляется вычисление разности Cjji, (ц() между длительностями основания исследуемого импульса и суммой длительностей переднего и заднего его фронтов, а для определения статистических характеристик параметров импульса число измерений выбирают исходя из достоверности этих измерений. Формула изобретения : Измеритель длительности фронтов импульсов по авт.св. W 1422189, о тл и ч а :о щ и и с я тем, что, с целью расширения функциональных возможностей измерителя за счет одно- временного автоматического измерения длительности фронтов импульсов и длительности их оснований и вершин, в него дополнительно введены последовательно соединенные третий

RS-триггер, четвертый ключ, третий счетчик и второй цифровой умножитель, последовательно соединенные четвертый элемент задержки и третий элемент ИЛИ, а также видеоусилитель,

причем S- и R-входы третьего RS- триггера соединены соответственно с выходами первого и второго блоков дифференцирования, установочный вход третьего счетчика соединен с выходом

третьего элемента задержки, второй информационный и управляющий входы второго цифрового умножителя, подключены соответственно к вторым разрядным выходам блока памяти и второму

выходу второго элемента задержки, а выход соединен с вторыми информационными разрядными входами регистратора, вход четвертого элемента задержки подключен к выходу первого

блока дифференцирования, выход третьего элемента ИЛИ соединен с информационным входом четвертого ключа, а вход и выход видеоусилителя соответственно подключены к выходу четвертого ключа и второму входу третьего элемента ИЛИ.

Авторы

Даты

1989-07-23—Публикация

1987-12-01—Подача