Изобретение относится к вычислительной технике и может быть использовано в устройствах передачи данных для преобразования параллельного двоичного кода в период повторения импульсов .

Целью изобретения является повышение надежности работы преобразователя .

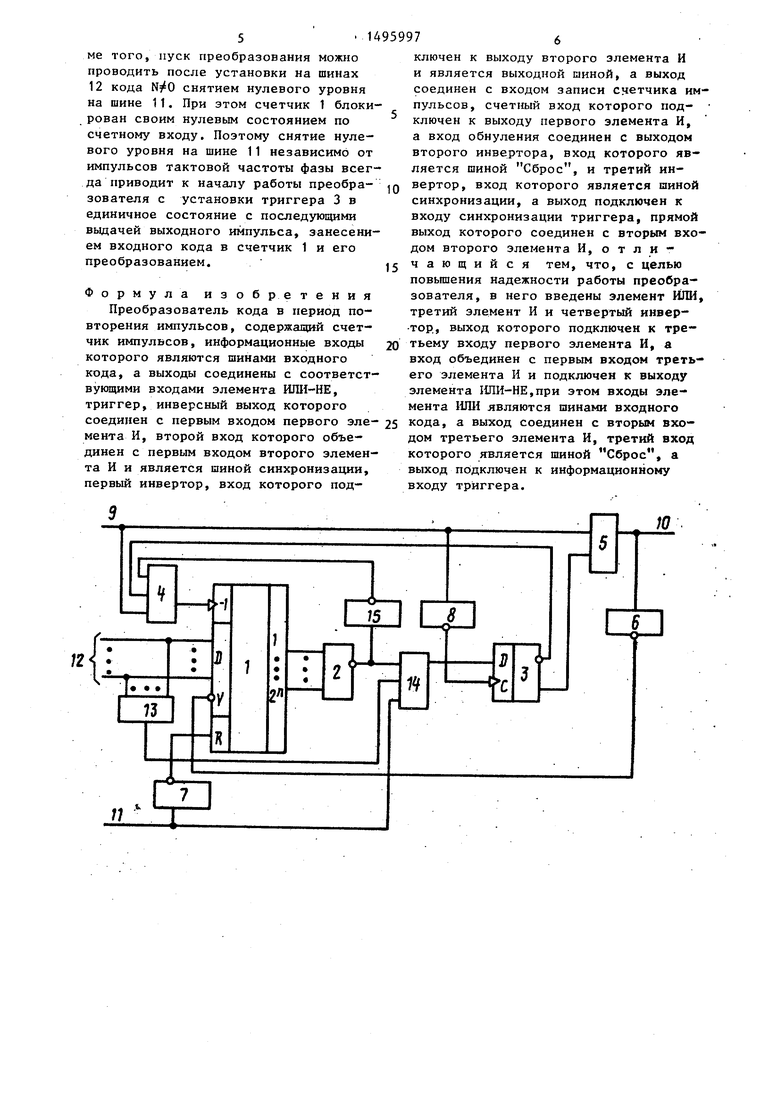

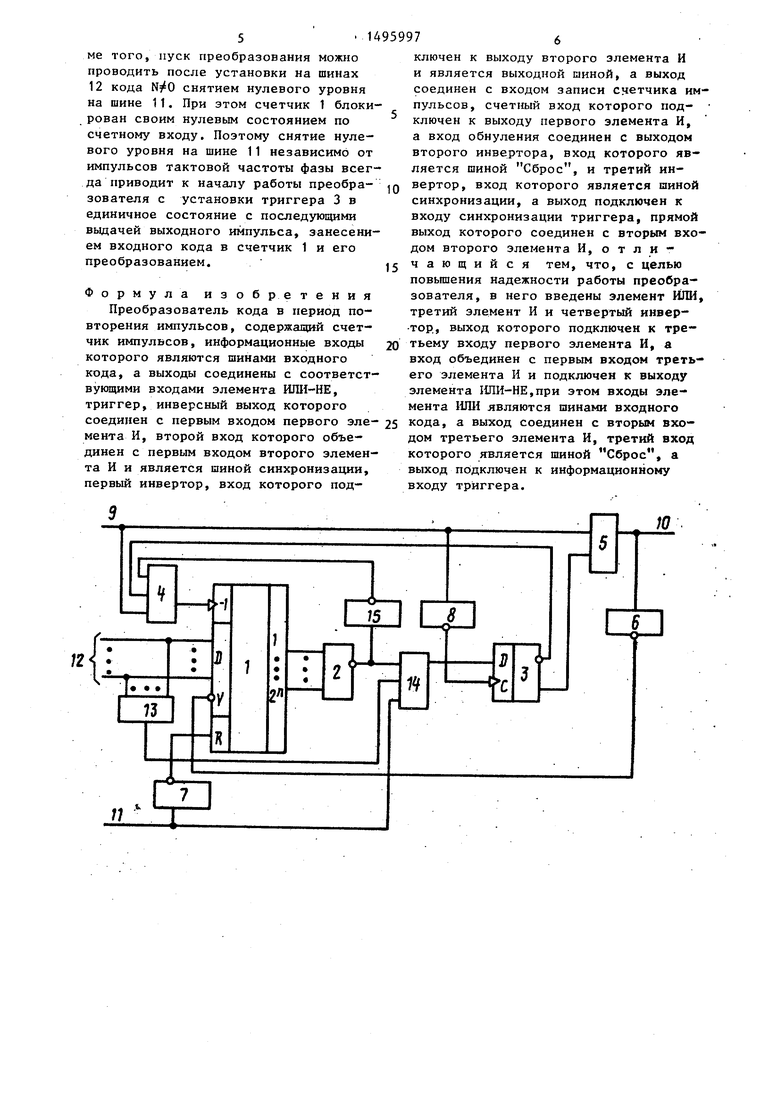

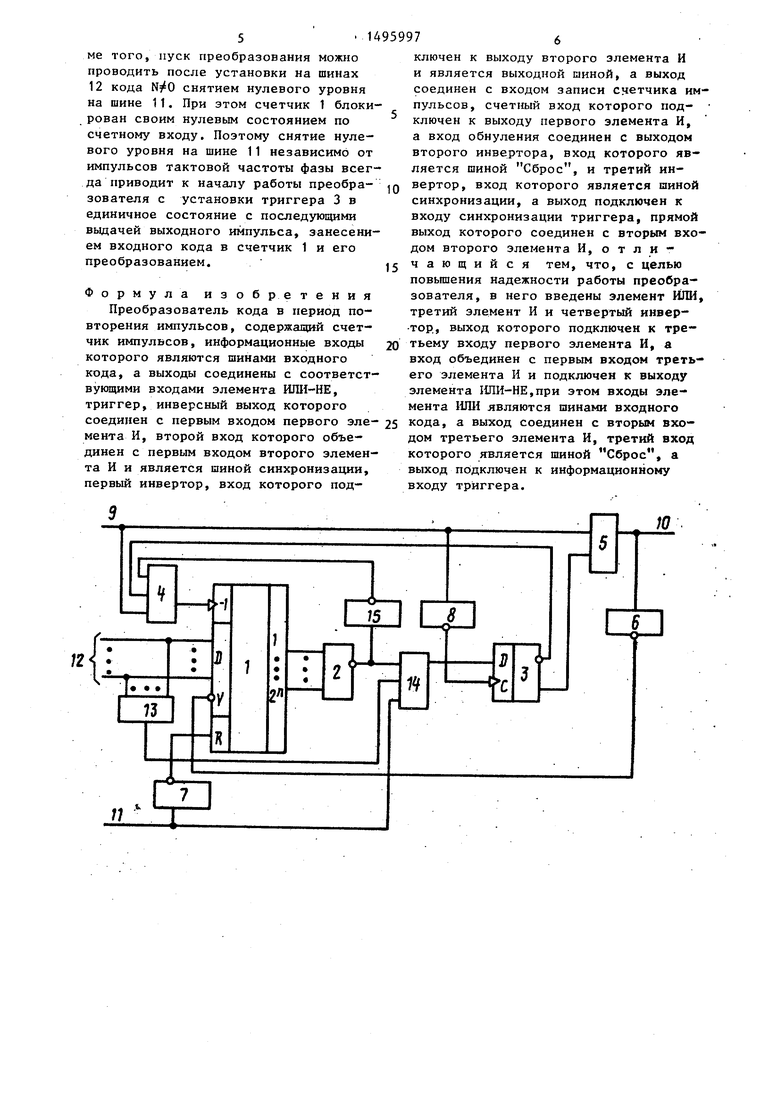

На чертеже представлена функциональная схема преобразователя.

Преобразователь кода в период повторения импульсов содержит счетчик 1 импульсов, элемент Ш1И-НЕ 2, триггер 3, элементы И 4 и 5, инверторы 6 - В, шину 9 синхронизации, выходную шину 10, шину 11 Сброс, шины 12 входного кода, элеме.нт ИЛИ 13, элемент И 14 и инвертор 15.

Преобразователь работает следующим образом.

В исходном состоянии на шине 9 присутствуют тактовые импульсы. На шинах 12 - нулевой код, который устанавливает на выходах элементов ИЛИ 13 и И 14 нулевые уровниг Инвертор 8 инвертирует тактовые импульсы. Триг- /гер 3 нулевым уровнем на D-входе (информационном) по заднему фронту тактового импульса на шине 9 установлен в нулевое состояние, при котором на его прямом выходе удерживается нулевой уровень, а на инверсном выходе - единичный уровень. Нулевой уровень с прямого выхода триггера 3 блокирует элемент И 5. При этом на выходе элемента И 5 и выходной шине 10 -г нулевой уровень, который инвертором 6 преобразуется в единичный уровень. Единичный уровень с выхода инвертора 6 не производит запись кода с шин 12 в счетчик 1. На шине t1 сиг.

СО

ел

со со

нал сброса отсутствует.(единичный уровень), На выходе инвертора 7 - нулевой уровень.

Состояние счетчика 1, элемента ИЛИ-НЕ 2, инвертора 15 и элемента И произвольно. При поступлении сигнала сброса по шине 11 счетчик устанавливается в нулевое состояние, при ;котором на его выходах устанавливают I ся нулевые уровни. Нулевые уровни выхо- дов счетчика 1 устанавливают на выходе элемента.1ШИ-НЕ 2 единичный уровень, по которому на выходах инвертора 15 1и элемента И 4 формируются нулевые ;уровни. После окончания сигнала сбро ica преобразователь находится в жду- щем режиме до тех пор, пока на шины 12 не поступит двоичный код- I числа, отличный от нуля. При поступ- |лении на шины 12 двоичного кода |на выходе элемента 1ШИ 13 устанав- |ливается единичный уровень, который I проходит через элемент И 14 на D- |вход триггера 3. По заднему фронту I первого ближайшего тактового им- ; пульса на шине 9 триггер 3 устанав- |ливается в единичное состояние. Еди- ;ничный уровень прямого выхода триггера 3 от крьшает элемент И 5 и с шины 9 на выходную шину 10 проходит первый импульс. На счетный вход счетчика 1 импульсы не поступают, так как элемент И 4 блокирован нулевь1ми уровнями инвертора 15 и инверсного выхода триггера 3. С выхода элемента И 5 первый импульс через инвертор 6 проходит на вход записи счетчика 1,

При нулевом уровне на входе запис счетчика 1 происходит запись числа в счетчик 1 с входов 12. При этом состояние счетчика 1 изменяется и на выходе элемента 11ПН-НЕ 2 устанавливается нулевой уровень, которьй проходит через элемент И 14 на D-вход триггера 3, Одновременно нулевой уровень выхода элемента ИЛИ-НЕ 2 устанавливает на выходе инвертора 13 единичный уровень, который поступает на третий вход элемента И 4. Установление кода числа в счетчике 1 и срабатывание элементов ИЛИ-НЕ 2 и И 14 должны произойти до момента появления заднего фронта первого импульса выхода 10, По заднему фронту первого импульса, проходящего через инвертор 8 на вход синхронизации триггера 3, последний устанавливает

5

0

5

0

5

0

5

0

5

ся в нулевое состояние, так как на его D-входе присутствует нулевой уровень с выхода элемента И 14. Элемент И 5 блокир уется. Единичный уровень с инверсного выхода триггера 3 открьшает элемент И 4 и импульсы тактовой частоты через элемент И 4 поступают на счетный вход счетчика 1. По переднему фронту каждого импульса из содержимого счетчика 1 вычитается единица. По задне1.гу фронту импульса, установившего счетчик 1 в нулевое состояние, триггер 3 устанавливается в единичное состояние, поскольку на его D-входе находится единичный уровень выхода элемента И 14. При этом элемент И 4 закрывается нулевым уровнем инверсного выхода триггера 3, а элемент И 5 открывается единичным уровнем с прямого выхода триггера 3. На выходную шину 10 проходит второй импульс с шины 9. Полученный временной интервал между первым и вторым импульсами на выходной шине 10 соответствует коду числа на шинах 12. Второй импульс, пройдя инвертор 6 и поступив на вход записи счетчика 1, производит запись нового кода. Если код на шинах 12 не изменился или изменился, но N не равно нулю, то далее процесс преобразования кода в период повторения импульсов повторяется.

Если код на шинах 12 изменился и стал равен нулю, то на выходе элемента ИЛИ 13 формируется нулевой уро- вень, который проходит через элемент И 14 на D-вход триггера 3. Триггер 3 по заднему фронту второго импульса, проходящего на выходную шину 10, устанавливается в нулевое состояние, тем cai-ibiM блокируя выходную шину 10. При коде (отсутствие преобразования) на шинах 12 преобразователь устанавливается в начальное состояние и находится в этом.состоянии до тех пор, пока код не станет . Нулевым уровнем сигнала на шине 11 производится начальная установка как перед началом работы, так и в процессе окончания работы. При этом триггер 3 устанавливается в начальное состояние задним фронтом импульса на шине 9 по нулевому уровню своего D-входа.

При блокировке преобразователя в процессе окончания работы независимо от времени прихода нулевого уровня сигнала на шине 11 искажения выходного импульса не происходит. Кроме того, пуск преобразования можно проводить после установки на шинах 12 кода снятием нулевого уровня на шине 11. При этом счетчик 1 блокирован своим нулевым состоянием по счетному входу. Поэтому снятие нулевого уровня на шине 11 независимо от импульсов тактовой частоты фазы всегключен к выходу второго элемента И и является выходной ииной, а выход соединен с входом записи счетчика импульсов, счетный вход которого под- ключен к выходу первого элемента И, а вход обнуления соединен с выходом второго инвертора, вход которого является шиной Сброс, и третий инда приводит к началу работы преобра- Q вертор, вход которого является шиной

синхронизации, а выход подключен к входу синхронизации триггера, прямой выход которого соединен с вторым входом второго элемента И, отличающийся тем, что, с целью повышения надежности работы преобразователя, в него введены элемент ИЛИ,

зователя с установки триггера 3 в единичное состояние с последующими выдачей выходного импульса, занесением входного кода в счетчик 1 и его преобразованием.

15

Формула изобретения Преобразователь кода в период повторения импульсов, содержащий счетчик импульсов, информационные входы 20 которого являются шинами входного кода, а выходы соединены с соответствующими входами элемента ИЛН-НЕ, триггер, инверсный выход которого соединен с первым входом первого эле- 25 мента И, второй вход которого объединен с первым входом второго элемента И и является шиной синхронизации, первый инвертор, вход которого подтретий элемент И и четвертый инвер- -тор, выход которого подключен к третьему входу первого элемента И, а вход объединен с первым входом третьего элемента И и подключен к выходу элемента 1ШИ-НЕ,при этом входы элемента ИЛИ являются шинами входного кода, а выход соединен с вторым входом третьего элемента И, третий вход которого является шиной Сброс, а выход подключен к информационному входу триггера.

ключен к выходу второго элемента И и является выходной ииной, а выход соединен с входом записи счетчика импульсов, счетный вход которого под- ключен к выходу первого элемента И, а вход обнуления соединен с выходом второго инвертора, вход которого является шиной Сброс, и третий интретий элемент И и четвертый инвер- -тор, выход которого подключен к третьему входу первого элемента И, а вход объединен с первым входом третьего элемента И и подключен к выходу элемента 1ШИ-НЕ,при этом входы элемента ИЛИ являются шинами входного кода, а выход соединен с вторым входом третьего элемента И, третий вход которого является шиной Сброс, а выход подключен к информационному входу триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управляемой задержки импульсов | 1985 |

|

SU1290503A1 |

| Управляемый формирователь импульсов | 1988 |

|

SU1559397A1 |

| Устройство тактовой синхронизации и выделения пачки импульсов | 1983 |

|

SU1185588A2 |

| Устройство для определения наименьшего общего кратного чисел | 1985 |

|

SU1304016A1 |

| Делитель частоты с дискретной регулировкой длительности импульсов | 1984 |

|

SU1226662A1 |

| Формирователь последовательности импульсов | 1989 |

|

SU1647862A1 |

| Счетное устройство | 1986 |

|

SU1396272A1 |

| Делитель частоты с переменным коэффициентом деления | 1985 |

|

SU1322471A1 |

| Устройство для селекции и формирования импульсов | 1981 |

|

SU995301A1 |

| Многоканальный счетчик импульсов | 1987 |

|

SU1508342A1 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах передачи данных. Цель изобретения - повышение надежности в работе преобразователя - достигается тем, что в преобразователь кода в период повторения импульсов, содержащий счетчик импульсов, элемент ИЛИ-НЕ, триггер, два элемента И, три инвертора, шину синхронизации, выходную шину, шину "Сброс" и шины входного кода, введены элементы ИЛИ, И и инвертор. Введение в преобразователь дополнительных элементов с соответствующими связями позволяет устранить искажение последнего выходного импульса, блокировать нулевым кодом информационные входы преобразователя и устранить зависимость начала преобразования от момента окончания сброса. 1 ил.

| Преобразователь кода в период повторения импульсов | 1982 |

|

SU1051705A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Машина для выворотки перчаток | 1959 |

|

SU128397A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-07-23—Публикация

1987-12-23—Подача