17.i(

П7

(Л

Фиг.--1

31508

Изобретение-относится к импульсной технике и может быть использовано в счетных устройствах для счета количества импульсов от нескольких одновременно работающих источников.

Целью изобретения является повышение быстродействия.

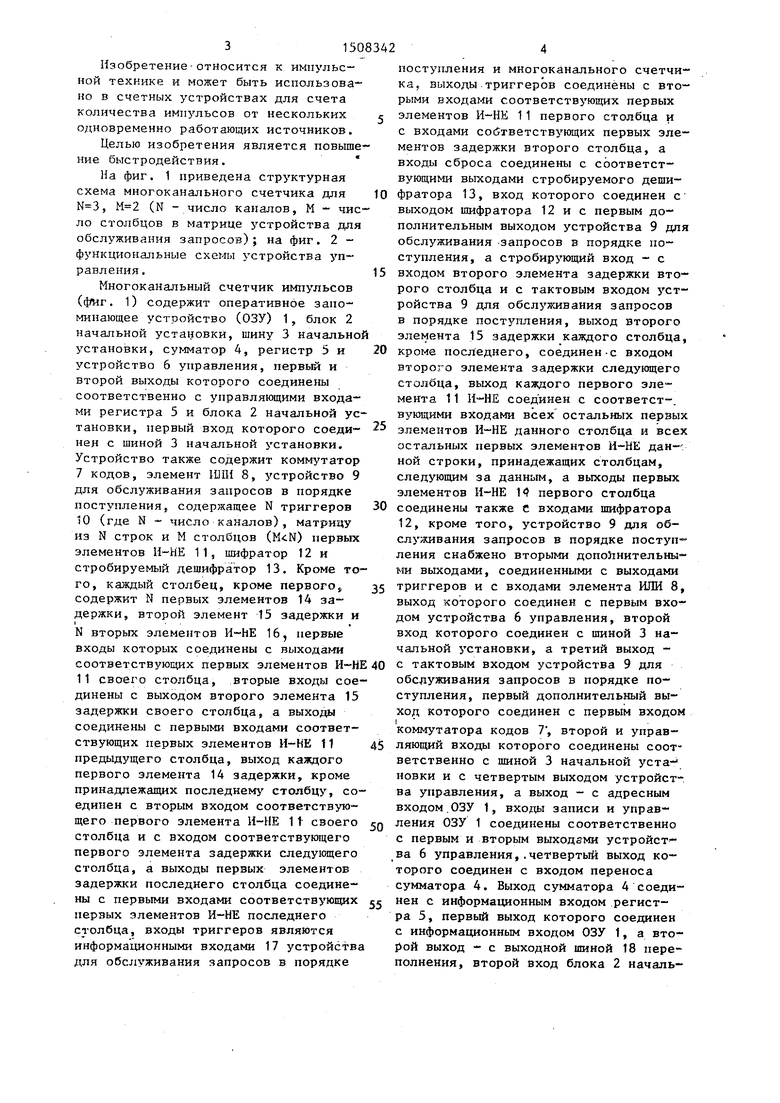

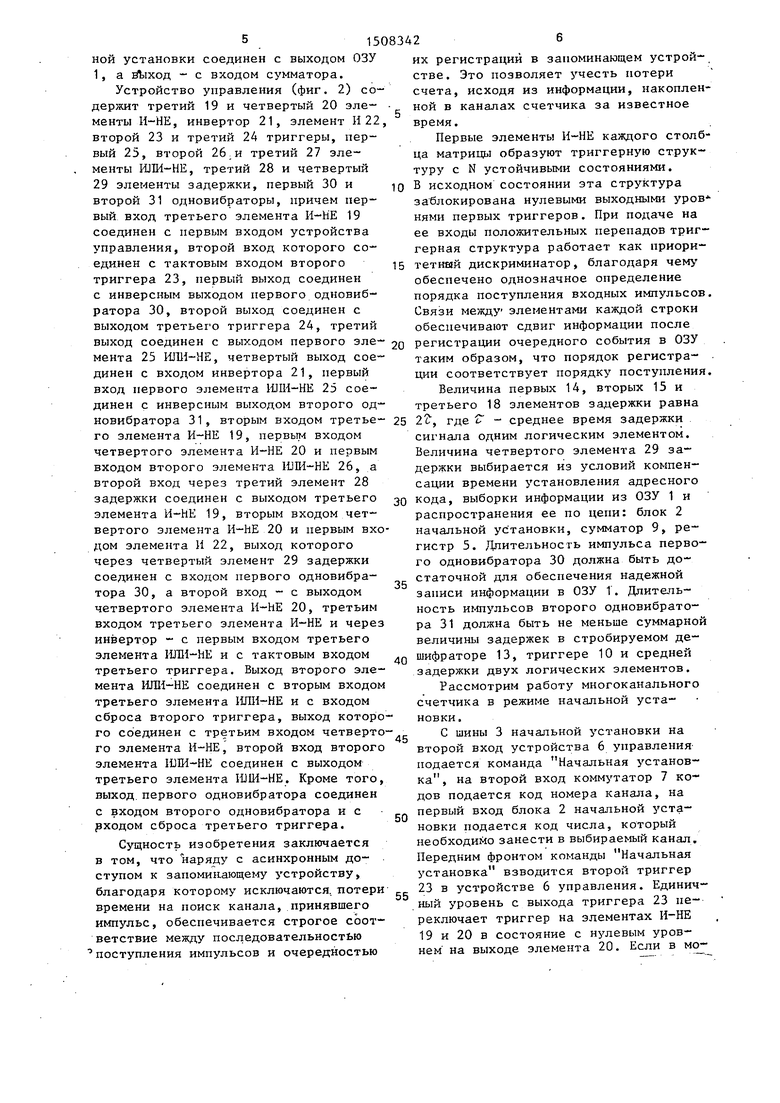

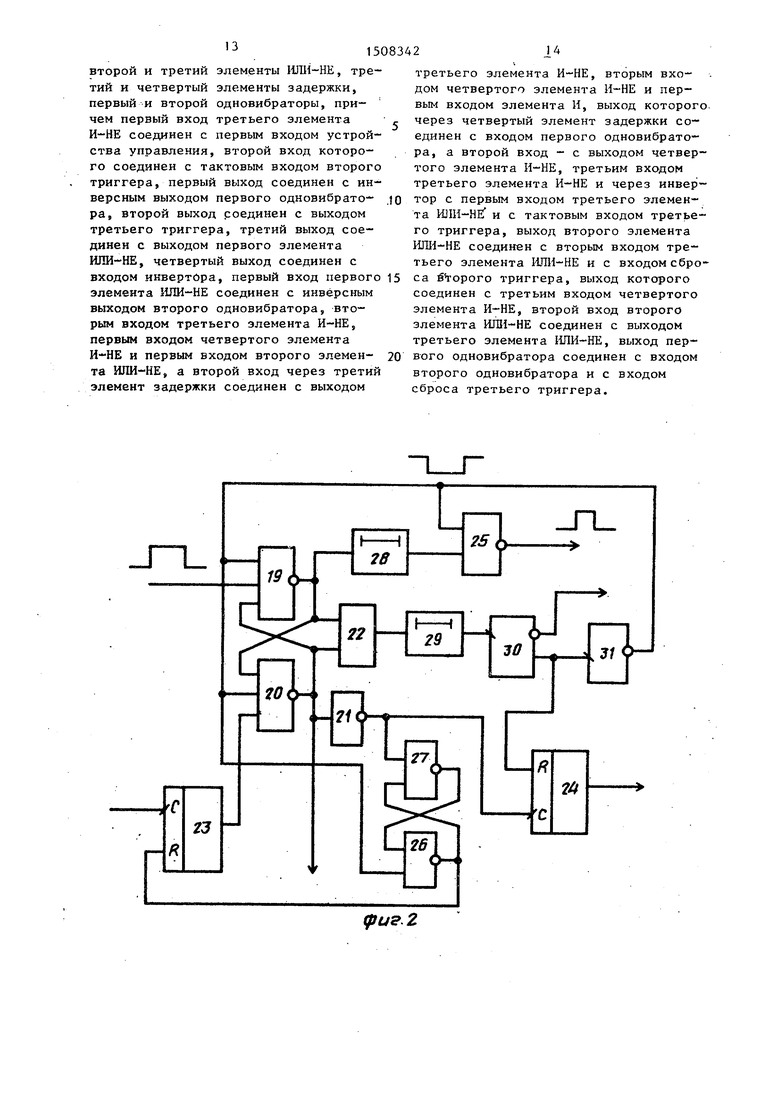

На фиг. 1 приведена структурная схема многоканального счетчика для , (N - число каналов, М - число столбцов в матрице устройства для обслуживания запросов); на фиг. 2 - функциональные схемы устройства управления.

Многоканальный счетчик импульсов (фяг. 1) содержит оперативное запоминающее устройство (ОЗУ) 1, блок 2 начальной установки, шину 3 начальной установки, сумматор 4, регистр 5 и устройство 6 управления, первый и второй выходы которого соединены соответственно с управляющими входами регистра 5 и блока 2 начальной установки, первый вход которого соеди- нен с шиной 3 начальной установки. Устройство также содержит коммутатор 7 кодов, элемент ШП 8, устройство 9 для обслуживания запросов в порядке поступления, содержащее N триггеров

10(где N - число каналов), матрицу из N строк и М столбцов () первых элементов И-НЕ 11, шифратор 12 и стробируемый дешифратор 13. Кроме того, каждый столбец, кроме первого содержит N первых элементов 14 задержки, второй элемент 15 задержки и

N вторых элементов И-hE 16, первые входы которых соединены с выходами соответствующих первых элементов И-НЕ

11своего столбца, вторые входы соединены с выходом второго элемента 15 задержки своего столбца, а выходы соединены с первыми входами соответствующих первых элементов И-НЕ 11 предыдущего столбца, выход каяадого первого элемента 14 задержки, кроме принадлежащих последнему столбцу, соединен с вторым входом соответствующего первого элемента И-НЕ 11 своего столбца и с входом соответствующего первого элемента задержки следующего столбца, а выходы первых элементов задержки последнего столбца соединены с первыми входами соответствующих первых элементов И-НЕ последнего столбца, входы триггеров являются информационными входами 17 устройства для обслуживания запросов в порядке

поступления и многоканального счетчика, выходы триггеров соединены с вторыми входами соответствующих первых элементов И-НЕ 11 первого столбца и с входами соответствующих первых элементов задержки второго столбца, а входы сброса соединены с соответствующими выходами стробируемого дешифратора 13, вход которого соединен с выходом шифратора 12 и с первым дополнительным выходом устройства 9 для обслуживания запросов в порядке поступления, а стробирующий вход - с входом второго элемента задержки второго столбца и с тактовым входом устройства 9 для обслуживания запросов в порядке поступления, выход второго элемента 15 задержки каждого столбца, кроме последнего, соединен-с входом второго элемента задержки следующего столбца, выход каждого первого элемента 11 И-НЕ соединен с соответст-. вующими входами всех остальных первых элементов И-НЕ данного столбца и всех остальных первых элементов И-НЕ дан-: ной строки, принадежащих столбцам, следующим за данным, а выходы первых элементов И-НЕ 1 первого столбца соединены также С входами шифратора 12, кроме того, устройство 9 для обслуживания запросов в порядке поступления снабжено вторыми дополнительны- ш выходами, соединенными с выходами триггеров и с входами элемента ИЛИ 8, выход которого соединен с первым вхо- дом устройства 6 управления, второй вход которого соединен с шиной 3 начальной установки, а третий выход - с тактовым входом устройства 9 для обслуживания запросов в порядке поступления, первый дополнительный выход которого соединен с первым входом

коммутатора кодов 7, второй и управляющий входы которого соединены соответственно с шиной 3 начальной уста- иовки и с четвертым выходом устройства управления, а выход - с адресным входом.ОЗУ 1, входы записи и управления ОЗУ 1 соединены соответственно с первым и вторым выходами устройства 6 управления,.четвертый выход которого соединен с входом переноса сумматора 4. Выход сумматора 4 соединен с информационным входом .регистра 5, первый выход которого соединен с информационным входом ОЗУ 1, а второй выход - с выходной шиной 18 переполнения, второй вход блока 2 начальной установки соединен с выходом ОЗУ 1, а йЪ1ход - с входом сумматора.

Устройство управления (фиг. 2) содержит третий 19 и четвертый 20 элементы И-НЕ, инвертор 21, элемент И 22 второй 23 и третий 24 триггеры, первый 25, второй 26-и третий 27 элементы ШШ-НЕ, третий 28 и четвертый 29 элементы задержки, первый 30 и второй 31 одновибраторы, причем первый вход третьего элемента И-НЕ 19 соединен с первым входом устройства управления, второй вход которого соединен с тактовым входом второго триггера 23, первый выход соединен с инверсным выходом первого одновиб ратора 30, второй выход соединен с выходом третьего триггера 24, третий выход соединен с выходом первого элемента 25 ИШ1-ИЕ, четвертый выход соединен с входом инвертора 21, первый вход первого элемента Ш1И-НЕ 25 соединен с инверсным выходом второго од- новибратора 31, вторым входом третьего элемента И-НЕ 19, первым входом четвертого элемента И-НЕ 20 и первым входом второго элемента ШШ-НЕ 26, а второй вход через третий элемент 28 задержки соединен с выходом третьего элемента И-НЕ 19, вторым входом четвертого элемента И-НЕ 20 и первым входом элемента И 22, выход которого через четвертый элемент 29 задержки соединен с входом первого одновибра- тора 30, а второй вход - с выходом четвертого элемента И-НЕ 20, третьим входом третьего элемента И-НЕ и через инвертор - с первым входом третьего элемента ЮТ1-НЕ и с тактовым входом третьего триггера. Выход второго элемента ИЛИ-НЕ соединен с вторым входом третьего элемента ИЛИ-НЕ и с входом сброса второго триггера, выход которого соединен с третьим входом четвертого элемента И-НЕ, второй вход второго элемента ШШ-НЕ соединен с выходом третьего элемента ШШ-НЕ. Кроме того, выход, первого одновибратора соединен с входом второго одновибратора и с рходом сброса третьего триггера.

Сущность изобретения заключается в том, что наряду с асинхронным доступом к запоминающему устройству, благодаря которому исключаются, потери времени на поиск канала, принявшего импульс, обеспечивается строгое соответствие между последовательностью поступления импульсов и очередностью

0

5

0

5

0

5

0

5

0

5

ИХ регистрации в запоминающем устрой-, стве. Это позволяет учесть потери счета, исходя из информации, накопленной в каналах счетчика за известное время.

Первые элементы И-НЕ каждого столбца матрицы образуют триггерную структуру с N устойчивыми состояниями. В исходном состоянии эта структура заблокирована нулевыми выходными уров Ними первых триггеров. При подаче на ее входы положительных перепадов триг- герная структура работает как приоритетный дискриминатор, благодаря чему обеспечено однозначное определение порядка поступления входных импульсов. Связи между элементами каждой строки обеспечивают сдвиг информации после регистрации очередного события в ОЗУ таким образом, что порядок регистрации соответствует порядку поступления.

Величина первых 14, вторых 15 и третьего 18 элементов задержки равна 2с, где tT - среднее время задержки сигнала одним логическим элементом. Величина четвертого элемента 29 задержки выбирается из условий компенсации времени установления адресного кода, выборки информации из ОЗУ 1 и распространения ее по цепи: блок 2 начальной установки, сумматор 9, регистр 5. Дпительность импульса первого одновибратора 30 должна быть достаточной для обеспечения надежной записи информации в ОЗУ Т. Длительность иг-тульсов второго одновибрато- ра 31 должна быть не меньше суммарной величины задержек в стробируемом дешифраторе 13, триггере 10 и средней задержки двух логических элементов.

Рассмотрим работу многоканального счетчика в режиме начальной установки.

С шины 3 начальной установки на второй вход устройства 6 управления подается команда Начальная установка, на второй вход коммутатор 7 кодов подается код номера канала, на первый вход блока 2 начальной установки подается код числа, который необходимо занести в выбираемый канал. Передним фронтом команды Начальная установка взводится второй триггер 23 в устройстве 6 управления. Единичный уровень с выхода триггера 23 переключает триггер на элементах И-НЕ 19 и 20 в состояние с нулевым уровнем на выходе элемента 20. Если в но 150834

мент прихода команды Начальная установка На первом входе устройства 6 управления,уже присутствует единичный уровень, т.е. нроисходит регистрация очередного импульса, то переключение триггера на элементах И-НЕ 19 и 20 в указанное состояние произойдет по окончании регистрации очередного импульса, когда единичный уровень с д первого входа будет снят. Аналогично, если во Бремя действия команды Начальная установка на счетчик поступает импульс, то его регистрация начнется только по окончании этой коман- 5 ды. После переключения триггера на элементах И-НЕ 19 и 20 в состояние, соответствующее режиму начальной ус- тановки, нулевой уровень с выхода элемента И-НЕ 21 через четвертый вы- 20 ход устройства 6 управления поступает на управляющий вход коммутатора 7 кодов и на вход переноса сумматора 4, обеспечивая передачу на адресный вход

ОЗУ кода числа с шины 3 Начальной ус- 25 третьем выходах устройства 6 управле- тановки, а также передачу сумматором 4 информации без добавления единицы. Передним фронтом сигнала с выхода элемента 20 взводится третий тригния установлен нулевой логический уровень. На первом и четвертом выходах устройства 6 управления, а также на выходах всех олементов 11 установгер 24. На втором выходе устройства 6 зо лен единичный логический уровень.

тельности выходного сигнала второго одновибратора 31, обеспечивающий сброс второго триггера 23. По окончании импульса второго одновибратора 31 триггер на элементах 19 и 20 либо устанавливается в исходное состояние с единичным уровнем на обоих выходах, либо в состояние с нулевым уровнем на выходе элемента 19. Последний случай имеет место, если за время выполнения команды Начальная установка на ка- кой-либо из входов счетчика поступил счетный импульс. В этом случае начинается цикл регистрации поступившего импульса. Таким образом, начальную установку можно производить, не останавливая всех входных импульсов.

Рассмотрим работу многоканального счетчика в режиме счёта входных им-. пульсов.

в исходном состоянии на выходах триггеров 10,23 и 24, а также на пер вом и втором входах, на втором и

третьем выходах устройства 6 управле-

третьем выходах устройства 6 управле-

ния установлен нулевой логический уровень. На первом и четвертом выходах устройства 6 управления, а также на выходах всех олементов 11 установ

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО РЕГИСТРАЦИИ СТАТИЧЕСКИХ ТЕЛЕВИЗИОННЫХ ИЗОБРАЖЕНИЙ | 1992 |

|

RU2054818C1 |

| Устройство для контроля оперативных накопителей | 1989 |

|

SU1705874A1 |

| УСТРОЙСТВО АНАЛИЗА ПЕРЕКРЫТИЙ КАНАЛОВ ПРИ РАЗМЕЩЕНИИ ПАРАЛЛЕЛЬНЫХ ПОДПРОГРАММ В МНОГОПРОЦЕССОРНЫХ СИСТЕМАХ | 2011 |

|

RU2460126C1 |

| Устройство для определения координат треков | 1985 |

|

SU1255976A1 |

| Устройство для подсчета минимального значения интенсивности размещения в многопроцессорных кубических циклических системах при однонаправленной передаче информации | 2018 |

|

RU2688236C1 |

| Устройство для счета количества изображений объекта | 1987 |

|

SU1494021A1 |

| УСТРОЙСТВО ПЛАНИРОВАНИЯ ТОПОЛОГИИ ЛОГИЧЕСКИХ ИНТЕГРАЛЬНЫХ СХЕМ | 2012 |

|

RU2530275C2 |

| Устройство для измерения интервалов времени | 1990 |

|

SU1739361A1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР | 2000 |

|

RU2208836C2 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

Изобретение относится к импульсной технике и может использоваться в счетных устройствах. Цель изобретения - повышение быстродействия. Счетчик импульсов содержит оперативное запоминающее устройство 1, блок 2 начальной установки, шину 3 начальной установки, сумматор 4, регистр 5 и устройство 6 управления. Введение в счетчик коммутатора кодов 7, элемента ИЛИ 8 и устройства 9 для обслуживания запросов в порядке поступления позволило уменьшить возможный интервал между сигналами по различным накалам без увеличения ошибки. 1 з.п. ф-лы, 2 ил.

35

управления устанавливается единичный уровень, поступающий на управляющие входы ОЗУ 1 и блока начальной установки. Тем самым запрещается выборка из ОЗУ 1 и обеспечивается поступление на вход су1-1матора 4 кода числа с шины 3 начальной установки. .

Первый одновибратор 30 вырабатывает на первом выходе устройства 6 управления сигнал записи, причем чет- .,, вертый элемент 29 задержки обеспечивает задержку этого сигнала на время, достаточное для установления кода числа на информационном входе ОЗУ 1. Одновременно третий триггер 24 сбрасывается в нулевое состояние и на вто- ром выходе устройства управления устанавливается нулевой уровень, обеспечивающий обращение к ОЗУ 1 по управляющему входу. Задним фронтом сигна45

Пусть ;на информационные входы уст ройства последовательно поступают им пульсы. По переднему фронту этих импульсов взводятся триггеры 10. Поскольку импульс на первый информационный вход поступил раньше, на выходе первого элемента И-НЕ 11 первой строки и первого столбца вырабатывается нулевой уровень, блокирующий элементы И-НЕ 11 данного столбца и последующих столбцов в данной строке На входы элементов И-НЕ 11 второго столбца поступают сигналы с выходов триггеров 10, задержанные элементами 14 задержки второго столбца. Посколь ку первый элемент И-НЕ 11 второго столбца блокирован нулевым уровнем, поступающим с первого элемента И-НЕ 11 первого столбца то переключается первый элемент И-НЕ 11 второй строки

ла записи запускается второй одновиб- О второго столбца, блокируя своим выхо

ратор 31, с выхода которого импульс нулевого уровня подается на входы элементов 19, 20 и 26. Так как на первом входе третьего элемента ШШ-НЕ 27 в этот момент действует единичный уро- вень, то на выходе второго элемента 1ШИ-НЕ 26 вырабатывается положительный импульс длительности, равной длидом последующие элементы 11 данного столбца и второй строки следующего столбца. На выходе шифратора 12 выра батывается ксзд номера г/.рвого канала поступающий через коммутатор 7 кодов на адресный вход ОЗУ 1. По этому адресу из ОЗУ считывается текущая ин- формадия, поступающая через блок 2

5

.,, 5

Пусть ;на информационные входы устройства последовательно поступают импульсы. По переднему фронту этих импульсов взводятся триггеры 10. Поскольку импульс на первый информационный вход поступил раньше, на выходе первого элемента И-НЕ 11 первой строки и первого столбца вырабатывается нулевой уровень, блокирующий элементы И-НЕ 11 данного столбца и последующих столбцов в данной строке. На входы элементов И-НЕ 11 второго столбца поступают сигналы с выходов триггеров 10, задержанные элементами 14 задержки второго столбца. Поскольку первый элемент И-НЕ 11 второго столбца блокирован нулевым уровнем, поступающим с первого элемента И-НЕ 11 первого столбца то переключается первый элемент И-НЕ 11 второй строки

О второго столбца, блокируя своим выхо

дом последующие элементы 11 данного столбца и второй строки следующего столбца. На выходе шифратора 12 вырабатывается ксзд номера г/.рвого канала, поступающий через коммутатор 7 кодов на адресный вход ОЗУ 1. По этому адресу из ОЗУ считывается текущая ин- формадия, поступающая через блок 2

начальной установки на вход сумматора 4. При этом, благодаря тому, что ОЗУ 1 имеет открытые коллекторные выходы и в блоке 2 начальной установ ки осуществлено соединение типа проводное 11Ш1, задержка распространени сигнала в блоке 2 начальной установки, практически отсутствует. В сумматоре 4 значение числа импуль сов увеличивается, на единицу. Посколку на управляющем входе регистра 5, информационные разряды которого построены на триггерах-защелках, присутствует единичный уровень, информация с выхода сумматора поступает на информационный вход ОЗУ 1.

Выходные сигналы триггеров 10 через элемент НЛН 8 поступают на первый вход устройства 6 управления. Триггер, образованный третьим 19 и четвертым 20 элементами И-НЕ, переключается в состояние, при котором на выходе третьего элемента И-НЕ 19 действует нулевой уровень. Спустя время, необходимое для установления на информационном входе ОЗУ 1 нового кода числа, первым одновибратором 30 на первом выходе устройства 6 управления вырабатывается импульс записи. Регистр обеспечивает сохранение и неизменном виде информации на информационном входе ОЗУ 1 на время действия импульса записи, В ОЗУ 1 по соответствующему адресу записывается код нового числа. При наличии единичного уровня на выходе переноса сумматора 4 на втором выходе регистра 5 (шина 18 переполнения) вырабатывается сигнал переполнения.

Задним фронтом выходного сигнала первого одновибратора 30 запускается второй одновибратор 31. Из выходного сигнала второго одновибратора 31 формируется импульс длительностью 3, поступающий с третьего вьпсода устройства 6 управления на тактовый вход устройства 9 для обслуживания запрог сов в порядке поступления. Этот импульс, пройдя на соответствующий вы- ход стробируемого дешифратора 13, вызывает сброс триггера 10 первого канала. Этот же сигнал задерживается вторым элементом 15 задержки второго столбца и поступает на входы вторых элементов И-НЕ 16 второго столбца. На выходе первого элемента И-НЕ 11 второй строки второго столбца установ ле н н левой уровень, а на выходах первых

элементов И-НЕ 1 1 первой строки второго и третьех о столбцов - единичный уровень, поэтому на выходах вторых элементов И-НЕ вырабатываются импульсы нулевого уровня. Эти импульсы устанавливают триггерную структуру на элементах 11 первого столбца в состояние , при котором нулевой уровень действует на выходе элемента 11 второй ; строки первого столбца. Это, в свою очередь, приводит к переключению триг герной структуры на элементах 11 второго Столбца в состояние, при котором нулеёой уровень действует на выходе третьего элемента 11 второго столбца. На выходе элемента ИЛИ 8 остается неизменным единичный уровень, поэтому с окончанием импульса второго одновибратора 31 устройство управления запускается вновь. Начинается цикл регистрации события по второму каналу. В следующем цикле происходит регистрация события по третьему каналу и в еле- : дующем - по четвертому. Таким образом порядок регистрации соответствует порядку поступления импульсов на вход многоканального счетчика. Количество столбцов М в устройстве 9 может быть определено из следующих соображений.

Вследствие статического характера входных потоков абсолютно точное определение числа поступивших импульсов по числу зарегистрированных в счетчике с конечным мертвым временем принципиально невозможно.

В предлагаемом многоканальном счетчике коррекция просчетов может быть произведена с тем большей точностью, чем больше значение М.

Пусть . При поступлении на счетт чик нескольких сигналов первым будет обслужен первый сигнал. Порядок обслуживания второго и последующих сигналов может нарушиться, так как после обслуживания первого сигнала триггер- ная структура на элементах 11 первого столбца случайным образом установится в одно из двух состояний. В практически важном случае , 1 (где п - интенсивность входного потока; , - мертвое время счетчика, т.е. время обслуживания одного события) вероятность тройного совпадения мала по - сравнению с вероятностью двойного совпадения. Исходя из величины и требуемой точности коррекции, следует выбирать необходимое значение М.

Формула изобретения

ны с выходом второго элемента задерж- 30 просов в порядке поступления, первый

ки своего столбца, а выходы соединены с первыми входами соответствующих первых элементов И-НЕ предьщущего столбца, выход каждого первого элемента

задержки, кроме принадлежащих послед- ,с чальной установки и с четвертым выхонему столбцу, соединен с вторым входом соответствующего первого элемента И-НЕ своего столбца и с входом соответствующего первого элемента задержки, следующего столбца, а выходы Q первых элементов задержки последнего столбца соединены с первыми входами соответствующих первых элементов И-НЕ последнего столбца, входы триггеров

дом устройства управления, а выход - с адресным входом оперативного запоминающего устройства, входы записи и управления оперативного запоминаю- щего устройства соединены соответственно с первым и вторым выходами устройства управления, четвертый выход ко горого соединен с входом переноса сумматора, выход сумматора соединен

являются информационными входами Уст 5 информационным входом регистра, перройства для обслуживания запросов в порядке поступления и многоканального счетчика, выходы триггеров соединены с вторыми входами соответствующих первых элементов И-НЕ первого столбца и с входами соответствующих первых элементов задержки второго столбца, а входы сброса соединены с выходами стробируемого дешифратора, информационные вхЬды которого соединены соответственно с выходами шифра тора и с первым дополнительным выходом устройства для обслуживания за- просов в порядке поступления, а стро-.

50

55

вый выход которого соединен с инфор- мационным входом оперативного запоминающего устройства, а второй выход - с выходной шиной переполнения, второй вход блока начальной установки соединен с выходом оперативного запоминающего устройства, а выход - с вхо- ом сумматора.

2, Счетчик по и. 1, о т л и ч а ю- щ и и с я тем, что устройство управления содержит третий и четвертый элементы И-НЕ, инвертор, элемент И, второй и третий триггеры, первый,

бирующий,вход соединен с входом второго элемента задержки второго столбца и с тактовым входом устройства для обслуживания запросов в порядке поступления, выход второго элемента задержки каждого столбца, кроме последнего, соединен с входом второго элемента задержки следующего столбца причем выход каждого первого элемента И-НЕ соединен с соответствующими дополнительными входами всех остальных первых элементов И-НЕ данного столбца и всех остальных первых элементов И-НЕ данной строки, принадлежащих столбцам, следующим за данным, а выходы первых элементов И-НЕ первого столбца соединены также с соответствующими входами шифратора, выходы триггеров являются вторыми дополнительными выходами устройства для обслуживания запросов в порядке поступления, которые подключе1й.1 к в ходам элемента lilM, выход которого соединен с первым входом устройства управления, второй вход устройства управления соединен с шиной начальной установки, а третий выход - с тактовым вводом устройства для обслуживания задополнительный выход которого соединен с первым входом коммутатора кодов, второй и управляющий входы которого соединены соответственно с шиной на-

дом устройства управления, а выход - с адресным входом оперативного запоминающего устройства, входы записи и управления оперативного запоминаю- щего устройства соединены соответственно с первым и вторым выходами устройства управления, четвертый выход ко горого соединен с входом переноса сумматора, выход сумматора соединен

вый выход которого соединен с инфор- мационным входом оперативного запоминающего устройства, а второй выход - с выходной шиной переполнения, второй вход блока начальной установки соединен с выходом оперативного запоминающего устройства, а выход - с вхо- ом сумматора.

2, Счетчик по и. 1, о т л и ч а ю- щ и и с я тем, что устройство управления содержит третий и четвертый элементы И-НЕ, инвертор, элемент И, второй и третий триггеры, первый,

второй и третий элементы ИЛИ-НЕ, третий и четвертый элементы задержки, первый и второй одновибраторы, причем первый вход третьего элемента И-НЕ соединен с первым входом устройства управления, второй вход которого соединен с тактовым входом второго триггера, первый выход соединен с инверсным выходом первого одновибрато- pa, второй выход соединен с выходом третьего триггера, третий выход соединен с выходом первого элемента ИЛИ-НЕ, четвертый выход соединен с входом инвертора, первый вход первого элемента 11ЛИ-НЕ соединен с инверсным выходом второго одновибратора, вторым входом третьего элемента И-НЕ, первым входом четвертого элемента И-НЕ и первым входом второго элемен- та ИЛИ-НЕ, а второй вход через третий элемент задержки соединен с выходом

третьего элемента И-НЕ, вторым входом четвертого элемента И-НЕ и первым входом элемента И, выход которого через четвертый элемент задержки соединен с входом первого одновибратора, а второй вход - с выходом четвертого элемента И-НЕ, третьим входом третьего элемента И-НЕ и через инвертор с первым входом третьего элемента ИЛИ-НЁ и с тактовым входом третьего триггера, выход второго элемента ИПИ-НЕ соединен с вторым входом третьего элемента ВДИ-НЕ и с входом сброса б горого триггера, выход которого соединен с третьим входом четвертого элемента И-НЕ, второй вход второго элемента ИЛИ-НЕ соединен с выходом третьего элемента ИЛИ-НЕ, выход первого одновибратора соединен с входом второго одновибратора и с входом сброса третьего триггера.

| Многоканальный счетчик импульсов | 1981 |

|

SU1014153A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Многоканальный счетчик импульсов | 1983 |

|

SU1170610A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-09-15—Публикация

1987-04-09—Подача