к

j:2b СО

СО 4

со

4

Изобретение относится к электросвязи и может быть использовано в системах передачи информации.

Целью Изобретения является повы- , шение быстродействия,

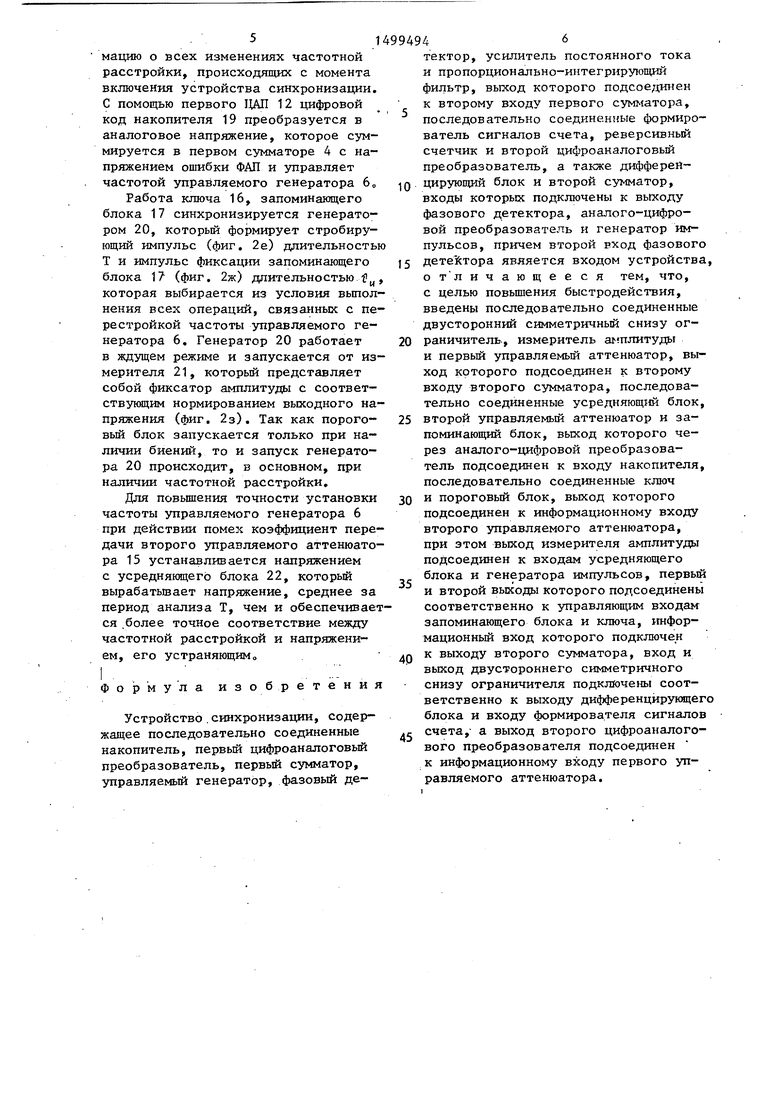

На фиг, 1 изображена структурная электрическая схема устройства синхронизации; на фиг о 2 - временные диаграммы сигналов, поясняющие ра- Jo боту устройства синхронизации.

Устройство синхронизации содержит фазовый детектор (ФД) 1, усилитель 2 постоянного тока (УПТ), пропорционально-интегрирующий фильтр (ПИФ) 3, 15 первый и второй сумматоры 4 и 5, управляемый генератор 6, дифференцирующий блок 7, двусторонний симмет- ричньй снизу ограничитель 8, порого- вьй блок 9, формирователь 10 сигни- 20 лов счета, реверсивный счетчик (РС) 11, первый 12 и второй 13 цифроанало- говые преобразователи (ЦАП), первый 14 и второй 15 управляемые аттенюаторы, ключ 16, запоминающий блок 17, 25 аналого-цифровой преобразователь 18, накопитель 19, генератор 20 импульсов, измеритель 21 амплитуды, усред- няющий блок 22о/

Устройство синхронизации работа- 30 ет следующим образом.

При частотном рассогласовании, меньшем полосы пропускания кольца фазовой автоподстройки (ФАЛ), содержащего ФД 1, УПТ 2, ПИФ 3, первый 35 сумматор 4 и управляемый генератор 6,, введение последнего в синхронный режим работы осуществляется за счет работы данного ,кольца ФАП,

При частотньк расстройках, не 40 отрабатываемых кольцом ФАП, на йы- ходе ФД 1 появляется напряжение бит ений (фиг. 1 и 2а), Это напряжение имеет периодический характер, причем уже первая гармоника этого напряже- 45 ния находится за пределами прозрачности ПИФ Зо Поэтому такое напряжение биений не поступает на вход управляемого генератора 6 из-за подавления в ПИФ 3 и кольцо ФАП не сраба- тьшает.

Вследствие пилообразной характеристики ФД 1 напряжение биений содержит участки с большой крутизной, которые свидетельствуют о наличии час- гг тотной расстройки. Эти участки выделяются с помощью дифференцирующего блока 7 (фиг. 2б), выходное напряжение которого имеет вид коротких им50

5

0

5

0 5

г

0

пульсов одной полярности. При другом знаке частотной расстройки полярность импульсов противоположная,

С выхода дифференцирующего блока

7импульсы поступают на ограничитель 8, форма импульсов на выходе которого подобна форме входных импульсов, но те входные импульсы, амплитуда которых меньше порогового напряжения, на выход ограничителя 8 не пройдут,

С выхода ограничителя 8 импульсы поступают одновременно в измеритель 21. и формирователь 10, которьй после соответствующей нормировки и преобразования подает импульсы оДной полярности, например, на . сз- ммирующий вход PC 11, а импульсы другой полярности - на .вычитающий вход PC 11,

8последнем в цифровом виде накапливается информация о количестве поступивших импульсов, которая в втором ЦАП 13 преобразуется в аналоговую форму (фиг, 2в), Это напряженке ступенчатой формы с помощью первого управляемого аттенюатора 14 изменяется по величине так, чтобы после второго сумматора 5 формировалось монотонное линейно изменяющееся напряжение (фиг„ 2г )., Это напряжение поступает на ключ 16, который открьша- ется генератором 20 на время анали- за Т. Интервал анализа определяется постоянной времени фильтра нижних частот или временем интегрирования интегратора в ФД 1,

Для сохранения монотонности напряжения (фиг, 2г) коэффициент передачи первого управляемого аттенюатора 14 должен устанавливаться пропорционально амплитуде биений. При этом независимо от величины частотной расстройки в конце интервала анализа Т на выходе ключа 16 - сигнал одинакового уровня. На этот уровень и настроен пороговый блок 9, После срабатывания последнего его выходное напряжение (фиг, 2д) изменяется обратно пропор-. ционально усредненной амплитуде биений во втором управляемом аттенюаторе 15, Затем это напряжение, величина которого пропорциональна начальной частотной расстройке, запоминает- ся в запоминающем блоке 17,

Далее аналоговое напряжение пе- . реводится в цифровую форму с помощью аналого-цифрового преобразователя 18 и накапливается в накопителе 19, Выходной код последнего содержит информацию о всех изменениях частотной расстройки, происходящих с момента включения устройства синхронизации. С помощью первого ЦАП 12 цифровой код накопителя 19 преобразуется в аналоговое напряжение, которое суммируется в первом сумматоре 4 с напряжением ошибки ФАЛ и управляет частотой управляемого генератора 6,

Работа ключа 16, запоминающего блока 17 синхронизируется генератором 20, который формирует стробиру- ющий импульс (фиг, 2е) длительностью Т и импульс фиксации запоминающего блока 17 (фиг. 2ж) длительностью f которая выбирается из условия вьтол- нения всех операций, связанных с перестройкой частоты управляемого генератора 6. Генератор 20 работает в ждущем режиме и запускается от измерителя 21, которьй представляет собой фиксатор амплитуды с соответствующим нормированием выходного напряжения (фиг. 2з). Так как пороговый блок запускается только при наличии биений, то и запуск генератора 20 происходит, в основном, при наличии частотной расстройки,

Для повышения точности установки частоты управляемого генератора 6 при действии помех коэффициент передачи второго управляемого аттенюатора 15 устанавливается напряжением с усредняющего блока 22, который вырабатьгоает напряжение, среднее за период анализа Т, чем и обеспечивается .более точное соответствие между частотной расстройкой и напряжением, его устраняющимо

I . . ..: ,

Формула изобретения

Устройство.синхронизации, содержащее последовательно соединенные накопитель, первый цифроаналоговый преобразователь, первый сумматор, управляемый генератор, фазовый де0

5

0

5

0

5

0

5

тектор, усилитель постоянного тока и пропорционально-интегрирующий фильтр, выход которого подсоединен к второму входу первого сумматора, последовательно соединенные формирователь сигналов счета, реверсивный счетчик и второй цифроаналоговый преобразователь, а также дифференцирующий блок и второй сумматор, входы которых подключены к выходу фазового детектора, аналого-цифровой преобразователь и генератор импульсов, причем второй вход фазового детектора является входом устройства, от личающееся тем, что, с целью повьш1ения быстродействия, введены последовательно соединенные двусторонний симметричный снизу ограничитель, измеритель апплитуды и первый управляемый аттенюатор, выход которого подсоединен к второму входу второго сумматора, последовательно соединенные усредняющий блок, второй управляемый аттенюатор и запоминающий блок, выход которого через аналого-цифровой преобразователь подсоединен к входу накопителя, последовательно соединенные ключ и пороговый блок, выход которого подсоединен к информационному входу второго управляемого аттенюатора, при этом выход измерителя амплитуды подсоединен к входам усредняющего блока и генератора импульсов, первый и второй выходы которого подсоединены соответственно к управляющим входак запоминающего блока и ключа, информационный вход которого подключен к выходу второго сумматора, вход и выход двустороннего симметричного снизу ограничителя подключены соответственно к выходу дифференцирукяцего блока и входу формирователя сигналов счета,- а выход второго цифроаналого- вого преобразователя подсоединен к информационному входу первого управляемого аттенюатора.

а б

л

А

А

X

/

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство фазовой автоподстройки частоты | 1990 |

|

SU1753592A1 |

| СИНТЕЗАТОР ЧАСТОТ | 2011 |

|

RU2477920C1 |

| Устройство синхронизации | 1985 |

|

SU1327287A1 |

| Устройство частотно-фазовой автоподстройки частоты | 1981 |

|

SU1243089A1 |

| Следящий фильтр для обработки непрерывного сигнала с частотной модуляцией | 1984 |

|

SU1218358A1 |

| Следящий фильтр-демодулятор | 1982 |

|

SU1095358A1 |

| Преобразователь отношения двух переменных напряжений в сдвиг фаз | 1976 |

|

SU653570A1 |

| Устройство синхронизации | 1984 |

|

SU1233292A1 |

| Устройство фазовой автоподстройки частоты | 1985 |

|

SU1290519A1 |

| Программный генератор | 1982 |

|

SU1062858A2 |

Изобретение относится к электросвязи. Цель изобретения - увеличение быстродействия. Устройство содержит фазовый детектор 1, усилитель 2 постоянного тока, пропорционально-интегрирующий фильтр 3, сумматоры 4 и 5, управляемый генератор 6, дифференцирующий блок 7, ограничитель 8, пороговый блок 9, формирователь 10 сигналов счета, реверсивный счетчик 11, ЦАП 12 и 13, управляемые аттенюаторы 14 и 15, ключ 16, запоминающий блок 17, АЦП 18, накопитель 19, генератор 20 импульсов, измеритель 21 амплитуды и усредняющий блок 22. Цель достигается за счет обеспечения более точного соответствия между частотной расстройкой и напряжением, его устраняющим. 2 ил.

ITv

Фиг.2

| Зайцев Г.Во, Стеклов ВоК | |||

| Комбинированные следящие системы.- Киев: Техника, 1978, с | |||

| Железнодорожный снегоочиститель на глубину до трех сажен | 1920 |

|

SU263A1 |

| Устройство синхронизации | 1985 |

|

SU1327287A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-08-07—Публикация

1987-11-06—Подача