СП

о

Юо

| название | год | авторы | номер документа |

|---|---|---|---|

| Счетный элемент с контролем | 1988 |

|

SU1569974A1 |

| Устройство для контроля последовательности импульсов | 1990 |

|

SU1791957A1 |

| Устройство тактовой синхронизации | 1988 |

|

SU1499456A1 |

| Селектор импульсов по длительности | 1983 |

|

SU1150746A1 |

| Устройство для допускового контроля длительности последовательности временных интервалов | 1988 |

|

SU1647508A1 |

| Устройство для контроля серий импульсов | 1989 |

|

SU1676076A1 |

| Устройство для обнаружения потери импульса | 1987 |

|

SU1525888A1 |

| Устройство для контроля двух импульсных последовательностей | 1988 |

|

SU1569834A1 |

| УСТРОЙСТВО ВВОДА-ВЫВОДА ИНФОРМАЦИИ ДЛЯ СИСТЕМЫ ЦИФРОВОГО УПРАВЛЕНИЯ | 1993 |

|

RU2042183C1 |

| МОДУЛЬ СИСТЕМНОГО КОНТРОЛЯ | 2003 |

|

RU2265240C2 |

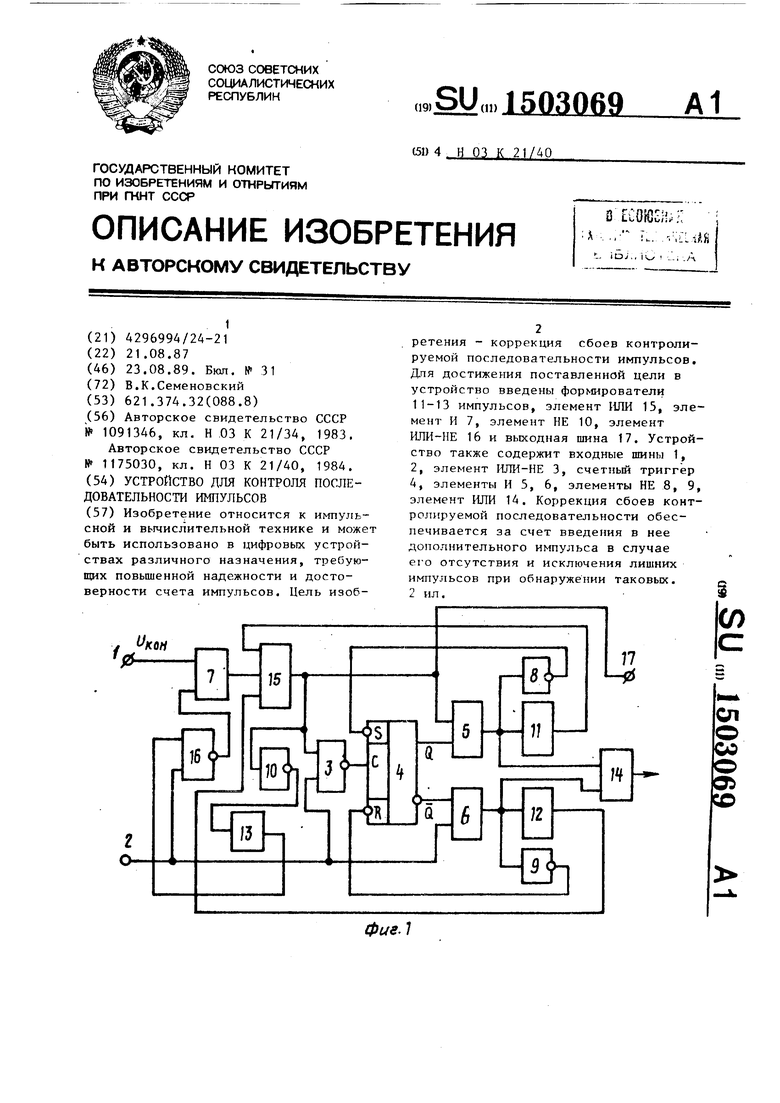

Изобретение относится к импульсной и вычислительной технике и может быть использовано в цифровых устройствах различного назначения, требующих повышенной надежности и достоверности счета импульсов. Цель изобретения - коррекция сбоев контролируемой последовательности импульсов. Для достижения поставленной цели в устройство введены формирователи 11 - 13 импульсов, элемент ИЛИ 15, элемент И 7, элемент НЕ 10, элемент ИЛИ-НЕ 16 и выходная шина 17. Устройство также содержит входные шины 1,2, элемент ИЛИ-НЕ 3, счетный триггер 4, элементы И 5,6, элементы НЕ 8,9, элемент ИЛИ 14. Коррекция сбоев контролируемой последовательности обеспечивается за счет введения в нее дополнительного импульса в случае его отсутствия и исключения лишних импульсов при обнаружении таковых. 2 ил.

фиеЛ

31503

Изобретение относится к импульсной и вычислительной технике и может быть использовано в цифровых устройствах различного назначения, требу- ющих обеспечения повышенной надежности и достоверности счета импульсов.

Целью изобретения является коррекция сбоев контролируемой последовательности импульсов.

Поставленная цель достигается за счет выделения новых конструктивных признаков, обеспечивающих введение в контролируемую последовательность дополнительного импульса в случае обнаружения отсутствия контролируемого импульса и исключение лишних импульсов, в случае их обнаружения.

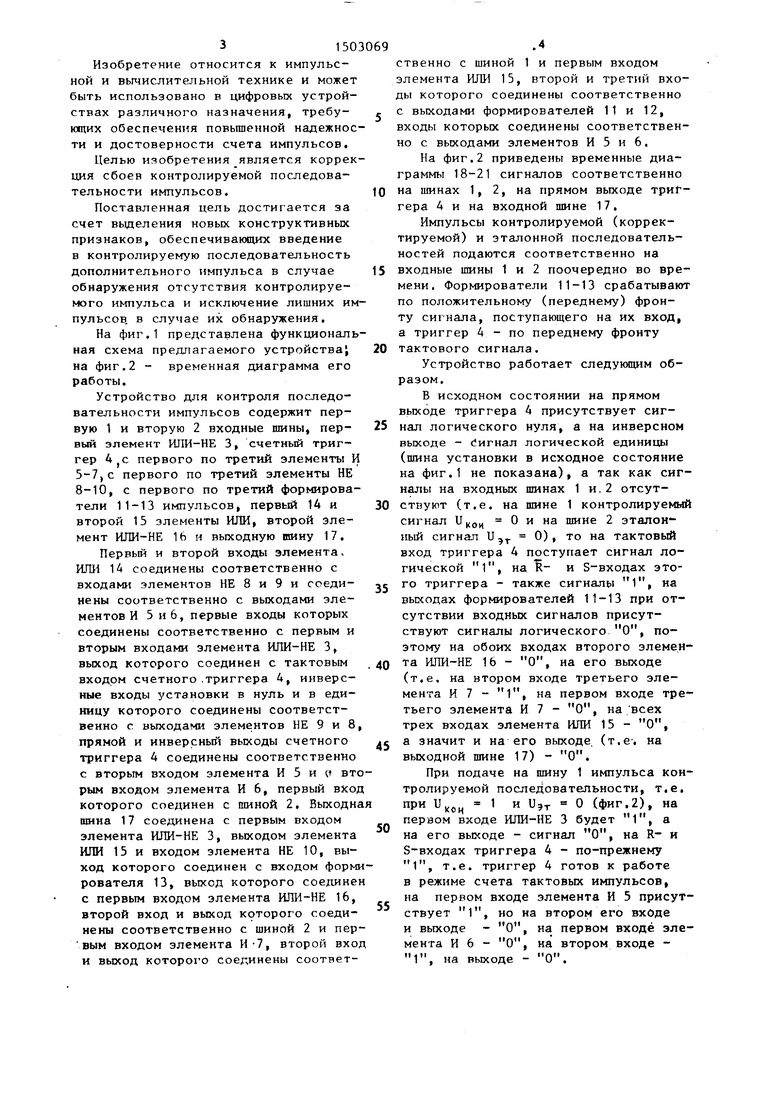

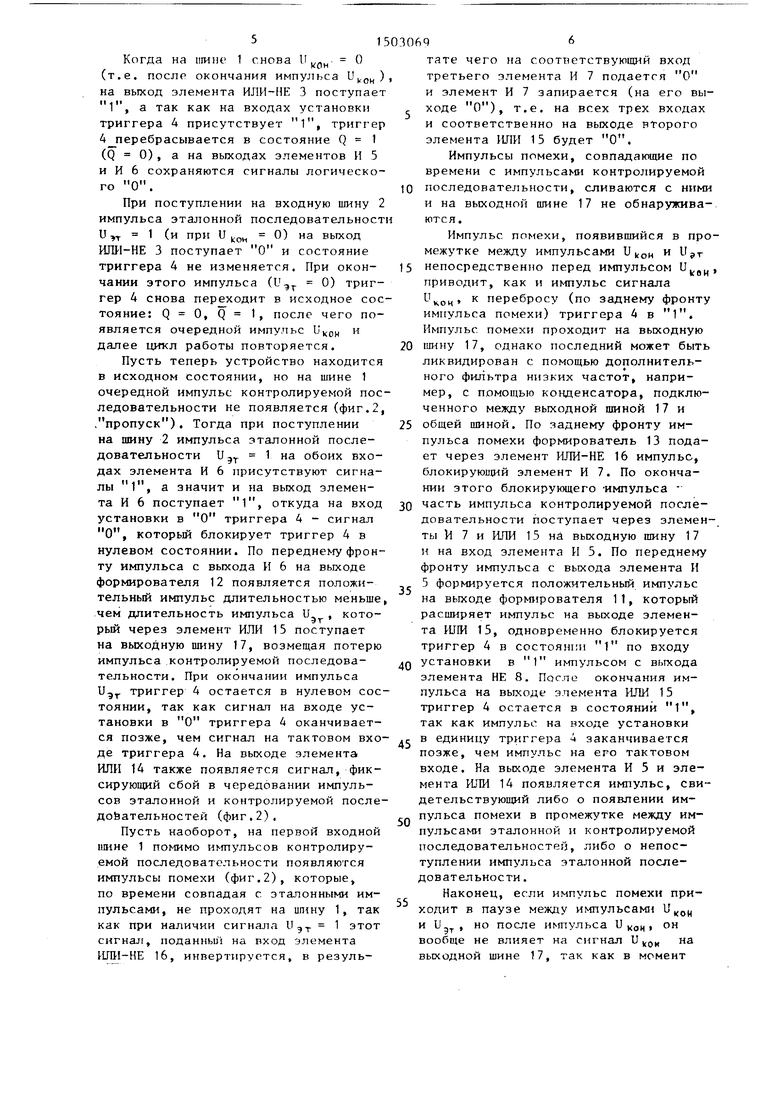

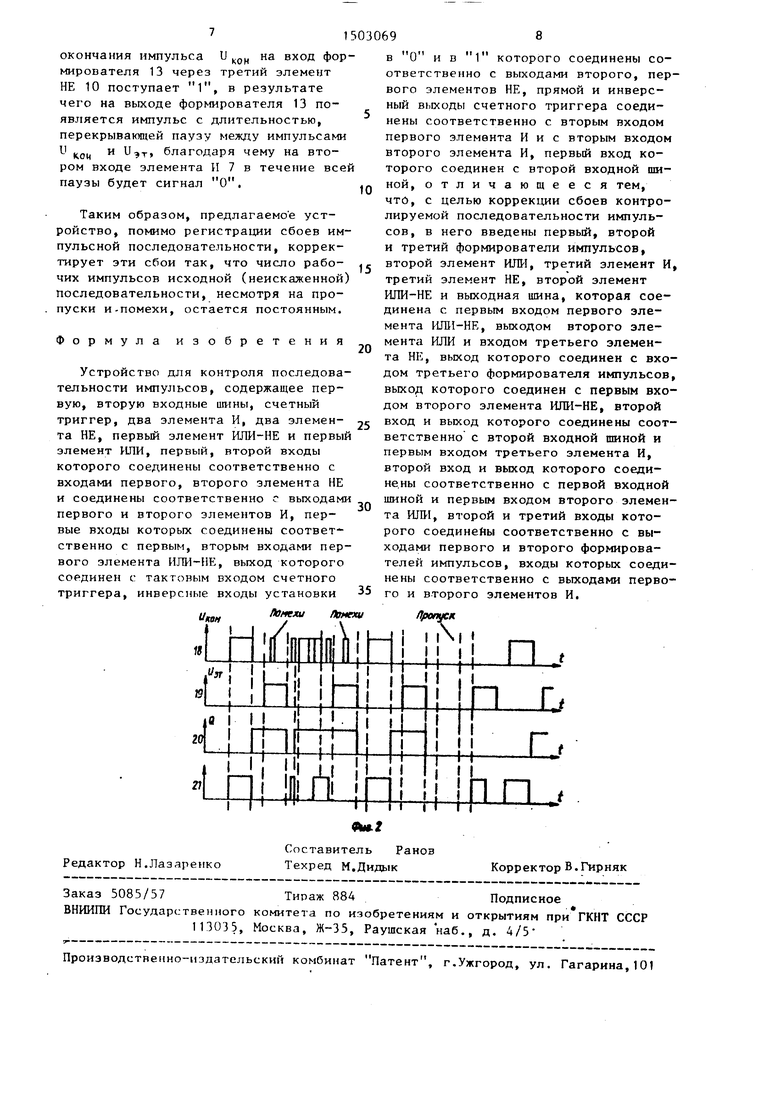

На фиг.1 представлена функциональная схема предлагаемого устройства , на фиг.2 - временная диаграмма его работы.

Устройство для контроля последовательности импульсов содержит первую 1 и вторую 2 входные шины, пер- вый элемент ИЛИ-НЕ 3, счетный триггер 4|С первого по третий элементы И 5-7,с первого по третий элементы НЕ 8-10, с первого по третий формирователи 11-13 импульсов, первый 1А и второй 15 элементы ИЛИ, второй элемент ИЛИ-НЕ 16 и выходную шину 17. Первый и второй входы элемента ИЛИ 14 соединены соответственно с входами элементов НЕ 8 и 9 и соеди- йены соответственно с выходами элементов И 5 и 6, первые входы которых соединены соответственно с первым и вторым входами элемента ИЛИ-НЕ 3, выход которого соединен с тактовым входом счетного .триггера 4, инверсные входы установки в нуль и в единицу которого соединены соответственно с выходами элементов НЕ 9 и 8, прямой и инверсный выходы счетного триггера 4 соединены соответственно с вторым входом элемента И 5 и о вторым входом элемента И 6, первый вход которого соединен с шиной 2. Выходна ошна 17 соединена с первым входом элемента ИЛИ-НЕ 3, выходом элемента ИЛИ 15 и входом элемента НЕ 10, выход которого соединен с входом формирователя 13, выход которого соединен с первым входом элемента ИЛИ-НЕ 16, второй вход и выход которого соединены соответственно с шиной 2 и пер- вым входом элемента И-7, второй вход и выход которого соединены соответ

0

5

0

5 0 е О с

0

ственно с шиной 1 и первым входом элемента ИЛИ 15, второй и третий входы которого соединены соответственно с выходами формирователей 11 и 12, входы которых соединены соответственно с выходами элементов И 5 и 6.

На фиг.2 приведены временные диаграммы 18-21 сигналов соответственно на шинах 1, 2, на прямом выходе триггера 4 и на входной шине 17.

Импульсы контролируемой (корректируемой) и эталонной последовательностей подаются соответственно на входные шины 1 и 2 поочередно во времени. Формирователи 11-13 срабатывают по положительному (переднему) фронту сигнала, поступающего на их вход, а триггер 4 - по переднему фронту тактового сигнала.

Устройство работает следующим образом.

В исходном состоянии на прямом выходе триггера 4 присутствует сигнал логического нуля, а на инверсном выходе - Сигнал логической единицы (шина установки в исходное состояние на фиг.1 не показана), а так как сигналы на входных шинах 1 и.2 отсутствуют (т.е. на шине 1 контролируемый сигнал О и на шине 2 эталонный сигнал и,. 0), то на тактовый вход триггера 4 поступает сигнал ло гической 1, на R- и S-входах этого триггера - также сигналы 1, на выходах формирователей 11-13 при отсутствии входных сигналов присутствуют сигналы логического О, поэтому на обоих входах второго элемента ИЛИ-НЕ 16 - О, на его выходе (т.е. на втором входе третьего элемента И 7 - 1, на первом входе третьего элемента И 7 - О, на всех трех входах элемента ИЛИ 15 - О, а значит и на его выходе, (т,е-, на выходной шине 17) - О.

При подаче на шину 1 импульса контролируемой последовательности, т.е.

при и

кои

1 и О (фиг.2), на

5

первом входе ИЛИ-НЕ 3 будет 1, а на его выходе - сигнал О, на R- и S-входах триггера 4 - по-прежнему 1, т.е. триггер 4 готов к работе в режиме счета тактовьпс импульсов, на первом входе элемента И 5 присутствует 1, но на втором его входе и выходе - О, на первом входе элемента И 6 - О, на втором входе - 1, на выходе - О.

.он О

Когда на шине 1 снова

(т.е. после окончания импульса и,,) на выход элемента ИЛИ-ИЕ 3 поступает 1, а так как на входах установки триггера 4 присутствует 1, триггер 4 перебрасывается в состояние Q 1 (Q 0), а на выходах элементов И 5 и И 6 сохраняются сигналы логического О.

При поступлении на входную шину 2 импульса эталонной последовательност и ,T. 1 (и при и 0) на выход ИЛИ-НЕ 3 поступает О и состояние триггера 4 не изменяется. При окончании этого импульса (U, 0) триггер 4 снова переходит в исходное состояние: Q О, Q 1, после чего появляется очередной импульс Ь, и далее цикл работы повторяется.

Пусть теперь устройство находится в исходном состоянии, но на шине 1 очередной импульс контролируемой последовательности не появляется (фиг.2, .пропуск). Тогда при поступлении на шину 2 импульса эталонной последовательности и 5-р 1 на обоих входах элемента И 6 присутствуют сигналы 1, а значит и на выход элемента И 6 поступает 1, откуда на вход установки в О триггера 4 - сигнал О, который блокирует триггер 4 в нулевом состоянии. По переднему фронту импульса с выхода И 6 на выходе формирователя 12 появляется положительный импульс длительностью меньше чем длительность импульса U, который через элемент ИЛИ 15 поступает на выходную шину 17, возмещая потерю импульса контролируемой последовательности. При окончании импульса Ug триггер 4 остается в нулевом состоянии, так как сигнал на входе установки в О триггера 4 оканчивается позже, чем сигнал на тактовом входе триггера 4. На выходе элемента ИЛИ 14 также появляется сигнал, фиксирующий сбой в чередовании импульсов эталонной и контролируемой последовательностей (фиг,2).

Пусть наоборот, на первой входной 1цине 1 помимо иьтульсов контролируемой последовательности появляются импульсы помехи (фиг.2), которые, по времени совпадая с эталонными импульсами, не проходят на итну 1, так как при наличии сигнала 11 1 этот сигнал, поданньи на вход элемента ШТИ-НЕ 16, инвертируется, в резуль

тате чего на соответствующий вход третьего элемента И 7 подается О и элемент И 7 запирается (на его выходе О), т.е. на всех трех входах и соответственно на выходе второго элемента ИЛИ 15 будет О.

Импульсы помехи, совпадающие по времени с импульсами контролируемой последовательности, сливаются с ними и на выходной шине 17 не обнаруживаются.

Импульс помехи, появившийся в промежутке между импульсами UKQH и

15 непосредственно перед и myльco U приводит, как и импульс сигнала

it

и

коч

к перебросу (по заднему фронту

импульса помехи) триггера 4 в 1. Импульс помехи проходит на выходную

0

0

5

0

5

0

5

шину 17, однако последний может быть ликвидирован с помощью дополнитель«

ного фильтра низких частот, например, с помощью конденсатора, подключенного между выходной шиной 17 и 5 общей шиной. По заднему фронту импульса помехи формирователь 13 подает через элемент ИЛИ-НЕ 16 импульс, блокирующий элемент И 7. По окончании этого блокирующего -импульса часть импульса контролируемой последовательности поступает через элементы И 7 и ИЛИ 15 на выходную шину 17 и на вход элемента И 5. По переднему фронту импульса с выхода элемента И 5 формируется положительный импульс на выходе формирователя 11, который расширяет импульс на вькоде элемента ИЛИ 15, одновременно блокируется триггер 4 в состоянии 1 по входу установки в 1 импульсом с выхода элемента НЕ 8. После окончания импульса на вьгходе элемента ИЛИ 15 триггер 4 остается в состоянии 1, так как импульс на входе установки в единицу триггера 4 заканчивается позже, чем импульс на его тактовом входе. На выходе элемента И 5 и элемента ИЛИ 14 появляется импульс, свидетельствующий либо о появлении импульса помехи в промежутке между импульсами эталонной и контролируемой последовательностей, либо о непоступлении импульса эталонной последовательности .

Наконец, если импульс помехи приходит в паузе между импульсами н и Ug , но после и myльca U кон вообще не влияет на сигнал U «Q на выходной шине 17, так как в момент

окончания импульса U . на вход формирователя 13 через третий элемент НЕ 10 поступает 1, в результате чего на выходе формирователя 13 появляется импульс с длительностью, перекрывающей паузу между импульсами и д и и,-г, благодаря чему на втором входе элемента И 7 в течение всей паузы будет сигнал О,

15030698

в О и в 1 которого соединены соответственно с выходами второго, первого элементов НЕ, прямой и инверсный выходы счетного триггера соединены соответственно с вторым входом первого элемента И и с вторым входом второго элемента И, первый вход которого соединен с второй входной шиной, отличающееся тем.

10

что, с целью коррекции сбоев контролируемой последовательности импульсов, в него введены первый, второй и третий формирователи импульсов, второй элемент ИЛИ, третий элемент И, третий элемент НЕ, второй элемент ИЛИ-НЕ и выходная шина, которая соединена с первым входом первого элемента ИЛ11-НЕ, выходом второго элемента ИЛИ и входом третьего элемента НЕ, выход которого соединен с входом третьего формирователя импульсов, выход которого соединен с первым входом второго элемента ИЛИ-НЕ, второй вход и выход которого соединены соответственно с второй входной шиной и первым входом третьего элемента И, второй вход и выход которого соеди- не.ны соответственно с первой входной шиной и первым входом второго элемента ИЛИ, второй и третий входы которого соединены соответственно с выходами первого и второго формирова- телеи импульсов, входы которых соединены соответственно с выходами первого и второго элементов И.

Таким образом, предлагаемое устройство, помимо регистрации сбоев импульсной последовательности, корректирует эти сбои так, что число рабочих импульсов исходной (неискаженной) последовательности, несмотря на пропуски и-помехи, остается постоянным.

Формула изобретения

Устройство для контроля последовательности импульсов, содержащее первую, вторую входные шины, счетный триггер, два элемента И, два элемен- та НЕ, первый элемент ИЛИ-НЕ и первый элемент ИЛИ, первый, второй входы которого соединены соответственно с входами первого, второго элемента НЕ и соединены соответственно с выходами первого и второго элементов И, первые входы которых соединены соответственно с первым, вторым входами первого элемента НЛИ-НЕ, выход которого соединен с тактовым входом счетного

триггера, инверсные входы установки

в О и в 1 которого соединены соответственно с выходами второго, первого элементов НЕ, прямой и инверсный выходы счетного триггера соединены соответственно с вторым входом первого элемента И и с вторым входом второго элемента И, первый вход которого соединен с второй входной шиной, отличающееся тем.

что, с целью коррекции сбоев контролируемой последовательности импульсов, в него введены первый, второй и третий формирователи импульсов, второй элемент ИЛИ, третий элемент И, третий элемент НЕ, второй элемент ИЛИ-НЕ и выходная шина, которая соединена с первым входом первого элемента ИЛ11-НЕ, выходом второго элемента ИЛИ и входом третьего элемента НЕ, выход которого соединен с входом третьего формирователя импульсов, выход которого соединен с первым входом второго элемента ИЛИ-НЕ, второй вход и выход которого соединены соответственно с второй входной шиной и первым входом третьего элемента И, второй вход и выход которого соеди- не.ны соответственно с первой входной шиной и первым входом второго элемента ИЛИ, второй и третий входы которого соединены соответственно с выходами первого и второго формирова- телеи импульсов, входы которых соединены соответственно с выходами первого и второго элементов И.

| Устройство для контроля последовательности импульсов | 1983 |

|

SU1091346A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для контроля последовательности импульсов | 1984 |

|

SU1175030A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-08-23—Публикация

1987-08-21—Подача