о

X о с

ч

о

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля серий импульсов | 1988 |

|

SU1649643A1 |

| Устройство для задержки импульсов | 1979 |

|

SU822331A1 |

| Устройство для контроля серий импульсов | 1987 |

|

SU1473077A1 |

| Устройство для контроля серий импульсов | 1987 |

|

SU1534751A1 |

| Устройство для передачи информации псевдослучайными сигналами | 1986 |

|

SU1392625A1 |

| Устройство для контроля передачи информации | 1984 |

|

SU1251083A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1310755A1 |

| Контролируемое устройство дешифрации | 1986 |

|

SU1410034A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1711167A1 |

Изобретение относится к импульсной технике и может найти применение при проектировании аппаратуры автоматического контроля дискретн ых устройств, в частности при проектировании устройств для обнаружения сбоев при испытаниях электронных блоков. Целью изобретения является повышение достоверности контроля серий импульсов. Устройство включает в свой состав регистр 1 памяти, выполненный на счетных триггерах 2, логические элементы ИЛИ 4, ЗАПРЕТ 6, И 9, блок 10 формирования импульсов по задним фронтам сигналов, фор- мирователь 5 импульсов, входные информационные шины 3 и шину 8 обнуления, а также выходную шину 7. При использовании изобретения в устройствах для контроля серий импульсов обеспечивается возможность проведения более точного контроля за счет обнаружения ложных импульсов внутри контролируемых серий. Причем обнаружение ложных импульсов происходит как при возникновении одиночного ложного импульса, так и при одновременном возникновении на соседних шинах ложного и рабочего импульсов. 2 ил. (/ С

Фиг 7

Изобретение относится к импульсное технике и может найти применение при проектировании аппаратуры автоматического контроля дискретных устройств, в частности при проектировании устройств для обнаружения сбоев при испытаниях электронных блоков.

Целью изобретения является повышение достоверности контроля серий импульсов.

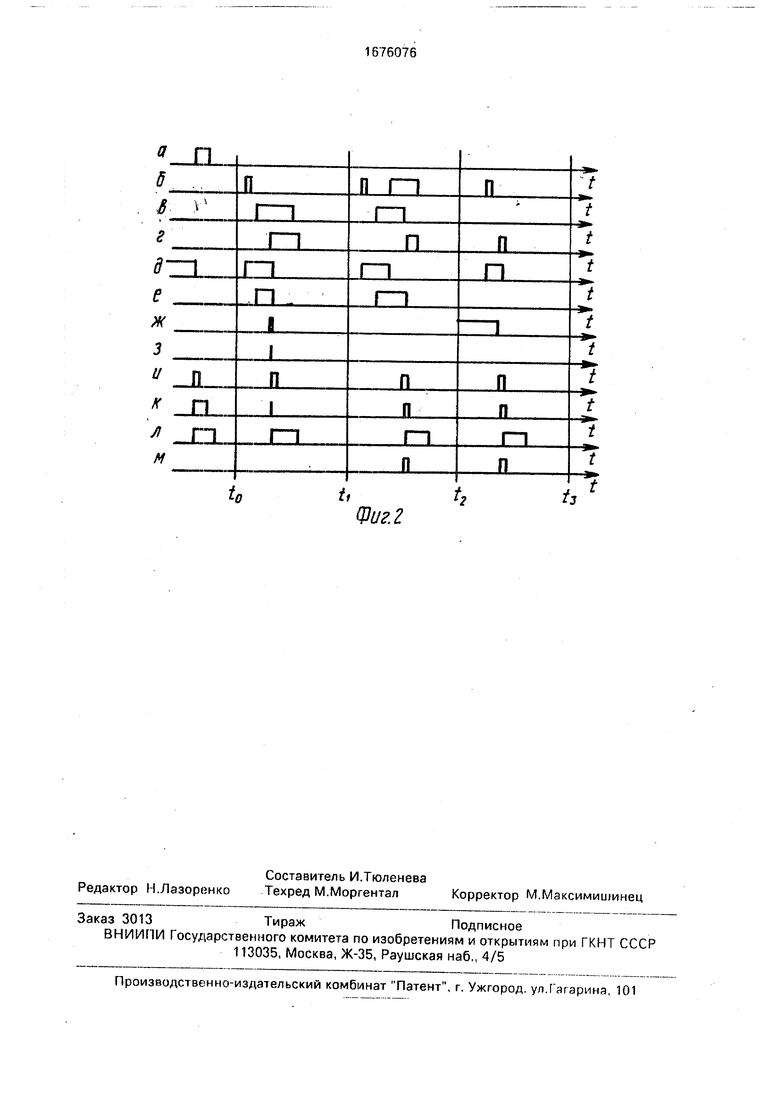

На фиг. 1 представлена функциональная схема устройства; на фиг. 2 - временные диаграммы его работы.

Устройстве для контроля серий импульсов содержит регистр 1 памяти, состоящий из триггеров 2.1-2.N, тактовые входы которых объединены с соответствующими вход- ными шинами 3 устройства, а входы обнуления объединены и подключены к выходу элемента ИЛИ 4 и через формирова- тель 5 импульсов к инверсному входу элемента ЗАПРЕТ 6. Выход элемента ЗАПРЕТ 6 соединен с выходной шиной 7 и первым входом элемента ИЛИ 4, второй вход которого объединен с шиной 8 обнуле- ния устройства, а третий его вход подключен к выходу элемента И 9. Входы элемента 1/1 попарно объединены с одноименными входами блока 10 формирования импульсов по задним фронтам сигналов и подключены к соответствующим выходам регистра 1 памяти, а прямой вход элемента ЗАПРЕТ 6 соединен с выходом блока 10 формирования импульсов по задним фронтам сигналов.

Блок 10 формирования импульсов по задним фронтам сигналов в общем случае представляет собой набор формирователей импульсов по задним фронтам входного сигнала, выходы которых объединены через элемент ИЛИ. Причем каждый из формирователей импульсов по заднему фронту входного сигнала может, например, содержать элемент И, входы которого, соответственно, через инвертор и элемент задержки соеди- нены с входной шиной формирователя.

Устройство работает следующим образом.

После включения питания, перед началом работы по шине 8 подается обнуляю- щий сигнал (фиг. 2а), приводящий устройство в исходное состояние, По окончании обнуляющего сигнала на всех элементах схемы и, следовательно, на выходной шине 7 появляется нулевой уровень напря- жения. Импульсы серий на входных шинах 3 устройства при этом отсутствуют.

Импульсы контролируемых серий, поступающие на входные шины 3 устройства (фиг. 26, в, г)устанавливают счетные триггеры регистра 1 в единичное состояние (фиг. 2д. е, ж).

С выходов счетных триггеров 2-1...2-N регистра 1 сигналы поступают на входы элемента И 9. В момент времени, когда на всех входах элемента И 9 установятся сигналы единичного уровня, на его выходе появится сигнал ,фиг. 2з, поступающий на вход элемента ИЛИ 4, С выхода элемента ИЛИ 4 этот сигнал поступает на вход формирователя 5 импульсов и на установочные входы счетных триггеров 2-1...2-N. На выходе формирователя 5 формируется сигнал (фиг. 2л), поступающий на инверсный вход элемента ЗАПРЕТ 6. Этот сигнал запрещает прохождение импульсов единичного уровня через элемент ЗАПРЕТ 6 на время действия сигнала. Одновременно с этим триггеры 2-1 ...2- N регистра 1 возвращаются в исходное нулевое состояние (фиг. 2д, е, ж). В связи с этим на входах блока 10 изменяется уровень сигналов (из единицы в ноль) и на его выходе формируется импульс единичного уровня (фиг. 2и), который поступает на прямой вход элемента ЗАПРЕТ 6. Ввиду того, что в это время на инверсном входе элемента ЗАПРЕТ 6 находится сигнал единичного уровня, на выходе элемента ЗАПРЕТ 6 и, следовательно, на выходной шине 7 устройства будет оставаться сигнал нулевого уровня (фиг. 2м), говорящий о нормальной последовательности импульсов в контролируемой серии.

В случае возникновения ложных импульсов внутри контролируемой серии (фиг, 2, интервал времени ti -tzj устройство работает следующим образом.

На одной из входных шин 3, где уже зафиксирован счетным триггером контролируемый импульс, возникает ложный импульс (фиг. 26), который устанавливает счетный триггер в исходное состояние (фиг. 2д). В результате этого на одном из входов блока 10 выделения заднего фронта импульсов происходит изменение уровня сигнала с единичного на нулевой. По этому перепаду на выходе блока 10 формируется единичный импульс (фиг. 2и), поступающий на вход элемента ЗАПРЕТ 6. Ввиду того, что на инверсном входе элемента ЗАПРЕТ 6 находится сигнал нулевого уровня, импульс с выхода блока 10 выделения заднего фронта импульсов через элемент ЗАПРЕТ 6 проходит на выходную шину 7 устройства (фиг. 2м), сигнализируя о сбойной ситуации. Одновременно этот сигнал через элемент ИЛИ 4 поступает на установочные входы счетных триггеров 2 регистра 1 и на запуск формирователя 5 импульсов. На выходе формирователя 5 формируется импульс (фиг. 2л),

который запрещает прохождение через элемент ЗАПРЕТ 6 сигналов единичного уровня. После возвращения счетных триггеров в исходное состояние устройство вновь готово к проведению контроля.

Работа устройства при исходном ненулевом состоянии триггеров 2 регистра 1 происходит следующим образом (интервал времени t2 - 13 на фиг. 2). Такой вариант возможен, если по одной из шин, например шине 3-N, к моменту времени t2 прошла помеха. В этом случае на выходе триггера 2-М появится единичный сигнал (фиг. 2ж), Такая же ситуация возможна, если по одной или нескольким шинам в предыдущем такте работы устройства не поступил импульс контролируемой серии.

Тогда первый же импульс из очередной контролируемой серии поступит на вход счетного триггера, который изменит свое состояние (фиг. 2ж), и по данному перепаду сигналов на выходе блока 10 формируется импульс (фиг. 2и), который через.элемент ЗАПРЕТ 6 поступает на выходную шину 7 устройства, сигнализируя о сбойной ситуа- ции. Дальнейшая работа устройства протекает аналогично алгоритму работы при возникновении ложного импульса.

Таким образом, использование предлагаемого устройства для контроля серий им- пульсов обеспечивает возможность проведения достоверного контроля за счет обнаружения ложных импульсов внутри контролируемых серий и пропажи импульсов контролируемой серии. Причем обнару- жение ложных импульсов устройством происходит как при возникновении отдельного ложного импульса, так и при одновременном возникновении на разных входных

шинах ложного и рабочего импульсов. Кроме того, после обнаружения сбойной ситу- ации устройство продолжает осуществлять контроль серии импульсов, приняв зз начало контролируемой серии очередной последующий импульс.

Отсутствие элементов формирования входных импульсов по длительности снимает ограничение на длительность и взаимное расположение во времени сигналов импульсных последовательностей.

Кроме того, возможен контроль устройством коротких помеховых импульсов, достаточных по длительности для срабатывания счетного триггера.

Формула изобретения

Устройство для контроля серий импульсов, содержащее регистр памяти, выполненный на триггерах, входы обнуления которых объединены между собой, формирователь импульсов, подключенный входом к выходу элемента ИЛИ, и элемент И. о т - личающееся тем, что, с целью повышения достоверности контроля серий, счетные входы триггеров регистра подключены к соответствующим входным шинам устройства, а выходы регистра - к попарно объединенным соответствующим входам элемента И и блока формирования импульсов по задним фронтам сигналов, соединенного выходом с прямым входом элемента ЗАПРЕТ, инверсный вход и выход которого подключены соответственно к выходу формирователя импульсов и первому входу элемента ИЛИ, подключенного своими вторым и третьим входами к обнуляющей шине устройства и выходу элемента И, а выходом - к объединенным входам обнуления триггеров регистра памяти.

Фиг. 2

| Устройство для контроля серий импульсов | 1985 |

|

SU1262709A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для контроля серий импульсов | 1986 |

|

SU1338035A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-09-07—Публикация

1989-04-28—Подача