Известные устройства для компенсации помех в ферротранзисториой ячейке двухтактного регистра сдвига с помощью дополнительных сердечников или дополнительных обмоток сложны по конструкции.

В предлагаемом устройстве для упрощения его схемы и снижения потребляемой мощности от источника тактовых импульсов эмиттер каждой ячейки соединен с базой транзистора следующей ячейки.

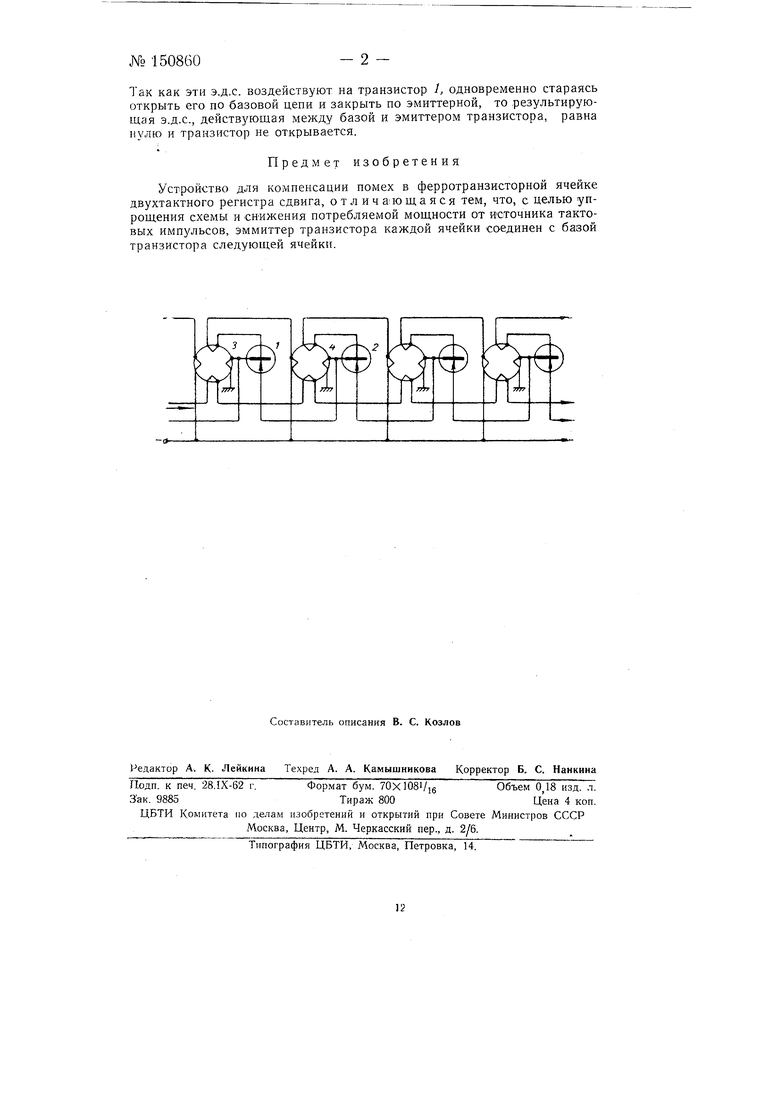

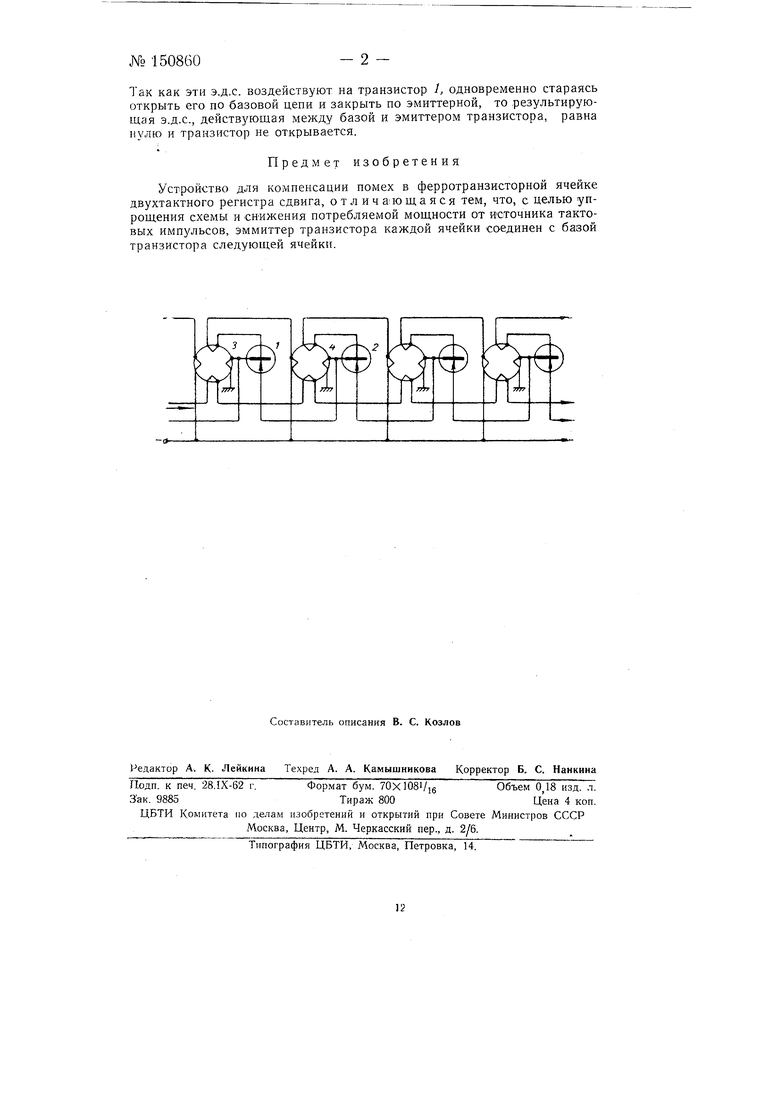

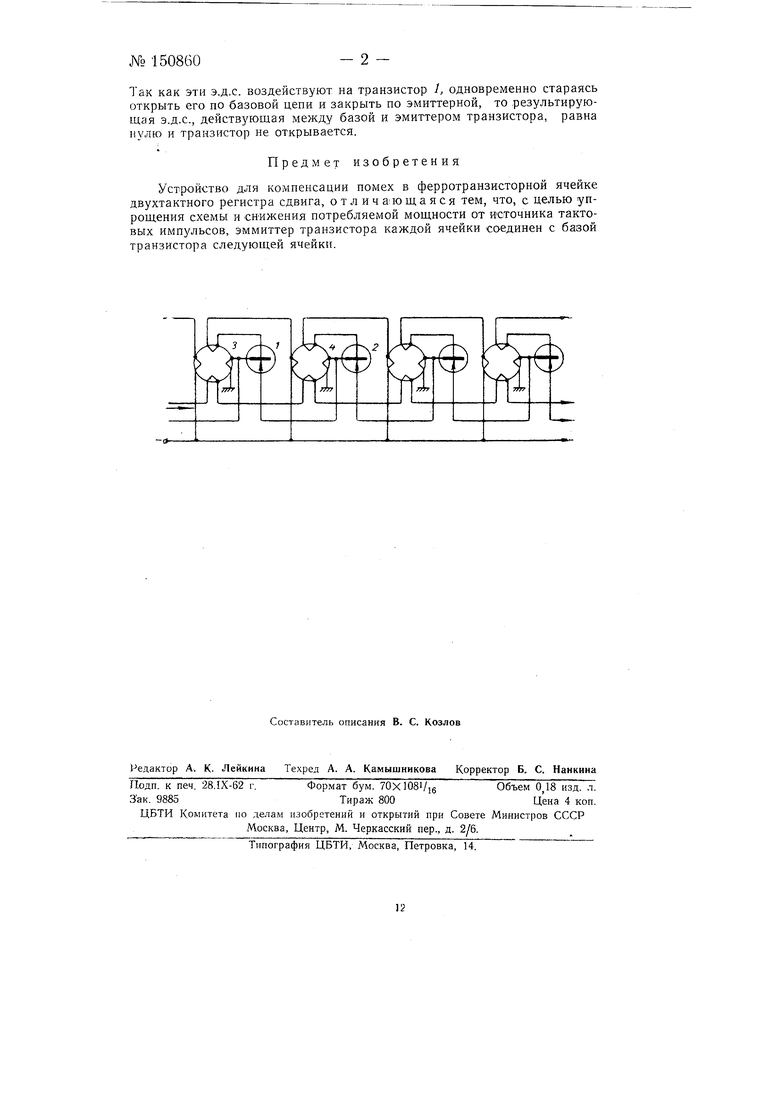

На чертеже приведена принципиальная схема описываемого устройства.

Схема устройства представляет собой двухтактный регистр сдвига па ферротранзисторных ячейках с двойной положительной обратной связью.

Положительная обратная связь образована подключением эмиттера транзистора / каждой ячейки к базе транзистора 2 следующей ячейки, что снижает потребляемую мощность и упрощает схему. Благодаря положительной обратной связи режим работы регистра не нарушается при последовательном включении обмоток списывания обоих тактов. Для получения преобладания ампервитков записи, как по величине, так и по времени, над ампервитками списывания в предлагаемо.м устройстве списывающий импульс тока имеет минимальную длительность порядка десятых долей микросекунды и амплитуду 200-300 лш-витков, необходимые лищь для открывания транзистора и запуска ячейки. Вследствие сильной положительной обратной связи со стороны списываемого и записываемого сердечников эти два процесса протекают самостоятельно до полного перемагпичивания обоих сердечников. При одновременном воздействии тока на соседние запоминающие трансформаторы 3 и 4 на их базовых обмотках возникают э.д.с. помехи отрицательной полярности.

Так как эти э.д.с. воздействуют на транзистор 1, одновременно стараясь открыть его по базовой цепи и закрыть по эмиттерной, то .результирующая Э.Д.С., действующая между базой и эмиттером транзистора, равна нулю и транзистор не открывается.

Предмет изобретения

Устройство для компенсации помех в ферротранзисторной ячейке двухтактного регистра сдвига, отлича ющаяся тем, что, с целью упрощения схемы и снижения потребляемой мощности от источника такто вых импульсов, эммиттер транзистора каждой ячейки соединен с базой транзистора следующей ячейки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Феррито-транзисторная ячейка двухтактного регистра сдвига | 1960 |

|

SU136762A1 |

| Логическое устройство для осуществления операции "запрета" на ферротранзисторных ячейках | 1961 |

|

SU150869A1 |

| Ферротранзисторная логическая схема "запрет" | 1959 |

|

SU130239A1 |

| Феррит-транзисторная ячейка | 1960 |

|

SU139480A1 |

| КОММУТАТОР ДЛЯ УПРАВЛЕНИЯ ШАГОВЫМ ДВИГАТЕЛЕМ | 1970 |

|

SU259986A1 |

| Двухфазный инвертор | 1978 |

|

SU817943A1 |

| УСТРОЙСТВО для УПРАВЛЕНИЯ АВТОНОМНЫМ ИНВЕРТОРОМ | 1968 |

|

SU221138A1 |

| ДВУХТАКТНЫЙ РАСПРЕДЕЛИТЕЛЬ | 1971 |

|

SU312372A1 |

| РЕГИСТР СДВИГА | 1973 |

|

SU364029A1 |

| ФОНд1иОйЕРТ11 | 1973 |

|

SU367512A1 |

Авторы

Даты

1962-01-01—Публикация

1961-05-23—Подача