Известны феррит-транзисториые ячейки, выполненные на двух последовательно включенных триодах, запоминающем трансформаторе и входном трансформаторе. Основной недостаток подобных устройств состоит в том, что мощность импульса списывания единицы должна превыщать мощность импульса записи единицы. Кроме того, известные ячейки обладают недостаточным быстродействием.

В описываемой ячейке для повыщения быстродействия и снижения мощности импульса списывания единицы обмотка возбуждения запоминающего трансформатора включена между эмиттером ключевого триода и базой основного триода.

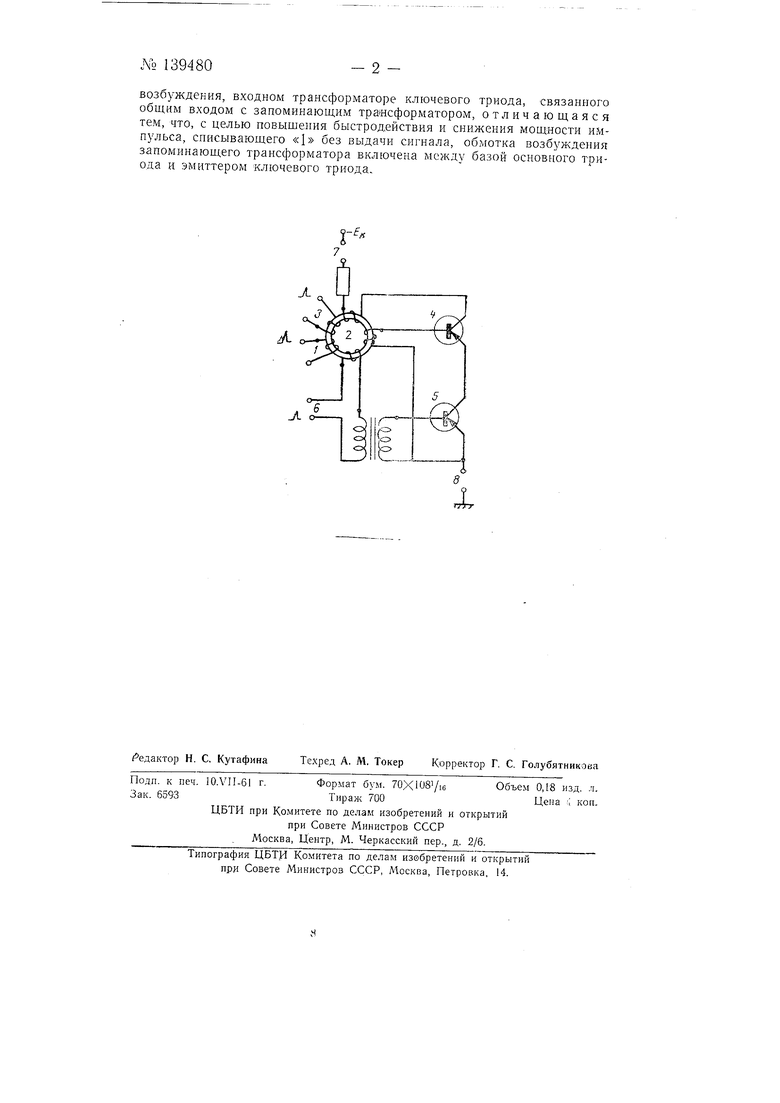

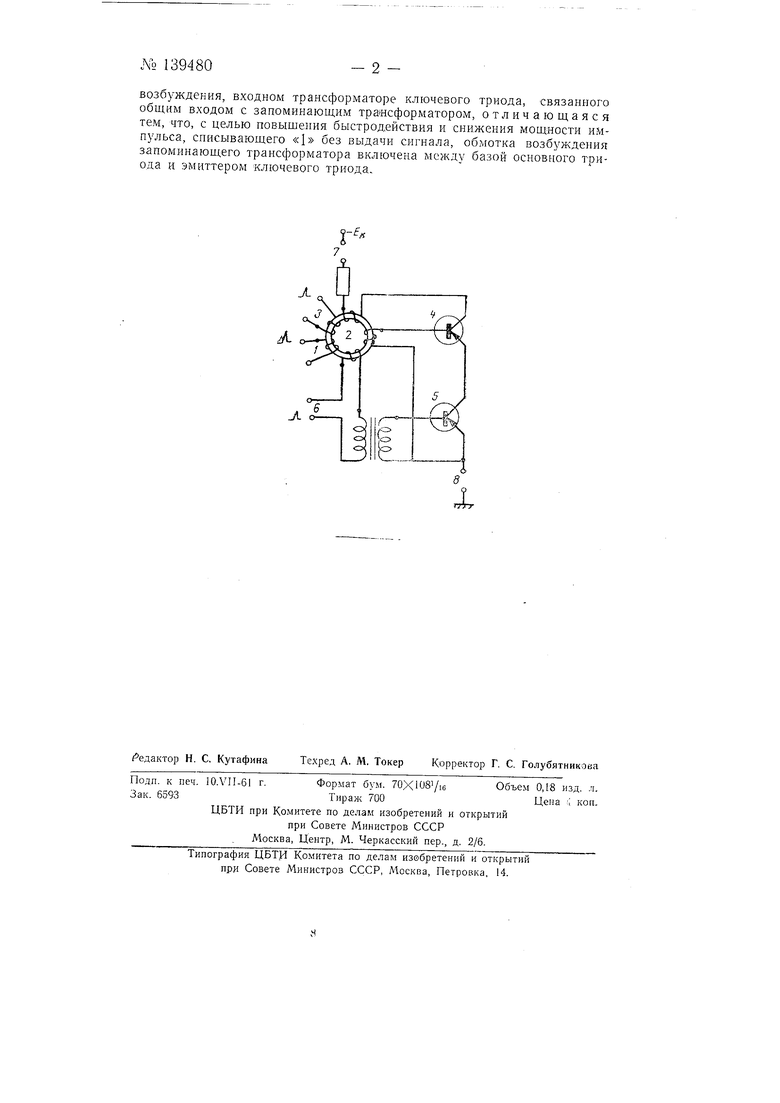

Принципиальная схема ячейки приведена на чертеже.

Запись единицы осуществляется по обмотке / запоминающего трансформатора 2. Импульсы «запрета поступают в обмотку 3 этого же трансформатора. При этом сигнал «заирета списывает единицу из сердечника трансформатора 2 без выдачи сигнала в нагрузку. В момент действия сигнала «запрета триод 4 не возбуждается, так как триод 5 закрыт. Это позволяет одновременно подавать импульсы «запрета иа обмотку 5 и импульсы списывания иа зажимы 6. Подобный режим работы повышает быстродействие устройства. Обмотки / и 5 могут быть выполнены одинаковыми, так как потребляемая мощность для записи единицы по обмотке / и ее списывания по обмотке 3 при данной схеме включения триодов 4 к 5 одинакова.

Выходные сигналы с ячейки снимаются с зажимов 7 т 8.

Предмет изобретения

Феррит-транзисторная ячейка, выполненная на двух последовательно включенных триодах, запоминающем трансформаторе, имеющем не менее трех управляющих обмоток, обмотку обратной связи и обмотку

возбуждения, входном трансформаторе ключевого триода, связанного общим входом с запоминающим трансформатором, отличающаяся тем, что, с целью повыщеиия быстродействия и снижения мощности импульса, списывающего «1 без выдачи сигнала, обмотка возбуждения запоминающего трансформатора включена между базой основного триода и эмиттером ключевого триода.

| название | год | авторы | номер документа |

|---|---|---|---|

| Феррито-транзисторная ячейка двухтактного регистра сдвига | 1960 |

|

SU136762A1 |

| УНИВЕРСАЛЬНАЯ ЦИФРОВАЯ УПРАВЛЯЮЩАЯ МАШИНА | 1965 |

|

SU170218A1 |

| Устройство для компенсации помех в ферротранзисторной ячейке двухтактного регистра сдвига | 1961 |

|

SU150860A1 |

| НАКАПЛИВАЮЩИЙ ДЕСЯТИЧНЫЙ СУММАТОР | 1966 |

|

SU224164A1 |

| УСТРОЙСТВО ЦИКЛИЧЕСКОЙ, СИНХРОННОЙ, с ВРЕМЕННЫМ | 1970 |

|

SU277009A1 |

| Ферротранзисторная логическая схема "запрет" | 1959 |

|

SU130239A1 |

| Логическое устройство для осуществления операции "запрета" на ферротранзисторных ячейках | 1961 |

|

SU150869A1 |

| РЕВЕРСИВНЫЙ ДВОИЧНЫЙ ФЕРРОТРАНЗИСТОРНЫЙСЧЕТЧИК | 1965 |

|

SU167372A1 |

| ПЕРЕКЛЮЧАТЕЛЬ ИМПУЛЬСОВ | 1973 |

|

SU362483A1 |

| ФОРМИРОВАТЕЛЬ ТОКА ЗАПРЕТА | 1969 |

|

SU233747A1 |

Авторы

Даты

1961-01-01—Публикация

1960-02-29—Подача