(Л

СП

00

со

СА

315I

гальванически развязанными и последовательно соединенными выходами. Выходные напряжения инверторных ячеек имеют паузы IT/B между полуволнами и последовательно сдвинуты между собой на фазовьй угол , Результирующее выходное напряжение преобразователя при этом имеет L-ступен- чатую форму (L - число ступеней на четверти периода частоты этого напряжения) , Блок управления содержит задающий генератор 7, подключенньй к распределителю 8 импульсов, делителю 9 частоты, распределителю 10 им- пульсов, делителю 11 частоты и фазосдвигающему узлу 12, Выходы распределителей 8, 10, 13 подключены к логическим узлам 15.1-15.6, Блок управления обеспечивает паузы между полуволнами в выходном напряжении каждой инверторной ячейки, равные ii /3+oi, а также паузы об в середипе каждой полуволны этих напряжений (ot - угол регулирования). Регулировочная характеристика при этом получается линейной, а качество выходного напряжения преобразователя остается высоким в широком диапазоне изменения этого напряжения. 2 з.п. ф-лы, 4 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь постоянного напряжения в квазисинусоидальное | 1982 |

|

SU1193760A1 |

| Способ преобразования постоянного напряжения в квазисинусоидальное ступенчатое | 1988 |

|

SU1737685A1 |

| Способ преобразования постоянного напряжения в регулируемое низкочастотное квазисинусоидальное напряжение | 1988 |

|

SU1599958A1 |

| СПОСОБ ПРЕОБРАЗОВАНИЯ ПОСТОЯННОГО НАПРЯЖЕНИЯ В ПЕРЕМЕННОЕ | 2008 |

|

RU2366068C1 |

| Преобразователь @ -фазного напряжения с промежуточным ВЧ-преобразователем | 1985 |

|

SU1394370A1 |

| Однофазный инвертор напряжения с многофазной широтно-импульсной модуляцией | 2023 |

|

RU2804997C1 |

| Преобразователь постоянного напряжения в квазисинусоидальное переменное | 1984 |

|

SU1365304A1 |

| Способ формирования квазисинусоидального переменного напряжения | 1987 |

|

SU1522368A1 |

| Способ преобразования постоянного напряжения в квазисинусоидальное переменное | 1987 |

|

SU1473052A1 |

| Устройство для управления преобразователем постоянного напряжения в трехфазное квазисинусоидальное | 1985 |

|

SU1415379A1 |

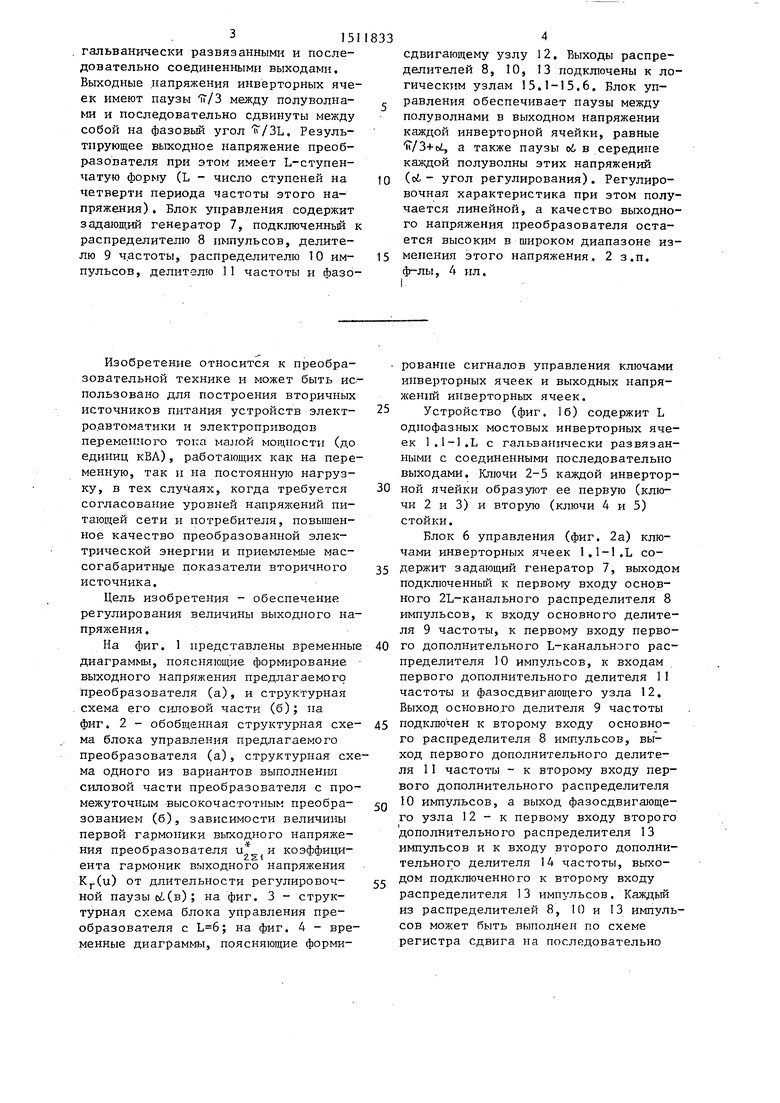

Изобретение относится к преобразовательной технике и может быть использовано для построения источников вторичного электропитания (ИВЭП) устройств электроавтоматики и электроприводов переменного тока. Цель изобретения - обеспечение регулирования величины выходного напряжения. Преобразователь постоянного напряжения в переменное многоступенчатой формы содержит L инверторных ячеек с гальванически развязанными и последовательно соединенными выходами. Выходные напряжения инверторных ячеек имеют паузы φ/3 между полуволнами и последовательно сдвинуты между собой на фазовый угол φ/3L. Результирующее выходное напряжение преобразователя при этом имеет L - ступенчатую форму (L - число ступеней на четверти периода частоты этого напряжения). Блок управления содержит задающий генератор 7, подключенный к распределителю 8 импульсов, делителю 9 частоты, распределителю 10 импульсов, делителю 11 частоты и фазосдвигающему узлу 12. Выходы распределителей 8, 10, 13 подключены к логическим узлам 15.1-15.6. Блок управления обеспечивает паузы между полуволнами в выходном напряжении каждой инверторной ячейки, равные φ/3+κ, а также паузы α в середине каждой полуволны этих напряжений (α - угол регулирования). Регулировочная характеристика при этом получается линейной, а качество выходного напряжения преобразователя остается высоким в широком диапазоне изменения этого напряжения. 2 з.п.ф-лы, 4 ил.

Изобретение относится к преобразовательной технике и может быть использовано для построения вторичных источников питания устройств электроавтоматики и электроприводов переменного тока малой мощности (до единиц кВА), работающих как на переменную, так и на постоянную нагрузку, в тех случаях, когда требуется согласование уровней напряжений питающей сети и потребителя, повышенное качество преобразованной электрической энергии и приемлемые мас- согабаритнце показатели вторичного источника.

Цель изобретения - обеспечение регулирования величины выходного напряжения .

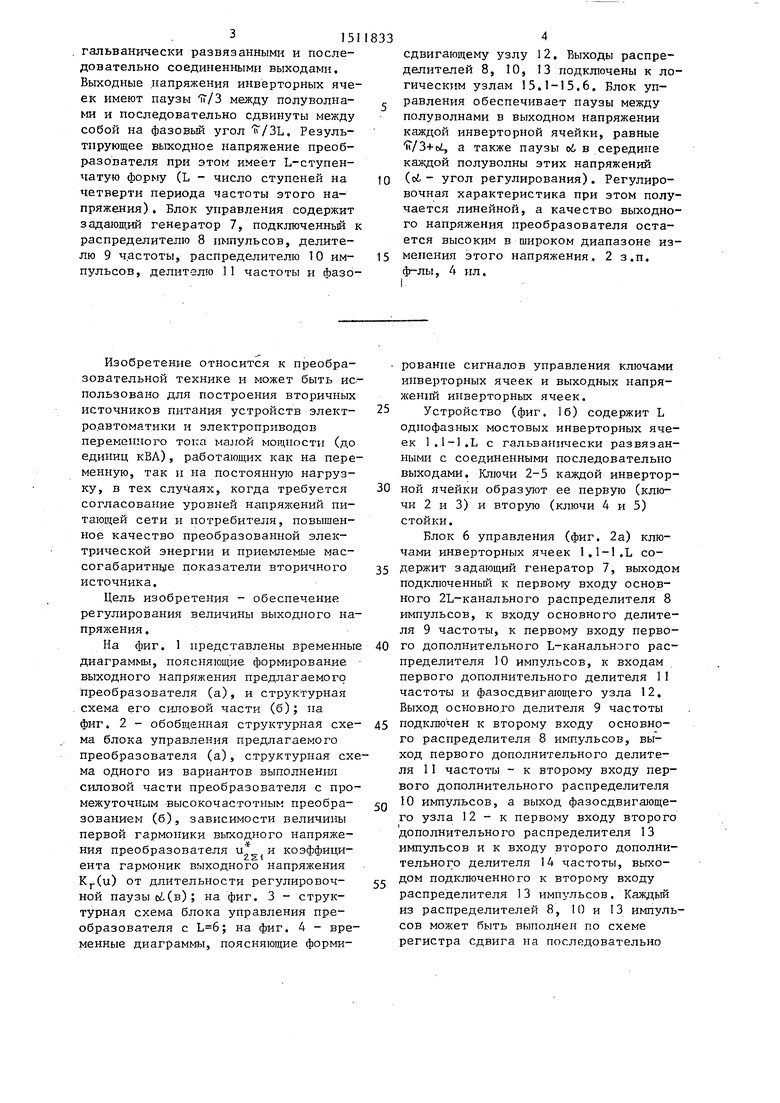

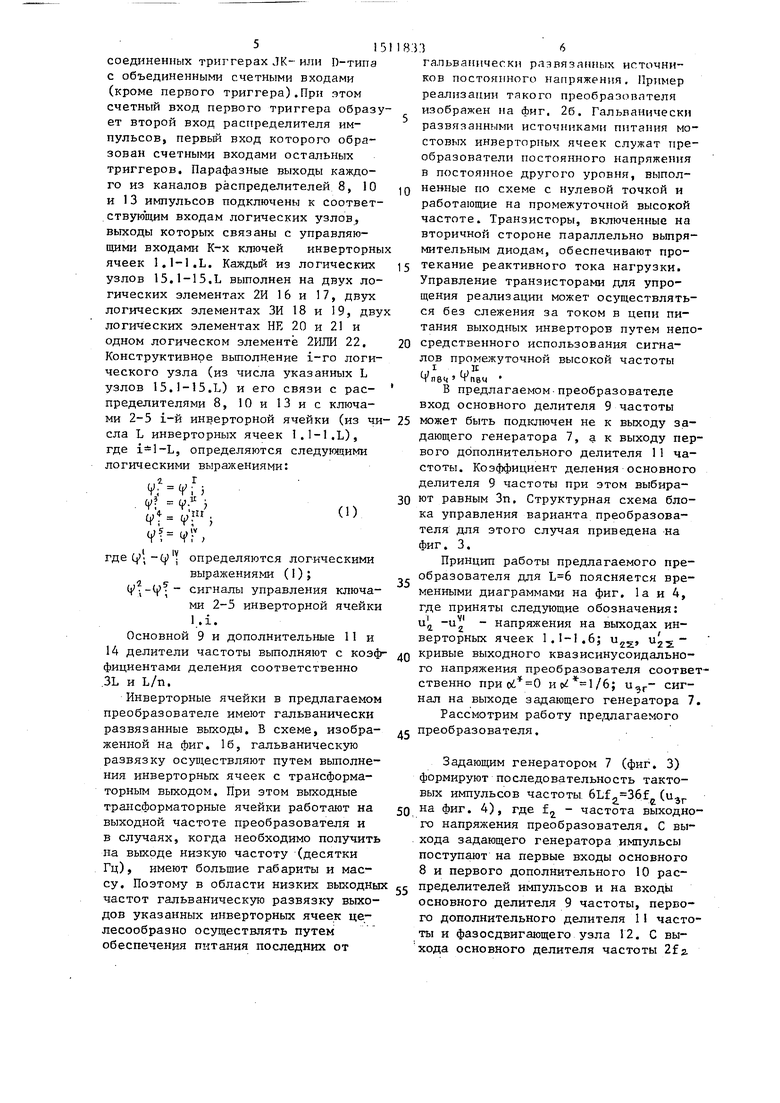

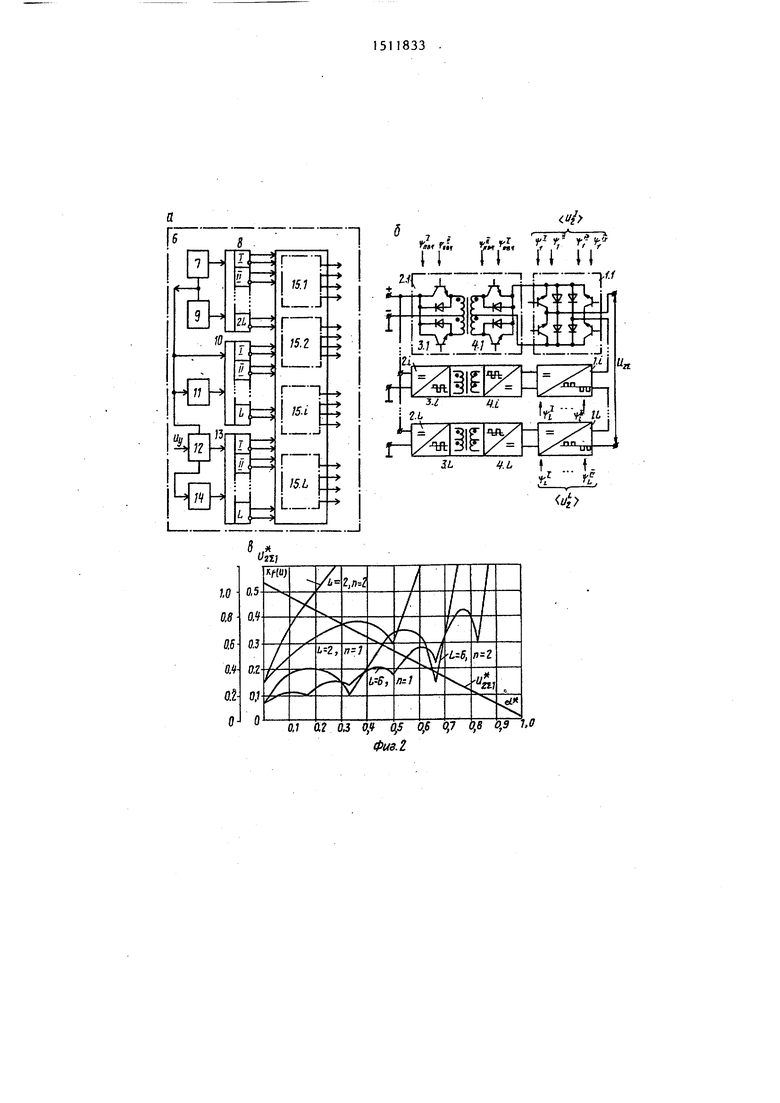

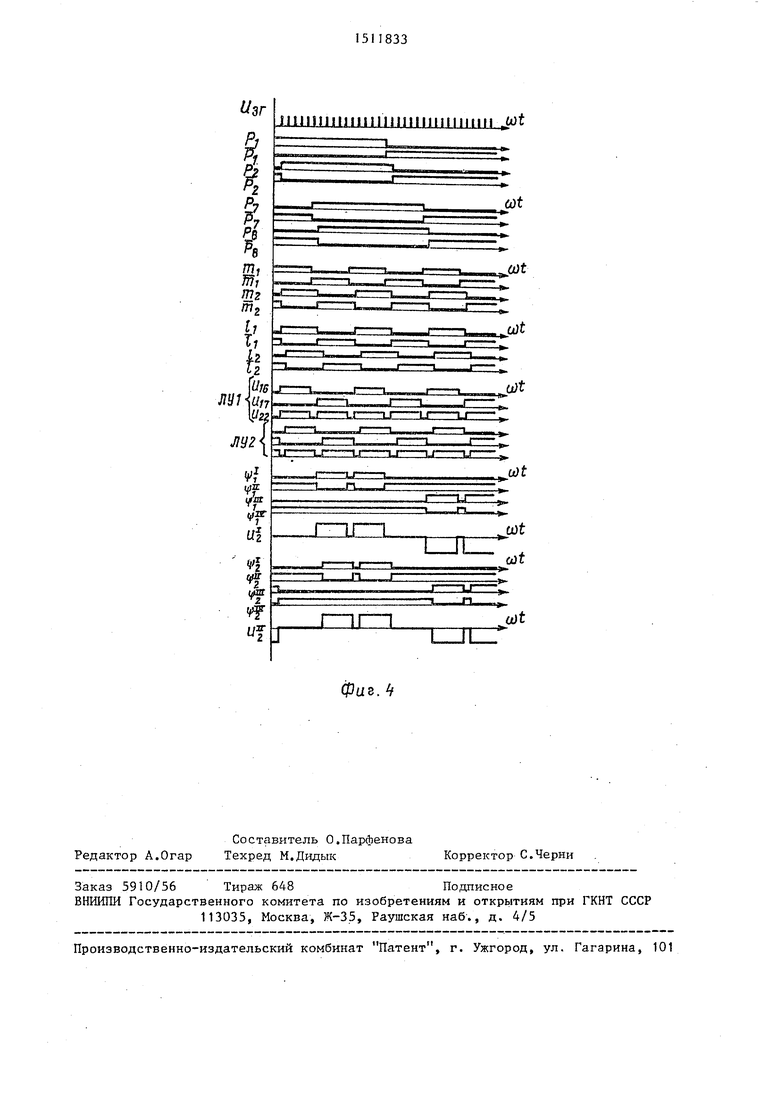

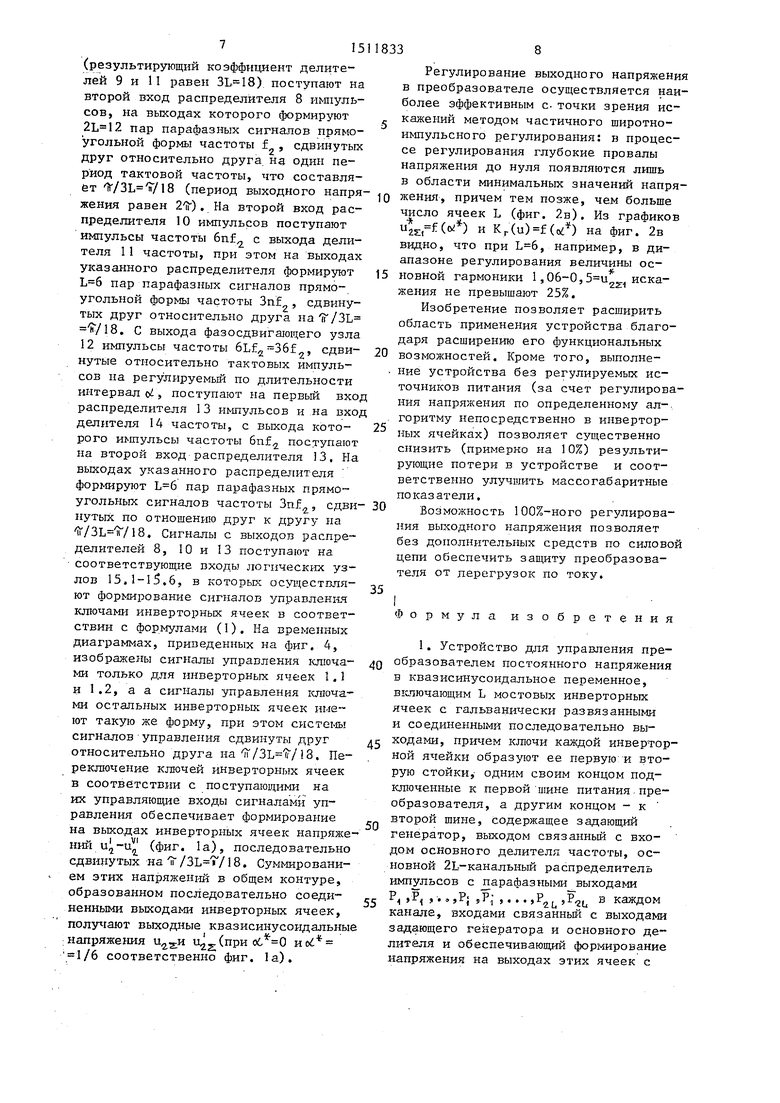

На фиг. 1 представлены временные диаграммы, поясняющие формирование выходного напряжения предлагаемого преобразователя (а), и структурная схема его силовой части (б); на фиг. 2 - обобщенная структурная схема блока управления предлагаемого преобразователя (а), структурная схема одного из вариантов выпол 1ен1щ силовой части преобразователя с промежуточным -высокочастотным преобразованием (б), зависимости величины

первой гармоники выходного напряже

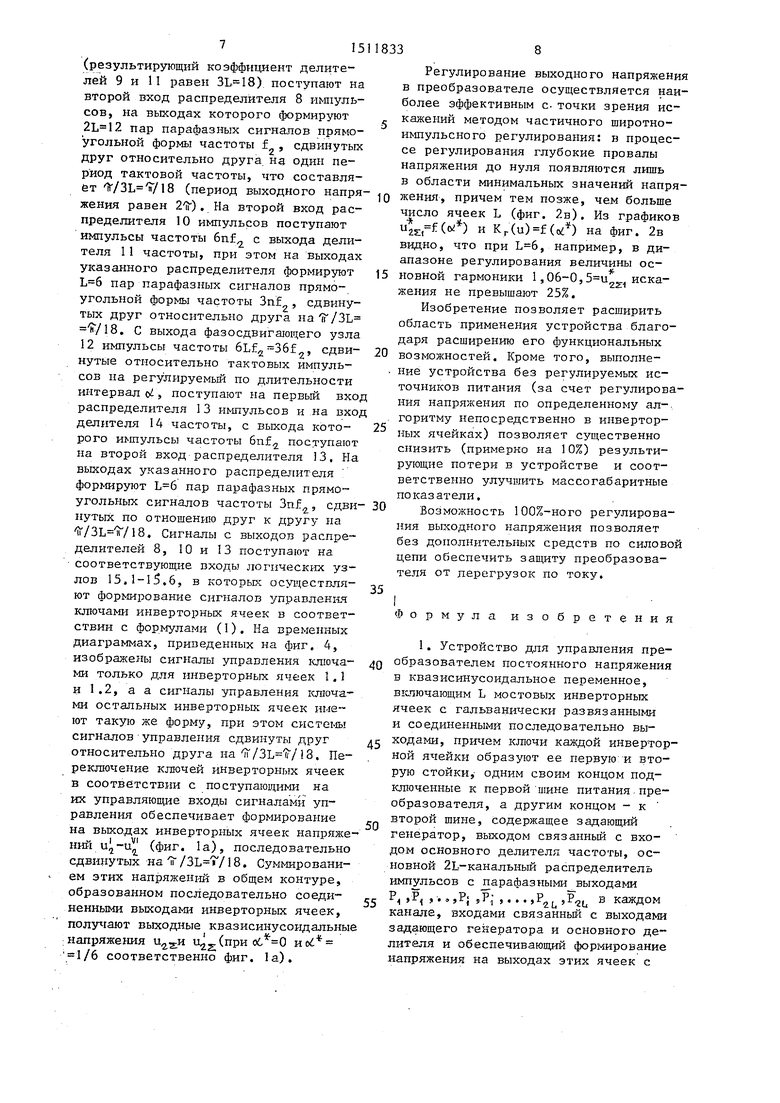

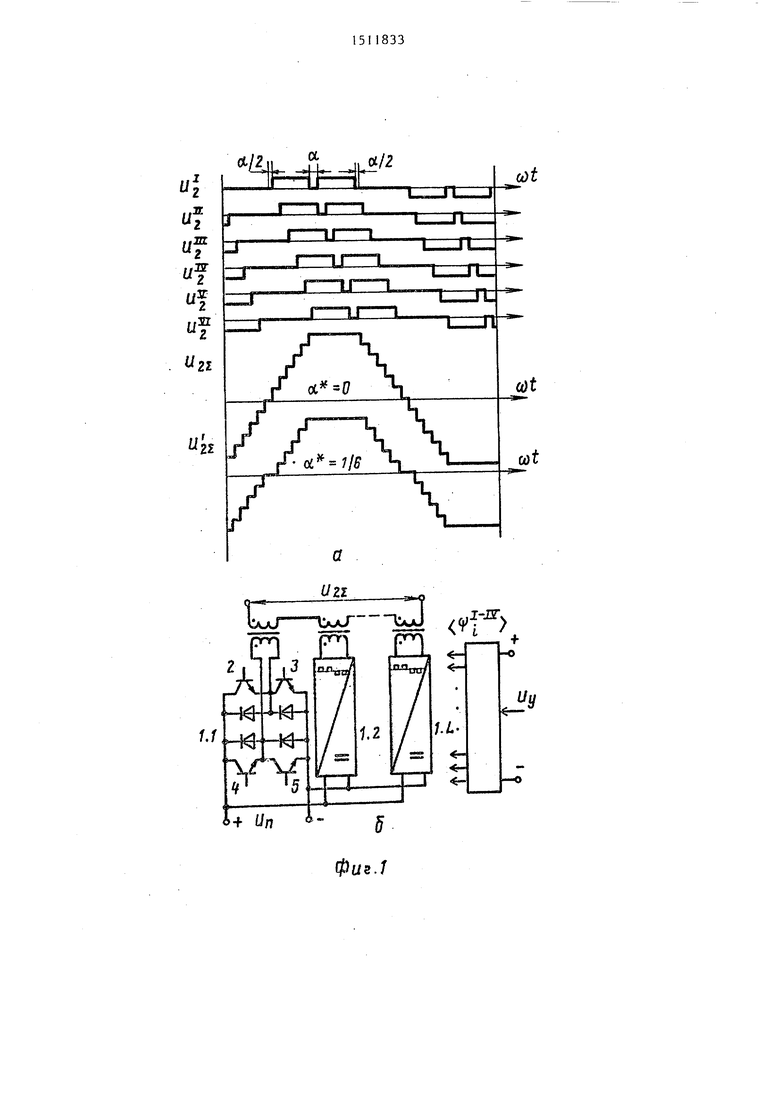

ния нреобразователя и и коэффициента гармоник выходного напряжения К(и) от длительности регулировочной паузы (х,(в) ; на фиг. 3 - структурная схема блока управления преобразователя с на фиг. 4 - временные диаграммы, поясняющие формирование сигналов управления ключами инверторных ячеек и выходных напряжений инверторных ячеек.

Устройство (фиг. 16) содержит L однофазных мостовых инверторных ячеек 1.1-1.L с гальванггчески развязанными с соединенными последовательно выходами. Ключи 2-5 каждой инверторной ячейки образуют ее первую (ключи 2 и 3) и вторую (ключи 4 и 5) стойкн.

Блок 6 управления (фиг. 2а) ключами инверторных ячеек 1.1-1.L содержит задающий генератор 7, выходом подключенньй к первому входу основного 2Ь-канального распределителя 8 импульсов, к входу основного делителя 9 частоты, к первому входу первого дополнительного L-канального распределителя 10 импульсов, к входам первого дополнительного делителя 11 частоты и фазосдвигающего узла 12. Выход основно.го делителя 9 частоты

подключен к второму входу основного распределителя 8 импульсов, выход первого дополнительного делителя 11 частоты - к второму входу первого дополнительного распределителя

10 и myльcoв, а выход фазосдвигающе- го узла 12 - к первому входу второго дополнительного распределителя 13 импульсов и к входу второго дополнительного делителя 14 частоты, выходом подключенного к второму входу распределителя 13 импульсов. Каждый из распределителей 8, 10 и 13 импульсов может быть выполнен по схеме регистра сдвига на последовательно

51 5

соединенных триггерах ЛК- или П-типа с объединенными счетными входами (кроме первого триггера).При этом счетный вход первого триггера образует второй вход распределителя импульсов, первьй вход которого образован счетными входами остальных триггеров. Парафазные выходы каждого из каналов распределителей 8, 10 и 13 импульсов подключены к соответствующим входам логических узлов, выходы которых связаны с управляющими входами К-х ключей инверторных ячеек 1.1-1.L. Каждый из логических узлов 15.1-15.L выполнен на двух логических элементах 2И 16 и 17, двух логических элементах ЗИ 18 и 19, двух логических элементах НЕ 20 и 21 и одном логическом элементе 2ИЛИ 22, Конструктивное вьшолн.ение i-ro логического узла (из числа указанных L узлов 15.1-15.L) и его связи с рас- пределителями 8, 10 и 13 и с ключами 2-5 1-й инверторной ячейки (из чи- ела L инверторных ячеек 1,1-l.L), где i-1-L, определяются следующими логическими выра}кениями:

(1)

rfj,(f

определяются логическими выражениями (1); сигналы управления ключами 2-5 инверторной ячейки

l..i. Основной 9 и дополнительные 11 и

14 делители частоты выполняют с коэффициентами деления соответственно .3L и L/n.

Инверторные ячейки в предлагаемом преобразователе имеют гальванически развязанные выходы, В схеме, изображенной на фиг. 16, гальваническую развязку осуществляют путем выполнения инверторных ячеек с трансформаторным выходом. При этом выходные трансформаторные ячейки работают на выходной частоте преобразователя и в слзгчаях, когда необходимо получить на выходе низкую частоту (десятки Гц), имеют большие габариты и массу. Поэтому в области низких выходны частот гальваническую развязку выходов указанных инверторных ячеек целесообразно осуществлять путем обеспечения питания последних от

Q 5 0 5

0

5

0

5

е

гальванически раявязянных источников постоянного напряжения. Пример реализации такого преобразователя изображен на фиг. 26. Гальнаническм развязанными источниками питания мостовых инверторных ячеек служат преобразователи постоянного напряжения в постоянное другого уровня, выполненные по схеме с нулевой точкой и работающие на промежуточной высокой частоте. Транзисторы, включенные на вторичной стороне параллельно выпрямительным диодам, обеспечивают протекание реактивного тока нагрузки. Управление транзисторами для упрощения реализации может осуществляться без слежения за током в цепи питания выходных инверторов путем непосредственного использования сигналов промежуточной высокой частоты

В предлагаемом-преобразователе

вход основного делителя 9 частоты может быть подключен не к выходу задающего генератора 7, а к выходу первого дополнительного делителя 11 частоты. Коэффициент деления основного делителя 9 частоты при этом выбирают равным Зп. Структурная схема блока управления варианта преобразователя для этого случая приведена -на фиг. 3,

Принцип работы предлагаемого преобразователя для поясняется временными диаграммами на фиг, 1а и 4, где приняты следующие обозначения: ulj - напряжения на выходах ин22 25.

0

верторных ячеек 1.1-1.6; и кривые выходного квазисинусоидального напряжения преобразователя соответственно npHci 0 Ugp- сигнал на выходе задающего генератора 7.

Рассмотрим работу предлагаемого преобразователя.

Задающим генератором 7 (фиг. 3) формируют последовательность тактовых импульсов частоты (u.j на фиг. 4), где f - частота выходного напряжения преобразователя. С выхода задающего генератора импульсы поступают на первые входы основного 8 и первого дополнительного 10 распределителей импульсов и на входы основного делителя 9 частоты, первого дополнительного делителя 1I частоты и фазосдвигающего узла 12. С выхода основного делителя частоты Zfa.

715

(результирующий коэффициент делителей 9 и 11 равен ) поступают на второй вход распределителя 8 им1уль- сов, на выходах которого формируют пар парафазных сигналов прямоугольной формы частоты f , сдвинутых друг относительно друга, на один период тактовой частоты, что составляет Or/3L ii /18 (период выходного напряжения равен 2 ir). На второй вход распределителя 10 импульсов поступают импульсы частоты 6nf с выхода делителя 11 частоты, при этом на выходах указанного распределителя формирзпот пар парафазных сигналов прямоугольной формы частоты ЗпЕ , сдвинутых друг относительно друга на n /3L « /18. С выхода фазосдвигающего узла 12 импульсы частоты , сдвинутые относительно тактовых импульсов па регулируемый по длительности интервал Ы, поступают на первый вхо распределителя 13 и шyльcoв к на вхо делителя 14 частоты, с выхода которого импульсы частоты Bnf поступают па второй вход распределителя 13. На выходах указанного распределителя ; формируют пар парафазных прямоугольных сигналов частоты 3nf.., сдвинутых по отношению друг к другу на ir/3L i /18, Сигналы с выходов распределителей 8, 10 и 13 поступают на соответствующие входы логических узлов 15.1-15,6, в которых осуществляют формирование сигналов упргшления ключами инверторных ячеек в соответствии с формулами (1), На временных диаграммах, приведенных на фиг, 4, изображены сигналы управления ключами только для инверторных ячеек 1,1 и 1,2, а а сигналы управления хипоча- ми остальных инверторных ячеек Hi-ie- ют такую же форму, при этом снстсмы сигналовуправления сдвинуты друг относительно друга на п /ЗЪ ( /18, Переключение ключей инверторных ячеек в соответствии с поступающими на их управляющие входы сигналами управления обеспечивает формирование на выходах инверторных ячеек напряжений (фиг, 1а), последовательно сдвинутых на IT/3L /18, Суммированием этих напряжений в общем контуре, образованном последовательно соединенными выходами инверторных ячеек, получают выходные квазисинусоидальные напряжения и(/ соответственно фиг, 1а),

8

Регулирование выходного напряжения в преобразователе осуществляется наиболее эффективным с. точки зрения исf. кажений методом частичного широтно- н шyльcнoгo регулирования: в процессе регулирования глубокие провалы напряжения до нуля появляются лишь в области минимальных значений нанря0 жения, причем тем позже, чем больше число ячеек L (фиг, 2в), Из графиков U25:rf(o) и Кг(и)(о/) на фиг, 2в видно, что при , например, в диапазоне регулирования величины ос5 новной гармоники 1,06-0, искажения не превышают 25%,

Изобретение позволяет расширить область применения устройства благодаря расширению его функциональных

0 возможностей. Кроме того, выполне- ние устройства без регулируемых источников питания (за счет регулирования напряжения по определенному ал-., горитму непосредственно в инвертор- ных ячейках) позволяет существенно снизить (примерно на 10%) результирующие потерн в устройстве и соответственно улучшить массогабаритные показатели.

0 Возможность 100%-ного регулирования выходного напряжения позволяет без дополнительных средств по силовой цепи обеспечить защиту преобразователя от перегрузок по току,

5

I

Формула изобретения

1, Устройство для управления пре- д образователем постоянного напряжения в квазисинусоидальное переменное, вхшючающим L мостовых инверторнмх ячеек с гальванически развязанными и соединенными последовательно вы- с ходами, причем ключи каждой инвертор- ной ячейки образуют ее первую:и вторую стойки,- одним своим концом подключенные к первой шине питания.преобразователя, а другим концом - к второй шине, содержащее задающий генератор, вьгходом связанный с входом основного делителя частоты, основной 2Ь-канальный распределитель импульсов с парафазными выходами

5 PI , в каждом канала, входами связанный с выходами задающего генератора и основного делителя и обеспечивающий формирование напряжения на выходах этих ячеек с

915

паузой 7/3 между полуволнами и последовательный фазовый сдвиг на угол Т/ЗЬ между полуволнами и последовательный фазовый сдвиг на угол if/3L между напряжениями ячеек, отличающееся тем, что, с целью обеспечения регулирования величины выходного напряжения, оно снабжено широкодиапазонным фазосдвигающим узлом, двумя дополнительными делителями частоты на L/n, где п - число импульсов на интервале |Г/3 выходного напряжения, двумя дополнительными L-канальными распределителями импульсов с парафазными выходами т,, т,,... ,т; ,m;,.. ,m;,mj и 1, ,..., 1; ,1;,.. . ,l,lj в каждом канале соответственно, а также аналогично выполненными логическими у злами, соединенными входами с соответствующими выходами соответствующих распределителей, а выходами предназначенными для соединения с управляющими входами соответствующей ключей соответствующих инверторных ячеек, причем входы первого дополнительного распределителя соединены с выходом задающего генератора непосредственно и через первьй дополнительный делитель частоты, входы второго дополнительного распределителя подключены к выходу широкодиапазонного фазосдви- гающего узла непосредственно и через второй дополнительный делитель частоты, вход фазосдвигающего узла соединен с выходом задающего генератора а i-й логический узел из числа L указанных узлов, его связи с распре1833

10

делителями импульсов и с ключами i-й инверторной ячейки определяются

следующими логическими выражениями:

г

ключа первой стойки,подключенного к первой шине пи- j. тания;

(- sCf j - для ключа первой стойки,подключенного к второй шине пииг - - - тания;

(;.Р; Pj(m;l;+m;l;) - для ключа второй стойки,подключенного к первой шине пи- тания;

(f. 0;. - для ключа второй стойки,подключенного к второй шине питания;где .

5

0

нератора, он выполнен с коэффициентом деления, равньш 3L.

3, Устройство по По 2, отличающееся тем, что, с целью упрощения, вход основного делителя частоты связан с выходом задающего генератора через первый дополнительный делитель частоты и выполнен с кО941фициентом деления, равным Зп.

оь/2|1 ; iJf/

за

и

21

22

i/2r

Uxf-UjxTbuJ

И n

:лМ.

-й-й1,1

;i т

f УЛ ./

а

..

0.2- 00.1 U2 03 Ofl QJS 0,B 0,7 0,8 0,3 Физ.1

.//

u, «/ -Гa/I у- у, и.г

ГГ гГ Г Г

SM:

JSjJ L.LL L ,

Zij

11

нь

LI

.i

-m

4A

Л

Ji4 .i t ... f.

r/ yf.

г/г

Usr

HIiniHMIiiHnillliniMHilM ,(Ut

l

Vf

vf

Uf

Физ. a)t

a)t

| Константинов В.Г | |||

| Многофазные преобразователи на транзисторах | |||

| М.: Энергия, 1972, 96 с | |||

| Способ преобразования постоянного напряжения в многоступенчатое переменное | 1979 |

|

SU1046876A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1989-09-30—Публикация

1987-05-27—Подача