Изобретение относится к электротехнике и может быть использовано в. системах вторичного электропитания . и электропривода. .

Цель изобретения - повышение КПД устройства, реализующего предлагаемый способ.

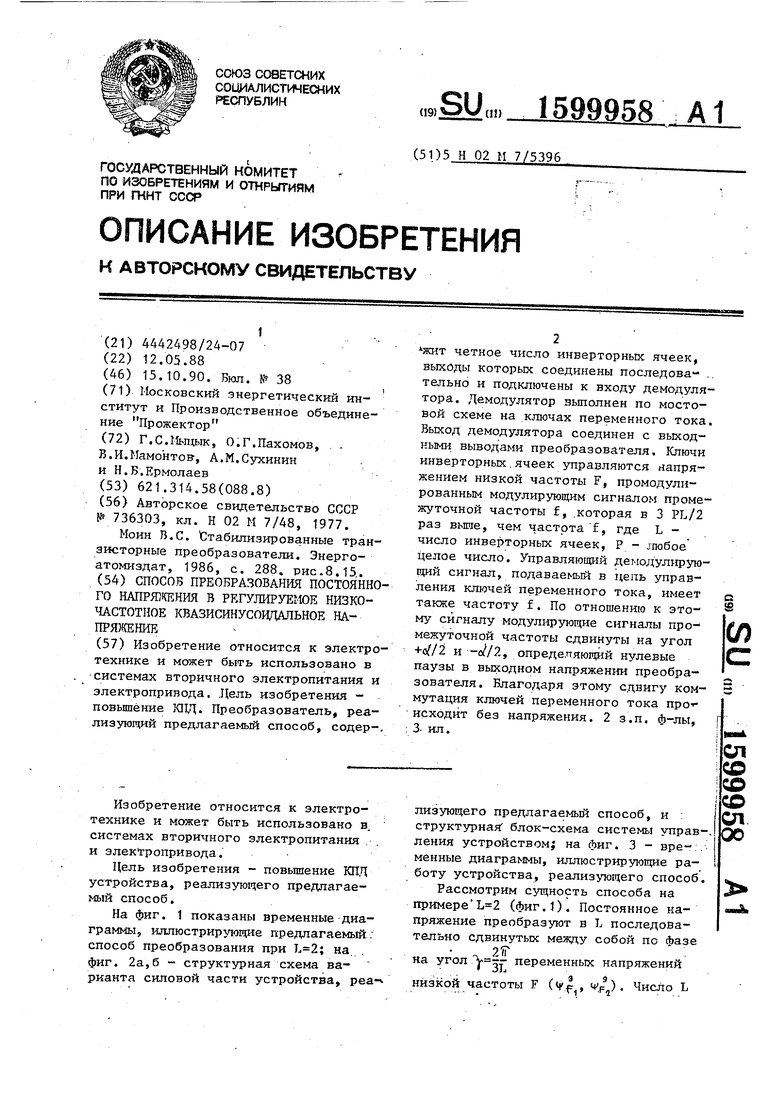

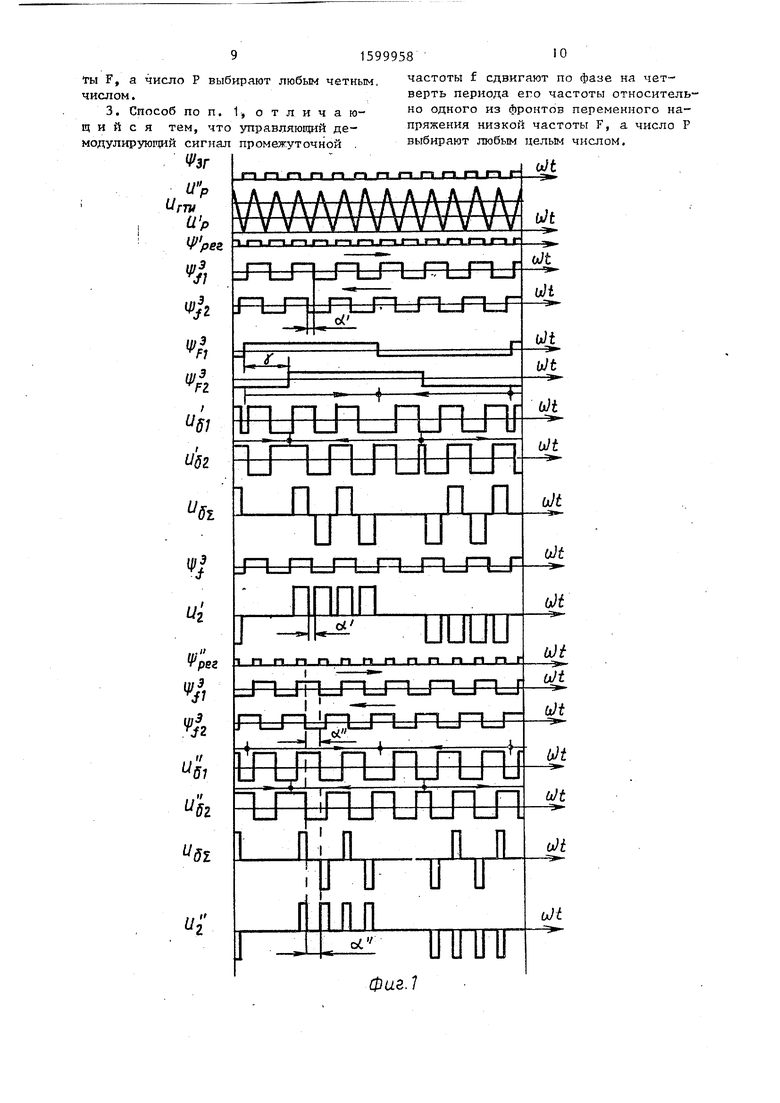

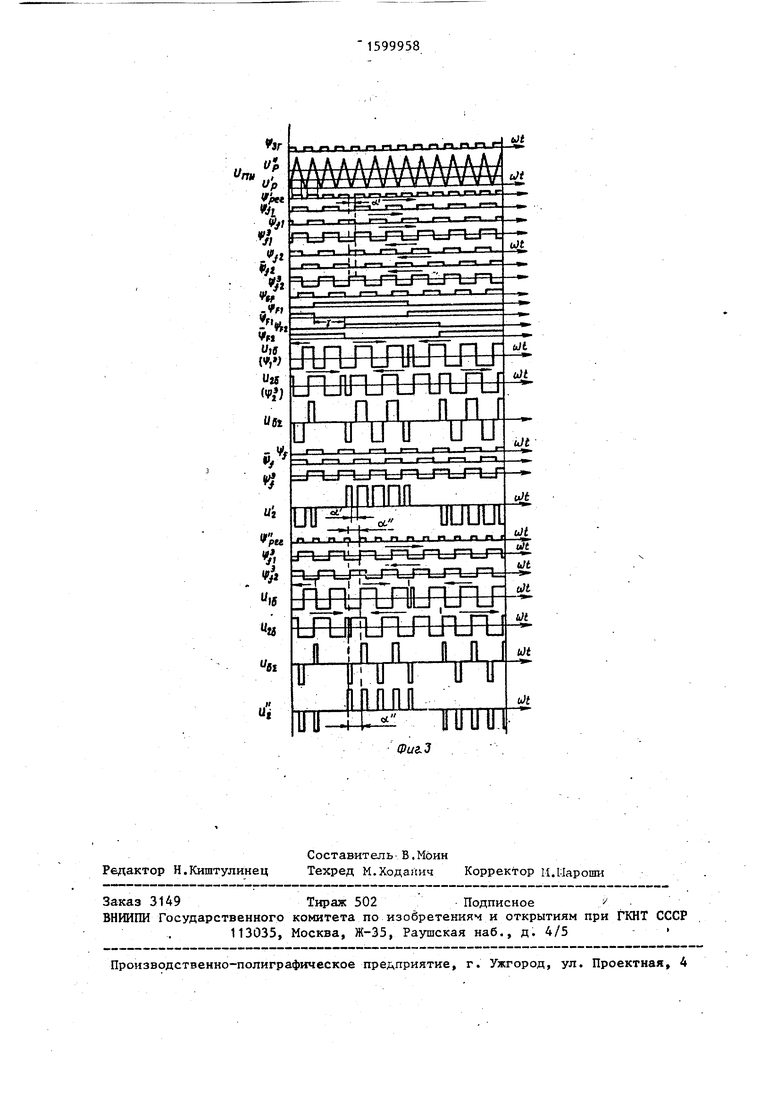

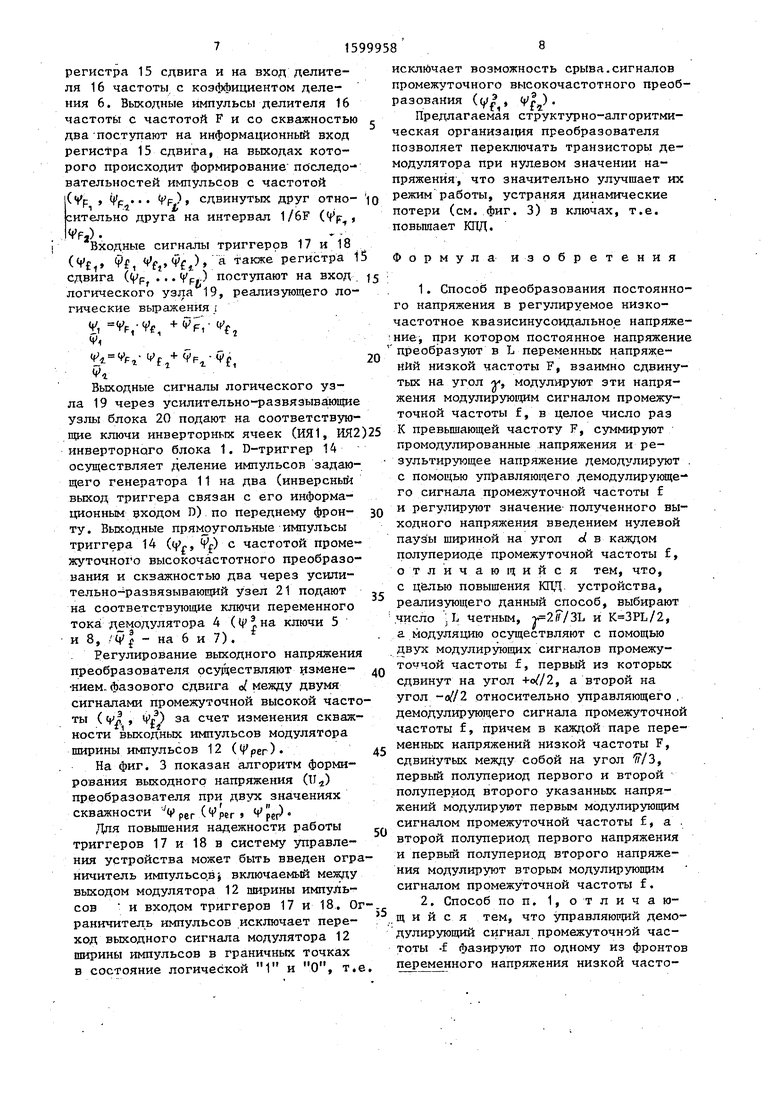

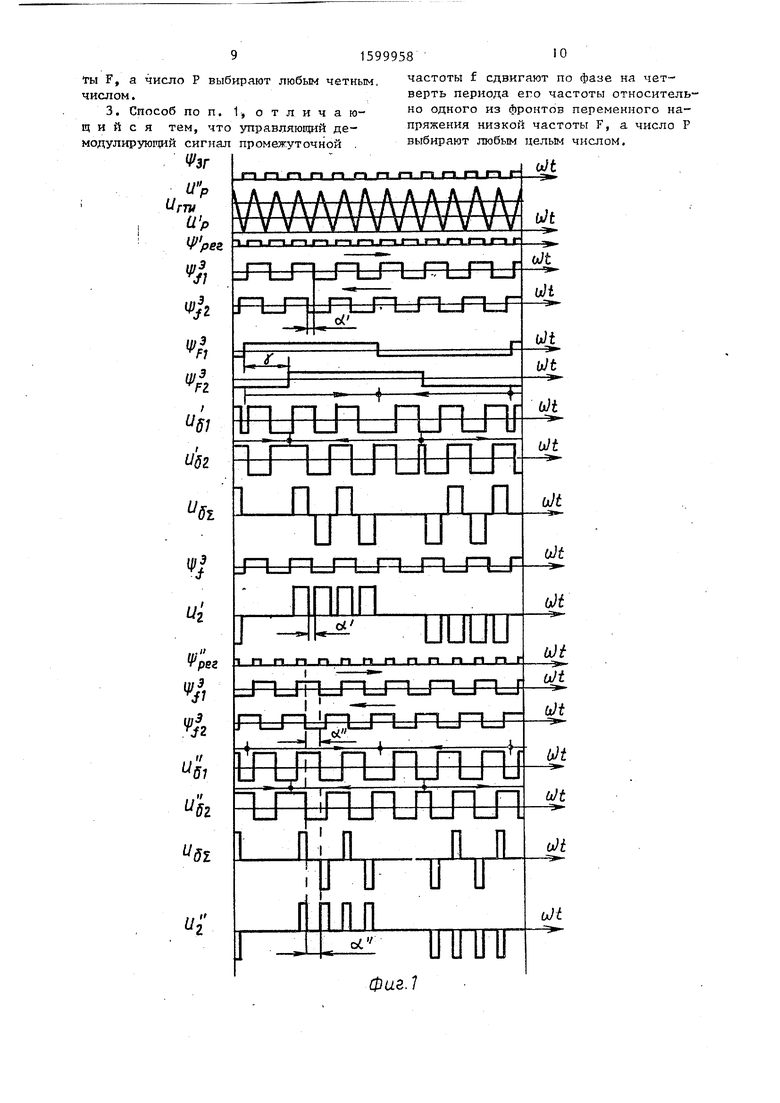

На фиг. 1 показаны временные диаграммы, иллюстрирующие предлагаемый: способ преобразования при на. фиг. 2а,б - структурная схема варианта силовой части устройства, реализующего предлагаемый способ, и : структурнаяГ блок-схема системы управления устройством; на фиг. 3 - вре- .. менные диаграммы, иллюстрирующие ра- боту устройства, реализующего способ .

Рассмотрим сущность способа на примере L 2 (фиг.1). Постоянное напряжение преобразуют в L последовательно сдвинутых между собой по Аазе

на угол 1- переменных напряжений

низкой частоты F (Vf, v/) . Число L

СП

со ;о о ел

00

задают четным. Далее формируют управляющий демодулирующий сигнал типа меандр, промежуточной частоты , обозначенный н Лиг. 1, Kak Vl « и два- аналогичных по форме с симметрично встречно изменяемым относительно друг друга фазовым сдвигом My модулирующих сигнала частоты f(Vf,, ). Затем модулируют низкочастотные наг . пряжения модулирующими сигналами частоты f, причем в каждой паре напряжений низкой частоты, сдвинутых между собой на угол 1f73, положительные полуволны одного напряжения и отрицательные полуволны другого напряжения модулируют первым модулирующим сигналом частоты f(р ), а отрицательные полуволны одного и положительные другого модулируют вторым модулирую1чим сигналом частоты f( у/. ) После этого трансформир тот полученные промодулированные напряжения (Uf Uj- ) с последующим суммированием всех напряжений. Затем полученное результирующее напряжение (Uy.) демо- дулируют с помощью демодулирующего сигнала Vf Выбирают кратность часРтот -3L, где Р - четное число

(минимальное значение коэффициента определяет минимально возможную частоту промежуточного высокочастот-- ного преобразования, период которой

2. равен

,Тля устранения двойных вольтсе- кундных площадей фазирование разно- частотных сигналов (р и 4 , . .tf производят, исходя из условия изме- нения полярности низкочастотных напряжений в момент, соответствующий четверти периода демодулирушщего сигнала (f (фиг. 3). При этом коэффициент Р выбирают любым целым числом (минимальное значение коэффициента

определяет ми1:имально возможную частоту промежуточного высокочас-, дотного преобразования, полупериод

2fr который равен ).

Регулирование величины выходной5 . низкочастотного напряжения осуществляют за счет изменения фазового сдвига о между двумя модулирующими сигналами частоты f ( V/P . .

Одним из возможных вариантов практической реализации предлагаемого

0

5

5

0

5

0

5

0

5

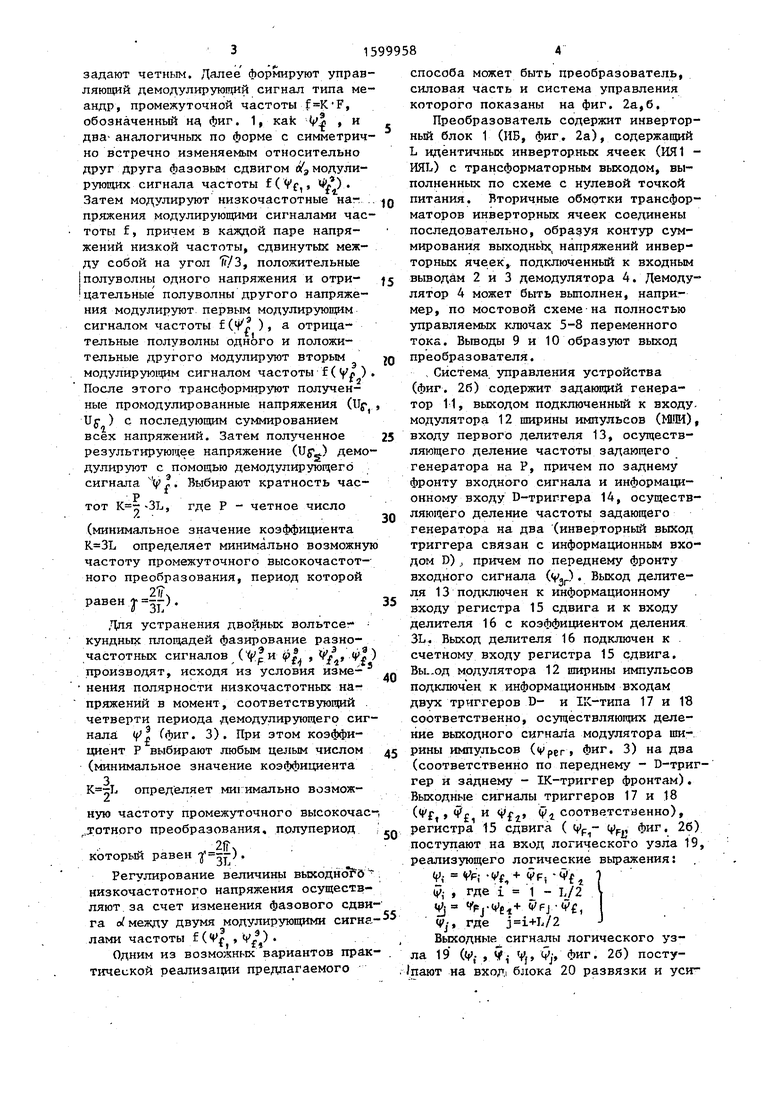

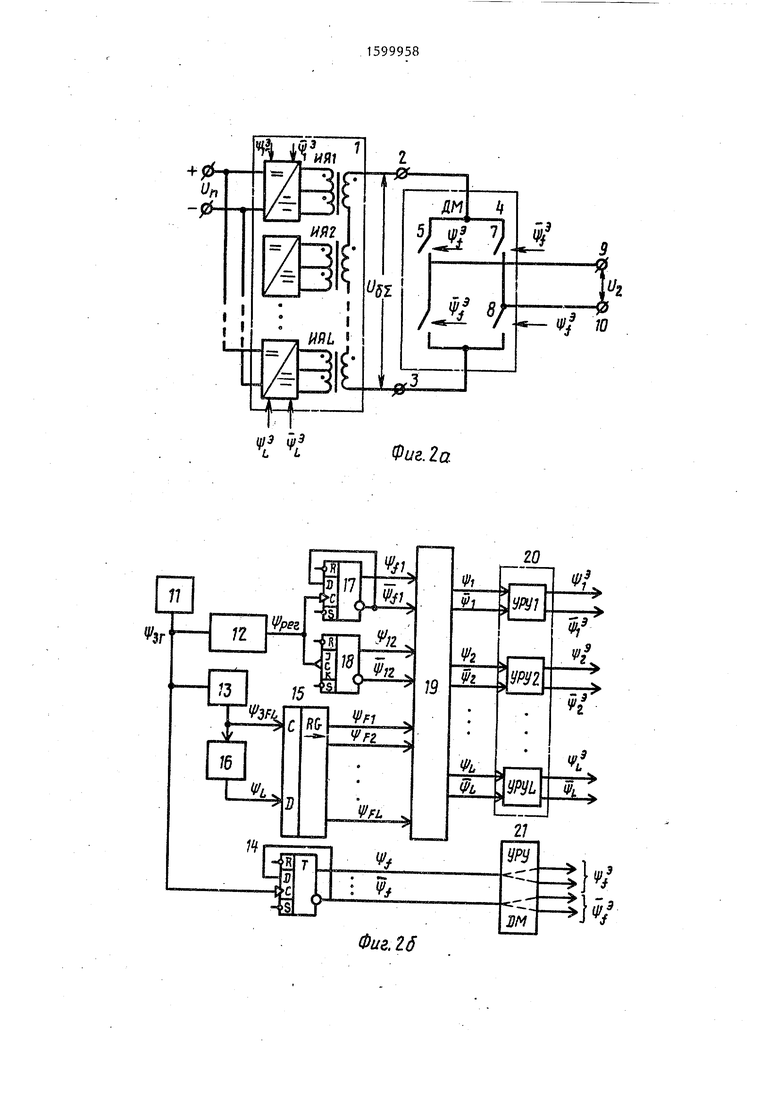

способа может быть преобразователь, силовая часть и система управления которого показаны на фиг. 2а,б.

Преобразователь содержит инвертор- ньй блок 1 (НБ, фиг, 2а), содержащий L идентичных инверторных ячеек (ИЯ1 - ИЯЬ) с трансформаторным выходом, выполненных по схеме с нулевой точкой питания. Вторичные обмотки трансформаторов инверторных ячеек соединены последовательно, образуя контур суммирования выходньЦ напряжений инверторных ячеек, подключенный к входным выводам 2 и 3 демодулятора 4. Демодулятор 4 может быть выполнен, например, по мостовой схеме на полностью управляемых ключах 5-8 переменного тока. Вьшоды 9 и 10 образуют выход преобразователя.

, Система з равления устройства (фиг. 26) содержит задающий генератор 11, выходом подключенный к входу, модулятора 12 щирины импульсов (MUH), входу первого делителя 13, осуществляющего деление частоты задающего генератора на Р, причем по заднему фронту входного сигнала и информационному входу D-триггер а 14, осуществляющего деление частоты задающего генератора на два (инверторный выход триггера связан с информационным входом D) причем по переднему фронту входного сигнала (Vjp) Выход делителя 13 подключен к информационному входу регистра 15 сдвига и к входу делителя 16 с коэффициентом деления 3L. Выход делителя 16 подключен к . счетному входу регистра 15 сдвига. Вы.,од модулятора 12 щирины импульсов подключен к информационным входам двух триггеров D- и 1К-типа 17 и 18 соответственно, осуществляющих деление выходного сигнала модулятора ширины импульсов (vper Фиг. 3) на два (соответственно по переднему - D-триггер и заднему - 1К-триггер фронтам). Выходные сигналы триггеров 17 и 18 (ff , и , ip соответстиенно), регистра 15 сдвига ( - (p, фиг. 26) поступают на вход логического узла 19, реализующего логические выражения:

V,- р; «f f, VPi 4 ц/. , где - L/2

fpj. cpFj -Vf,

где

Vj

Vy

Выходные сигналы логического узла 19 (Vf , V,- Vp Vj, фиг. 26) посту- пают на вхоД| блока 20 развязки и усиления 20, состоящего из L идентичных усилительно-развязываю1чих узлов УРУ1 - УРУ1. (фиг. 26). Выходные сигналы (v , ..... (t, ((},фиг. 26) блока 20 подают на соответствующие ключи соответствующих инверторных ячеек (ИЯ1-ИЯЬ) инверторного блока 1 (фиг. 26).

Выходные сигналы D-триггера 14 подают на вход усилительно-развязывающего узла 21, выходные сигналы (уД й) которого подают на соответствующие ключи 5-8 переменного тока модулятора 4 ( (| на ключи 5 и 8, на клУ)чи 6 и 7) .

Усилительно-развязьшающие узлы 21 и блок 20 (УРУ1-УРУЪ) могут быть выполнены, например, по одной из схем инверторной ячейки с трансформаторным выходом, позволяющей легко осуществ-- лять тиражирование требуемого числа управляющих сигналов.

Модулятор 12 юирины импульсов (М М) содержит генератор треугольных импульсов симметричной формы (11 ртк фиг. 3) и компаратор, на один вход которого поступает напряжение 11 ти на второй изменяемый (в пределах максимального и минимального значений напряжения f-f уровень постоянного напряжения.

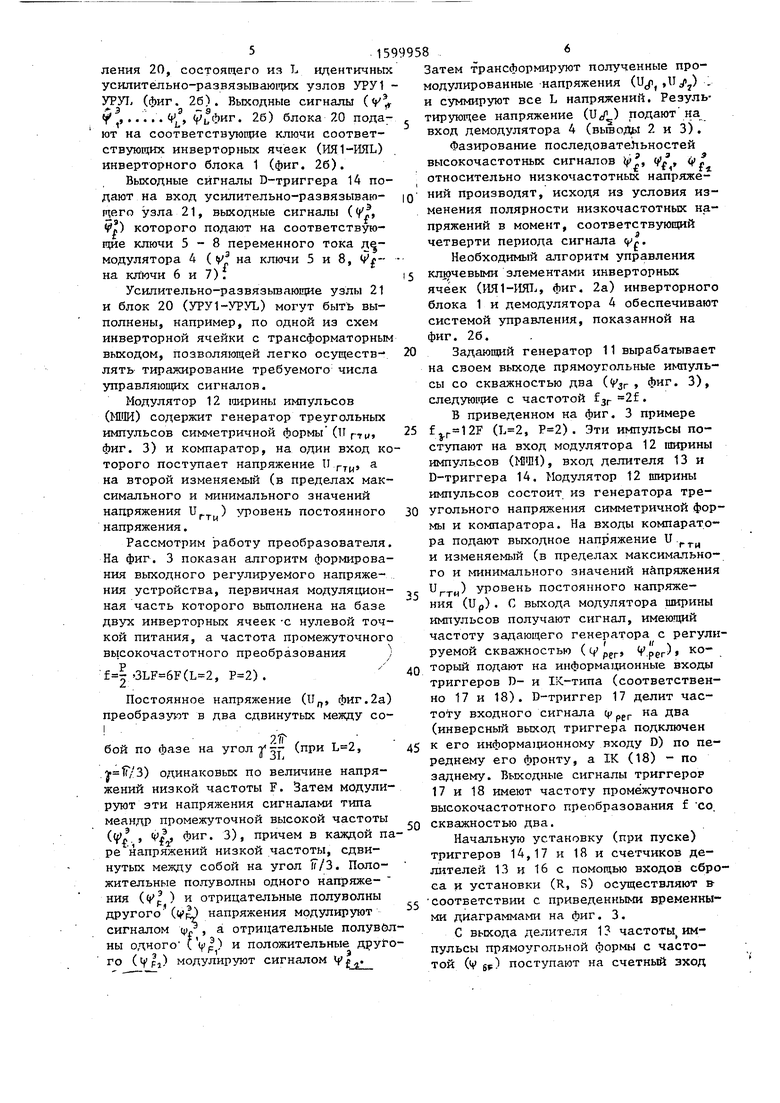

Рассмотрим работу преобразователя. На фиг. 3 показан алгоритм формирования выходного регулируемого напряжения устройства, первичная модуляционная часть которого выполнена на базе двух инверторных ячеек -с нулевой точкой питания, а частота промежуточного высокочастотного преобразования j

f | 3LF 6F(, ) .

Постоянное напряжение (И, фиг.2а) преобразуют в два сдвинутых между соPITбой по фазе на угол (при ,

:tr/3) одинаковых по величине напряжений низкой частоты F. Затем модулируют эти напряжения сигналами типа меандр промежуточной высокой частоты (V/. Ь причем в каждой паре напряжений низкой частоты, сдвинутых между собой на угол F/3. Положительные полуволны одного напряжения («t с ) и отрицательные полуволны другого (vlJ напряжения модулируют сигналом , а отрицательные полувблf 1 : НЫ

ГО (у Fa) модулируют сигналом У.

Затем трансформируют полученные про- модулированные напряжения ( ) - и суммируют все L напряжений. Результирующее напряжение (U) подают на вход демодулятора 4 (вьгаоДы 2 и 3). Фазирование последовательностей

высокочастотных сигналов

10

20

25

30

-; {

относительно низкочастотньк напряжений производят, исходя из условия из менения полярности низкочастотных на пряжений в момент, соответствующий четверти периода сигнала Vr

Необходимый алгоритм управления ключевыми элементами инверторных ячеек (ИЯ1-ИШ., фиг. 2а) инверторног блока 1 и демодулятора 4 обеспечиваю системой управления, показанной на фиг. 26.

Задающий генератор 11 вырабатывает на своем выходе прямоугольные импуль сы со скважностью два («f ar Фиг. 3), следуюгцие с частотой f г 2f.

В приведенном на фиг. 3 примере fj.r.12F (, ) . Эти импульсы поступают на вход модулятора 12 ширины импульсов (), вход делителя 13 и D-триггера 14. Нодулятор 12 ширины импульсов состоит из генератора треугольного напряжения симметричной фор мы и компаратора. На входы компарато ра подают выходное напряжение и изменяемый (в пределах максимально го и минимального значений напряжени и „) уровень постоянного напряжения (Up). С выхода модулятора ширины импульсов получают сигнал, имеющий частоту задающего генератора с регул руемой скважностью (( р, V.per ° торый подают на информаи;ионные входы триггеров D- и 1К-типа (соответствен но 17 и 18). D-триггер 17 делит частоту входного сигнала (j; р на два (инверсный выход триггера подключен 45 к его информа1щонному входу D) по пе реднему его фронту, а IK (18) - по заднему. Выходные сигналы триггеров 17 и 18 имеют частоту промежуточного высокочастотного преобразования f СО скважностью два.

Начальную установку (при пуске) триггеров 14,17 и 18 и счетчиков делителей 13 и 16 с помощью входов сбр са и установки (R, S) осуществляют в соответствии с приведенными временны ми диаграммами на фиг. 3.

35

40

50

55

налом Vf,-, а отрицательный uujiyBUJi- Q выхода делителя 1 частоты им- одного CVI,) и положительные друго- пульсы прямоугольной формы с частотой (v sf поступают на счетный зход

9958

Затем трансформируют полученные про- модулированные напряжения ( ) - и суммируют все L напряжений. Результирующее напряжение (U) подают на вход демодулятора 4 (вьгаоДы 2 и 3). Фазирование последовательностей

высокочастотных сигналов

10

20

25

30

-; {

относительно низкочастотньк напряжений производят, исходя из условия изменения полярности низкочастотных напряжений в момент, соответствующий четверти периода сигнала Vr

Необходимый алгоритм управления ключевыми элементами инверторных ячеек (ИЯ1-ИШ., фиг. 2а) инверторного блока 1 и демодулятора 4 обеспечивают системой управления, показанной на фиг. 26.

Задающий генератор 11 вырабатывает на своем выходе прямоугольные импульсы со скважностью два («f ar Фиг. 3), следуюгцие с частотой f г 2f.

В приведенном на фиг. 3 примере fj.r.12F (, ) . Эти импульсы поступают на вход модулятора 12 ширины импульсов (), вход делителя 13 и D-триггера 14. Нодулятор 12 ширины импульсов состоит из генератора треугольного напряжения симметричной формы и компаратора. На входы компаратора подают выходное напряжение и изменяемый (в пределах максимального и минимального значений напряжения и „) уровень постоянного напряжения (Up). С выхода модулятора ширины импульсов получают сигнал, имеющий частоту задающего генератора с регулируемой скважностью (( р, V.per ° торый подают на информаи;ионные входы триггеров D- и 1К-типа (соответственно 17 и 18). D-триггер 17 делит частоту входного сигнала (j; р на два (инверсный выход триггера подключен 45 к его информа1щонному входу D) по переднему его фронту, а IK (18) - по заднему. Выходные сигналы триггеров 17 и 18 имеют частоту промежуточного высокочастотного преобразования f СО. скважностью два.

Начальную установку (при пуске) триггеров 14,17 и 18 и счетчиков делителей 13 и 16 с помощью входов сброса и установки (R, S) осуществляют в- соответствии с приведенными временными диаграммами на фиг. 3.

35

40

50

55

регистра 15 сдвига и на вход делителя 16 частоты с коэффициентом деления 6. Вькодные импульсы делителя 16 частоты с частотой F и со скважностью два поступают на информационный вход регистра 15 сдвига, на выходах которого происходит формирование последовательностей импульсов с частотой (VF J tfp ... ) сдвинутых друг отно- сительно друга на интервал 1/6F (Vp

VF )., .

Входные сигналы триггеров 17 и 18 (««,, f, t ft f 4) а также регистра 1 сдвига (VF, ... Vp,) поступают на вход. логического узла 19, реализующего логические выражения i

V, VF,-Vf, ,- Vf V

Vf/cJ F -Vf,

Vi

Выходные сигналы логического узла 19 через усилительно-развязывгцощие узлы блока 20 подают на соответствующие ключи инверторных ячеек (ИЯ1, ИЯ2 инверторного блока 1. D-триггер 14 осуществляет деление импульсов задающего генератора 11 на два (инверсный выход триггера связан с его информа- ционньм входом D) по переднему фрон- ту. Выходные прямоугольные импульсы триггера 14 ((р, Vf) с частотой промежуточного высокочастотного преобразования и скважностью два через усилительно-развязывающий узел 21 подают на соответствующие ключи переменного тока демодулятора 4 ( ключи 5 и 8, - на 6 и 7).

Регулирование выходного напряжения преобразователя осуществляют измене- нием. фазового сдвига о между двумя сигналами промежуточной высокой частоты ( , Ф/) за счет изменения скважности выходных импульсов модулятора щирины импульсов 12 (фрег).

На фиг. 3 показан алгоритм формирования выходного напряжения (114) преобразователя при двух значениях скважности per С Vper t per

Для повьпиения надежности работы триггеров 17 и 18 в систему управления устройства может быть введен ограничитель импульсовj включаемый между выходом модулятора 12 ширины импульсов и входом триггеров 17 и 18. О раничитель импульсов исключает переход выходного сигнала модулятора 12 ширины импульсов в граничных точках в состояние логической 1 и О, т.е

с

5 ;

0

25 ЗО

0 45

гс.

исклнЬчает возможность срыва.сигналов промежуточного высокочастотного преобразования ((f l

Предлагаемая структурно-алгоритмическая организа1р1Я преобразователя позволяет переключать транзисторы демодулятора при нулевом значении напряжения, что значительно улучшает их режим работы, устраняя динамические потери (см. фиг. 3) в ключах, т.е. повьппает КПД.

Формула изобретения

1.Способ преобразования постоянного напряжения в регулируемое низкочастотное квазисинусоидальное напряжение, при котором постоянное напряжение

преобразуют в L переменных напряжений низкой частоты F, взаимно сдвинутых на угол И, модулируют эти напряжения модулирующим сигналом промежуточной частоты f, в целое число раз К превьш1ающей частоту F, суммируют промодулированные напряжения и результирующее напряжение демодзшируют . с помощью управляющего демодулирукще- го сигнала промежуточной частоты f и регулируют значение полученного выходного напряжения введением нулевой пауз ы шириной на угол d в каждом полупериоде промежуточной частоты f, отличающийся тем, что, с ц&лью повышения КПД устройства, реализующего данный способ, выбирают число JL четным, 2F/3L и K 3PL/2, а модуляцию осуществляют с помощью двух модулирующих сигналов промежуточной частоты f, первый из которых сдвинут на угол W/2, а второй на угол -oil2 относительно управляющего , демодулирующего сигнала промежуточной частоты f, причем в каждой паре переменных напряжений низкой частоты F, сдвинутых между собой на угол «/З, первый полупериод первого и второй полупериод второго указанных напряжений модулируют первым модулирующим сигналом промежуточной частоты , а . второй полупериод первого напряжения и первый полупериод второго напряжения модулируют вторым модулирующим сигналом промежуточной частоты f.

2.Способ по п. 1, отличающийся тем, что управляющий демо- дулирующий сигнал промежуточной частоты -f фазируют по одному из фронтов переменного напряжения низкой часто /

рее

г-I j-u-nLf-n г-1 г-1 f-11-1 г

/;

Ф/2

п

51 и дг

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ преобразования постоянного напряжения в квазисинусоидальное переменное | 1987 |

|

SU1473052A1 |

| Преобразователь постоянного напряжения в квазисинусоидальное | 1982 |

|

SU1193760A1 |

| Способ преобразования переменного напряжения в постоянное | 1985 |

|

SU1385208A1 |

| Преобразователь с выходным переменным напряжением заданной формы | 1990 |

|

SU1812606A1 |

| СПОСОБ ПРЕОБРАЗОВАНИЯ ПОСТОЯННОГО НАПРЯЖЕНИЯ В ПЕРЕМЕННОЕ | 2008 |

|

RU2366068C1 |

| Устройство для управления преобразователем постоянного напряжения в квазисинусоидальное трехфазное | 1988 |

|

SU1577025A1 |

| Преобразователь постоянного напряжения в регулируемое трехфазное напряжение | 1987 |

|

SU1541739A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСТОЯННОГО НАПРЯЖЕНИЯ В КВАЗИСИНУСОИДАЛЬНОЕ ПЕРЕМЕННОЕ | 1978 |

|

SU826529A1 |

| Устройство для управления преобразователем постоянного напряжения в квазисинусоидальное переменное | 1987 |

|

SU1511833A1 |

| Устройство для управления регулируемым по напряжению преобразователем постоянного напряжения в трехфазное | 1986 |

|

SU1471268A1 |

Изобретение относится к электротехнике и может быть использовано в системах вторичного электропитания и электропривода. Цель изобретения - повышение КПД. Преобразователь, реализующий предложенный способ, содержит четное число инверторных ячеек, выходы которых соединены последовательно и подключены к входу демодулятора. Демодулятор выполнен по мостовой схеме на ключах переменного тока 5 - 8. Выход демодулятора соединен с выходными выводами преобразователя. Ключи инверторных ячеек управляются напряжением низкой частоты F, промодулированным модулирующим сигналом промежуточной частоты F, которая в 3 PL/2 раз выше, чем частота F, где L - число инверторных ячеек, P - любое целое число. Управляющий демодулирующий сигнал, подаваемый в цепь управления ключей переменного тока, имеет также частоту F. По отношению к этому сигналу модулирующие сигналы промежуточной частоты сдвинуты на угол +α/2 и -α/2, определяющий нулевые паузы в выходном напряжении преобразователя. Благодаря этому сдвигу коммутация ключей переменного тока происходит без напряжения. 2 з.п.ф-лы, 3 ил.

1 П П

п п

U U U U

П-Г

ппп

1

Ы

UUU

.

рег

Ч /,

1ГиУШ Г1ПГЦ

п п

(t

(jjt

(jJi

UUUU

(jJi

b)i

UUUU

фиг.1

Фиг. 26

| Преобразователь постоянного напряжения в квазисинусоидальное переменное | 1977 |

|

SU736303A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Моин B.C | |||

| Стабилизированные транзисторные преобразователи | |||

| Энерго- атомиздат, 1986, с | |||

| ДВОЙНОЙ ГАЕЧНЫЙ КЛЮЧ | 1920 |

|

SU288A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1990-10-15—Публикация

1988-05-12—Подача