Фиг. 2

, Изобретение относится к автомати- ;ке и вычислительной технике и пред- :назначено для использования в качест- ве решающих полей параллельных про- jueccopoB, ориентированных на нечис- |ленную обработку информации. I Цель изобретения - повьшение быстродействия ячейки за счет сокращения числа элементов в цепи распространения управляющего сигнала.

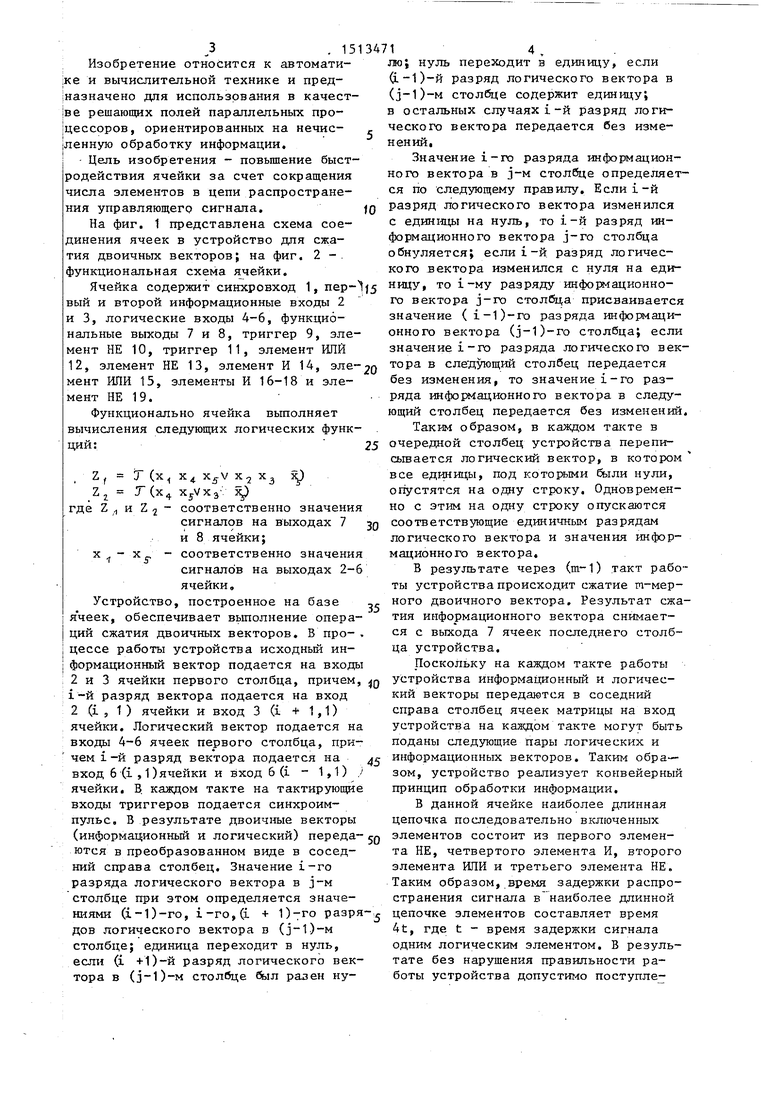

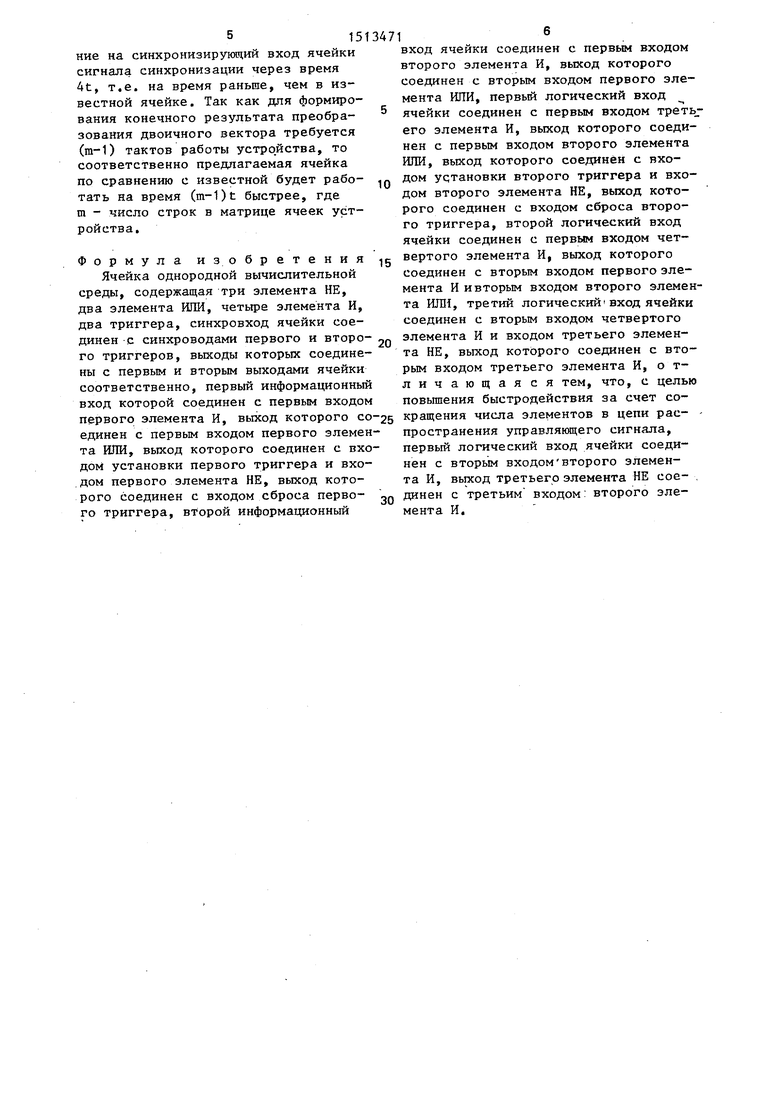

На фиг. 1 представлена схема соединения ячеек в устройство для сжатия двоичных векторов; на фиг. 2 -. функциональная схема ячейки.

to

лю; нуль переходит в единицу, если 0.-1)-й разряд логического вектора в (j-l)-M столбце содержит единицу; в остальных случаях i-и разряд логического вектора передается без изменений,

Значение i-ro разряда информационного вектора в j-M столбце определяется по следующему правилу. разряд логического вектора изменился с единицы на нуль, то г-й разряд информационного вектора j-ro столбца обнуляется; если i-и разряд логического вектора изменился с нуля на едиЯчейка содержит синхровход 1,nep-1j5 ЧУ то i-му разряду информационно- вый и второй информационные входы 2 го вектора j-ro столбца присваивается и 3, логические входы 4-6, функцио-значение (i-l)-ro разряда инфо1мацинальные выходы 7 и 8, триггер 9, эле- онного вектора (j-1)-ro столбца; если мент НЕ 10, триггер 11, элемент ИЛИзначение i-ro разряда логического век12, элемент НЕ 13, элемент И 14, эле-2о ™Р следующий столбец передается мент ИЛИ 15, элементы И 16-18 и элемент НЕ 19.

Функционально ячейка вьшолняет вычисления следующих логических функций:

без изменения, то значение 1-го разряда информационного вектора в следующий столбец передается без изменений.

Таким образом, в каждом тшсте в 25 очередной столбец устройства переписывается логический вектор, в котором все единицы, под которыми были нули, опустятся на одну строку. Одновременно с этим на одну строку опускаются соответствующие единичным разрядам логического вектора и значения информационного вектора.

Z - J Qx х s 1

.- 5Таким образом, в каждом тшсте в 25 очередной столбец устройства переписывается логический вектор, в котором все единицы, под которыми были нули, опустятся на одну строку. Одновременно с этим на одну строку опускаются соответствующие единичным разрядам логического вектора и значения информационного вектора.

В результате через (т-1) такт работы устройства происходит сжатие тп-мер- ного двоичного вектора. Результат ежа

х

Z J ГСх XjVXj X,.) где Z ,, и Z 2 соответственно значения

сигналов на выходах 7 jO и 8 ячейки;

- соответственно значения сигналов на выходах 2-6 ячейки.

Устройство, построенное на базе ,,

I я чеек, обеспечивает вьшолнение опера- тия информационного вектора снимает- I ций сжатия двоичных векторов. В про- , I цессе работы устройства исходный ин- j формационный вектор подается на входы 2 и 3 ячейки первого столбца, причем, Q устройства информационный и логичес- i-и разряд вектора подается на вход кий векторы передаются в соседний 2 (i , 1 ) ячейки и вход 3 (i + 1,1) справа столбец ячеек матрицы на вход ячейки. Логический вектор подается на входы 4-6 ячеек первого столбца, причем i-и разряд вектора подается на 5 информационных векторов. Таким обра- вход 6(i 1 )ячейки и вход 6(1 - 1,1) У зом, устройство реализует конвейерный ячейки. В. каждом такте на тактирующие входы триггеров подается синхроимпульс. В результате двоичные векторы (информационный и логический) переда- JQ элементов состоит из первого элемен- ются в преобразованном виде в сосед- та НЕ, четвертого элемента И, второго НИИ справа столбец. Значение i-ro элемента ИЛИ и третьего элемента НЕ, разряда логического вектора в J-M Таким образом, время задержки распро- столбце при этом определяется значе- странения сигнала в наиболее длинной ниями (i-l)-ro, i-ro,(i + 1)-го разря-, цепочке элементов составляет время дов логического вектора в (j-l)-M 4t, где t - время задержки сигнала столбце; единица переходит в нуль, одним логическим элементом. В резуль- если (i +1)-й разряд логического век- тате без нарушения правильности ра- тора в (j-l)-M столбце был разен ну- боты устройства допустш-ю поступлеся с выхода 7 ячеек последнего столбца устройства.

Поскольку на каждом такте работы

устройства на каждом такте могут быть поданы следующие пары логических и

принцип обработки информации.

В данной ячейке наиболее длинная цепочка последовательно включенных

лю; нуль переходит в единицу, если 0.-1)-й разряд логического вектора в (j-l)-M столбце содержит единицу; в остальных случаях i-и разряд логического вектора передается без изменений,

Значение i-ro разряда информационного вектора в j-M столбце определяется по следующему правилу. разряд логического вектора изменился с единицы на нуль, то г-й разряд информационного вектора j-ro столбца обнуляется; если i-и разряд логического вектора изменился с нуля на еди™Р следующий столбец передается

без изменения, то значение 1-го разряда информационного вектора в следующий столбец передается без изменений.

Таким образом, в каждом тшсте в очередной столбец устройства переписывается логический вектор, в котором все единицы, под которыми были нули, опустятся на одну строку. Одновременно с этим на одну строку опускаются соответствующие единичным разрядам логического вектора и значения информационного вектора.

В результате через (т-1) такт работы устройства происходит сжатие тп-мер- ного двоичного вектора. Результат ежа

тия информационного вектора снимает- устройства информационный и логичес- кий векторы передаются в соседний справа столбец ячеек матрицы на вход информационных векторов. Таким обра- зом, устройство реализует конвейерный элементов состоит из первого элемен- та НЕ, четвертого элемента И, второго элемента ИЛИ и третьего элемента НЕ, Таким образом, время задержки распро- странения сигнала в наиболее длинной цепочке элементов составляет время 4t, где t - время задержки сигнала одним логическим элементом. В резуль- тате без нарушения правильности ра- боты устройства допустш-ю поступлеся с выхода 7 ячеек последнего столбца устройства.

Поскольку на каждом такте работы

тия информационного вектора снимает- устройства информационный и логичес- кий векторы передаются в соседний справа столбец ячеек матрицы на вход информационных векторов. Таким обра- зом, устройство реализует конвейерный элементов состоит из первого элемен- та НЕ, четвертого элемента И, второго элемента ИЛИ и третьего элемента НЕ, Таким образом, время задержки распро- странения сигнала в наиболее длинной цепочке элементов составляет время 4t, где t - время задержки сигнала одним логическим элементом. В резуль- тате без нарушения правильности ра- боты устройства допустш-ю поступлеустройства на каждом такте могут быть поданы следующие пары логических и

тия информационного вектора снимает- устройства информационный и логичес- кий векторы передаются в соседний справа столбец ячеек матрицы на вход информационных векторов. Таким обра- зом, устройство реализует конвейерны элементов состоит из первого элемен- та НЕ, четвертого элемента И, второг элемента ИЛИ и третьего элемента НЕ, Таким образом, время задержки распро странения сигнала в наиболее длинной цепочке элементов составляет время 4t, где t - время задержки сигнала одним логическим элементом. В резуль тате без нарушения правильности ра- боты устройства допустш-ю поступлепринцип обработки информации.

В данной ячейке наиболее длинная цепочка последовательно включенных

5151

ние на синхронизирующий вход ячейки сигнала синхронизации через время 4t, т.е. на время раньше, чем в известной ячейке. Так как для формирования конечного результата преобразования двоичного вектора требуется (т-1) тактов работы устро.йства, то соответственно предлагаемая ячейка по сравнению с известной будет работать на время (m-1)t быстрее, где m - число строк в матрице ячеек устройства.

Формула изобретения

Ячейка однородной вычислительной среды, содержащая три элемента НЕ, два элемента ИЛИ, четыре элемента И, два триггера, синхровход ячейки соединен с синхроводами первого и второго триггеров, выходы которых соединены с первым и вторым выходами ячейки соответственно, первый информационный вход которой соединен с первым входом первого элемента И, выход которого со единен с первым входом первого элемен та ШШ, выход которого соединен с входом установки первого триггера и вхо- .дом первого элемента НЕ, вькод которого соединен с входом сброса первого триггера, второй информационный

16

вход ячейки соединен с первым входом второго элемента И, выход которого соединен с вторым входом первого элемента ШТИ, первьм логический вход

ячейки соединен с первым входом треть - его элемента И, выход которого соединен с первым входом второго элемента ШШ, выход которого соединён с входом установки второго триггера и входом второго элемента НЕ, выход которого соединен с входом сброса второго триггера, второй логический вход ячейки соединен с первым входом чет- вертого элемента И, выход которого соединен с вторым входом первого элемента И ивторым входом второго элемента ИЛИ, третий логический вход ячейки соединен с вторым входом четвертого элемента И и входом третьего элемента НЕ, выход которого соединен с вторым входом третьего элемента И, о т- личающаяся тем, что, с целью повьшения быстродействия за счет сокращения числа элементов в цепи рас- - пространения управляющего сигнала, первый логический вход ячейки соединен с вторым входом второго элемента И, вьпсод третьего элемента НЕ сое- ,

динен с третьим входом: второго элемента И,

BJ(

Л|, V- v

Др-JгЧ

вш.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сжатия двоичных векторов | 1985 |

|

SU1256041A1 |

| ЯЧЕЙКА ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ И УСТРОЙСТВО ДЛЯ СЖАТИЯ ДВОИЧНЫХ ВЕКТОРОВ НА БАЗЕ ЯЧЕЕК ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ | 2011 |

|

RU2450327C1 |

| ЯЧЕЙКА ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ, ОДНОРОДНАЯ ВЫЧИСЛИТЕЛЬНАЯ СРЕДА И УСТРОЙСТВО ДЛЯ КОНВЕЙЕРНЫХ ВЫЧИСЛЕНИЙ СУММЫ м n-РАЗРЯДНЫХ ЧИСЕЛ | 2011 |

|

RU2475815C1 |

| Устройство для сжатия векторов | 1987 |

|

SU1425704A1 |

| Устройство для сжатия двоичных векторов | 1980 |

|

SU943739A1 |

| Ячейка однородной структуры | 1986 |

|

SU1335975A2 |

| Многофункциональное вычислительное устройство | 1985 |

|

SU1293727A1 |

| Ячейка однородной среды | 1986 |

|

SU1372322A1 |

| Ячейка однородной структуры | 1988 |

|

SU1501035A2 |

| ЯЧЕЙКА ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ | 2004 |

|

RU2284568C2 |

Изобретение относится к автоматике и вычислительной технике и предназначено для применения в устройстве для сжатия двоичных векторов и других системах логической обработки информации. Цель изобретения - повышение быстродействия ячейки за счет сокращения числа элементов в цепи распространения управляющего сигнала. Для достижения цели в ячейку, содержащую синхровход 1, первый 2 и второй 3 информационные входы, логические входы 4-6, первый 7 и второй 8 функциональные выходы, триггеры 9, 11, элементы НЕ 10, 13, 19, элементы И 14, 16-18, элементы ИЛИ 12, 15 с соответствующими связями, введены две новые связи. 2 ил.

VIUZ.I

| Устройство для сжатия двоичных векторов | 1980 |

|

SU943739A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сжатия двоичных векторов | 1985 |

|

SU1256041A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-10-07—Публикация

1987-11-30—Подача