Изобретенц,е относится к специаль- ным устройствам для обработки инфор- нации в ЦВМ, устройствам матричных или векторных вычислений, устройства перевода с одного языка на другой.

Цель изобретения - расширение функциональных возможностей за счет снятия ограничений на разрядность компонент информационного вектора

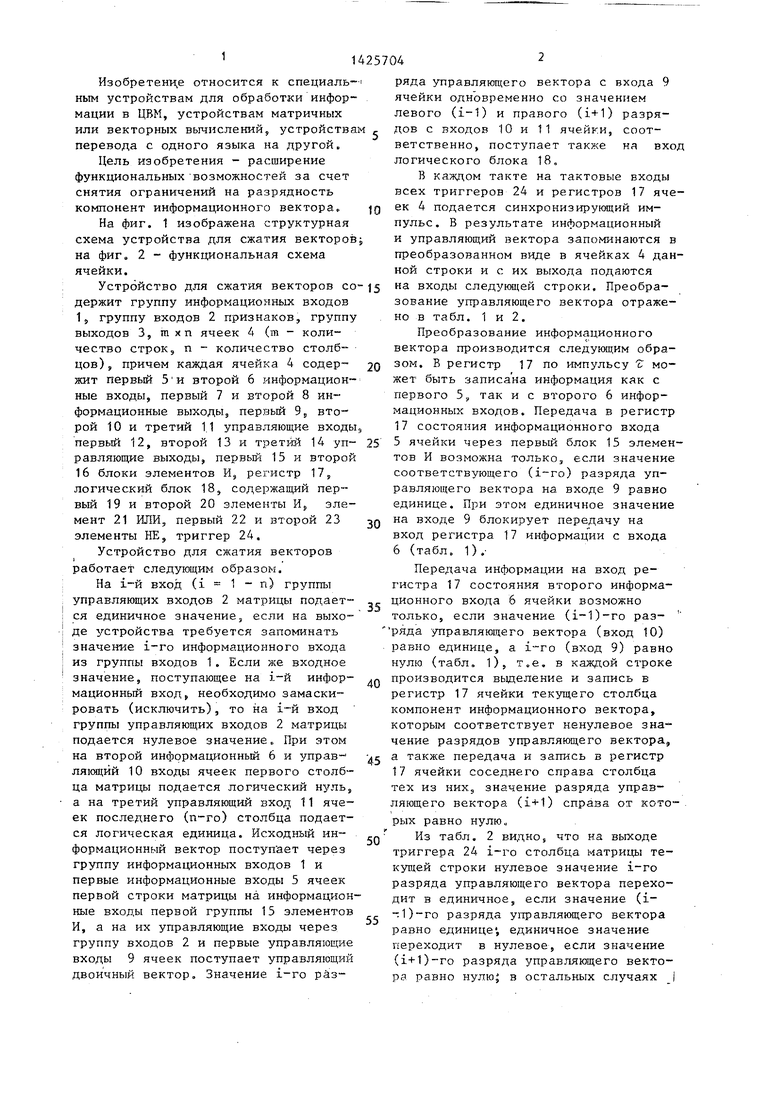

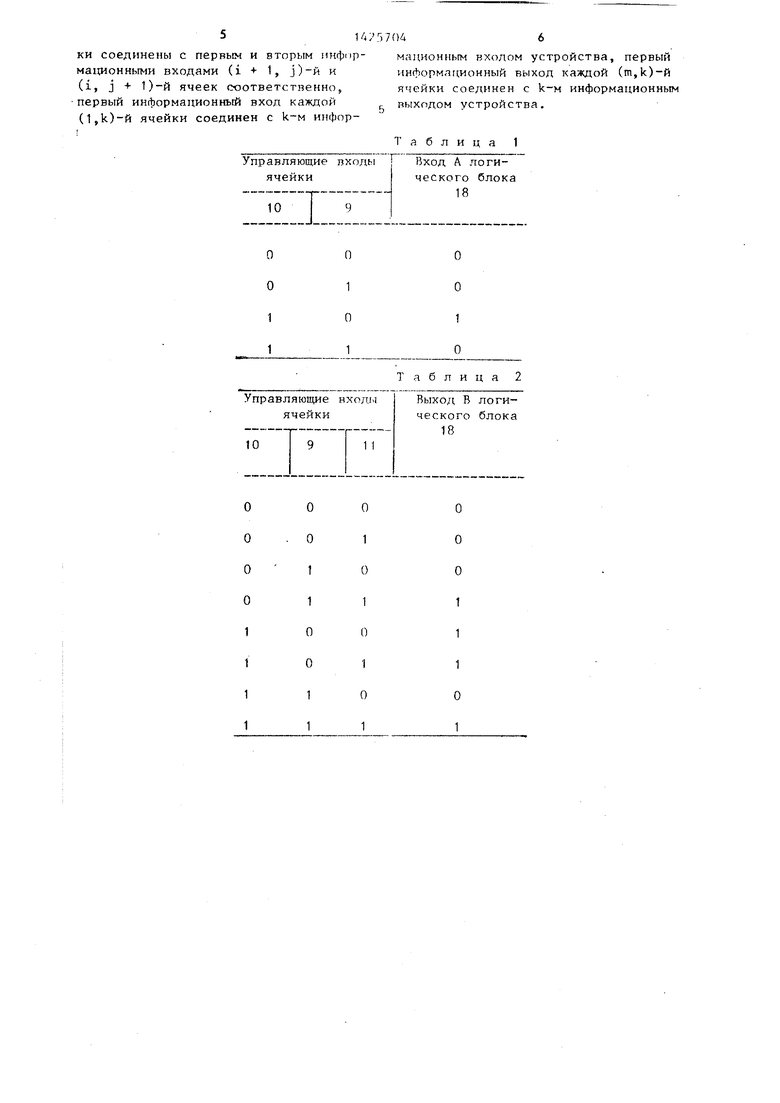

На фиг. 1 изображена структурная схема устройства для сжатия векторов на фиг, 2 - функциональная схема ячейки.

Устройство для сжатия векторов со держит группу информационных входов 1, группу входов 2 признаков, группу выходов 3, га хп ячеек 4 (т - количество строк, п - количество столбцов) , причем каждая ячейка 4 содар- жит первый 5 и второй 6 информационные входы, первый 7 и второй 8 информационные выходы, первый 9, второй 10 и третий и управляющие входы

первый 12, второй 13 и третий 14 управляющие выходы, первый 15 и второй 16 блоки элементов И рег истр 17, логический блок 18, содержащий первый 19 и второй 20 элементы И, элемент 21 ИЛИ, первый 22 и второй 23 элементы НЕ, триггер 24.

Устройство для сжатия векторов

I

работает следующим образом.

На i-й вход (i 1 - п) группы управляющих входов 2 матрицы подается единичное значение, если на выходе устройства требуется запоминать значение i-ro информационного входа из группы входов 1. Если же входное значение, поступающее на i-й информационный вход, необходимо замаскировать (исключить), то на 1--й вход группы управляющих входов 2 матрицы подается нулевое значение. При этом на второй информационный 6 и управ- лякмцйй 10 входы ячеек первого столбца матрицы подается логический нуль, а на третий управляющий входт; 11 ячеек последнего (п-го) столбца подается логическая единица. Исходный информационный вектор поступает через группу информационных входов 1 и первые информационные входы 5 ячеек первой строки матрицы на информационные входы первой группы 15 элементов И, а на их управляющие входы через группу входов 2 и первые управляющие входы 9 ячеек поступает управляющий двоичный вектор. Значение i-ro рйз , дов

g

5 0

5

0

5

0

5

0

5

ряда управляюа его вектора с входа 9 ячейки одновременно со значением левого (i-1) и правого (i+1) разряс входов 10 и 11 ячейки, соответственно, поступает также на вход логического блока 18.

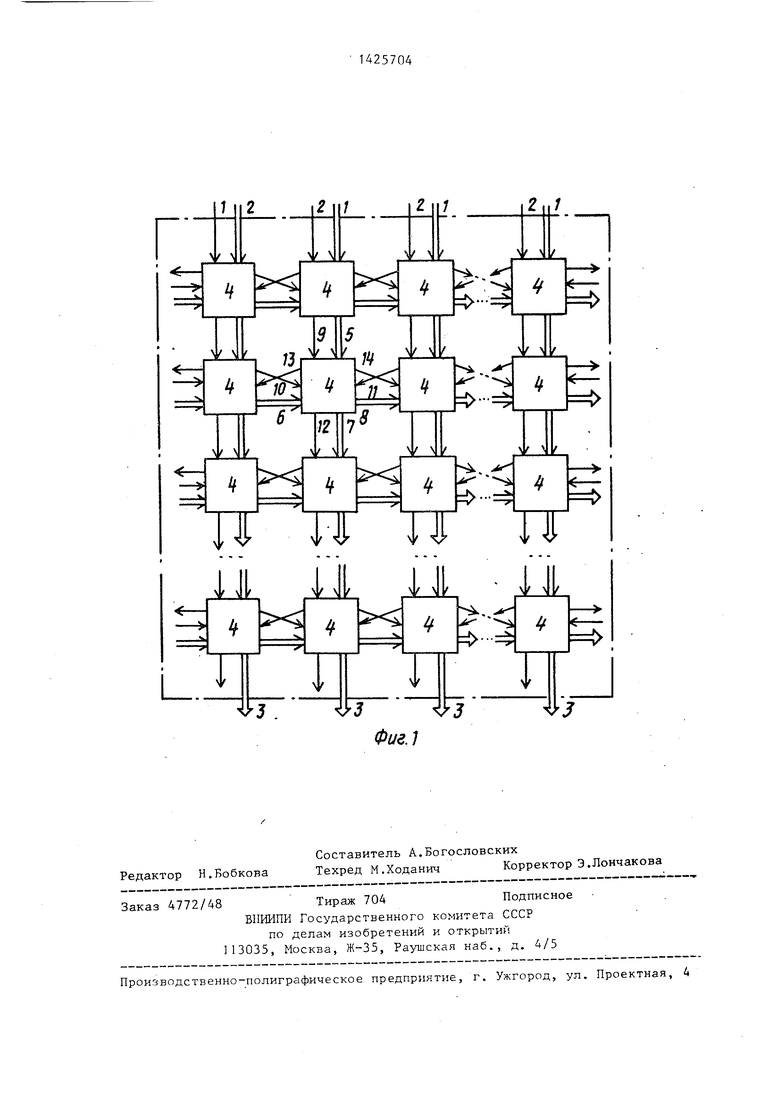

В каждом такте на тактовые входы всех триггеров 24 и регистров 17 ячеек 4 подается синхронизирующий импульс. В результате информационный и управляющий вектора запоминаются в преобразованном виде в ячейках 4 данной строки и с их выхода подаются на входы следующей строки. Преобразование управляющего вектора отражено в табл. 1 и 2.

Преобразование информационного вектора производится следующим образом. В регистр 17 по импульсу 1 может быть записана информация как с первого 5, так и с второго 6 инфор- мацтлоннык входов. Передача в регистр 17 состояния информационного входа

5ячейки через первый блок 15 элементов И возможна только, если значение соответствующего () разряда управляющего вектора на входе 9 равно единице. При этом единичное значение на входе 9 блокирует передачу на вход регистра 17 информации с входа

6(табл. 1).Передача информации на вход регистра 17 состояния второго информационного входа 6 ячейки возможно только, если значение (i-1)-го раз- ряда управляющего вектора (вход 10) равно единице, а i-ro (вход 9) равно нулю (табл. 1), т.е. в каждой строке производится вьщеление и запись в регистр 17 ячейки текущего столбца компонент информационного вектора, которым соответствует ненулевое значение разрядов управляющего вектора, а также передача и запись в регистр 17 ячейки соседнего справа столбца тех из них, значение разряда управ- ля ощего вектора () справа от кото-, рых равно нулю„

Из табл. 2 видно, что на выходе триггера 24 i-ro столбца матрицы текущей строки нулевое значение 1-го разряда управляющего вектора переходит в единичное, если значение (i- -1)-го разряда управляющего вектора равно единице , единичное значение переходит в нулевое, если значение (i+1)-го разряда управляющего вектора равно нулю; в остальных случаях |

значение управляющего вектора записывается без изменений.

Таким образом, в каждом такте в очередную строку переписываются информационный и управляющий векторы, преобразованные таким образом, что ненулевые компоненты этих векторов сдвигаются вправо на одну позицию на место нулевых компонент. Очевидно что за п тактов (в наихудшем слу-- чае) выполняется сжатие п-мерного информационного вектора. При этом результат сжатия оказывается в регистрах 17 строки и на выходах 3 матриш.

Последовательное сжатие множества информационных векторов выполняется устройством в конвейерном режиме следующим образом.

Поскольку во втором такте частично преобразованные информационный и управляющий вектора передаются во вторую строку, на информационный 1 и управляющий 2 входы устройства мо- гут быть поданы следуклцие информационный и управляющий векторы, В третьем такте первые информационный и управляющий векторы передаются в третью строку, вторые инфор.мацион- ный и управляюпщй векторы передаются во вторую строку, и на информационны 1 и управляющие 2 входы могут быть поданы третий информационный и уп- равляю1ций векторы и т.д. Начиная с п-го тракта, с выходов 3 матрицы последовательно с интервалом € выдаются результаты сжатия первого, второго и других информационных векто- ров.

Формула изобретения

Устройство для сжатия векторов, содержащее матрицу ячеек из m строк и п столбцов, причем каждая ячейка содержит два жлемента И, элемент ШШ, два элемента НЕ и триггер, выход которого является первым управляющим выходом ячейки, первый управляющий вход которой соединен с вторым и третьим управляюощми выходами ячейкР, первым входом первого элемента И, входом первого элемента НЕ, выход которого соединен с первым входом второго элемента И, выход которого соединен с первым входом элемента ШТИ, выход которого соединен с входом установки триггера и входом

Q 5

0

5- Q

5

0

5

0

5

704

второго элемента ПК, выход которого соединен с входом cfipoca триггера, синхровход которого соединен с синх- ровходом ячеГжи, второй управляющий вход которой соединен с вторым входом второго элемента И, третий уп- равляющ1да вход ячейки соединен с вторым входом первого элемента И, выход которого соединен с вторым входом элемента ИЛИ, первый управляющий выход (i, з)-й ячейки (i 2, m - 1, j 2, п - О соединен с первым управляющим входом (i + 1, j)-й ячейки, второй управляющий выход (i, )й ячейки соединен с третьим управляющим входом (i, j - 1)-й ячейки, третий управляюицш выход которой соединен с вторым управляющим входом (i, )-й ячейки, третий управляклций выход которой соединен с вторым управляющим входом (i, j + 1)-й ячейки, второй управляющий выход которой соединен с третьим управляющим входом (1,)-й ячейки, первый управлягаций выход (i - 1, j)fi ячейки соединен с первым управляющим входом (i, з)й ячейки, первьв управляющий вход (1, k)-H ячейки (k 1, п) соединен с k-M управляющим входом устройства, отличающееся тем, что, с целью расширения функциональных возможностей за счет исключения ограничений на разрядность компонент информационного вектора, в каждую ячейку матрицы введены два блока элементов И и регистр, информационный выход которого соединен с первым информационным выходом ячейки, первый информационный вход которой соединен с первым входом первого блока элементов И, выход которого соединен с информационным входом регистра, выходом второго блока элементов И и вторым информационным выходом ячейки, второй информационный вход которой соединен с первым входом второго блока элементов И, второй вход которого соединен с выходом второго элемента И, первый управляющий вход ячейки соединен с вторым входом первого блока элементов И, вход записи регистра соединен с синхровходом ячейки, первый и второй информационные входы (L, )-й ячейки соединены с первым и вторым информационными выходами (i- 1, j)-йи (i, j - 1)-й ячеек соответственно, первый и второй информационные выходы (i, )-й ячей514737046

ки соединены с первым и вторым инфпр- мадионньгм входом устройства, первый мационными входами (i 1, j)-A и информлционный выход каждой (m,k)-ft

(i, j + 1)й ячеек соответственно, первый информационный вход каждой (1,и)-й ячейки соединен с k-м инфорячейки соединен с k-м информационным ( выходом устройства.

ячейки соединен с k-м информационным ( выходом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для редактирования таблиц | 1989 |

|

SU1711184A1 |

| Способ и матричное устройство параллельно-конвейерного поиска по образцу | 2022 |

|

RU2789997C1 |

| Матричное устройство для параллельного поиска вхождений и обработки данных | 2021 |

|

RU2762781C1 |

| УСТРОЙСТВО ДЛЯ ПАРАЛЛЕЛЬНОГО ПОИСКА ВХОЖДЕНИЙ И ПЕРЕСЕЧЕНИЙ СЛОВ | 2010 |

|

RU2430408C1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Матричное устройство для быстрого поиска вхождений и обработки данных | 2022 |

|

RU2787742C1 |

| Ячейка однородной вычислительной среды | 1987 |

|

SU1513471A1 |

| Устройство для сжатия двоичных векторов | 1985 |

|

SU1256041A1 |

| ЯЧЕЙКА ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ И УСТРОЙСТВО ДЛЯ СЖАТИЯ ДВОИЧНЫХ ВЕКТОРОВ НА БАЗЕ ЯЧЕЕК ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ | 2011 |

|

RU2450327C1 |

| СИСТЕМА ДЛЯ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ С ИСПРАВЛЕНИЕМ ОШИБОК | 1991 |

|

RU2007042C1 |

Изобретение относится к автоматике и вычислительной технике. Цель изобретения - расширение функциональ9 13 ных возможностей за счет исключения ограничений на разрядность компонент информационного вектора. Для достижения поставленной цели в устройство для сжатия векторов, содержащее мат-i рицу ячеек из m строк и п столбцов, причем каждая ячейка содержит логический блок 18, содержащий два элемента И 19, 20, элемент ИЛИ 21, два элемента НЕ 22, 23, триггер 24, ячейки 4 связаны в матрицу управляющими связями 9-14, введены в каждую ячейку два блока 15, 16 элементов И, регистр 17 и; информационные связи 5-8. 2 ил., 2 табл. (Л

Управляющие входы ячейки

10

О О 1 1

п 1

о 1

Управляющие входи ячейки

о о

1 о о 1 1

Таблица 1 Вход А логического блока 18

о о 1 о

Таблица 2

Выход В логического блока 18

о о о 1 1 1

о 1

Фие.1

| Многоканальное устройство для редактирования | 1984 |

|

SU1211759A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сжатия двоичных векторов | 1985 |

|

SU1256041A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-09-23—Публикация

1987-03-23—Подача