шинами; на фиг.5 - временные диаграммы сигналов, пояснящие работу устройства.

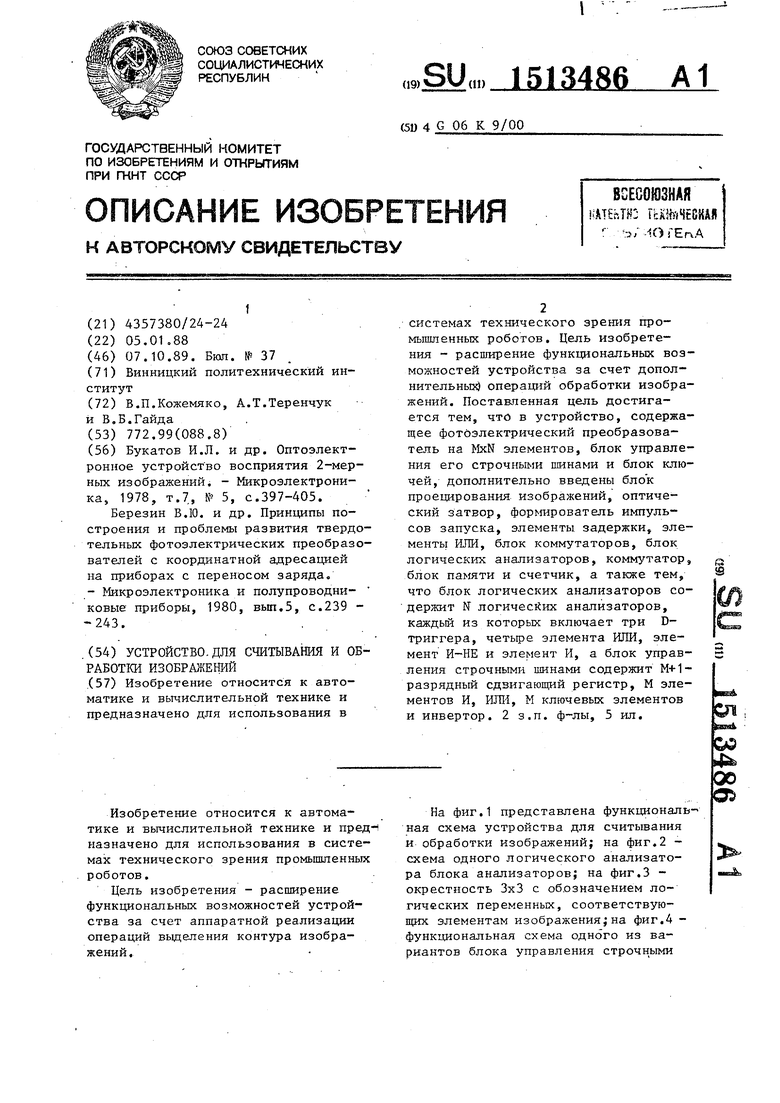

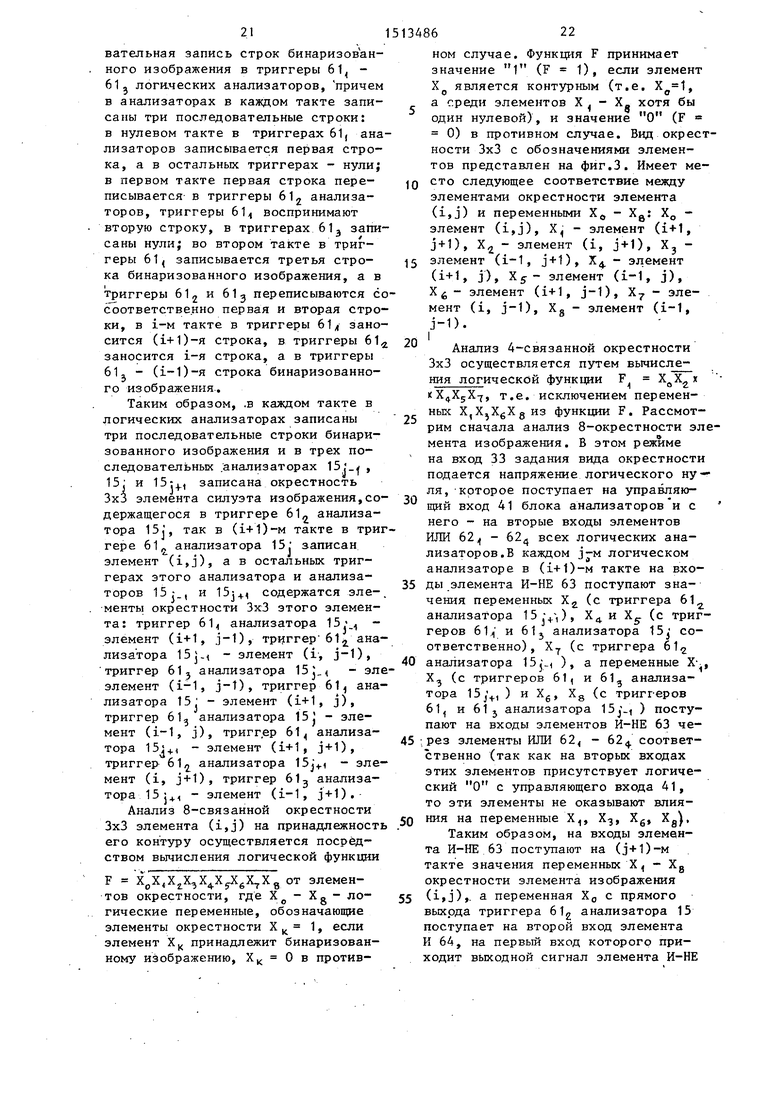

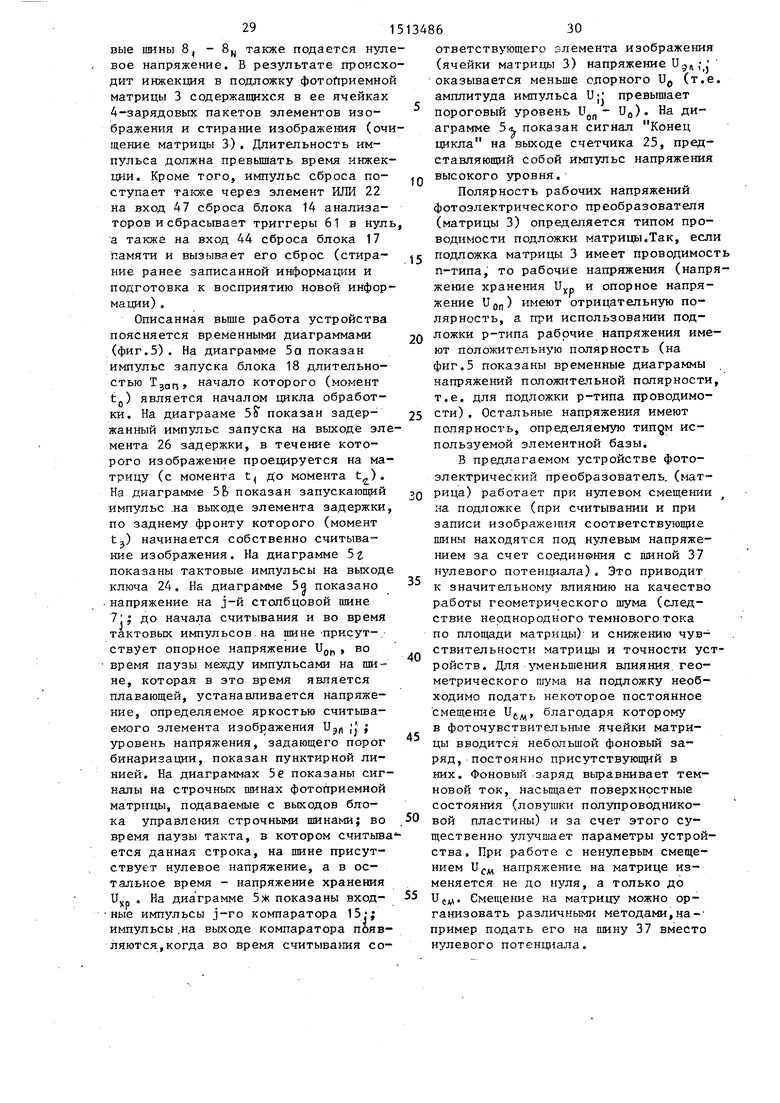

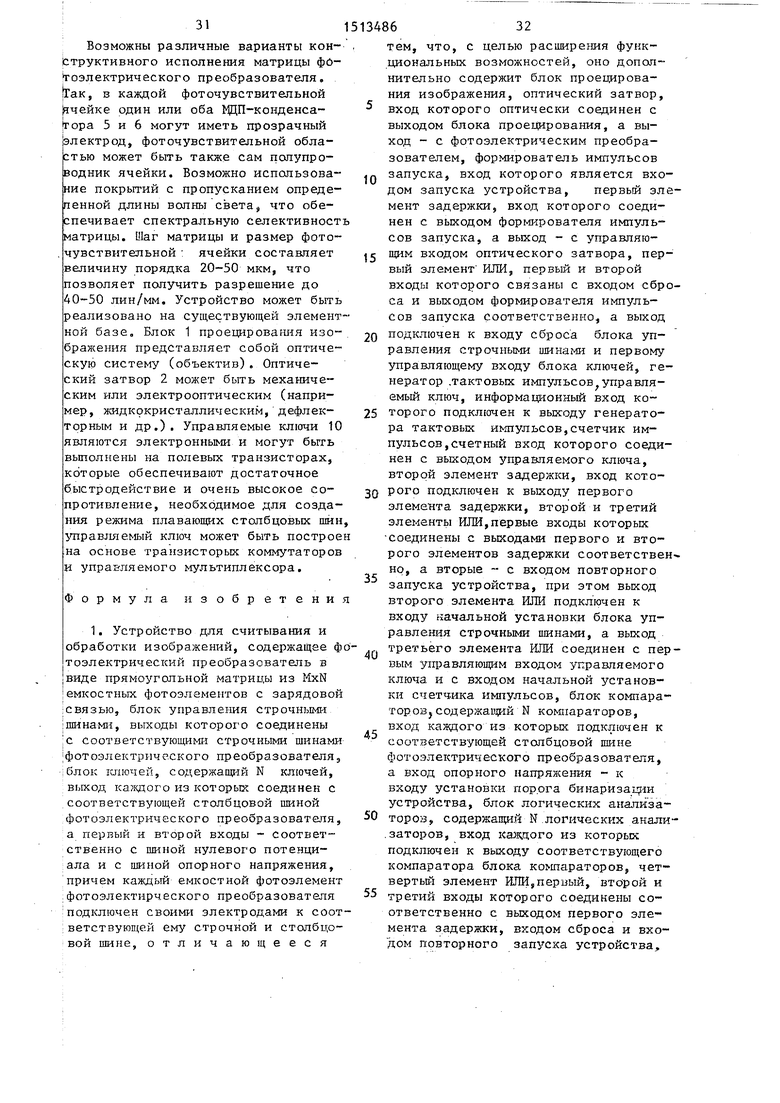

Устройство (фиг.1) содержит блок 1 проецирования изображения, оптический затвор 2, фотоэлектрический преобразователь 3 в виде прямоугольной матрицы емкостных фотоэлементов с переносом заряда из М строк и N столбцов, каждый элемент (ячейка) 4 которой состоит из двух 1Ф1П-КОН- денсаторов 5 и 6, между которыми существует зарядовая связь, причем электрод первого ВДП-конденсато- ра 5 соединен с соответствующей строчной пшной 7, а второго МДП-кон- денсатора 6 - с соответствующей столбцовой шиной 8, блок 9 управляемых ключей, содержащий N ключей, 10 - 10у, блок 11 управления строчными шинами, блок 12 компараторов, состоящий из N компараторов 13 - 13 блок 14 логических анализаторов, содержащий. N логических анализаторов , коммутатор 16, блок 17 памяти, формирователь 18 импульсов запуска, первый 19, второй 20, третий 21 и четвертый 22 элементы ИЛИ, генератор 23 тактовых импульсов, управляемый ключ 24, счетчик 25 импульсов первый 26, второй 27 и третий 28 элементы задержки, вход 29 начального запуска, вход 30 повторого запуска, вход 31 сброса, вход 32 установки порога бинаризации, вход 33 задания вида окрестности, группу 34 выходов сигналов бинарного препарата (силуэта) , выход 35 сигнала Конец цикла, выход 36 устройства.

Входом устройства является оптический вход блока 1 проецирования изображений, выход которого через оптический затвор 2 оптически соединен с входом фотоэлектрического преобразователя 3. Каждая ячейка 4 фотоприемной матрицы 3 содержит два ЩП-конденсатора 5 и 6, между кото- рьпчи имеется зарядовая связь.Между соседни 1и ячейками матрицы зарядовая связь отсутствует. Электрод ЩП-конденсатора 5 ячейки 4;: соединен с i-й строчной ииной 7j , а электрод ВДП-конденсатора 6 ячейки 4 - с j-й столбцовой шиной 8. Каждая столбцовая шина 8j подключена к выходу j-ro ключа 10 , входящего в блок 9 управления ключей, и

0

5

0

5

0

5

0

5

0

5

к входу j-ro компаратора 13 блока 12 компараторов. При этом столбцовые шины матрицы 3 являются плавающими. Первый контакт каждого ключа 10 соединен с шиной 37 нулевого потенциала, а второй - с шиной 38 опорного напряжения так, что ключ может находиться в одном из трех состояний: или выход соединен с шиной 37 нулевого потенциала, или с пиной 38 опорного потенциала, или ключ разомкнут. Каждая i-я строчная-шина 7 фотоприемной- матрицы 3 подключена к i-му выходу блока управления строчными шинами 11, Выход каждого компаратора 13i блока 12 соединен с входом JTo логического анализатора 15- блока 14 анализаторов и с J-M вькодом в группе 34 выходов сигналов бинарного силуэта. Вход 39 опорного напряжения блока 12 компараторов соединен с входом 32 установки порога бинаризации, и к нему подключены входы опорного напряжения всех компараторов 13 - 13,. Выход каждого логического анализатора 15j блока 14 соединен с J-M управляющим входом 40: коммутатора 16, а управляющий вход 41 блока 14 анализаторов подключен к входу 33 вида окрестности. Каждый выход 42 коммутатора 16 соединен с соответствующим J-M входом блока 17 памяти, выход которого является выходом 36 устройства. Вход формирователя 18 импульсов зацуска подключен к входу 29 начального запуска устройства, а его выход соединен с одним входом элемента ШШ 19 и с входом элемента 26 задержки, выход которого соединен с первым входом элемента ИЛИ 20, с входом элемента 27 задержки, с первым входом элемента ШШ 22 и С управляющим входом 43 оптического затвора 2. Другой вход элемента ИЛИ 19 соединен с входом 31 сброса устройства, к которому подключены также второй вход элемента ШШ 22 и вход 44 сброса блока 17 памяти. Выход элемента ИЛИ 19 соединен с входом 45 сброса блока 11 угфавле- ния строчными шинами и с первым управ- ляюшим входом 46 блока 9 ключей,Вход 30 повторного запуска устройства соединен с вторыми входами элементов ИЛИ 21 и 20 и с третьим входом элемента РШИ 22, выход которого связан . с входом 47 сброса блока 14 анализа5

торов. Выход элемента ИЛИ 20 подключен к входу 48 начальной установки блока 11 управления строчными шинами Выход генератора 23 тактовых импульсов подключен к входу управляемого ключа 24, выход которого связан со счетным входом 49 счетчика импульсов 25. Первый управляющий вход 50 ключа 24 и вход 51 сброса счетчика 25 соединены с выходом элемента РШИ 21, Первый выход 52 счетчика 25 подключен к информационному входу 53 коммутатора 16, а его второй выход

54- к второму управляющему входу

55ключа 24 и к выходу 35 сигнала Конец цикла. Выход ключа 24 соединен с тактовым входом 56 блока 11 управления строчными шинами, с вторым управляющим входом 57 блока 9 ключей и с входом элемента 28 задержки, выход которого подключен к тактовым управляюш 1м входам 58 и 59 соответственно блока 14 анализаторов

и блока 17 памяти. Вход 60 блока 11 управления строчными шинами соединен

с шиной напряжения хранения U

хр

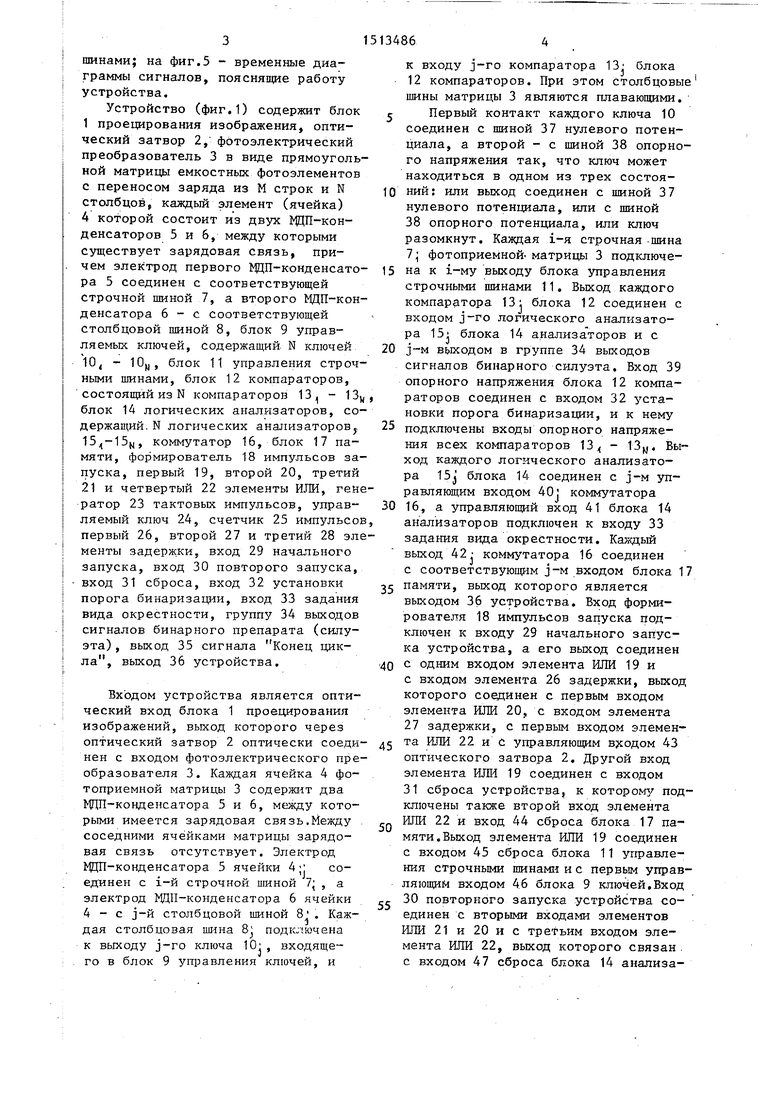

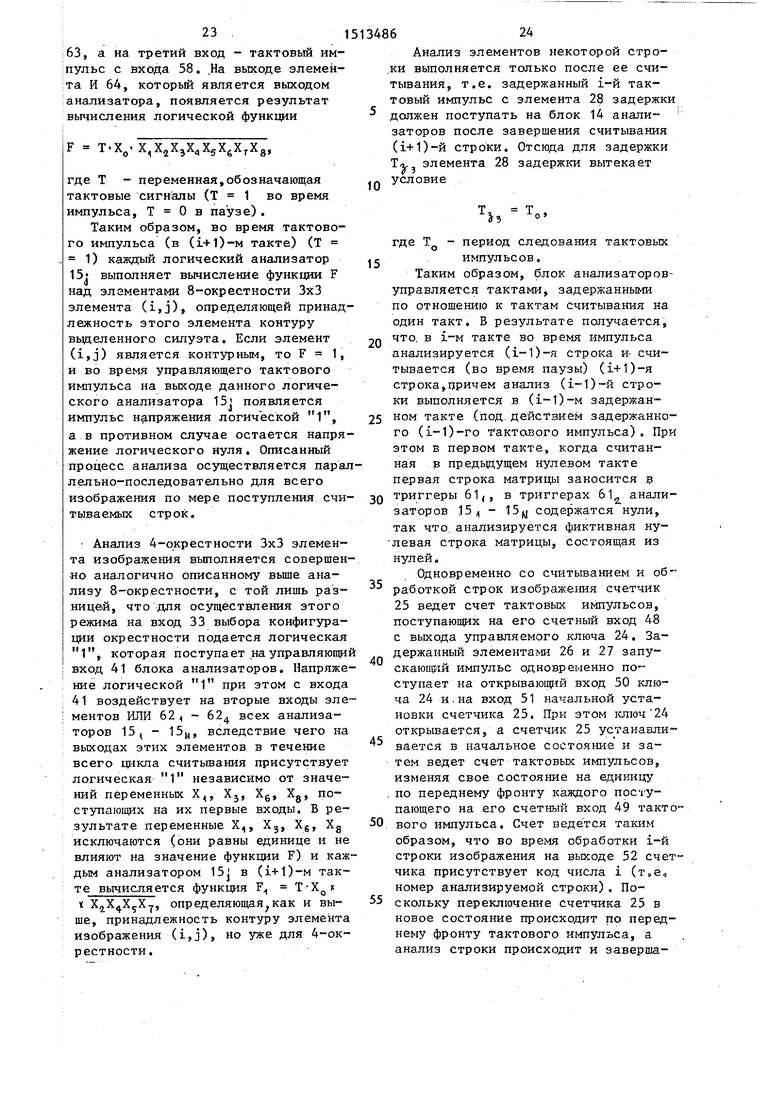

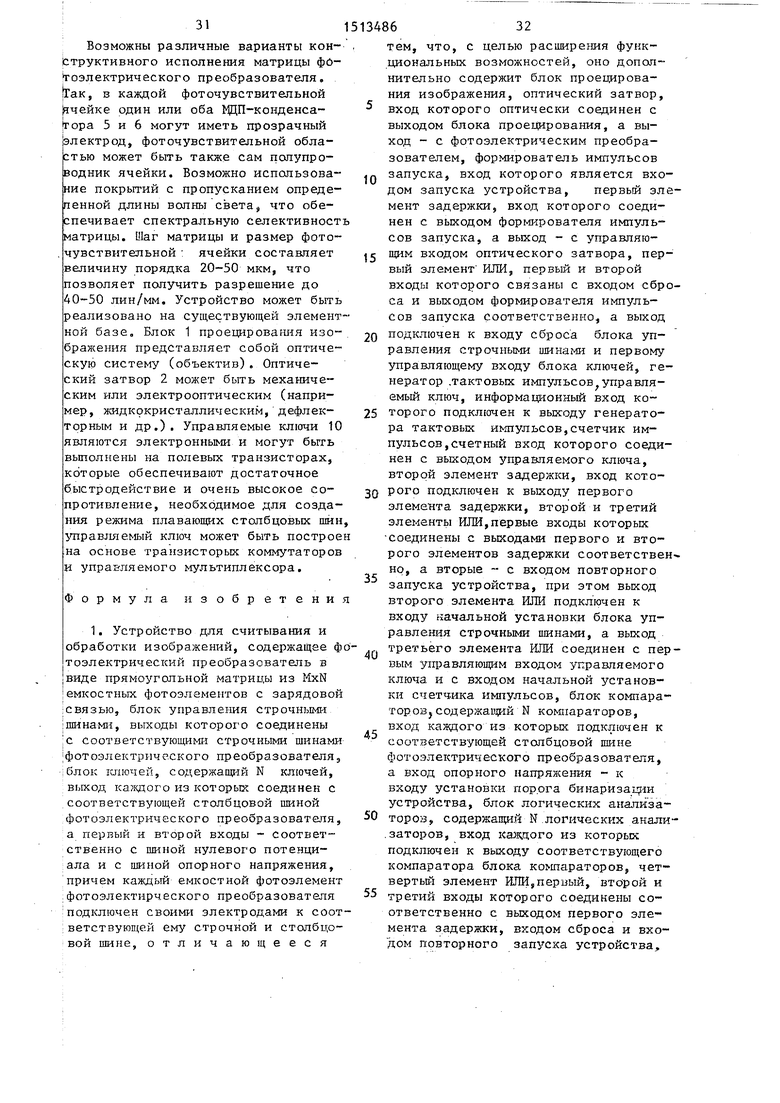

Логический анализатор 15 блока 14 (фиг.2) содержит первый 61,, второй 61„ и третий 613 D-триггеры, че тьтре элемента ИЛИ 62 i - 62, элемент И-НЕ 63 и элемент И 64. Информационный D-вход триггера 61 является входом логического анализатора (он подключается к выходу соответствую- ш,его компаратора 13 блока компарато- ров), а его прямой выход соединен с D-входом триггера 61 и с одним из входов элемента И-НЕ 63. R-.входы ус- тановк и нуля триггеров 61 - 61 j со- единены с входом 47 сброса блока анаизаторов. Выход элемента И-НЕ 63 соединен с первым входом элемента И 64, выход которого является выходом логического анализатора. Второй вход элемента И 64 соединен с прямым выходом триггера 612, которому подключен также D-вход триггера 61. Третий вход элемента И 64 соединен с тактовым входом 58 блока анализаторов, к которому подсоединены также синхронизирующие С-входы триггеров 61, - 61. Вторые входы элементов ЛИ 62 - 62J объединены и подключены к управляющему входу 41 блока анаизаторов, В анализаторе 15: первый вход элемента И-НЕ 63 соединен с пря ым выходом D-триггера 61 соседнего анализатора 15( , второй вход - с

134866

выходом элемента 62 , третий вход - с выходом элемента ИЛИ 62,, четвер- тый вход - с прямым выходом D-триггера 61, этого же анализатора, пя- тый вход - с прямым выходом D-триггера 61 этого же анализатора, шестой вход - с выходом элемента ИЛИ 62,, седьмой вход - с выходом мента ИЛИ 62, восьмой вход - с прямым выходом D-триггера 61 соседнего логического анализатора 15.., . При этом первые входы элементов 62 и 62 анализатора 15; соединены соот15 ветственно с прямыми-вькодами триггеров 61t и 615 соседнего логического анализатора 15j- , а первые входы его элементов 62 и 62 соединены соответственно с прямыми выхо2Q дани D-триггеров 61 и 61 соседнего логического анализатора 15.,,

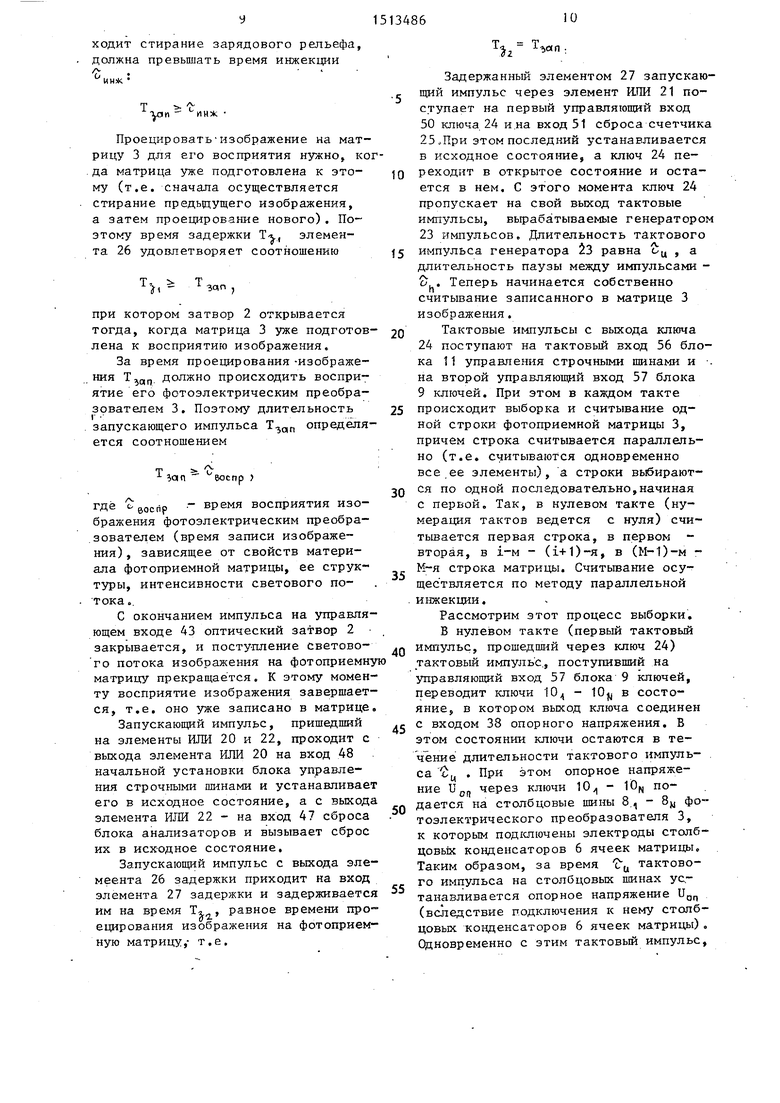

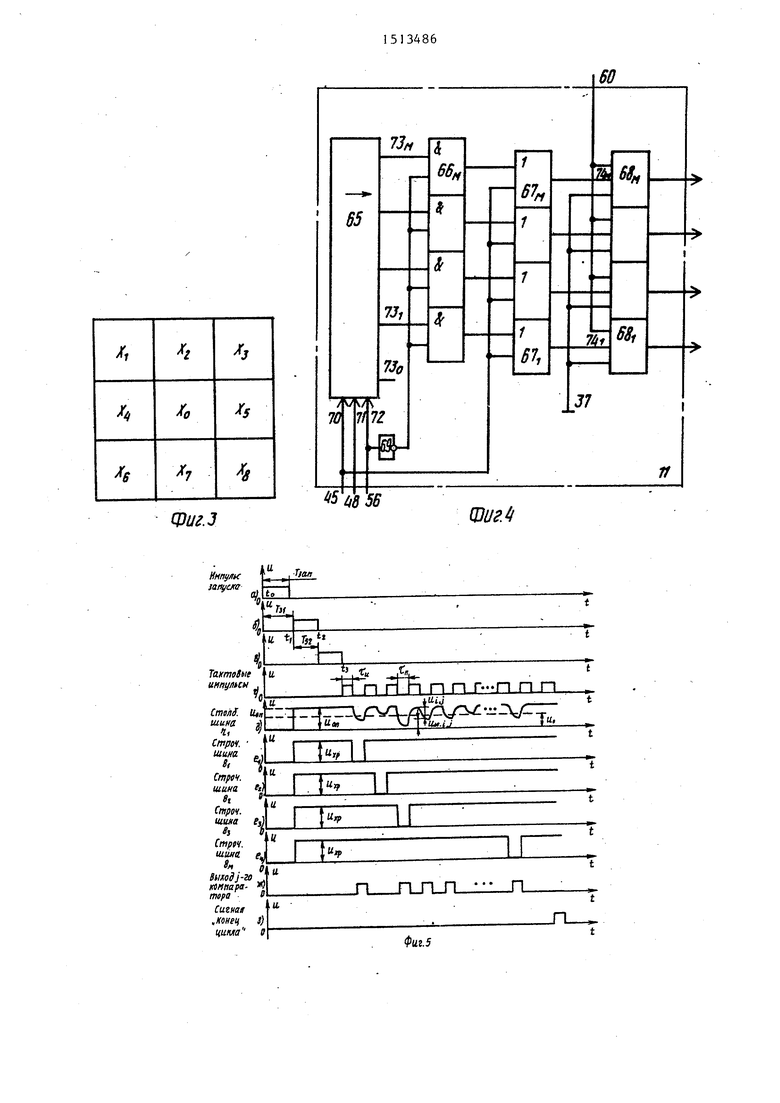

Блок 11 управления строчными шина- ми (фиг.4) содержит сдвиговьй регистр

25 65 на М-4-1 разрядов, М элементов И 66 - 66ц, М элементов ИЛИ 67 - 67, М ключевых элементов 68 ;, - 68, инвертор 69. Вход 70 сброса регистра 65 подключен к входу 45 сброса бло3Q ка управления строчными шинами, к которому подсоединены также вторые входы всех элементов ШШ 67 - К входу 48 начальной установки блока 11 подключен вход 71 записи в младший (нулевой) разряд регистра 65, а к третьему входу 56 - тактовый вход 72 регистра 65 и вход инвертора 69. Выход 73 каждого i-го разряда регистра 65, начиная с первого 73,

,„ соединен с первым входом i-ro элемента И 66, при этом выход 73(j нулевого разряда остается незадействованным. Вторые входы всех элементов И 66 соединены с выходом инвертора 69, а выход каждого элемента И 66

35

45

соединен с первым входом соответствующего элемента ИЛИ 67 . Выход каждого элемента ИЛИ 67,- подхслючен к управляющему входу 74 i-ro ключевого элемента 68, выход которого является L-M выходом блока 11, к которому подключается строчная шина 8 фотоприемной матрицы,Первый и второй входы каждого ключевого элемента 68, соединены соответственно с входом 60 блока 11, который под- клнзчен к шине напряжения хранения , и с шиной 37 нулевого потенциала.

Устройство работает следующим образом.

.Клок 1 проецирования изображений формирует световой поток обрабатываемого изображения,,который поступает на оптический затвор 2, находящийся в закрытом состоянии в отсутствии напряжения на управляющем входе 43. Поэтому световой поток изображения не проходит через затвор 2, Для запуска устройства подается сигнал (например, импульс напряжения) на вход 29 начального запуска, отку- .да он проходит на вход формирователя 18 импульсов запуска. При этом формирователь 18 вырабатывает прямоугольный импульс напряжения длительностью , которьй поступает на вход элемента 26 задержки и на вход 45 сброса блока 11 управле тя строчными шинами и на первый управляющий вход 46 блока 9 ключей. Это приводит к тому, что блок 11. управления строчными шинами устанавливает нулевое напряжение на всех строчных гш- нах 7, - 7д, а выходы ключей 10 - 10jj соединяются на время запускающего импульса Tjqn с 11ИНОЙ 37 нулево- го потенциала, так что на всех столбцовых шинах 8 V - 8ц также устанавливается нулевой потенциал. Со строчных и столбцовых шин нулевой потенциал поступает на электроды ЩП-кон- денсаторов 5 и 6 и имевшиеся в этих конденсаторах заряды (неосновные носители), оставшиеся от предьщуще- го цикла работы или игумовые, и тасек- тируются в подложку, в результате чего ячейки фотоприемной матрицы освобо щаются от зарядов, и матрица подготавливается к восприятию нового изображения о Инжекция зарядов в подпожку (стирание ранее записанного изображения) происходит за время y, . Запускающий импульс задерживается элементом 26 задержки на время Tj и с его выхода поступает на управляющий вход 43 оптического затвора 2, который под действием этого импульса открывается и в течение его длительности Т пропускает световой поток изображения на фотоприемную матрицу 3 и на входы .элементов ИЛИ 20 и 22 и элемента 27 задержки, С выхода элемента ИЛИ 20 импульс запуска приходит на вход 48 начальной установки блока 11 управ- ления строчными шинами, в результате чего на строчных шинах 7 - 7;i устанавливается напряжение хранения , По окончании импульса запуска на входе 46 (т„е. по истечении времени Т ) ключи 10 - 10ц переходят в свое нормальное состояние, в котором их вькоды подключены к шине 38 опорного напряжения, и на

столбцовые шины 8 - 8 подается опорное напряжение и, , являющееся также напряжением хранения для столбцовых ВДП-конденсаторов 6. Напряжения и UQJ удовлетворяют

соотношению

UXP Uon

и.

где UQ - пороговое напряжение ВДП- 20 . . структур.

Теперь на строчных шинах присут5

0

ствует напряжение хранения U

хр

на

столбцов-ых шинах - напряжение U

и обрабатываемое-изображение проеци5 руется на фотоприемную матрицу 3. Под действием напряжений на строчных и столбцовых шинах под электродами ОДП-конденсаторов 5 и 6 возникают потенциальные ямы, причем глуg бина потенциальной ямы под строчным электродом 5 больше, чем под столбцовым электродом (так как )« Световой поток изображения, пропускаемый оптическим затвором 2 в течение времени , воздействует на фоточувствительные ячейки 4 фотоэлектрического преобразователя 3 и вызьшает генерацию в них носителей заряда, причем неосновые носители остаются в ячейках и собираются в более, глубокой потенциальной яме под строчным электродом. Величина заряда, накопленного в каждой ячейке 4 за время проедарова- ния изображения-, пропорциональна количеству поступившего на нее света, т.е. яркости соответствующего элемента изображения. Таким обра зом, за время проецирования изображение записывается в матрице 3 фо5

0

топриемных ячеек 4 в виде распределения заряда по ячейкам (зарядового рельефа).

Так как к началу проецирования текущего изображения на матрицу она должна быть подготовлена к его восприятию, т.е. очищена от зарядов, то длительность запускающего импульса Б течение которого происходит стирание зарядового рельефа, должна превьш ать время инжекции

инж

Т ъ.

уэи инж

Проецировать Изображение на матрицу 3 для его вослриятия нужно, кода матрица уже подготовлена к это- му (т.е. сначала осуществляется стирание предьдущего изображения, а затем проецирование нового). Поэтому время задержки Т., элемента 26 удовлетворяет соотношению

Т,, i

3qn j

при котором затвор 2 открывается

тогда, когда матрица 3 уже подготов-

лена к восприятию изображения.

За время проецирования-изображения должно происходить восприятие его фотоэлектрическим преобразователем 3. Поэтому длительность запускающего импульса Т определяется соотношением

Т

ап воспр )

где tT

eocrip время восприятия изображения фотоэлектрическим преобразователем (время записи изображения) , зависящее от свойств материала фотоприемной матрицы, ее структуры, интенсивности светового потока..

С окончанием импульса на управляющем входе 43 оптический затвор 2 закрывается, и поступление светово- го потока изображения на фотоприемну матрицу прекращается. К этому моменту восприятие изображения завершается, т.е. оно уже записано в матрице.

Запускающий импульс, пришедший на элементы ИЛИ 20 и 22, проходит с выхода элемента ИЛИ 20 на вход 48 начальной установки блока управления строчными шинами и устанавливает его в исходное состояние, а с выхода элемента ИТШ 22 - на вход 47 сброса блока анализаторов и вызывает сброс их в исходное состояние.

Запускающий импульс с выхода эле- меента 26 задержки приходит на вход элемента 27 задержки и задерживается им на время Т , равное времени про ецирования изображения на фотоприем- ную матрицу,- т.е.

Q 5

0

5

0

5

.„

.,

0

Задержанный элементом 27 запускаю- импульс через элемент И.ПИ 21 поступает на первый управляющий вход 50 ключа 24 и на вход 51 сброса счетчика 25.При этом последний устанавливается в исходное состояние, а ключ 24 переходит в открытое состояние и остается в нем. С этого момента ключ 24 пропускает на свой выход тактовые импульсы, вырабатываемые генератором

23импульсов. Длительность тактового импульса генератора 3 равна Оц , а длительность паузы между импульсами - о,. Теперь начинается собственно считывание записанного в матрице 3 изображения.

Тактовые иг-шульсы с выхода ключа

24поступают на тактовый вход 56 блока 11 управления строчными шинами и . на второй управляющий вход 57 блока

9 ключей. При этом в каждом такте происходит выборка и считывание одной строки фотоприемной матрицы 3, причем строка считывается параллельно (т.е. считываются одновременно все ее элементы), а строки выбираются по одной последовательно,начиная с первой. Так, в нулевом такте (нумерация тактов ведется с нуля) счи- тьшается первая строка, в первом - вторая, в i-M - (1-ь1)-я, в (М-1)-м - М-я строка матрицы. Считьшание осу- щес твляется по методу параллельной инжекции.

Рассмотрим этот процесс выборки.

В нулевом такте (первый тактовый импульс, прошедший через ключ 24) тактовый импульс,, поступивший на управляющий вход 57 блока 9 ключей, переводит ключи 10 - 10 в состояние, в котором выход ключа соединен с входом 38 опорного напряжения. В этом состоянии ключи остаются в те- чЪние длительности тактового импульса t . При этом опорное напряжение Up через ключи 10 j, - 10 подается на столбцовые шины 8,, - 8у фотоэлектрического преобразователя 3, к которым под1шючены электроды столб- UOBbix конденсаторов 6 ячеек матрицы. Таким образом, за время тактового импульса на столбцовых шинах ус,- танавливается опорное напряжение Ug (вследствие подключения к нему столбцовых конденсаторов 6 ячеек матрицы). Одновременно с этим тактовый импульс.

поступивший на тактовый вход 56 блока 11 управления строчными шинаадг, вызывает прохождение сигналов с выхода ключа 24 на первый выход блока 11, к которому подключена первая строчная шина 7 . При этом во время тактового импульса на шине 7, как и на других шинах 7. - 7 остается

высокое напряжение U

хр

После-окончания первого тактового импульса на время паузы , между тактовыми импульсами на первом выходе блока 11 устанавливается нулевое напряжение, которое поступает на шину 7, и с нее на электроды строчных конденсаторов 5 первой стро ки. фотоприемной матрицы 3. По окон чании тактового импульса на управляющем входе 57 блока, 9 ключей устанавливается на время паузы Ь нулевое напряжение, вследствие чего ключи 10 - 10| размыкаются и остаются разомкнутыми в течение всей паузы; при этом столбцойые ишшы 8 - 8 оказываются плавающими (так как они отключены от источника напряжения) .

; Таким образом, во время паузы ну левого такта на строчной шине 7 присутствует нулевое напряжение, на шинах 7з 7д - высокое напряжение

хранения , столбцовые шины 8 - 8ц( отключены от источника напряже- .ния и являются плавающими. При этом под электродами конденсаторов 5 я че ек первой строки потенциальные ямы исчезают, в ячейках всех остальнькс строк изменений не происходит. Во время тактового импульса столбцовые конденсаторы 6 всех ячеек матрицы были заряжены до опорного напряжения . Поэтому во время паузы, ко .да шины 8 ;, - 8 j являются плаваюш;ими под Электродами этих конденсаторов имеются потенциальные ямы,глубина которых определяется напряжениемU причем в ячейках первой строки гл у- бина ямы под электродом 6 ячейки больше, чем под электродом 5, так как на шине - нулевое напряжеш е В результате в ячейках первой строки происходит перетекание накопленного заряда, который находился под электродом 5, в более глубокзто потенциальную яму под электродом 6, причем заряд перетекает полностью,, Это приводит к тому, что потенциал каждой столбцовой шины 8j уменьшает

ся на величину, равную сигнальному заряду (который накоплен в ячейке и в данном такте перетек под электрод конденсатора 6) в соответствующей j-й ячейке первой строки, деленную на полную емкость столбцовой потенциал присутствует в течение паузы между тактовыми импульсами на плавающей столбцовой шине 8 и снимается с нее.

В следующем.первом такте тактовый импульс поступает на входы 56 и 57 соответственно блока 11 управления строч1шми шинами и блока 9 ключей, в результате чего на первом выходе блока 11 снова устанавливается напряжение хранения Uj(p , сигналь; с выхода ключа 24 передаются, на второй выход блока 11, ключи 10 - переключаются в состояние, в котором их выходы соединены с входом 38 опорного напряжения и, При этом на строчной шине 7 устанавливается напряжение , на шине 7,во время тактового импульса оста0

5

0

5

0

5

ется напряжение (как и на остальных строчных пинах), на столбцовых шинах 8 S| устанавливается опорное напряжение V , причем 11 . Это приводит к тому, что в ячейках первой строки происходит обратное перетекание сигнальных зарядов столбцовых электродов 6 под строчные электроды 5 (в более глубокие потенциальные ямы), которое происходит за время тактового, импульса . Так что в первой строке /

сигнальные заряды снова хра11ятся под

электродами строчных конденсаторов 5 и могут быть снова Считаны в будущем.

Затем во время паузы первого такта вьшолняется считывание второй строки матрицы, что происходит совершенно аналогично считыванию первой строки: столбцовые шины 8 - 8у на паузы отключаются от источников напряжения разомкнутыми ключами 10, - 10fj и являются плаваю- шдни, причем во тактового импульса на них установршось опорное напряжение,до которого заряжаются столбцовые конденсаторы 6, на шине 7 7 на время паузы устанавливается нулевое .напряжение, происходит перетекание сигнальных зарядовьрс пакетов в ячейках второй строки под электроды столбцовьк конденсаторов

131513А86

6, вследствие чего на j-й столбцовой шине 8: наводится изменение напряжения, пропорциональное величине сигнального заряда в j-й ячейке второй строки. Описанный процесс считывания выполняется последовательно для всех строк матрицы, так что в каждом такте считывается одна строка (в нулевом такте считывается пер10

25 6

вая строка, в первом - вторая, в i-M - (1+1)-я, в (М-1)-м - М-я строка), При этом в i-м такте за мя тактового импульса происходит установление на столбцовых шинах

1у опорного напряжения U и

обратный Перенос зарядовых пакетов из-под столбцовых электродов 6 под строчные электроды 5 в i-й строке матрицы (так как на столбцовых шинах присутствует опорное напряжение а на строчных - напряжение хране- ния), а во время паузы - перетекание зарядовых пакетов в (1+1)-й стрке из-под строчных электродов 5 под столбцовые электроды 6 (так как столбцовые шины 8д 8ц отключены ключами 10 - Юц от источника напряжения и являются плаваюшдми, а на строчной шине 8-, присутствует нулевое напряжение, поступающее с (i+D-ro выхода блока управления строчными шинами 11), вследствие чего на плаваюш11:х столбцовых шинах 8, 8 наводится изменение потенциала, пропорциональное величине зарядовых пакетов в соответствующих ячейках (на шине 8 наводится изменение потенциала, пропорцио- наль ное заряду в ячейке 4 ) .

В процессе считывания управление столбцовыми шинами 8,, - 8 осуществляется с помощью ключей 10 ;) - 10щ, которые переключаются под действием тактовых импульсов, , поочередно подавая на шины опорное напряжение Ug и отключая их от источника напряжения, а управление строчными ши нами 71 - 7д - с помощью блока 11 управления строчными шинами.

Блок 11 работает следующим образом,

В начале цикла работы запускающий импульс с выхода блока 18 через элемент ИЛИ 19 поступает на вход 45 сброса блока 11, откуда попадает на ,вход 70 сброса регистра 65 и вызывает установление всех разрядов регист ,ра в нулевое состояние. Этот же им14

15

0

0

5

0

5

0

5

10

пульс с входа 45 поступает на вторые входы элементов PfflH 67ц - 67/, вследствие чего на их выходах появляются импульсы напряжения высокого уровня длительности , , которые воздействуют на управляющие входы 7, - 74д, соответств тощих ключевых элементов 68 - 68д,. При этом ключи 68, - 68„ переходят на время этого импульса в состояние, в котором их выходы соединены с вторыми входами, т«е, с шиной 37 нулевого потенциала, Таким образом, на время Т,,дп запускающего импульса на строчные шины 7( - 7дд матрицы подается нулевое напряжение, чем обеспечивается ин- жекция зарядов ячеек в подложку и стирание информации в матрице 3, Затем, после окончания импульса на входе 45, на выходах элементов ИЛИ 67 - 67у(д устанавливается нулевое напряжение, которое поступает на входы 741 - 74д ключевых элементов 5 68 - 68f, переводя их в состояние, в котором их выходы соединены с шиной 60 напряжения хранения (при этом на строчные шины 7 м. подается напряжение хранения и осуществляется восприятие изображения - накопленных зарядов в ячейках матрицы 3) .

После окончания импульса на входе 45 задержанный запускающий импульс поступает на вход 48 блока 11 и с него на вход 71 записи в младший разряд регистра 65, вследствие чего в младший (нулевой) разряд регистра 65 записывается единица. Во время проецирования изображения состояние блока 11 управления строчными шинами сохраняется таким: в мпадшем разряде регистра 65 содержится 1, :& В остальных разрядах - нули,на вы- ходах .элементов И 67, - 67д присутствуют напряжения логического нуля, которые, поступая на входы соответ- ствуюш 1х ключевых элементов 68 - , поддерживает их в состоянии, в котором на их входы подается на- прялсение хранения (напряжение хранения поступает на строчные шины /и чем обеспечивается восприятие изображения), Затем; запускающий импульс поступает с элемента 27 задержки через элемент ИЛИ 21 на управляющий ключ 24 и открывает его, при этом тактдвые импульсы генератора 23 проходят через него и по ,

151

ступают на тактовый вход 56 блска 11 и с него - на тактовый вход 72 регистра 65 и на вход инвертора 69. Под действием каждого тактового импульса (по его переднему фронту) происходит сдвиг информации, записанной в регистре 65 на один разряд (так в нулевом такте едигшца из нулевого разряда регистра 65 сдвигается в первый разряд и появляется на выходе 73 , а в нулевой (младший) разряд заносится нуль, в первом такте единица переносится во второй разряд{ в i-M такте - в (i+ +1)-й разряд регистра 65). Напряжение с выхода i-ro разряда регистра -65 поступает на первый вход элемента И 66j на второй вход которо го поступают с выхода инвертора 69 проинвертированные тактовые импульсы. При этом в 1-м такте имеем: на (i+1)-M выходе регистра 65 присутствует напряжение логической единицы, во время такт.ового импульса на вторых входах элементов И 66 - 66 -присутствует напряжете логического нуля (так как тактовые импульсы инвертируются инвертором 69), а во время паузы - напряжение логической единицы; в результате этого в i-M такте во время тактового импульса на выходе (i+1)-ro элемента И 66 присутствует логический нуль (так как на втором входе присутствует логический нуль - про- инвертированный импульс), а во время паузы - логическая ед,иница (так как на первый вход поступает единица с (i+1)-го выхода регистра, а на второй вход. - проинвертированная пауза между тактовыми импульсами), на .выходах остальных элементов И остается логический нуль.

Таким образом, в i-м такте на выходах всех элементов ИЛИ 67, за исключением (i+1)-го, присутствует напряжение логического нуля, а на выходе элемента 67; во время тактового импульса присутствует нулевое напряжение, а во время паузы этого такта - напряжение логичв ской единицы. С элементов ИЛИ сигна лы поступают на управляющие входы 74 соответствую1цих ключей 68, вслед ствие чего в i-м такте все ключевые элементы, кроме (i+1)-ro, находятся в состоянии, в котором на их выходы подается напряжение хранения с

51348616

первьк входов, а элемент 68 во время тактового импульса также находится в этом состоянии и во время паузы i-ro такта переходит в состоя- ние, в котором на его выход подает-, ся с второго входа нулевой потенциал. Таким образом, в i-м такте на строчную шину 7 {. матрицы 3 во вре

мя тактового импульса подается напряжение хранения, а во время паузы - нулевой потенциал, чем и обеспечивается считывание информации с (if1)-й строки матрицы 3, как описано вьше.

Для обеспечения нормального процесса считывания изображения с матрицы длительности тактового импульса и паузы должны удовлетворять таКИМ условиям: за время импульса должно происходить установление опорного напряжения на столбцовых шинах, т„е. заряд Щ(П-конденсаторов 6 до Од ,а также одновременно с этим обратный перенос зарядовых пакетов из-под столбцовых электродов конденсаторов 6 считанной строки под строчные электроды 5, так что

ц 5:: max „„.с

Чет ) - 06р V

},

5

0

где о

УСТ время установления опорного напряжения на столбцовых шинах; ОБО время обратного переноса зарядов под строчные электроды;

а также за время паузы должно происходить считыващие элементов выбранной строки, т.е. перенос зарядовых пакетов под столбцовые электроды 6 ячеек этой строки.и изменение напряжения на плавающих столбцовых шинах, так что

. 45

/ -Лм

с-п5

СЧ. ЭП J

где с-сц, эд - время считывания элемента изображения. В процессе считьшания выполняется последовательная выборка строк матрицы, в которой записано изображение таким образом, что в i-м такте (счет тактов ведется с нуля) считывается ()-я строка матрицы, причем значения яркостей элементов

изображения представляются изменениями величины напряжения на соответствующих столбцовых шинах 8 - Вц матрицы 3, т.е. в конечном итоге амплитудой импульса напряжения на столбцовой шине 8 во время паузы соответствующего такта (амплитУда импульса отсчитывается относительно уровня опорного напряжения),

Так, в нулевом такте на шине 8 наводится изменение напряжения, соответствующее элементу изображения, записанному в ячейке , в i-м такте - элементу изображения, записанному в ячейке i+t I . Столбцовые шины 8, - 8 ц фотоприемной матрицы 3 подключены к входам соответствую- mjix компараторов 13;|-13к блока- 12 компараторов, так что напряжение с этих шин поступает на входы соответствующих компараторов 13, входы опорного напряжения которых соедине ны с входом 39 опорного напряжения блока 12 компараторов, который соединен с входом 32 установки порога бинаризации. На вход 32 устройства подается постоянное напряжение , которое определяет порог бинаризации изображения и соответствует некоторому пороговому уровню яркости, Каждьш компаратор 13 сравнивает с опорным напряжением и напряжение, поступающее на его вход с шины 8j т.е. в такте вьшолняется сравнение напряжения,соответствующего ячейке 4, с опорным напряжением UQ, т.е. сравнение яркости элемента изображения 4,-, с пороговым уровнем яркости. При этом ввиду того, что яркость элемента изображения представляется изменением напряжения на столбцовой шине относительно опорного напряжения (т.е. амплитудой импульса во время паузы относительно этого уровня), значения напряжений сравниваются относительно уровня опорного напряжения U , Это значит, что яркость элемента, изображения (i,j) представляется пропорциональной ей амплитудой импульса напряжения U;., отсчитьюаемой от уровня ,5 т,е, на шине 8 во время считы- вашш этого элемента присутствует

напряжение U j

и

OU

Ui.i

J

и

соответственно, пороговый уровень яркости.пропорционален разностному напряжению U Ug - U.

Сравнение яркости элемента изображения с пороговым уровнем выполняется компаратораг«1 таким образом: если в (i-l)-M такте напряжение

и

jft.i.i

соответствзшщее эл ементу изо

бражения (i,j), меньше, чем Ug (т,е, амгшитуда U; импульса на шине 8 больше, чем Up U о соответственно, яркость элемента превышает пороговый уровень),то на выходе компаратора 13 появляется импульс напряжения высокого уровня (логической единицы), а в противном случае на выходе компаратора присутствует напряжение логического нуля:

1, если и„ ;.

и.

J

О, если и

эл, ).

и

о J

0

1где U|; - выходное напряжение j-ro

компаратора 13j в (1-1)-м такте (при считывании L-Й строки),

Таким образом, в процессе описанного параллельно-последовательного считывания элементам изображения с помощью компараторов 13, - 3ц при-

(1 4 II 1 4

сваивается значение

если их

35

40

25 яркость превьш1ает заданньй пороговый уровень, и О в противном случае, т,е, выполняется бинаризация изображения и вьделяется его силуэт, причем порог бинаризации (порогоый уро30 вень яркости) задается опорным напряжением UQ. При этом каждая строка считьшается и обрабатьшается параллельно в одном такте (i-я строка - в (i-1)-M такте), а строки обрабатываются последовательно, так что каждый компаратор 13 последовательно обрабатывает элементы j-ro столбца матрицы, и на его выходе последовательно появляются их значения, В i-M такте на выходах блока компараторов появляются бинаризованные значения элементов (i+1)-и строки матрищз в виде импульсов напряжения, С выходов блока компараторов сигналы элементов бинаризованного изображения поступают на выходы 34 сигналов бинарного препарата, с которых они могут сниматься известными методами для обработки, запоминания или отображения на экране дисплея (например, они могут считываться с помощью быстродействующего буферного регистра). ,

С выходов компараторов 13. 13 сигналы элементов изображения поступают ria входы соответствующих логических анализаторов 15 - 15) бло ка 14 анализаторов (с компаратора 13j на вход анализатора 15), Блок

45

50

55

14 анализаторов в процессе парал лельно-последовательного считывания изображения вьтолняет выделение кбит турных элементов бинаризованного блоком компараторов изображения (силуэта), т.е. таких элементов силуэта, которые имеют хотя бы один соседний элемент, не принадлежащий силуэту. На блок ,14 анализаторов в каждом такте поступает параллельно одна соответствующая строка бинаризованного изображения (строка нулей и единиц) с выходов блока 12 компараторов (на каждьш анализатор 15; поступает j-й элемент этой строки; и блок анализаторов вьтолняет анализ элементов соответствующей записанной в нем строки бинарного препарата на принадлежность их контуру силуэта. Это осуществляется посредством того, что каждый логический анализатор 15 в (1+1)-м такте анализирует окрестность 3x3; элемента изображения (i,j) и определяет принадлежность его контуру силуэта, для чего вычисляется логическая функщя от элементов окрестности 3x3 элемента (i,j), которая при томает значение 1, если элемент является контурным, и О в противном случае. Таким образом, блок 14 анализаторов выполняет в процессе параллельно- последовательного считывания изображения выделение контуров бинарного силуэта изображения, т.е. формирование контурного препарата бинарного силуэта, для чего присваивает значение 1 тем элементам силуэта, котрые являются контурными, и О всем остальным. В (1+1)-м такте тактовый импульс с выхода элемента 28 задержки поступает на тактовый управляемый вход 58 блока анализаторов и под действием его анализаторы 15 воспринимают соответствующие элементы (1+1)-й строки и выполняют анализ элементов i-й строки, записанной ранее в блоке анализаторов. При этом, если элемент (i,j) появляется контурным, то на выходе анализатора 15; появляется в соответствующем такте и myльc напряжения высокого уровня, а в противном случае присутствует напряжение логического нуля.

. Блок 14 логических анализаторов работает следующим образом. Запускающий импульс через элемент ИЛИ

22 попадает на вход сброса 47 блока 14, с которого поступает на R-входы установки нуля триггеров 61 Ц всех анализаторов 15 - 15, и устанавливает их в нулевое состояние. Затем в процессе считывания изобра- жегтая на входы анализаторов 15. - 15| с вьгходов компараторов поступа- Q IOT элементы строк бинаризованного .изображения, которые воспринимаются ими и обрабатываются.

В исходном нулевом такте проис5 ходит считывание элементов первой строки (во время паузы), которая бинаризуется блоком компараторов, и с некоторой задержкой появляются, сигналы на выходе блока 14 компараQ торов, когда на входах логических анализаторов установились напряжения элементов первой строки, а на тактовый вход 58 блока анализаторов приходит импульс нулевого такта, задер5 жанный элементом 28 задержки. Тактовый импульс поступает с входа 58 на С-входы триггеров 61 - 61 а анализаторов блока 14, а на D-входах из первых триггеров 61, присутствуют

0 напряжения элементов бинаризованной первой строки, поэтому бинаризованная первая строка записывается в . триггеры 61 анализаторов 15 - 15„ (в триггер 61,.:- записывается j-й элемент). Запись происходит по переднему фронту тактового импульса. В следующем,первом такте во время паузы происходит считывание с матрицы второй строки, напряжения би- назированных элементов которой появляются на.выходах компараторов 13 - 13jj и поступают на D-входы первых триггеров 61J анализаторов 15 - 15(j . При поступлении задержанного тактового импульса первого такта .на вход 58 блока 14 и с него на,С-входы триггеров вторая строка бинаризованного изображения записывается в первые триггеры 61 анализаторов 15 - 15,, а первая строка переписывается

0 из триггеров 61 в триггеры 61 анализаторов, так как их D-входы подключены к прямым выходам триггеров 61. Цепочка триггеров 61 - 61, в каждом анализаторе представля ет собой синхронный трехразрядный сдвиговый регистр. В процессе параллельно-последовательного считывания изображения происходит последо5

0

5

21

вательная запись строк бинаризованного изображения в триггеры 61 - 61, логических анализаторов, причем в анализаторах в каждом такте записаны три последовательные строки: в нулевом такте в триггерах 61, анализаторов записывается первая строка, а в остальных триггерах - нули; в первом такте первая строка переписывается в триггеры 612 анализаторов, триггеры 61 воспринимают вторую строку, в триггерах бЦ зайи саны нули; во втором такте в триггеры 61 записывается третья строка бинаризованного изображения, а в триггеры 612 3 переписываются с соответственно первая и вторая строки, в i-M такте в триггеры 61 заносится (1+1)-я строка, в триггеры 61 заносится i-я строка, а в триггеры 61- - (1-1)-я строка бинаризованного изображения-.

Таким образом, .в каждом такте в логических анализаторах записаны три последовательные строки бинаризованного изображения и в трех последовательных .анализаторах 15j , 15; и 15-.J., записана окрестность 3x3 элемента силуэта изображения,содержащегося в триггере 61 анализатора 15;, так в (i+1)-M такте в тригере 61 анализатора 15 записан элемент (i,j), а в остальных триггерах этого анализатора и анализаторов 15: , и 15j4i содержатся элементы окрестности 3x3 этого элемента: триггер 61 анализатора IS;., - элемент (i+1, j-1), триггер-61,;, анализатора - элемент (i, j-1), триггер 615 анализатора 15J. - эл элемент (i-1, ), триггер 61, анализатора 15 - элемент (i+1, j), триггер 6 la анализатора 15j - элемент (i-1, j), триггер 61 анализатора , - элемент (i+1, j+1), триггер 612 анализатора 15, - элемент (i, j+1), триггер eig анализатора 15 ;+, - элемент (i-1, j+1).

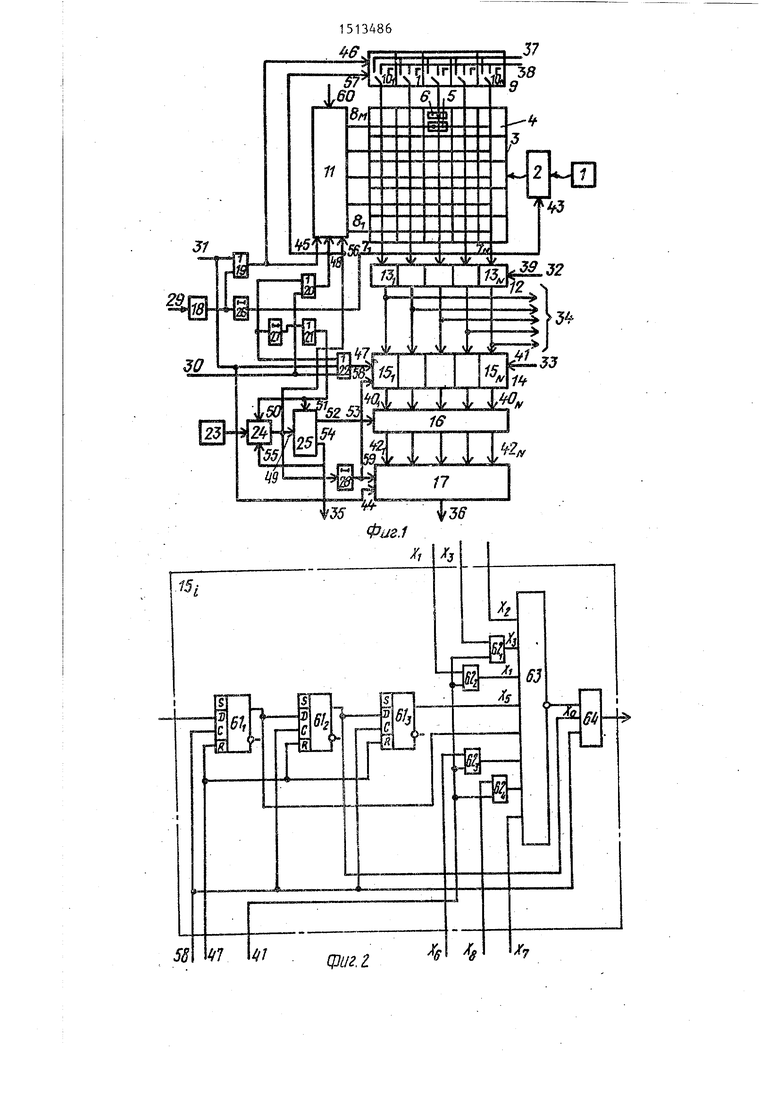

Анализ 8-связанной окрестности 3x3 элемента (i,j) на принадлежност его контуру осуществляется посредством вычисления логической функции

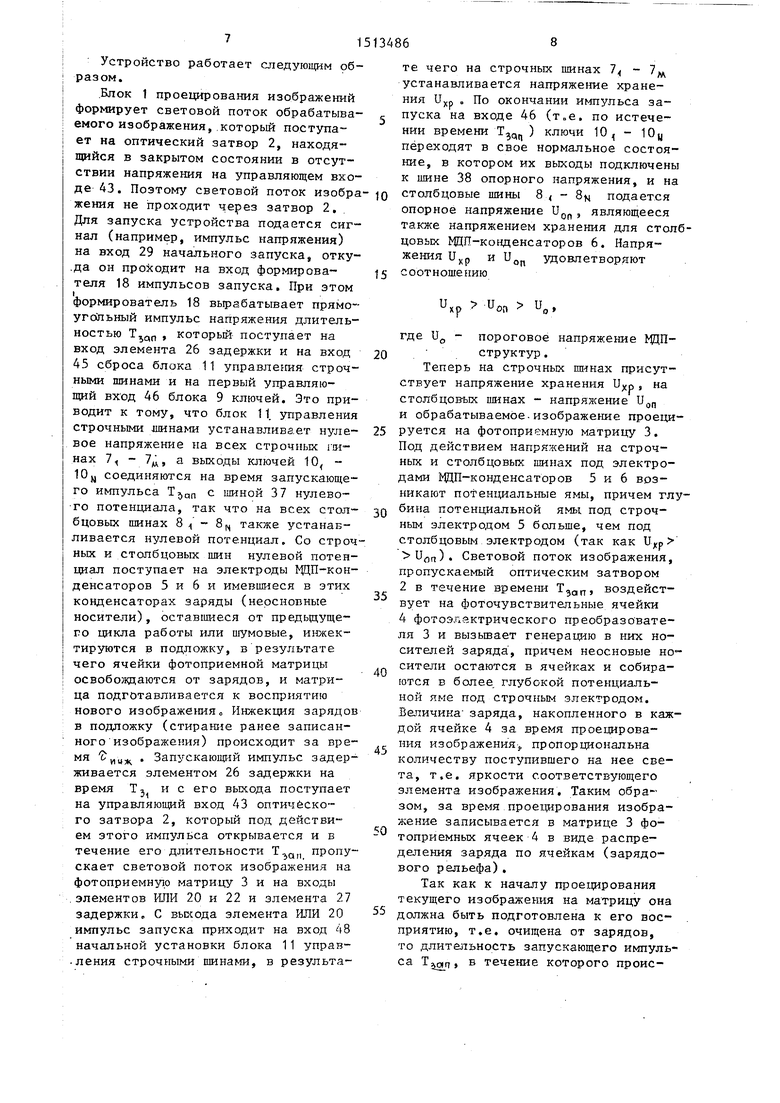

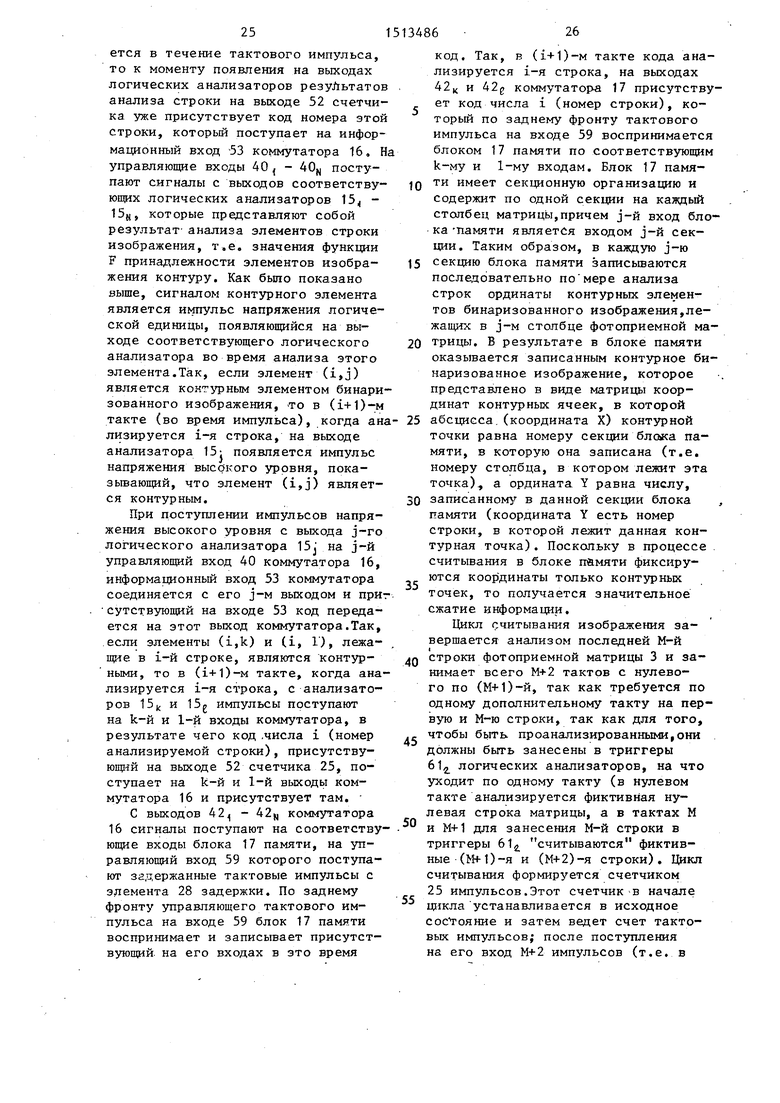

F XpX,X2.X,X X5XgX Xg от элементов окрестности, где Х - Xg - логические переменные, обозначающие элементы окрестности Х 1, если элемент X,, принадлежит бинаризован-

|Ч

ному изображению, Х О в против-

22

0

I

ном случае. Функция F принимает значение 1 (F 1), если элемент Х является контурным (т.е. , а среди элементов X - Х хотя бы один нулевой), и значение О (F 0) в противном случае. Вид окрестности 3x3 с обозначениями элементов представлен на фиг.З. Имеет меJO сто следующее соответствие между элементами окрестности элемента (i,j) и переменными Х, - Xgi Х - элемент (i,j), Х - элемент (i+1, j + 1), X,j - элемент (i, j + 1), Xj элемент (i-1, j + 1), X,- элемент (i+1, j), Xj- элемент (i-1, j), элемент (i+1, j-1), X - элемент (i, j-1), Xg- элемент (i-1, j1).

Анализ 4-связанной окрестности 3x3 осуществляется путем вычисления логической функции F кХ,Х5Х7, т.е. исключением перемен- ных X,X XgXgH3 функции F. Рассмотрим сначала анализ 8-окрестности элемента изображения. В этом режиме на вход 33 задания вида окрестности подается напряжение логического нуля, которое поступает на управляющий вход 41 блока анализаторов и с него - на вторые входы элементов Р1ПИ 62 - 62 всех логических анализаторов. В каждом jjM логическом анализаторе в (i+1)-M такте на вхо5 ды элемента И-НЕ 63 поступают значения переменных Х (с триггера 61 анализатора 15 ,), Х и Х. (с триггеров 61j, и 61J анализатора соответственно), Х (с триггера 61

0 анализатора ), а переменные Х-., Х (с триггеров 61, и 6Ц анализатора 15у, ) и Xg, Xg (с триггеров 61 и 61j анализатора 15у., ) поступают на входы элементов И-НЕ 63 че5 ; рез элементы ИЛИ 62 - . соответственно (так как на вторых входах этих элементов присутствует логический О с управляющего входа 41, то эти элементы не оказывают влия0 ния на переменные X,, Хз, Xg, Xg), Таким образом, на входы элемента И-НЕ 63 поступают на (j+1)-M такте значения переменных X, - Xg окрестности элемента изображения

5 () переменная Х с прямого выхода триггера 612 анализатора 15 поступает на второй вход элемента И 64, на первый вход которого приходит выходной сигнал элемента И-НЕ

23 ,

63, а на третий вход - тактовый им- ;пульс с входа 58. .На выходе элемен- ;та И 64, который является выходом :анализатора, появляется результат

вычисления логической функции

Т Хд X XjXjX XjXgX Xg,

где Т - переменная,обозначающая актовые сигналы (Т 1 во время мпульса, Т О в паузе).

Таким образом, во время тактового импульса (в (i+1)-M такте) (Т 1) каждый логический анализатор 15: выполняет вычисление функции F над элементами 8-окрестности 3x3 элемента (i,j), определяющей принадежность этого элемента контуру вьвделенного силуэта. Если элемент (i,j) является контурным, то F 1, и во время управляющего тактового импульса на выходе данного логического анализатора 15 появляется импульс напряжения логической 1, а в противном случае остается напряжение логического нуля. Описанный процесс анализа осуществляется паралельно-последовательно для всего изображения по мере поступления считываемых стр ок.

Анализ 4-окрестности 3x3 элемен- та изображения выполняется совершенно аналогично описанному выше анализу 8 окрестности, с той лишь разницей, что для осуществления этого режима на вход 33 выбора конфигура- Щ1И окрестности подается логическая 1, которая поступает ,на управляющий вход 41 блока анализаторов, Напряже- ние логической 1 при этом с входа 41 воздействует на вторые входы эле- ментов ИЛИ 62, - 62 всех анализа- торов 15 - 15(,, вследствие чего на выходах этих элементов в течение всего цикла считьшания присутствует логическая 1 независимо от значений переменных Х, Xj, Xg, Xg, поступающих на их первые входы. В результате переменные Х, Х, Xg, Xg исключаются (они равны единице и не влияют на значение функции F) и каждым анализатором 15 в (1+1)-м так- те вычисляется функция F t , определяющая как и выше, принадлежность контуру элемента изображения (i,j), но уже для 4-окрестности.

24

Анализ элементов некоторой стро- .ки выполняется только после ее считывания, т.е. задержанный 1-й тактовый импульс с элемента 28 задержки должен поступать на блок 14 анали- заторов после завершения считывания (1+1)-й строки. Отсюда для задержки Т элемента 28 задержки вытекает условие

-о

0

5

0

5

0

5

0

5

где Т - период следования тактовых

импульсов.

Таким образом, блок анализаторов- управляется тактами, задержанными по отношению к тактам считывания на один такт. В результате получается, что. в i-M такте во время импульса анализируется (1-1)-я строка И считывается (во время паузы) (1+1)-я строка,цричем анализ (i-1)-и строки выполняется в (i-l)-M задержанном такте (под. действием задержанного (i-1)-ro тактового импульса). При этом в первом такте, когда считанная в предьдущем нулевом такте первая строка матрицы заносится э триггеры 61,, в триггерах 61 ,j анализаторов 15д - 15 содержатся нули, так что. анализируется фиктивная нулевая строка матрицы, состоящая из нулей.

Одновременно со считьгоанием и обработкой строк изображения счетчик 25 ведет счет тактовых, импульсов, поступающих на его счетный вход 48 с выхода управляемого ключа 24. Задержанный элементами 26 и 27 запускающий импульс одновременно поступает на открывающий вход 50 ключа 24 и.на вход 51 начальной установки счетчика 25. При этом ключ 24 открывается, а счетчик 25 устанавливается в начальное состояние и затем ведет счет тактовых импульсов, изменяя свое состояние на единицу

. по переднему фронту каждого посчу- пающего на его счетный вход 49 такто вого импульса. Счет ведётся таким образом, что во время обработки i-й строки изображения на выходе 52 счетчика присутствует код числа i (т.е, номер анализируемой строки). Поскольку переключение счетчика 25 в новое состояние происходит по переднему фронту тактового импульса, а анализ строки происходит и завершается в течение тактового импульса, то к моменту появления на выходах логических анализаторов результатов . анализа строки на выкоде 52 счетчика уже присутствует код номера этой строки, который поступает на информационный вход 53 коммутатора 16. На управляющие входы 40 - 40 поступают сигналы с выходов соответствующих логических анализаторов 15 - 15н, которые представляют собой результат- анализа элементов строки изображения, т.е. значения функции F принадлежности элементов изображения контуру. Как было показано выше, сигналом контзфного элемента является импульс напряжения логической единицы, появляющийся на выходе соответствующего логического анализатора во время анализа этого элемента.Так, если элемент (i,j) вляется контурным элементом бинаризованного изображения, то в (1+1)-м такте (во время импульса), когда анаизируется i-я строка, на выходе анализатора 15; появляется импульс напряжения высокого уровня, пока- зьшающий, что элемент (i,j) является контурным.

При поступлении импульсов напряения высокого уровня с выхода j-ro огического анализатора 15; на j-й правляющий вход 40 коммутатора 16, информационный вход 53 коммутатора соединяется с его j-м выходом и прит

сутствующий на входе 53 код передается на этот выход коммутатора.Так, если элементы (i,k) и (i, 1), лежа- . щие в i-й строке, являются контурными, то в (i+1)-M такте, когда анализируется i-я строка, с анализаторов 15|j и 15g импульсы поступают на k-й и 1-й входы коммутатора, в результате чего код .числа i (номер анализируемой строки), присутствующий на выходе 52 счетчика 25, поступает на k-й и 1-й выходы коммутатора 16 и присутствует там.

С выходов 42 - 42(, коммутатора 16 сигналы поступают на соответствующие входы блока 17 памяти, на управляющий вход 59 которого поступа- куг задержанные тактовые импульсы с элемента 28 задержки. По заднему фронту управляющего тактового импульса на входе 59 блок 17 памяти воспринимает и записывает присутствующий на его входах в это время

0

5

0

5

0

5

0

5

0

5

код. Так, в (i+1)-M такте кода анализируется i-я строка, на выходах 42ц и 42g коммутатора 17 присутствует код числа i (номер строки), который по заднему фронту тактового импульса на входе 59 воспринимается блоком 17 памяти по соответствующим k-му и 1-му входам. Блок 17 памяти имеет секционную организацию и содержит по одной секции на каждый столбец матрицы,причем j-й вход блока-памяти является входом j-й секции. Таким образом, в каждую j-ю секцию блока памяти записьшаются последовательно по мере анализа строк ординаты контурных элементов бинаризованного изображения,лежащих в J-M столбце фотоприемной матрицы. В результате в блоке памяти оказывается записанным контурное бинаризованное изображение, которое представлено в виде матрицы координат контурных ячеек, в которой абсцисса.(координата X) контурной точки равна номеру секции блока памяти, в которую она записана (т.е. номеру столбца, в котором лежит эта точка), а ордината Y равна числу, записанному в данной секции блока , памяти (координата Y есть номер строки, в которой лежит данная контурная точка). Поскольку в процессе . считывания в блоке памяти фиксируются координаты только контурньк точек, то получается значительное сжатие информации.

Цикл считывания изображения завершается анализом последней М-й строки фотоприемной матрицы 3 и занимает всего М+2 тактов с нулевого по (М+1)-й, так как требуется по одному дополнительному такту на первую и М-ю строки, так как для того, чтобы бьггь проанализированными,они должны быть занесены в триггеры 612 логических анализаторов, на что уходит по одному такту (в нулевом такте анализируется фиктивная нулевая строка матрицы, а в тактах М и М+1 для занесения М-й строки в триггеры 61 считываются фиктивные (№1)-я и (М+2)-я строки). Цикл считывания формируется счетчиком 25 импульсов.Этот счетчик-в начале цикла устанавливается в исходное сос тояние и затем ведет счет тактовых импульсов; после поступления на его вход М+2 импульсов (т.е. в

М+1)-м такте считывания с нулевого) а его втором выходе 54 появляетсй апряжение высокого зфовня, которое оступает на второй управляющий вход 5 ключа 24 и закрывает его. В ре- ультате прохождение тактовых им- ульсов через ключ 24 прекращается цикл работы и считывания изобра- е1тая заканчивается. Напряжение с ыхода 54 счетчика поступает также а выход 35 сигнала Конец 1щкла стройства и сигнализирует об окон - ании цикла обработки изображения.

Как бьио показано выше, номер актического такта работы устройст- за на единицу больше, чем число, рисутствующее на выходе 52 счетчи- са 25, т.е.:во время i-ro такта на ыходе 52 присутствует число (i-1). Такая работа счетчика может быть еализована различны1 и способами. 1ожет использоваться циклический счетчик с предварительной установ- ой, при этом в начале цикла счет- 1ИК устанавливается в состояние на здиницу меньше максимального, затем нулевом такте он переходит в максимальное состояние, в первом так- ге устанавливается в нулевое состоя- иe и далее считает такты так, что 2ГО выходной код на единицу меньше шсла входных импульсов; таким образом счетчик считает (М+1) тактов, г.е. до состояния (М+1),код которо- : о может вьщеляться логической схе лой (например, ИЛИ), по достижении которого вырабатывается сигнал на выходе 54 счетчика. Возможна реализация на счетчике, который считает актовые импульсы от О до М+1, т.е, И такте принимает состоятше i, ia его выходной код (число 1) преобра- Ьуется в код номера анализир уемой строки (число i-1) логической схемой ;(например, комбинационной схемой или программируемой логической матрицей) ,

Поскольку на выходе 52 счетчика -25 присутствует многоразрядный код, :то его выход 52 и,соответственно,ин- )формационный вход 53 коммутатора :16, его выходы и входы блока 17 памяти являются многоразрядными, приче разрядность определяется числом

строк в матрице 3 (например, если в йатрице 256 строк, то число разрядов равно 8).

0

5

0

5

0

5

0

Как следует из описания работы счетчика 25, его коэффициент пересчета равен М+2.

Таким образом, после окончания цикла работы устройства в блоке 17 памяти записаны координаты контурных элементов бинаризованного по заданному порогу изображения, а в матрице 3 хранится исходное изображение (в виде распределения зарядовых пакетов по ячейкам).

Возможно вьшолнение повторного тдикла считывания одного и того же изображения (например, с измененным порогом бинаризации). Для этого подается импульс напряжения высокого уровня на вход 29 повторного запуска устройства. Этот импульс через элемент ИЛИ 20 поступает на вход 48 начальной установки блока 11 управления строчными шинами и подготавливает $го к новому циклу, через элемент ИЛИ 22 попадает на вход 47 сброса блока 14 логических анализаторов и устанавливает триггеры 61 анализаторов 15 - 15ц) в нулевое состояние, через элемент PfflH 21 попадает на первый управляющий вход 50 кл1€гча 24 и на вход начальной установки счетчика 25, При этом счетчик 25 устанавливается в исходное состояние, а ключ 24 открывается и пропускает на свой выход тактовые иь-тульсы, под действием которых протекает описанный выше процесс параллельно-последовательного считывания и обработки записанного в матрице 3 изображения.

Порог бинаризации изображения изменяется посредством изменения опорного напряжения U на входе 32 устройства. Вид анализируемой окрестности задается напряжением на входе 33 устройства (при напряжении логического нуля анализируется 8-связанная окрестность 3x3, а при напряжении логической единицы - 4-связанная окрестность 3x3),

Сброс устройства осуществляется подачей импульса на вход 31 сброса. Этот импульс поступает на вход -45 сброса блока управления строчными шинами и на управляющий вход 46 блока 9 ключей. При этом с выходов блока 11 на строчные шины 7 - 7 подается нулевое напряжение, выходы ключей соединяются с шиной 37 . вого потенциала, так что на столбцо10

291513486

вые шины 8, 8 также подается нулевое напряжение. В результате происходит инжекция в подложку фотойриемной матрицы 3 содержащихся в ее ячейках А-зарядовых пакетов элементов изображения и стирание изображеютя (очищение матрицы 3), Длительность импульса должна превышать время инжек- ции. Кроме того, импульс сброса поступает та1сх е через элемент ИЛИ 22 на вход 47 сброса блока 14 анализаторов и сбрасывает триггеры 61 в нуль, а также на вход 44 сброса блока 17 памяти и вызывает его сброс (стирание ранее записанной информации и подготовка к восприятию новой информации) .

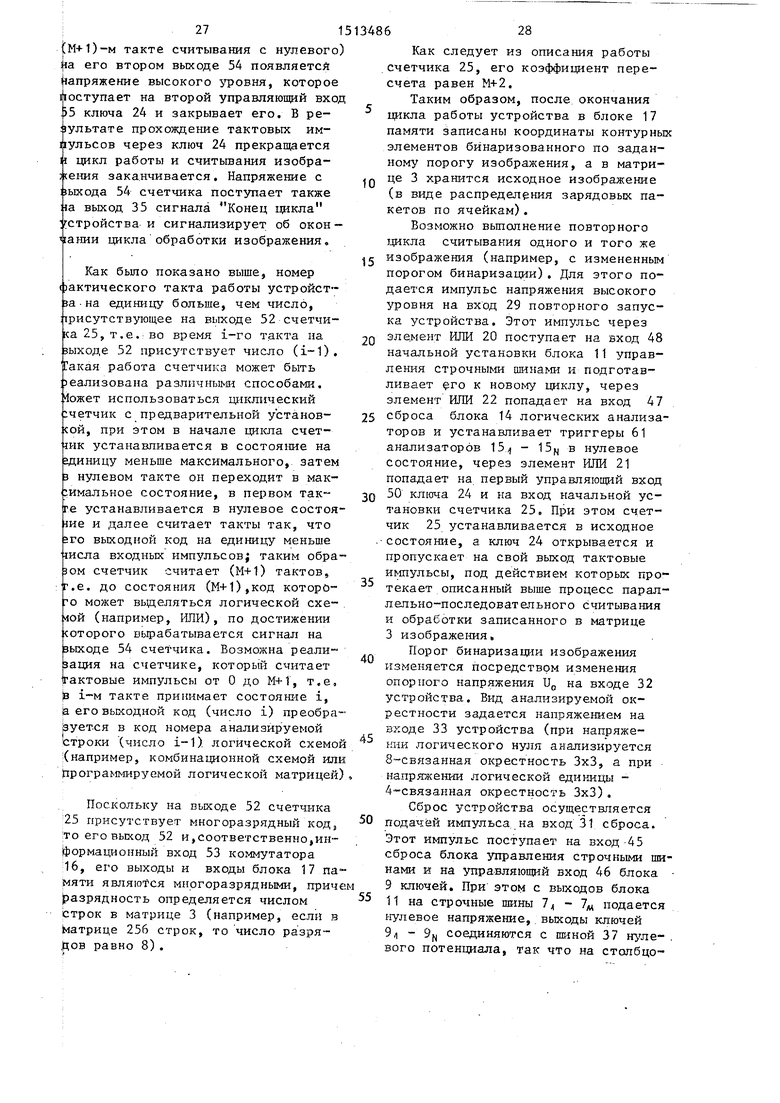

Описанная выше работа устройства поясняется временными диаграммами (фиг,5). На диаграмме 5а показан импульс запуска блока 18 длительностью Tjan, начало которого (момент

15

20

tp) является началом цикла обработки. На диаграаме SS показан задержанный импульс запуска на выходе элемента 26 задержки, в течение которого изображение проецируется на матрицу (с момента t д о момента t). На диаграмме 5Ь показан запускающий импульс .на выходе элемента задержки, по заднему фронту которого (момент tj) начинается собственно считывание изображения. На диаграмме 5z показаны тактовые импульсы на выходе ключа 24. На диаграмме 5а показано

напряжение на j-й столбцовой шине 7 ; до начала считывания и во время тактовых импульсов.на шине-присут-. ствует опорное напряжение и, во

время паузы между импульсами на шине, которая в это время является плавающей, устанавливается напряжение, определяемое яркостью считьша- емого элемента изображения Uj , j ; уровень напряжения, задающего порог бинаризации, показан пунктирной линией. На диаграммах 5е показаны сигналы на строчньгх шинах фотоприемной матрицы, подаваемые с выходов блока управления строчными шинами; во время Паузы такта, в котором считьта - ется данная строка, на шине присутствует нулевое напряжение, а в остальное время - напряжение хранения

35

40

45

50

и

SP

На диа грамме 5ж показаны вход- 55

15;

от ок ам по аг ци ст вы

фо во по пжеже

ля ло ют фи на т.

25 ст по по

эл

30 ри на за ши ни ну к ра ст по ст ро ме хо см в цы ря ни но со во ще ст ни

ные импульсы j-ro компаратора i..,, импульсы ,на выходе компаратора появляются, когда во время считыва шя со-

и5 га при нул

86

30

ответствующего элемента изображения (ячейки матрицы 3) напряжение УЗЛ i ,i оказывается меньше сдорного U, (т.е. амплитуда импульса U|j превышает пороговый уровень и, - Uo). На диаграмме 5 показан сигнал Конец цикла на выходе счетчика 25, пред- ставляюш 1й собой импульс напряжения высокого уровня.

Полярность рабочих напряжений фотоэлектрического преобразователя (матрицы 3) определяется типом проводимости подложки матрицы.Так, если подложка матрицы 3 имеет проводимость птипа, то рабочие напряжения (напряжение хранения U и опорное напряжение Ug) имеют отрицательнзто по0

5

0

5

0

лярность, а при использовании подложки р-типа рабочие напряжения имеют положительную полярность (на фиг.5 показаны временные диаграммы напряжений положительной полярности, т.е. для подложки р-типа проводимо5 сти) . Остальные напряжения имеют полярность, определяемую тип§м используемой элементной базы.

В предлагаемом устройстве фотоэлектрический преобразователь, (мат0 рица) работает при нулевом смещении на подложке (при считывании и при записи изображегшя соответствующие шины находятся под нулевым напряжением за счет соединения с шиной 37 нулевого потенциала). Это приводит к значительному влиянию на качество работы геометрического шума (следствие неоднородного темнового тока по площади матрицы) и снижению чувствительности матрицы и точности устройств. Для меньшения влияния, геометрического шума на подложку необходимо подать некоторое постоянное смещение U., благодаря которому в фоточувствительные ячейки матрицы вводится небольшой фоновый заряд, постоянно присутствующий в них. Фоновый заряд выравнивает тем- новой ток, насьпцает поверхностные состояния (ловушки полупроводниковой пластины) и за счет этого существенно улучшает параметры устройства. При работе с ненулевым смещением Uf напряжение на матрице изи5;. Смещение на матрицу можно организовать различными методами,на- пример подать его на шину 37 вместо нулевого потенциала.

Возможны различные варианты кон- Структивного исполнения матрицы фй- гоэлектрического преобразователя. Гак, в каждой фоточувствительной |ячейке один или оба ЩП-конденса iropa 5 и 6 могут иметь прозрачный электрод, фоточувствительной областью может быть также сам полупроводник ячейки. Возможно использование покрытий с пропусканием опреде- пенной длины волны света, что обеспечивает спектральную селективност матрицы. Шаг матрицы и размер фото чувствительной : ячейки составляет величину порядка 20-50 мкм, что позволяет получить разрешение до 40-50 ЛИН/ММ. Устройство может быть реализовано на существующей элементной базе. Блок 1 проецироваш я изо- бражения представляет собой оптическую систему (объектив). Оптический затвор 2 может быть механическим или электрооптическим (например, жидкокристаллическим, дефлек- торным и др.). Управляемые ключи 10 являются электронными и могут бьггь вьтолнены на полевых транзисторах, которые обеспечивают достаточное быстродействие и очень высокое сопротивление, необхсэдимое для создания режима плавающих столбцовых шин ynpawwet-ibm ключ может быть построе на основе траизисторых коммутаторов и управляемого мультиплексора.

Формула изобретени

1. Устройство для считывания и обработки изображений, содержащее фтоэлектрический преобразователь в I виде прямоугольной матрицы из MxN емкостных фотоэлементов с зарядовой связью, блок управления строчными iшинами, выходы которого соединены с соответствующими строчными шинами фотоэлектрического преобразователя, ;блок 1шючей, содержащ-хй N ключей, выход каждого из которых соединен с соответствующей столбцовой шиной фотоэлектрического преобразоватгутя, а первый и второй входы - соответственно с шиной нулевого потенци- ;ала и с шиной опорного напряжения, причем каждый емкостной фотоэлемент ;фотоэлектирческого преобразователя подключен своими электродами к соот :ветствующей ему строчной и столбцовой шине, отличающееся

0

5

0

5

тем, что, с целью расширения функциональных возможностей, оно дополнительно содержит блок проецирования изображения, оптический затвор, вход которого оптически соединен с выходом блока проецирования, а выход - с фотоэлектрическим преобразователем, формирователь импульсов запуска, вход которого является входом запуска устройства, первьй элемент задержки, вход которого соединен с выходом фор 1ирователя импульсов запуска, а выход - с управляющим входом оптического затвора, первый элемент ИЛИ, первый и второй входы которого связаны с входом сброса и выходом формирователя импульсов запуска С-оответственно, а выход подключен к входу сброса блока управления строчными шинаг-м и первому управляющему входу блока ключей, генератор .тактовых импульсов управляемый ключ, информационный вход которого подключен к выходу генератора тактовых импульсов,счетчик импульсов, счетный вход которого соединен с выходом управляемого ключа, второй элемент задержки, вход которого подключен к выходу первого элемента задержки, второй и третий элементы ИЛИ,первые входы которых соединены с выходами первого и второго элементов задержки соответствен но, а вторые - с входом повторного

0

5

запуска устройства, при этом выход второго элемента ШШ подключен к входу начальной установки блока управления строчными шинами, а выход третьего элемента ШТИ соединен с первым управляющим входом управляемого ключа и с входом начальной установки счетчика импульсов, блок компараторов, содержаищй N компараторов, вход каждого из KOTopbDc подключен к соответствующей столбцовой шине фотоэлектрического преобразователя, а вход опорного напряжения - к входу установки порога бинаризац11и устройства, блок логических анализа- , содержащий N .логических анали- .заторов, вход ка)вдого из которых подключен к выходу соответствующего компаратора блока ко шараторов, четвертый элемент ИЛИ,первый, второй и 5 третий входы которого соединены соответственно с выходом первого элемента задержки, входом сброса и входом повторного запуска устройства.

0

а выход - с входом сброса блока логических анализаторов, управляющий вход которого соединен с входЪм задания вида окрестности устройства а тактовый вход через третий элемент задержки соединен с выходом управляемого ключа, к которому подключены также тактовый вход блока управления строчными шинами и второй управляющий вход блока ключей, коммутатор, каждый управляющий вход которого соединен с выходом соответствующего логического анализатора блока логических анализаторов, а информационный вход подключен к первому выходу счетчика импульсов, второй выход которого соединен с вторым управляющим, входом управляемого ключа и выходом сигнала Конец цикла устройства, и блок памяти, каждый информационный .вход которого соединен с соответствующим вькодом коммутатора, тактовый вход подключен к выходу управляемого клича через третий элемент задержки, а вход сброса - к входу сброса устройства, при этом выход блока памяти является выходом устройства, а выходы компараторов образуют группу выходов сигналов силуэта изображения .

2, Устройство по П.1, отличающееся тем, что блок логических анализаторов содержит N логических анализаторов, каждый из ко- торых включает три последовательно соединенных D-триггеров, D-вход первого из которых является входом блока, а D-вход каждого следующего подключен к прямому выходу предьщущего, R-входы установки нуля подключены к входу сброса блока, а синхронизи- руюпре С-входы - к тактовому входу блока, четыре элемента ИЛИ, элемент И-НЕ и элемент И, выход которого является выходом анализатора, а первый, второй и третий входы с оедине- ны с выходом элемента И-НЕ,с прямым выходом второго D-триггера этого анализатора и с тактовым входом блока, вторые входы всех элементов ИЛИ соединены с управляющим входом блока, при этом в каждом j-м логическом анализаторе первый вход элемента И-НЕ и входы первого и второго элементов ИЛИ соединены соответственно с прямыми-выходами вто- , рого, третьего и первого D-триггеров соседнего (j-l)-ro логического анализатора, а выходы первого и второго, элементов ИЛИ подключены к второму и третьему входам элемента 10 И-МЕ, четвертый и пятый входы элемента И-НЕ соединены с прямыми выходами первого и третьего D-триггеров этого же логического анализатора, первые входы третьего и четвертого эле- 15 ментов ИЛИ и восьмой вход элемента И-НЕ соединены с прямыми выходами соответственно первого, третьего и второго D-триггеров соседнего (j+ +1)-го логического анализатора, а ще- 0 стой и седьмой входы элемента И-НЕ - с выходами третьего и четвертого элементов ИЛИ.

3. Устройство по п.1, о т л и ч а- ю щ е е с я тем, что блок управле- 5 ния строчными шинами содержит ()- (Разрядный сдвигающий регистр,,вход сброса, вход записи в младший разряд и тактовый вход которого соединены соответственно с входом сброса, 0 входом начальной установки и тактовым входом блока управления строчными шинами, М элементов И, М элементов ИЛИ, М ключевых элементов и инвертор, выход каждог® i-ro разряда сдвигающего регистра, за исключением -младшего, соединен с первым входом соответствующего i-ro элемента И, выход которого подключен к первому входу соответствующего i-ro элемента ИЛИ, к выходу которого подсоединен управляющий вход соответствующего i-ro ключевого элемента, выход которого является i-м выходом блока управления строчными шинами, при этом вторые входы всех 5 элементов И под1спючены к выходу

инвертора, вход которого соединен с тактовым входом блока управления строчными шинами, вторые входы всех элементов ИЛИ соединены с входом 0 сброса блока управления строчными шинами, а первый и второй входь; каж- дого ключевого элемента соединены соответственно с шиной напряжения хранения и с шиной нулевого потен- 5 циала,

5

0

1513486 6

.57

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования гистограммы изображения | 1990 |

|

SU1826081A1 |

| УСТРОЙСТВО СЧИТЫВАНИЯ ДЛЯ МНОГОЭЛЕМЕНТНЫХ ФОТОПРИЕМНИКОВ ИНФРАКРАСНОГО ИЗЛУЧЕНИЯ | 2013 |

|

RU2529768C1 |

| Устройство считывания для многоэлементных фотоприемников инфракрасного излучения | 2016 |

|

RU2645428C1 |

| ПАНЕЛЬ ЖИДКОКРИСТАЛЛИЧЕСКОГО ДИСПЛЕЯ И СПОСОБ УПРАВЛЕНИЯ ЕЮ | 1992 |

|

RU2089941C1 |

| Устройство для распознавания прямого края объекта | 1988 |

|

SU1587552A1 |

| Устройство для контроля дефектов фотошаблона | 1989 |

|

SU1698712A1 |

| КРЕМНИЕВЫЙ МУЛЬТИПЛЕКСОР | 2015 |

|

RU2602373C1 |

| Устройство преобразования аналогового видеосигнала в двухуровневый | 1982 |

|

SU1107335A1 |

| Устройство для обработки и считывания изображений | 1989 |

|

SU1661809A1 |

| Устройство для считывания изображений | 1987 |

|

SU1524074A1 |

Изобретение относится к автоматике и вычислительной технике и предназначено для использования в системах технического зрения промышленных роботов. Цель изобретения - расширение функциональных возможностей устройства за счет дополнительных операций обработки изображений. Поставленная цель достигается тем, что в устройство, содержащее фотоэлектрический преобразователь на M.N элементов, блок управления его строчными шинами и блок ключей, дополнительно введены блок проецирования изображений, оптический затвор, формирователь импульсов запуска, элементы задержки, элементы ИЛИ, блок коммутаторов, блок логических анализаторов, коммутатор, блок памяти и счетчик, а также тем, что блок логических анализаторов содержит N логических анализаторов, каждый из которых включает три D- триггера, четыре элемента ИЛИ, элемент И-НЕ и элемент И, а блок управления строчными шинами содержит М+1-разрядный сдвигающий регистр, М элементов И, ИЛИ, М ключевых элементов и инвертор. 2 з.п. ф-лы, 5 ил.

57

I « JUo

/f

31

t35

С

IT

ir

35

-0411

V

i

Д

f

л f ч /V f5 Г

Д

1 5.

-)

i5.

fi/

ffl , glL-JJ

/

MLCOcJ J

:

Z

/y

/7

W

Фш.1

-58

Фиг.З

Шиг.

| Букатов И.Л | |||

| и др | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| - Микроэлектроника, 1978, т.7, № 5, с.397-405 | |||

| Березин В.Ю | |||

| и др | |||

| Принципы построения и проблемы развития твердотельных фотоэлектрических преобразователей с координатной адресацией на приборах с переносом заряда | |||

| - Микроэлектроника и полупроводниковые приборы, 1980, вьт.5, с.239 - -243. | |||

| , ,(54) УСТРОЙСТВО | |||

| Способ получения на волокне оливково-зеленой окраски путем образования никелевого лака азокрасителя | 1920 |

|

SU57A1 |

| Цель изобретения - расширение функциональных возможностей устройства за счет аппаратной реализации операций вьщеления контура изображений , системах технического зрения промышленных роботов | |||

| Цель изобретения - расширение функциональных возможностей устройства за счет допол- нительньвЗ операций обработки изображений | |||

| Поставленная цель достигается тем, что в устройство, содержащее фотоэлектрический преобразователь на MxN элементов, блок управления его строчными шинами и блок ключей, дополнительно введены блок проецирования изображений, оптический затвор, фop rapoвaтeль импульсов запуска, элементы задержки, элементы ИЛИ, блок коммутаторов, блок логических анализаторов, коммутатор, блок памяти и счетчик, а также тем, что блок логических анализаторов содержит N логичесйих анализаторов, каждый из которых включает три D- триггера, четыре элемента ИЛИ, элемент И-НЕ и элемент И, а блок управления строчными шинами содержит М+1- разрядный сдвигающий регистр, М элементов И, ИШ-1, М ключевых элементов и инвертор | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| ф-лы, 5 ил | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1989-10-07—Публикация

1988-01-05—Подача