Ю

Изобретение относится к импульсной технике и может быть иенользова- но в измерительных устройствах о

Целью изобретения является расши- рение функциональных возможностей устройства путем обеспечения счета индикации с основанием двенадцать.

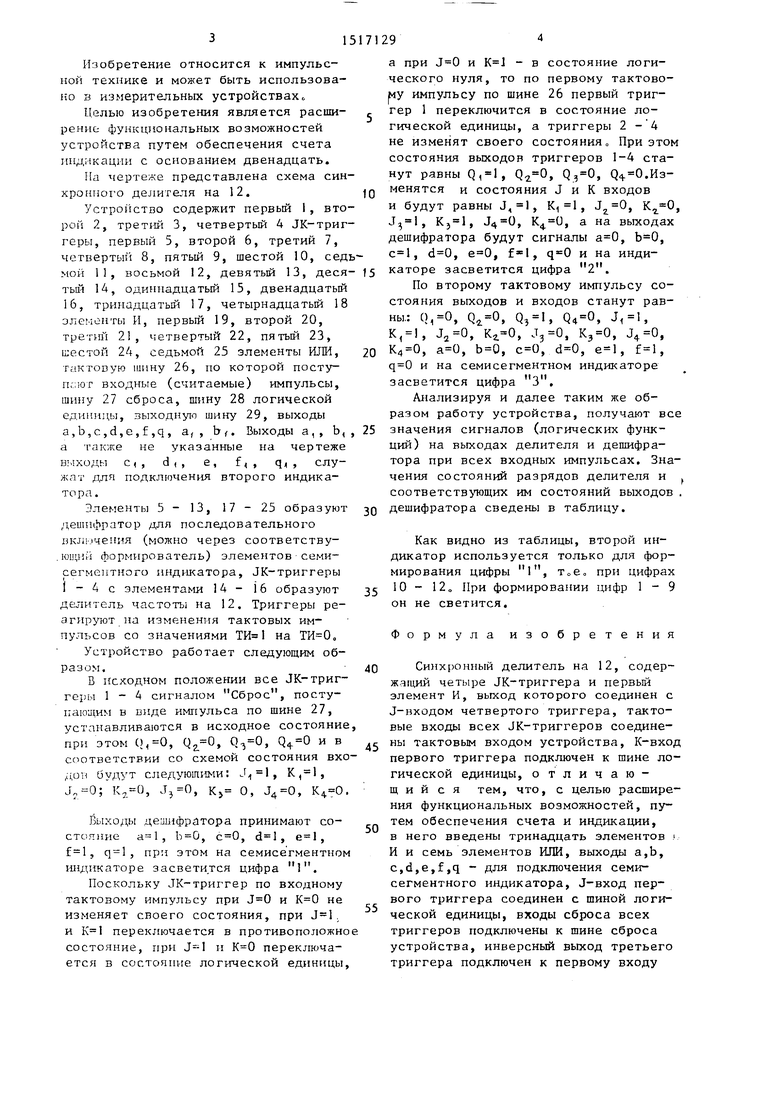

На чертеже представлена схема син xpoHiioi o делителя на 12.

YcTpoi icTBo содержит первый 1 , второй 2, третий 3, четвертый 4 JK-триг геры, первый 5, второй 6, третий 7, четвертый 8, пятый 9, шестой 10, седмой II, восьмой 12, девятый 13, деся тьш 1А, одиннадцатый 15, двенадцатьй 16, тринадцатый 17, четырнадцатьй 18 элементы И, первый 19, второй 20, третш 21, четвертый 22, пятый 23, шестой 24, седьмой 25 элементы ИЛИ, тактовую шину 26, но которой посту- п;.;ют входные (считаемые) импульсы, шину 27 сброса, шину 28 логической единицы, выходную шину 29, выходы a,b,c,d,e,f,q, а,, Ъ(, Выходы а,, Ь, а также не указанные на чертеже выходы с,, d,, е, f, , q, , служат для подключения второго индикатора.

Элементы 5 - 13, 17 - 25 образуют дешифратор для последовательного икл1 1чеиия (можно через соответству- .ющий формирователь) элементов семи- сегмептного индикатора, JK-триггеры I - 4 с элементами 14 - 16 образуют делитель частоть; на 12. Триггеры ре- на изменения тактовых импульсов со значениями на

Устройство работает следующим образом.

В исходном положении все JK-триггеры 1 - 4 сигналом Сброс, поступающим в виде импульса по шине 27, устанавливаются в исходное состояние при этом (),0, , , ив соответствии со схемой состояния вхо доп будут следующими: , К, 1, j,,0; К,0, , к5 О, , К4.0.

Выходы дешифратора принимают состояние , , , , , 1, , при этом на семисегментном индикаторе засвети.тся цифра 1.

Поскольку JK-триггер по входному тактовому импульсу при и не изменяет своего состояния, при и переключается в противоположно состояние, при и переключается в состояние логической единицы.

5 0 5

о 5

0

0

5

а при и - в состояние логического нуля, то по первому тактовому импульсу ПС шине 26 первый триггер 1 переключится в состояние логической единицы, а триггеры 2 - 4 не изменят своего состояния. При этом состояния выходов триггеров 1-4 станут равны Q, l, Q2.0, , .Изменятся и состояния J и к входов и будут равны J,l, , , , , , , , а на выходах дешифратора будут сигналы , , , , , , и на индикаторе засветится цифра 2.

По второму тактовому импульсу состояния выходов и входов станут рав- ны,: 0,0, , Q,I, , J,l, К, , , , , , , , , , , , , , и на семисегментном индикаторе засветится цифра 3,

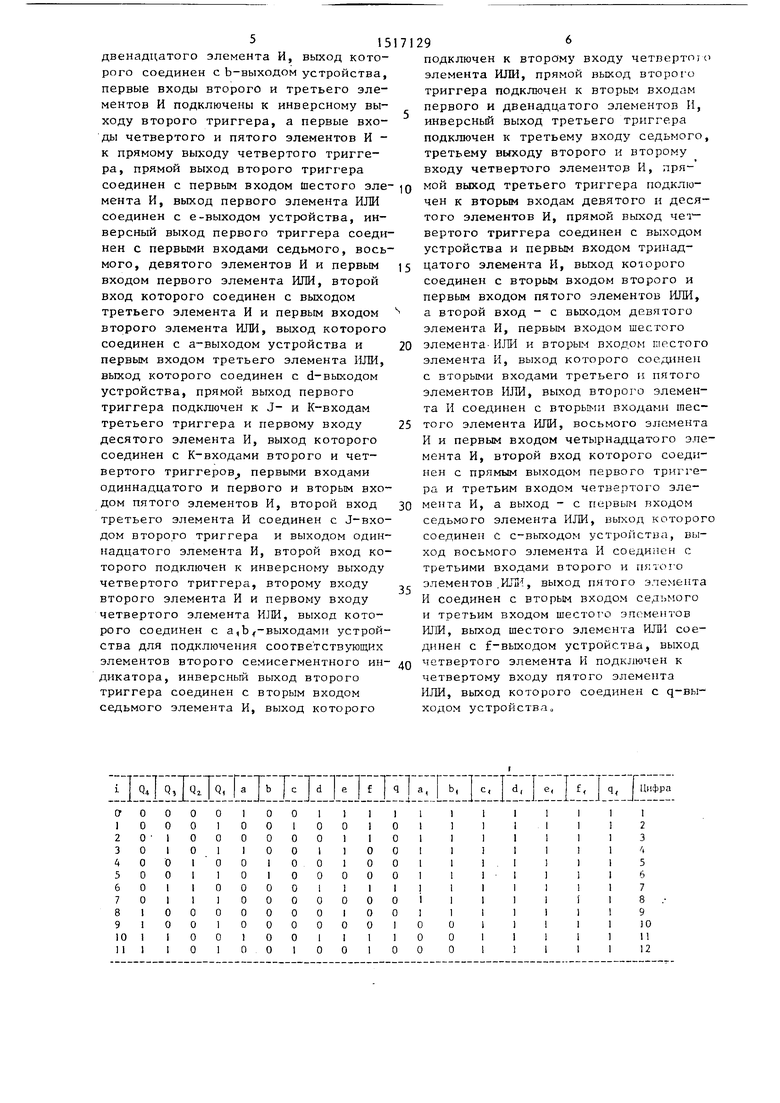

Анализируя и далее таким же образом работу устройства, получают все значения сигналов (логических функций) на выходах делителя и дешифратора при всех входных импульсах. Значения состояний разрядов делителя и соответств тощих им состояний выходов . дешифратора сведены в таблицу.

Как видно из таблицы, второй индикатор используется только для формирования цифры 1, т„е„ при цифрах 10 - 12„ При формировании цифр 1 - 9 он не светится.

Формула изобретения

Синхронный делитель на 12, содержащий четыре JK-триггера и первьй элемент И, выход которого соединен с J-входом четвертого триггера, тактовые входы всех JK-триггеров соединены тактовым входом устройства, К-вход первого триггера подключен к шине логической единицы, отличающийся тем, что, с целью расширения функциональных возможностей, путем обеспечения счета и индикации, в него введены тринадцать элементов ) И и семь элементов ИЛИ, выходы а,Ь, c,d,e,f,q - для подключения семи- сегментного индикатора, J-вход первого триггера соединен с шиной логической единицы, входы сброса всех триггеров подключены к шине сброса устройства, инверсный выход третьего триггера подключен к первому входу

515

двенадцатого элемента И, выход которого соединен с Ь-выходом устройства, первые входы второго и третьего элементов И подключены к инверсному выходу второго триггера, а первые входы четвертого и пятого элементов И - к прямому выходу четвертого триггера, прямой выход второго триггера соединен с первым входом Шестого элемента И, выход первого элемента ИЛИ соединен с е-выходом устройства, инверсный выход первого триггера соединен с первыми входами седьмого, восьмого, девятого элементов И и первым входом первого элемента ИЛИ, второй вход которого соединен с выходом третьего элемента И и первым входом второго элемента ИЛИ, выход которого соединен с а-выходом устройства и первым входом третьего элемента ИЛИ, выход которого соединен с d-выходом устройства, прямой выход первого триггера подключен к J- и К-входам третьего триггера и первому входу десятого элемента И, выход которого соединен с К-входами второго и четвертого триггеров, первыми входами одиннадцатого и перйого и вторым входом пятого элементов И, второй вход третьего элемента И соединен с J-вхо- дом второго триггера и выходом одиннадцатого элемента И, второй вход которого подключен к инвepcнo fy выходу четвертого триггера, второму входу второго элемента И и первому входу четвертого элемента ИЛИ, выход которого соединен с а Ь -выходами устройства для подключения соответствующих элементов второго семисегментного индикатора, инверсный выход второго триггера соединен с вторым входом седьмого элемента И, выход которого

296

подключен к второму входу четвертог ,) элемента ИЛИ, прямой выход второго триггера подключен к вторым входам первого и двенадцатого элементов И, инверсный выход третьего триггера подключен к третьему входу седьмого, третьему выходу второго и второму входу четвертого элементов И, лрямой выход третьего триггера подключен к вторым входам девятого и десятого элементов И, прямой выход четвертого триггера соединен с выходом устройства и первым входом тринадцатого элемента И, выход которого соединен с вторым входом второго и первым входом пятого элементов ИЛИ,

а второй вход - с выходом девятого элемента И, первым входом шестого

элемента-ИЛИ и вторым входом шестого элемента И, выход которого соединен с вторыми входами третьего и пятого элементов ИЛИ, выход второго элемента И соединен с вторыми входами шестого элемента ИЛИ, восьмого элемента И и первым входом четырнадцатого элемента И, второй вход которого соединен с прямым выходом первого триггера и третьим входом четвертого элемента И, а выход - с первым входом седьмого элемента ИЛИ, выход которого соединен с с-выходом устройства, вы- ход восьмого элемента И соединен с третьими входами второго и пятого элементов .ИЛ1-, выход пятого элемента И соединен с вторым входом седьмого и третьим входом шестотю эпемеитов ИЛИ, выход шестого элемента ИЛИ соединен с f-выходом устройства, выход четвертого элемента И подключен к четвертому входу пятого элемента Р1ЛИ, выход которого соединен с q-Bbi-- ходом устройства„

| название | год | авторы | номер документа |

|---|---|---|---|

| Реверсивная счетная декада | 1988 |

|

SU1554141A1 |

| Декадный счетчик для семисегментных индикаторов | 1987 |

|

SU1451853A1 |

| Декадный счетчик для семисегментных индикаторов | 1986 |

|

SU1383494A1 |

| Декадный счетчик для семисегментных индикаторов | 1985 |

|

SU1330757A1 |

| Счетчик импульсов для семисегментных индикаторов | 1988 |

|

SU1580550A1 |

| Вычитающий декадный счетчик для семисегментных индикаторов | 1986 |

|

SU1383492A1 |

| Декадный счетчик для семисегментных индикаторов | 1986 |

|

SU1359906A1 |

| Декадный счетчик для семисегментных индикаторов | 1985 |

|

SU1319276A1 |

| Декадный счетчик для семисегментных индикаторов | 1985 |

|

SU1285592A1 |

| Декадный счетчик для семисегментных индикаторов | 1986 |

|

SU1368985A1 |

Изобретение относится к импульсной технике и может быть использовано в измерительных устройствах. Цель изобретения - расширение функциональных возможностей - достигается путем обеспечения счета индикации с основанием двенадцать. Синхронный делитель содержит JK-триггеры 1-4, элементы И 5-18, элементы ИЛИ 19-25, тактовую шину 26, по которой поступают входные импульсы, шину 27 сброса, шину 28 логической единицы, выходную шину 28. Элементы 5-13 и 17-25 образуют дешифратор для последовательного включения элементов семисегментного индикатора, JK-триггеры 1-4 с элементами 14-16 образуют делитель частоты на двенадцать. 1 табл., 1 ил.

| Справочник по интегральным микросхемам, - М.:Энергия, 1980, с„7-11, рис«5-286„ Авторское свидетельство СССР 1298902, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-10-23—Публикация

1987-11-27—Подача